Conjunto de instrues assembly Cdigomquina assembler add s

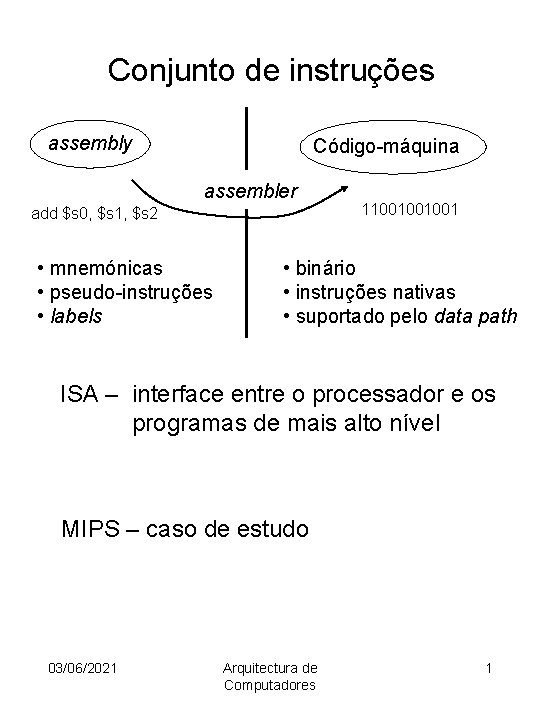

Conjunto de instruções assembly Código-máquina assembler add $s 0, $s 1, $s 2 • mnemónicas • pseudo-instruções • labels 11001001001 • binário • instruções nativas • suportado pelo data path ISA – interface entre o processador e os programas de mais alto nível MIPS – caso de estudo 03/06/2021 Arquitectura de Computadores 1

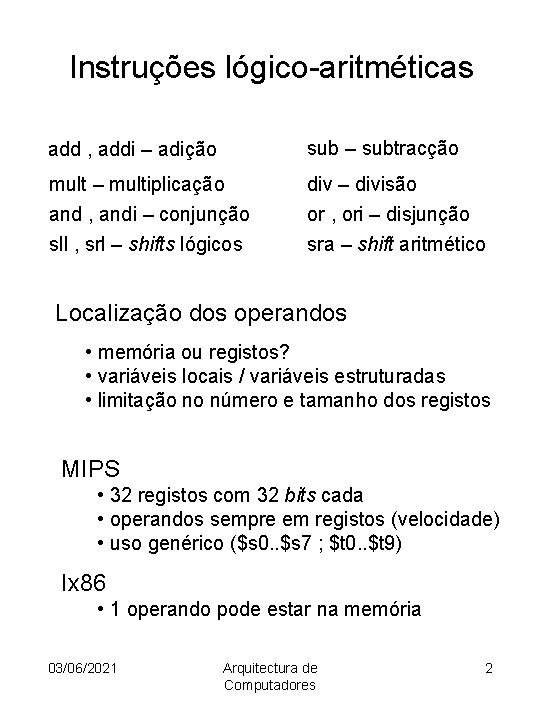

Instruções lógico-aritméticas add , addi – adição sub – subtracção mult – multiplicação and , andi – conjunção sll , srl – shifts lógicos div – divisão or , ori – disjunção sra – shift aritmético Localização dos operandos • memória ou registos? • variáveis locais / variáveis estruturadas • limitação no número e tamanho dos registos MIPS • 32 registos com 32 bits cada • operandos sempre em registos (velocidade) • uso genérico ($s 0. . $s 7 ; $t 0. . $t 9) Ix 86 • 1 operando pode estar na memória 03/06/2021 Arquitectura de Computadores 2

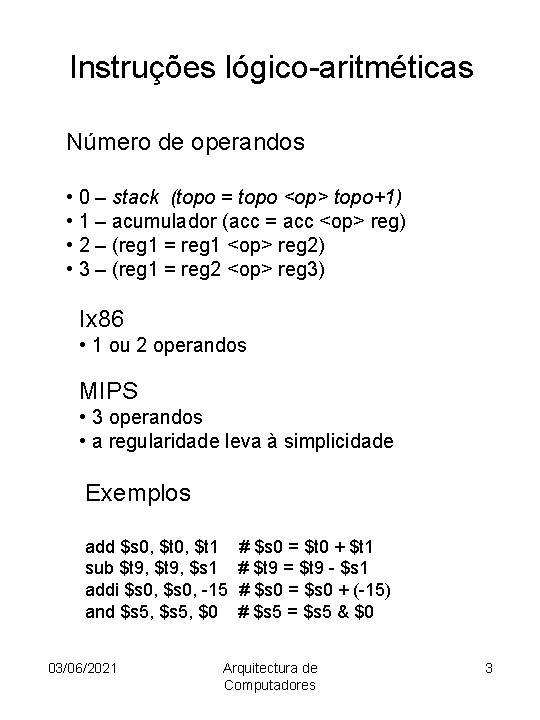

Instruções lógico-aritméticas Número de operandos • 0 – stack (topo = topo <op> topo+1) • 1 – acumulador (acc = acc <op> reg) • 2 – (reg 1 = reg 1 <op> reg 2) • 3 – (reg 1 = reg 2 <op> reg 3) Ix 86 • 1 ou 2 operandos MIPS • 3 operandos • a regularidade leva à simplicidade Exemplos add $s 0, $t 1 sub $t 9, $s 1 addi $s 0, -15 and $s 5, $0 03/06/2021 # $s 0 = $t 0 + $t 1 # $t 9 = $t 9 - $s 1 # $s 0 = $s 0 + (-15) # $s 5 = $s 5 & $0 Arquitectura de Computadores 3

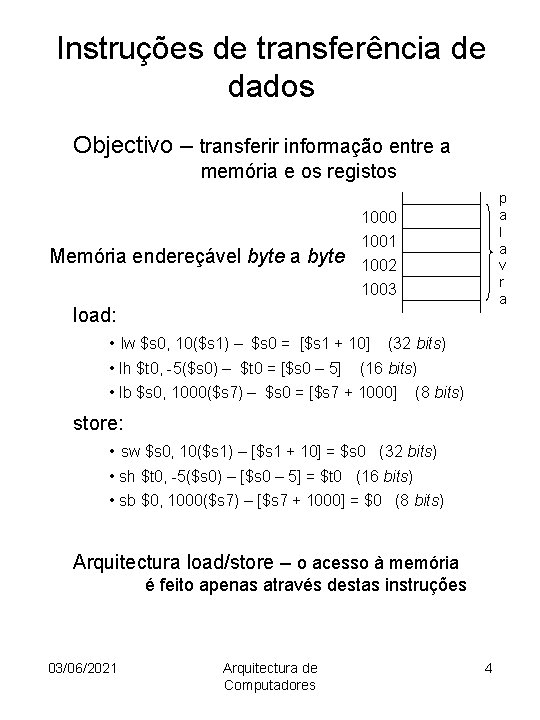

Instruções de transferência de dados Objectivo – transferir informação entre a memória e os registos Memória endereçável byte a byte p a l a v r a 1000 1001 1002 1003 load: • lw $s 0, 10($s 1) – $s 0 = [$s 1 + 10] (32 bits) • lh $t 0, -5($s 0) – $t 0 = [$s 0 – 5] (16 bits) • lb $s 0, 1000($s 7) – $s 0 = [$s 7 + 1000] (8 bits) store: • sw $s 0, 10($s 1) – [$s 1 + 10] = $s 0 (32 bits) • sh $t 0, -5($s 0) – [$s 0 – 5] = $t 0 (16 bits) • sb $0, 1000($s 7) – [$s 7 + 1000] = $0 (8 bits) Arquitectura load/store – o acesso à memória é feito apenas através destas instruções 03/06/2021 Arquitectura de Computadores 4

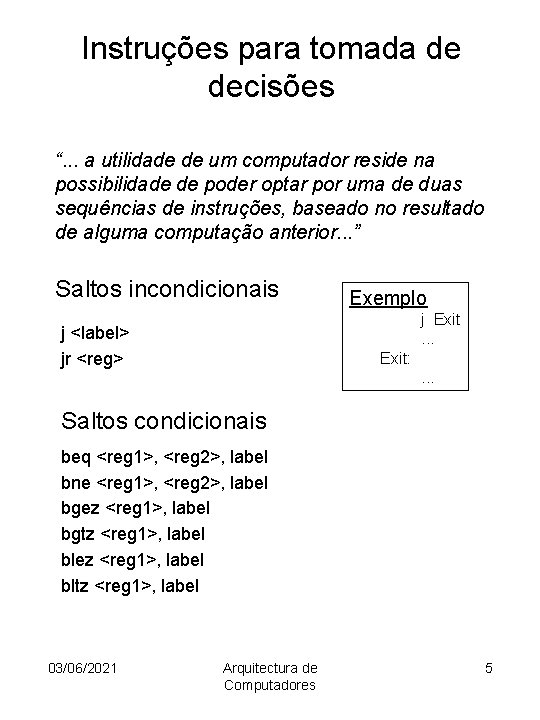

Instruções para tomada de decisões “. . . a utilidade de um computador reside na possibilidade de poder optar por uma de duas sequências de instruções, baseado no resultado de alguma computação anterior. . . ” Saltos incondicionais Exemplo j Exit. . . j <label> jr <reg> Exit: . . . Saltos condicionais beq <reg 1>, <reg 2>, label bne <reg 1>, <reg 2>, label bgez <reg 1>, label bgtz <reg 1>, label blez <reg 1>, label bltz <reg 1>, label 03/06/2021 Arquitectura de Computadores 5

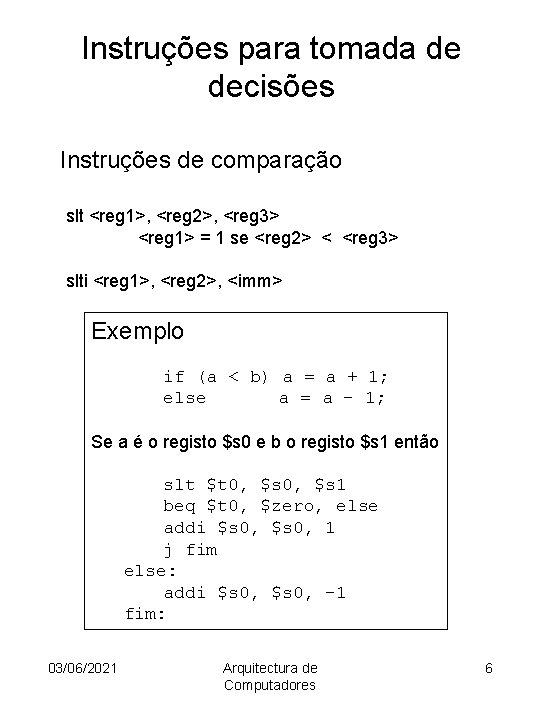

Instruções para tomada de decisões Instruções de comparação slt <reg 1>, <reg 2>, <reg 3> <reg 1> = 1 se <reg 2> < <reg 3> slti <reg 1>, <reg 2>, <imm> Exemplo if (a < b) a = a + 1; else a = a – 1; Se a é o registo $s 0 e b o registo $s 1 então slt $t 0, $s 1 beq $t 0, $zero, else addi $s 0, 1 j fim else: addi $s 0, -1 fim: 03/06/2021 Arquitectura de Computadores 6

- Slides: 6