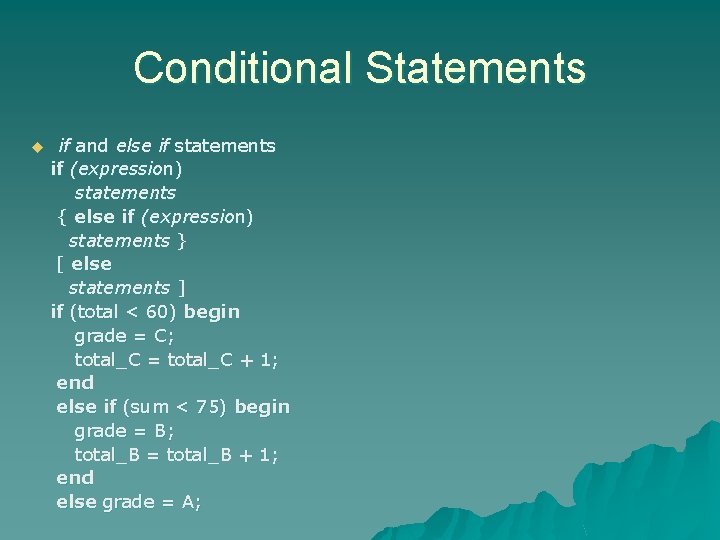

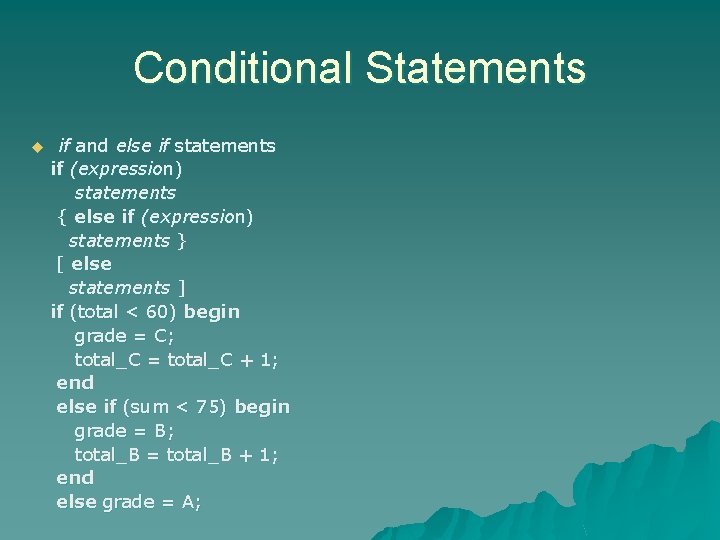

Conditional Statements u if and else if statements

- Slides: 14

Conditional Statements u if and else if statements if (expression) statements { else if (expression) statements } [ else statements ] if (total < 60) begin grade = C; total_C = total_C + 1; end else if (sum < 75) begin grade = B; total_B = total_B + 1; end else grade = A;

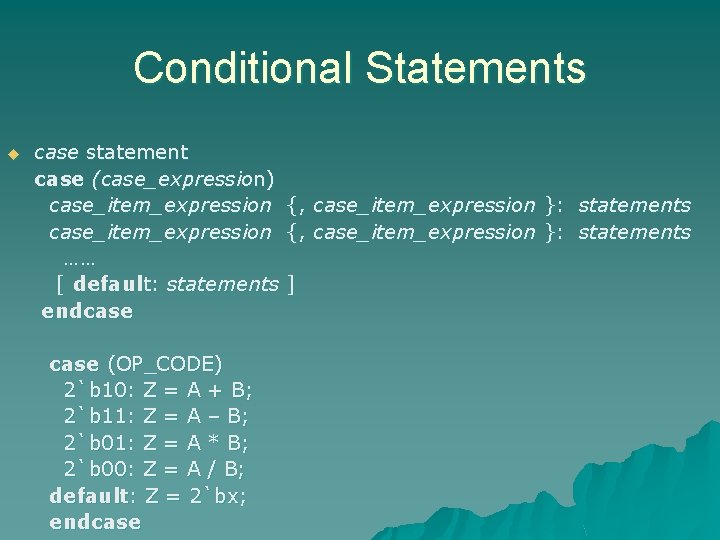

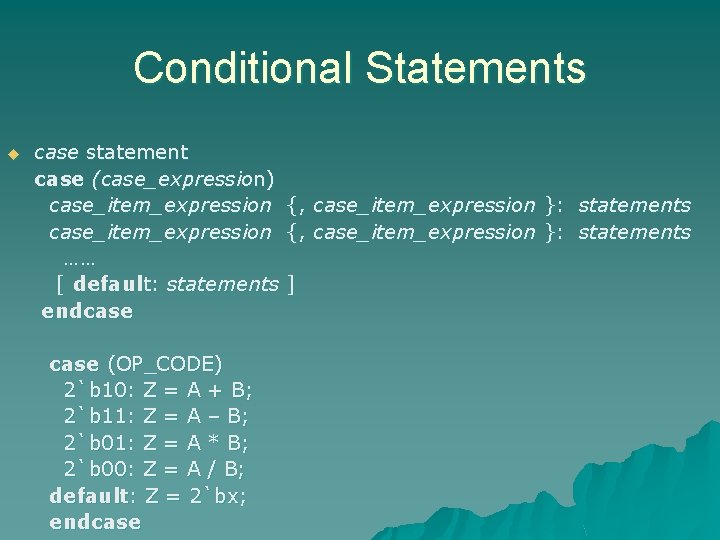

Conditional Statements u case statement case (case_expression) case_item_expression …… [ default: statements endcase (OP_CODE) 2`b 10: Z = A + B; 2`b 11: Z = A – B; 2`b 01: Z = A * B; 2`b 00: Z = A / B; default: Z = 2`bx; endcase {, case_item_expression }: statements ]

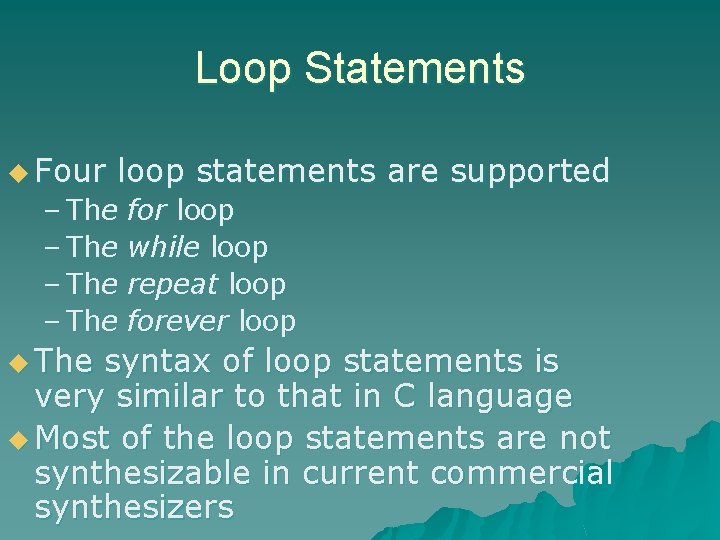

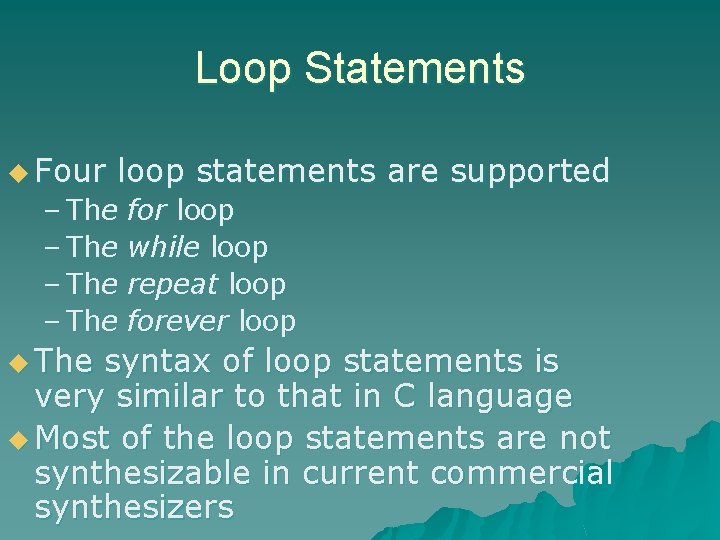

Loop Statements u Four loop statements are supported – The u The for loop while loop repeat loop forever loop syntax of loop statements is very similar to that in C language u Most of the loop statements are not synthesizable in current commercial synthesizers

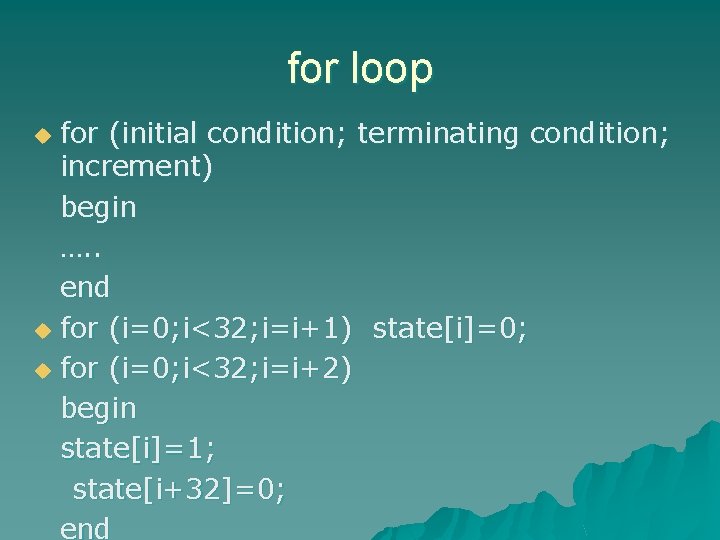

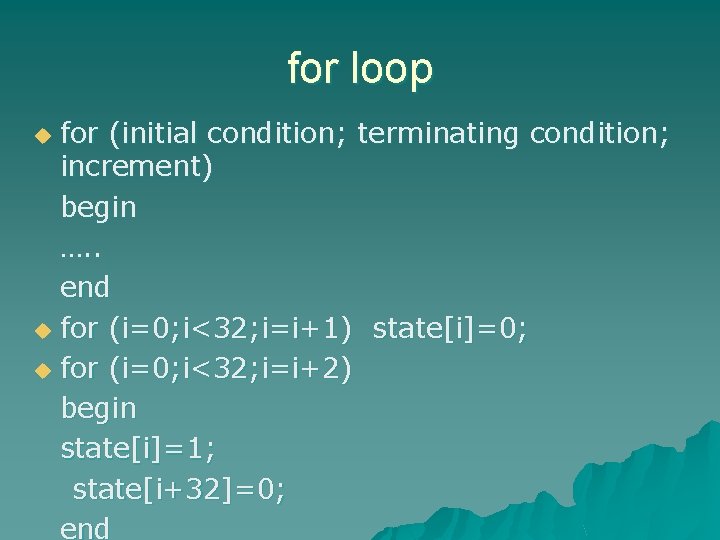

for loop for (initial condition; terminating condition; increment) begin …. . end u for (i=0; i<32; i=i+1) state[i]=0; u for (i=0; i<32; i=i+2) begin state[i]=1; state[i+32]=0; end u

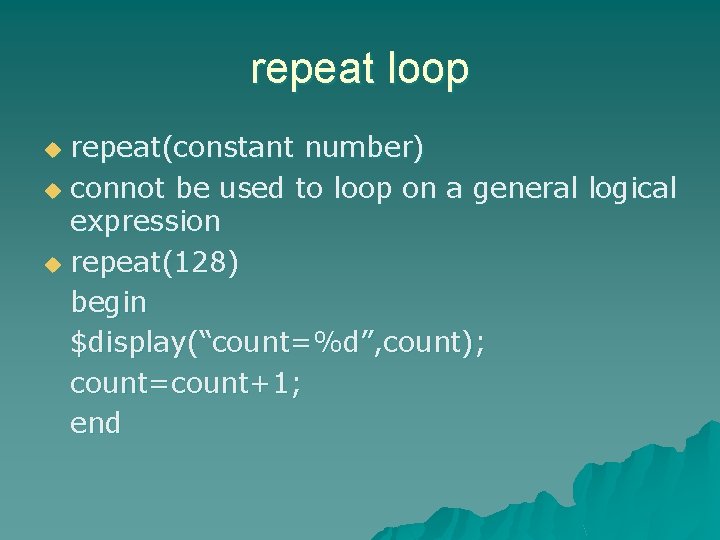

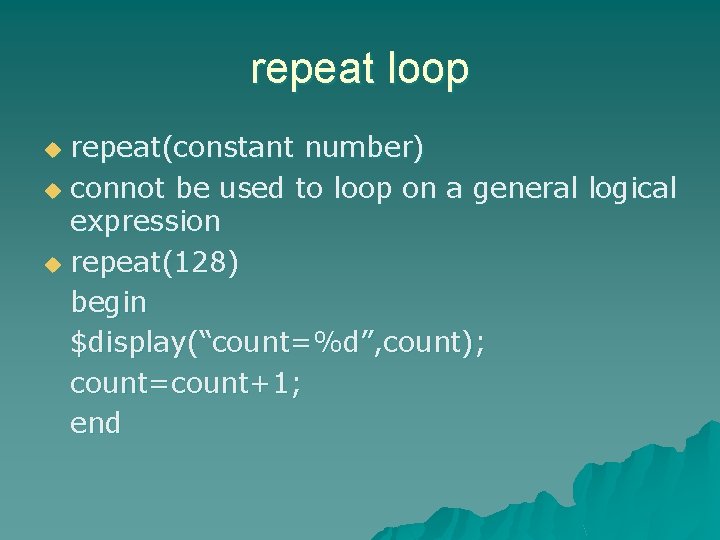

repeat loop repeat(constant number) u connot be used to loop on a general logical expression u repeat(128) begin $display(“count=%d”, count); count=count+1; end u

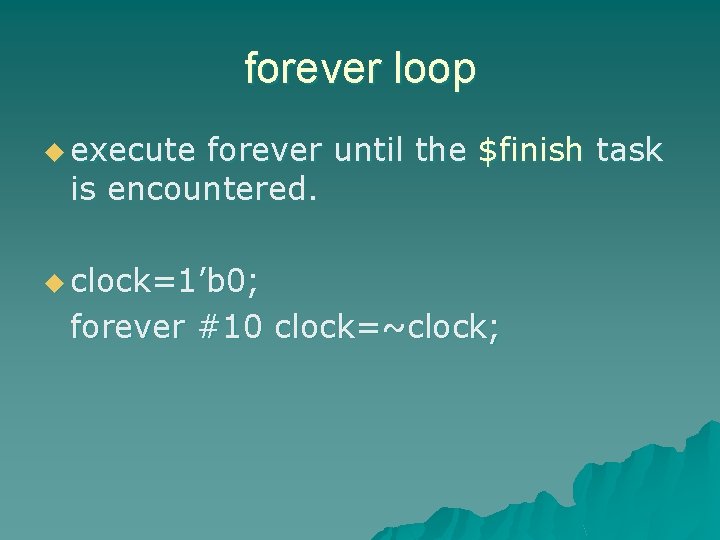

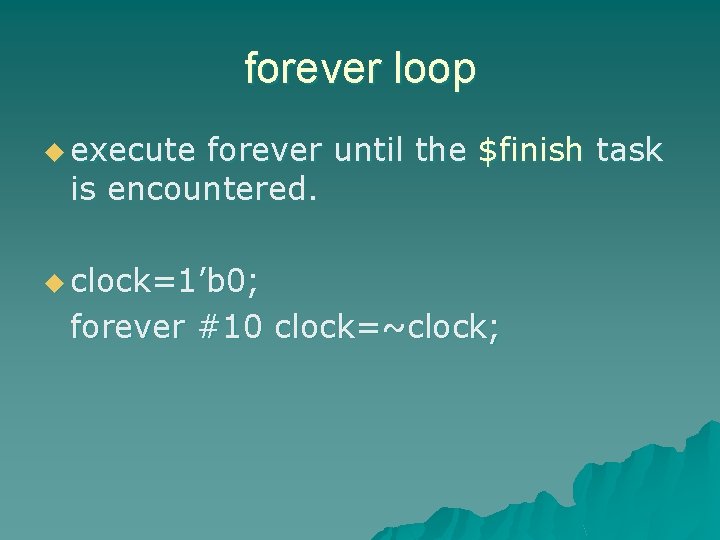

forever loop u execute forever until the $finish task is encountered. u clock=1’b 0; forever #10 clock=~clock;

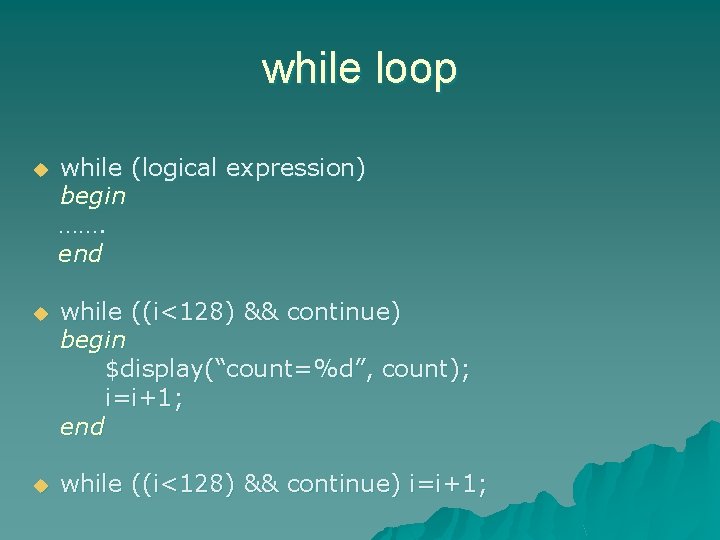

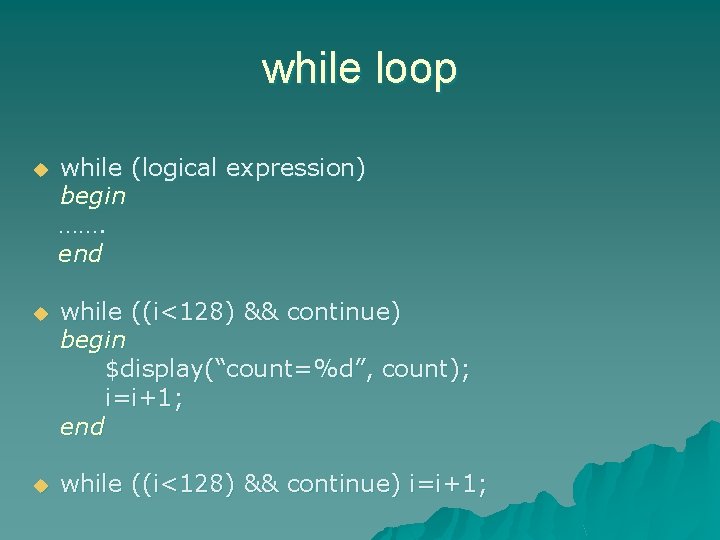

while loop u while (logical expression) begin ……. end u while ((i<128) && continue) begin $display(“count=%d”, count); i=i+1; end u while ((i<128) && continue) i=i+1;

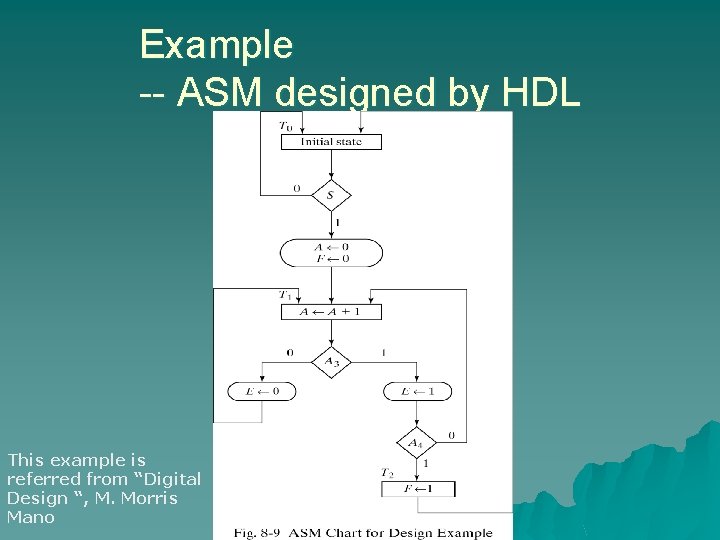

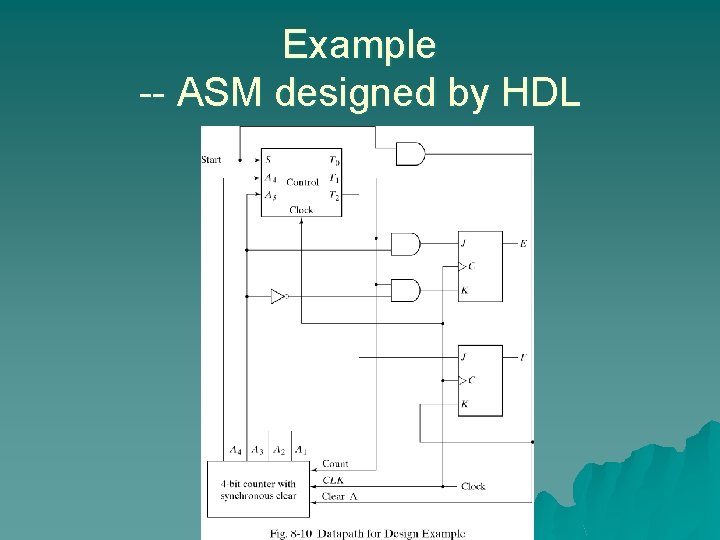

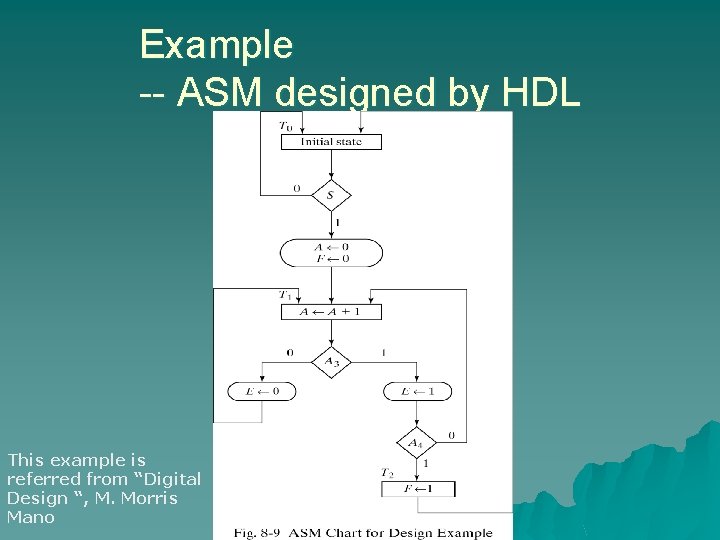

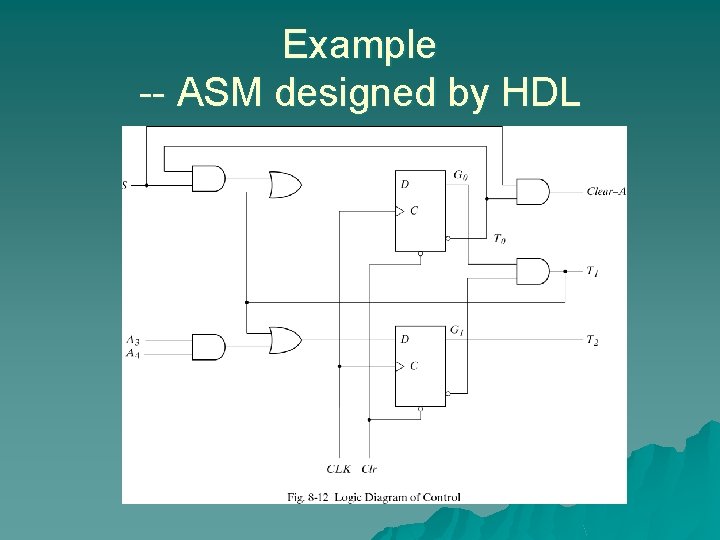

Example -- ASM designed by HDL This example is referred from “Digital Design “, M. Morris Mano

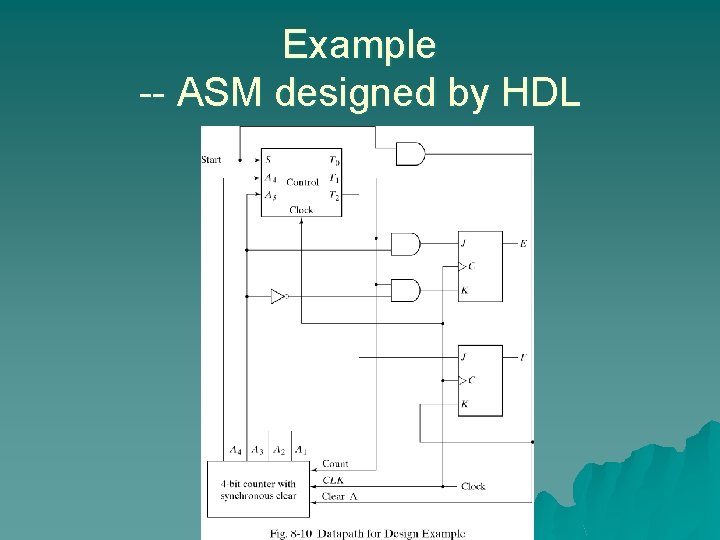

Example -- ASM designed by HDL

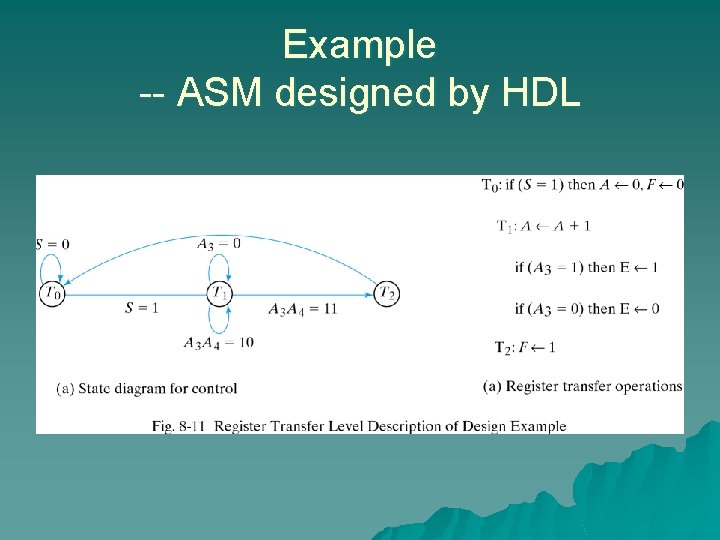

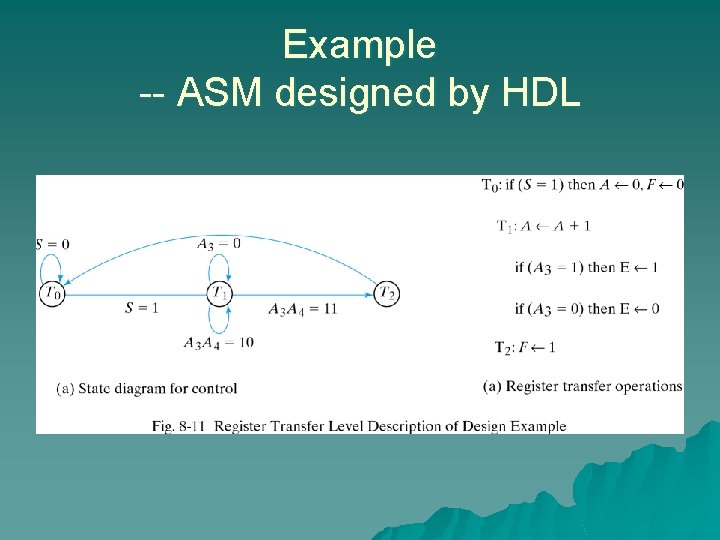

Example -- ASM designed by HDL

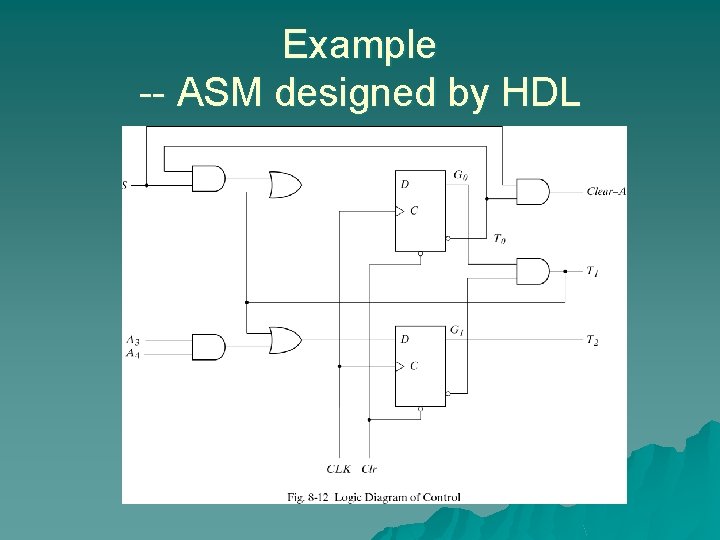

Example -- ASM designed by HDL

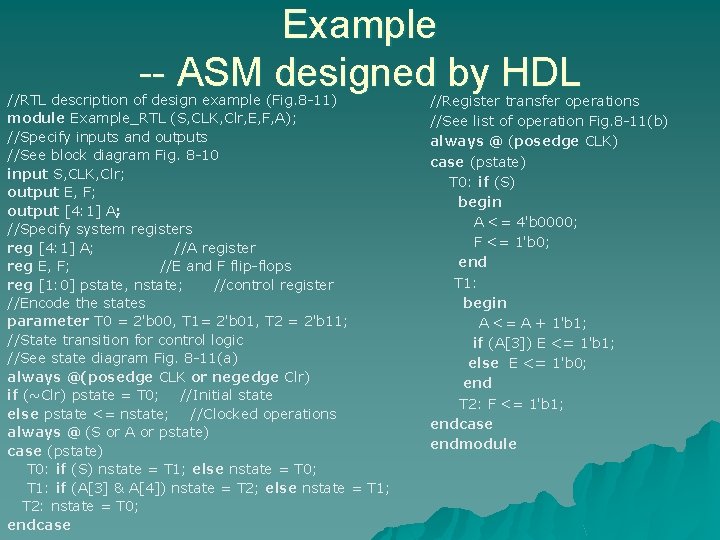

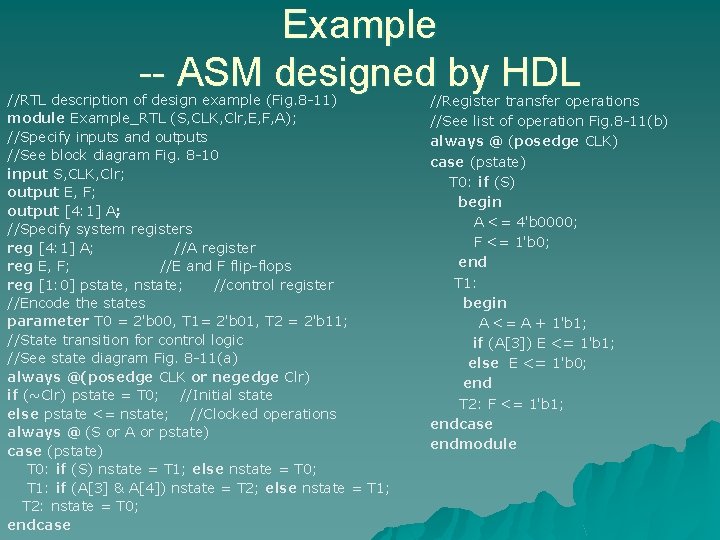

Example -- ASM designed by HDL //RTL description of design example (Fig. 8 -11) module Example_RTL (S, CLK, Clr, E, F, A); //Specify inputs and outputs //See block diagram Fig. 8 -10 input S, CLK, Clr; output E, F; output [4: 1] A; //Specify system registers reg [4: 1] A; //A register reg E, F; //E and F flip-flops reg [1: 0] pstate, nstate; //control register //Encode the states parameter T 0 = 2'b 00, T 1= 2'b 01, T 2 = 2'b 11; //State transition for control logic //See state diagram Fig. 8 -11(a) always @(posedge CLK or negedge Clr) if (~Clr) pstate = T 0; //Initial state else pstate <= nstate; //Clocked operations always @ (S or A or pstate) case (pstate) T 0: if (S) nstate = T 1; else nstate = T 0; T 1: if (A[3] & A[4]) nstate = T 2; else nstate = T 1; T 2: nstate = T 0; endcase //Register transfer operations //See list of operation Fig. 8 -11(b) always @ (posedge CLK) case (pstate) T 0: if (S) begin A <= 4'b 0000; F <= 1'b 0; end T 1: begin A <= A + 1'b 1; if (A[3]) E <= 1'b 1; else E <= 1'b 0; end T 2: F <= 1'b 1; endcase endmodule

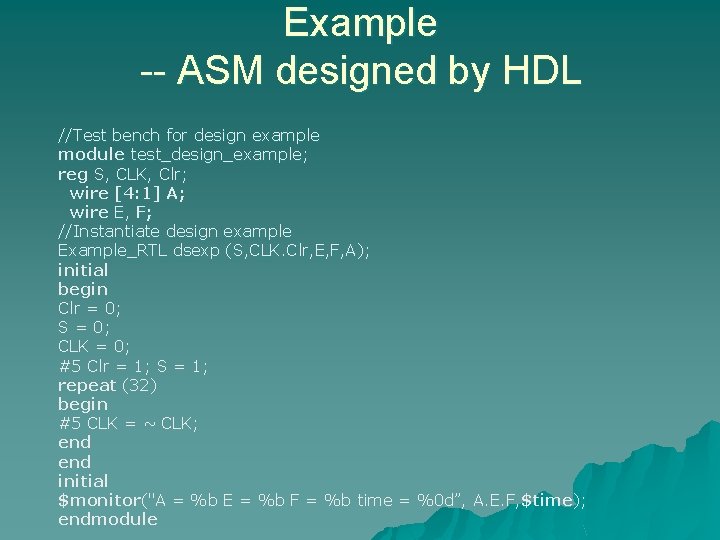

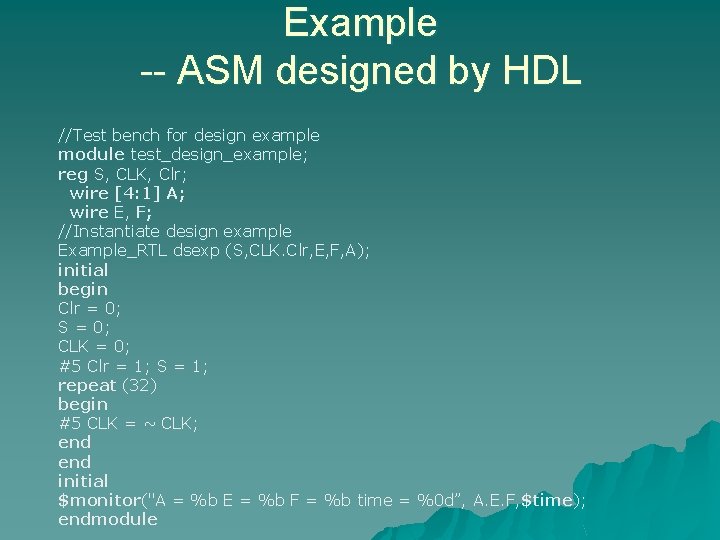

Example -- ASM designed by HDL //Test bench for design example module test_design_example; reg S, CLK, Clr; wire [4: 1] A; wire E, F; //Instantiate design example Example_RTL dsexp (S, CLK. Clr, E, F, A); initial begin Clr = 0; S = 0; CLK = 0; #5 Clr = 1; S = 1; repeat (32) begin #5 CLK = ~ CLK; end initial $monitor("A = %b E = %b F = %b time = %0 d”, A. E. F, $time); endmodule

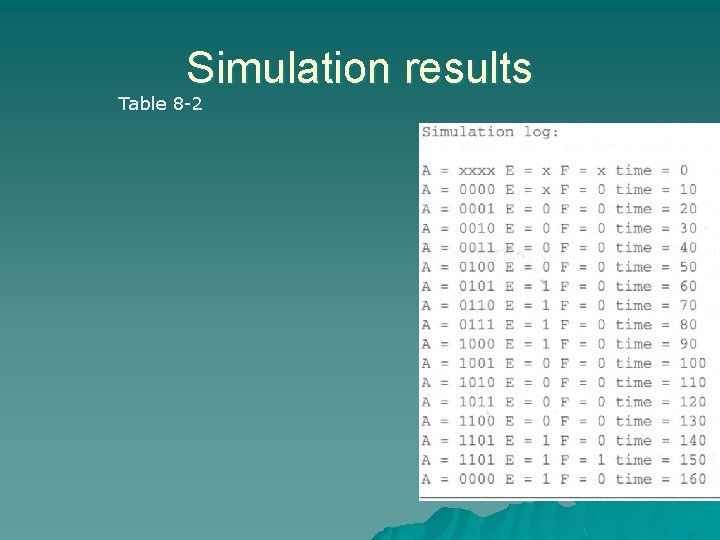

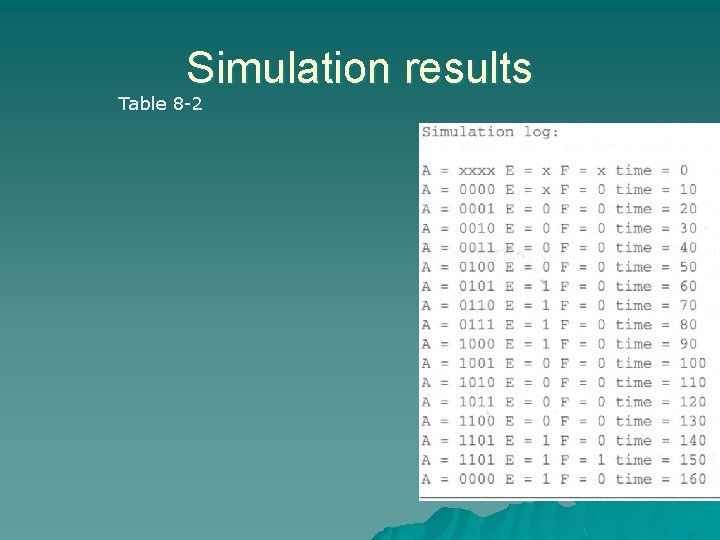

Simulation results Table 8 -2