Concurrent statements Concurrent statements lie between the begin

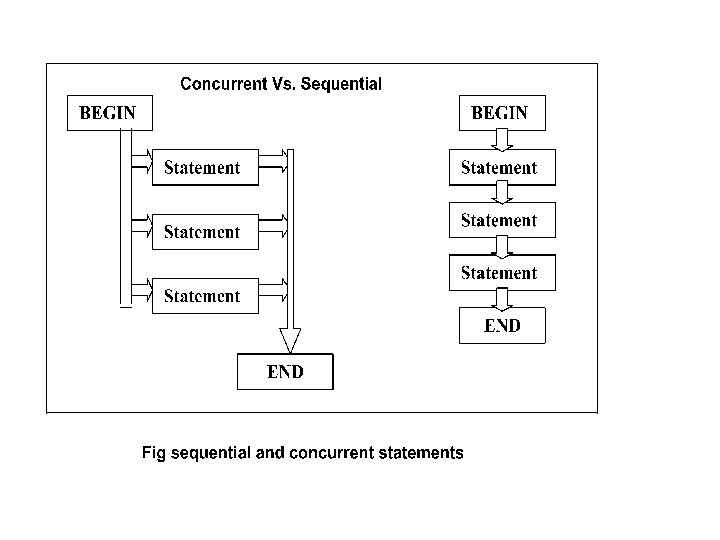

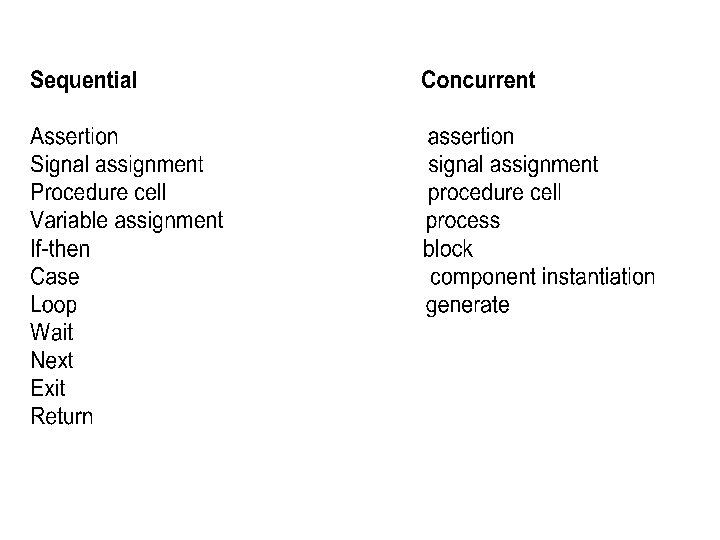

Concurrent statements • Concurrent statements lie between the ‘begin ‘ and ‘end’ portion of an architecture. • They are executed in parallel. • Concurrent signal assignment statements • Selective signal assignment • Conditional signal assignment • Process statement • Component Instantiation • Generate statement

Concurrent statements • The block and process are concurrent statements. • Signal assignments & procedure calls are concurrent provided they do not reside in a process statement. • The order of the concurrent statements does not have an effect on the logic that is described.

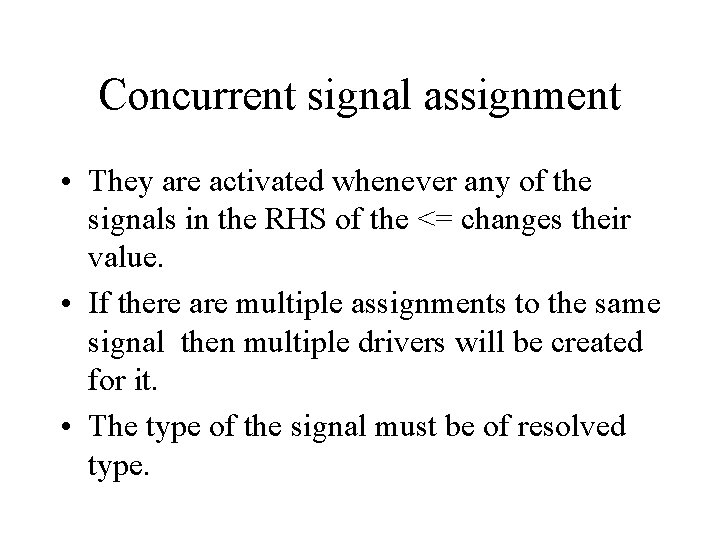

Concurrent signal assignment • They are activated whenever any of the signals in the RHS of the <= changes their value. • If there are multiple assignments to the same signal then multiple drivers will be created for it. • The type of the signal must be of resolved type.

Concurrent signal assignment • Architecture concurrent of half_adder is • begin • sum <= a xor b; • carry <= a and b; • end concurrent;

Concurrent signal assignment • Architecture conc of ent is • begin • y <= a or b; • Y <= a and b; • end conc; • -- multiple drivers will be created for signal y.

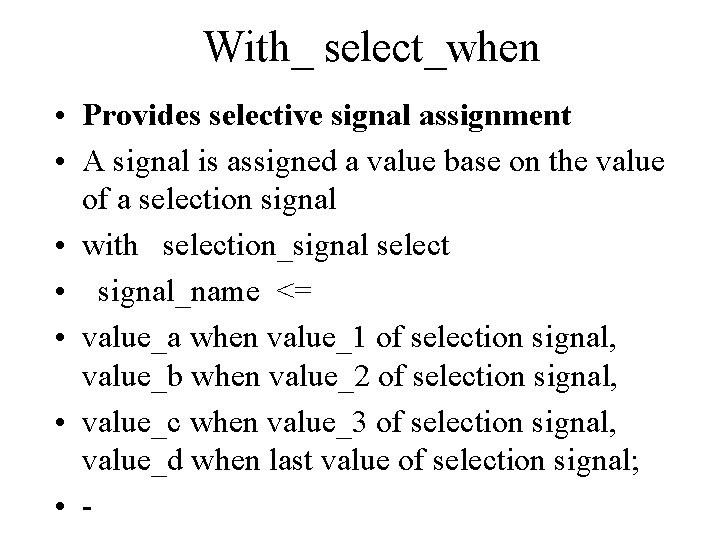

With_ select_when • Provides selective signal assignment • A signal is assigned a value base on the value of a selection signal • with selection_signal select • signal_name <= • value_a when value_1 of selection signal, value_b when value_2 of selection signal, • value_c when value_3 of selection signal, value_d when last value of selection signal; • -

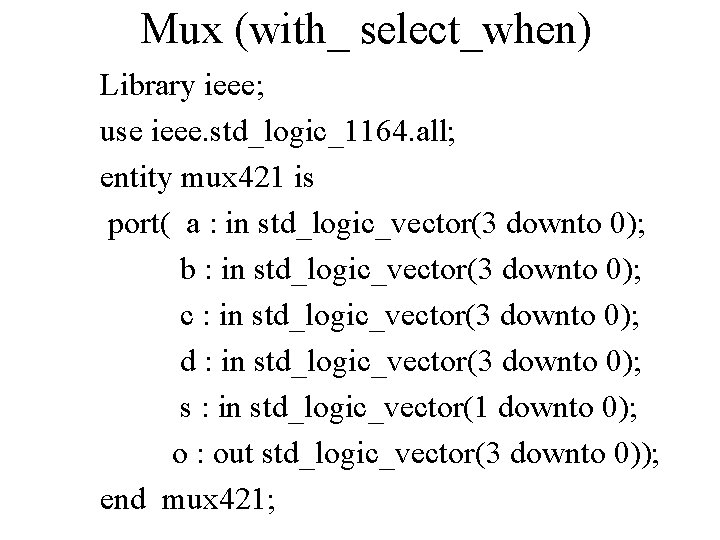

Mux (with_ select_when) Library ieee; use ieee. std_logic_1164. all; entity mux 421 is port( a : in std_logic_vector(3 downto 0); b : in std_logic_vector(3 downto 0); c : in std_logic_vector(3 downto 0); d : in std_logic_vector(3 downto 0); s : in std_logic_vector(1 downto 0); o : out std_logic_vector(3 downto 0)); end mux 421;

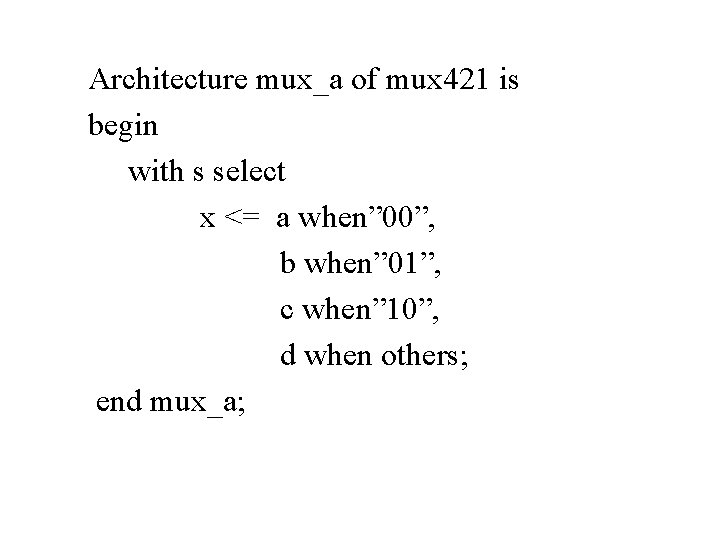

Architecture mux_a of mux 421 is begin with s select x <= a when” 00”, b when” 01”, c when” 10”, d when others; end mux_a;

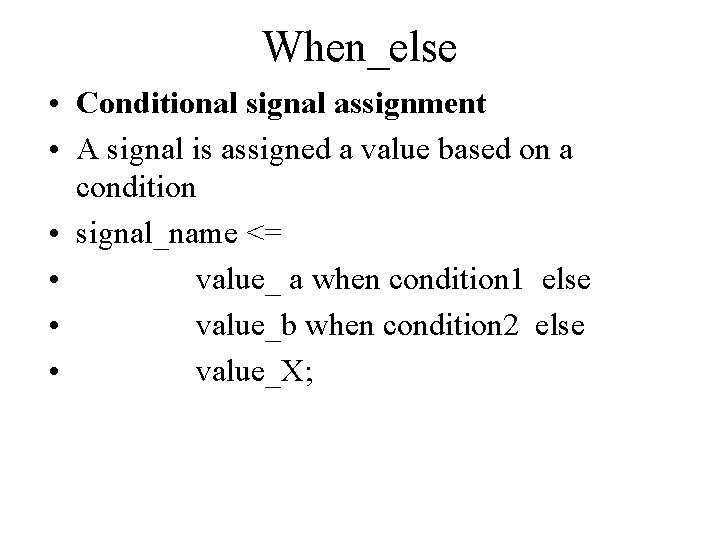

When_else • Conditional signal assignment • A signal is assigned a value based on a condition • signal_name <= • value_ a when condition 1 else • value_b when condition 2 else • value_X;

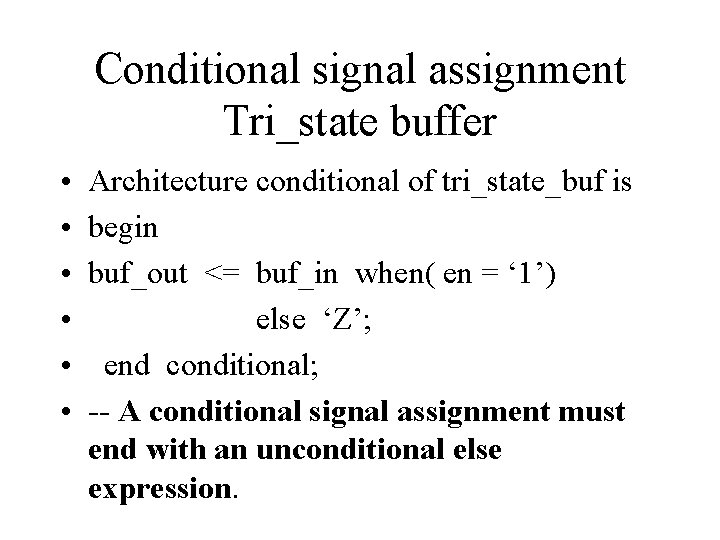

Conditional signal assignment Tri_state buffer • • • Architecture conditional of tri_state_buf is begin buf_out <= buf_in when( en = ‘ 1’) else ‘Z’; end conditional; -- A conditional signal assignment must end with an unconditional else expression.

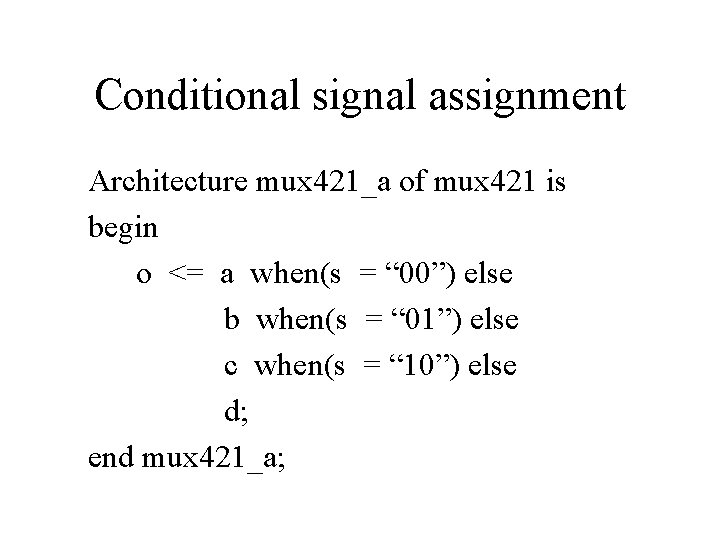

Conditional signal assignment Architecture mux 421_a of mux 421 is begin o <= a when(s = “ 00”) else b when(s = “ 01”) else c when(s = “ 10”) else d; end mux 421_a;

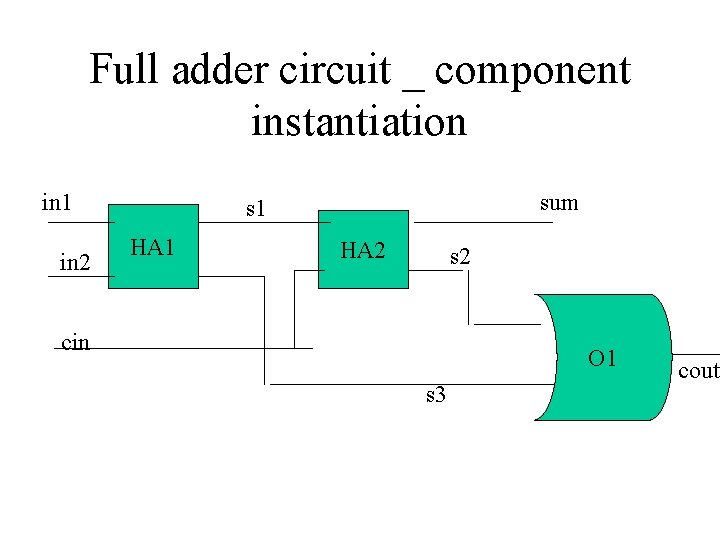

Full adder circuit _ component instantiation in 1 in 2 sum s 1 HA 2 s 2 cin O 1 s 3 cout

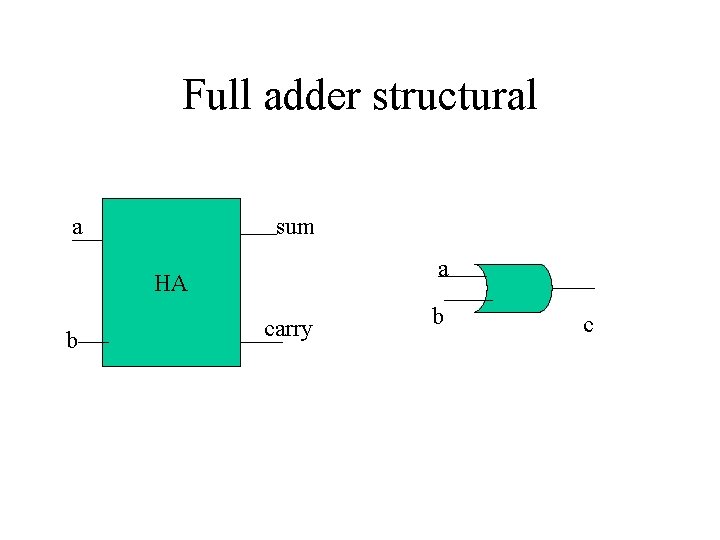

Full adder structural a sum a HA b carry b c

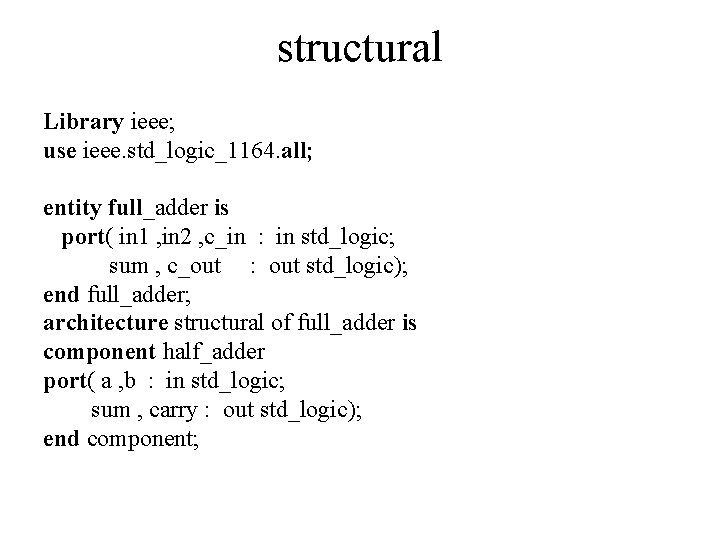

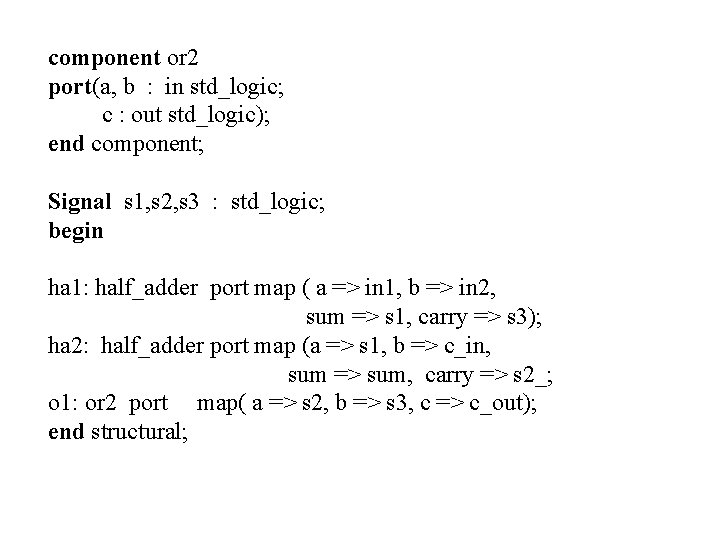

structural Library ieee; use ieee. std_logic_1164. all; entity full_adder is port( in 1 , in 2 , c_in : in std_logic; sum , c_out : out std_logic); end full_adder; architecture structural of full_adder is component half_adder port( a , b : in std_logic; sum , carry : out std_logic); end component;

component or 2 port(a, b : in std_logic; c : out std_logic); end component; Signal s 1, s 2, s 3 : std_logic; begin ha 1: half_adder port map ( a => in 1, b => in 2, sum => s 1, carry => s 3); ha 2: half_adder port map (a => s 1, b => c_in, sum => sum, carry => s 2_; o 1: or 2 port map( a => s 2, b => s 3, c => c_out); end structural;

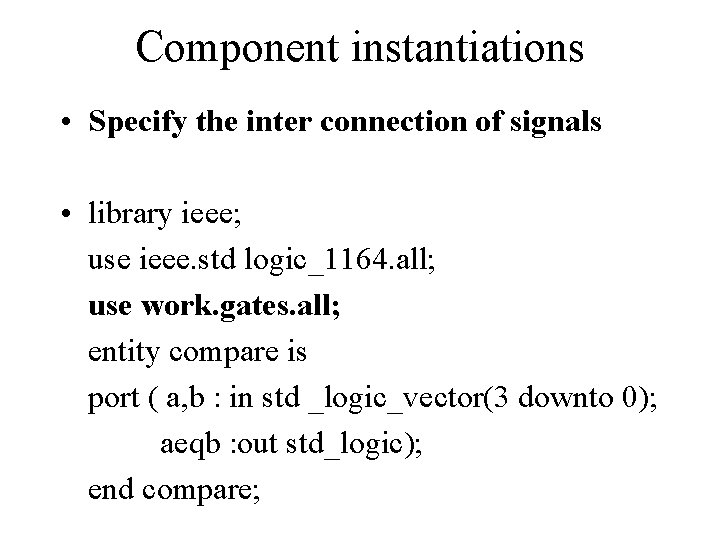

Component instantiations • Specify the inter connection of signals • library ieee; use ieee. std logic_1164. all; use work. gates. all; entity compare is port ( a, b : in std _logic_vector(3 downto 0); aeqb : out std_logic); end compare;

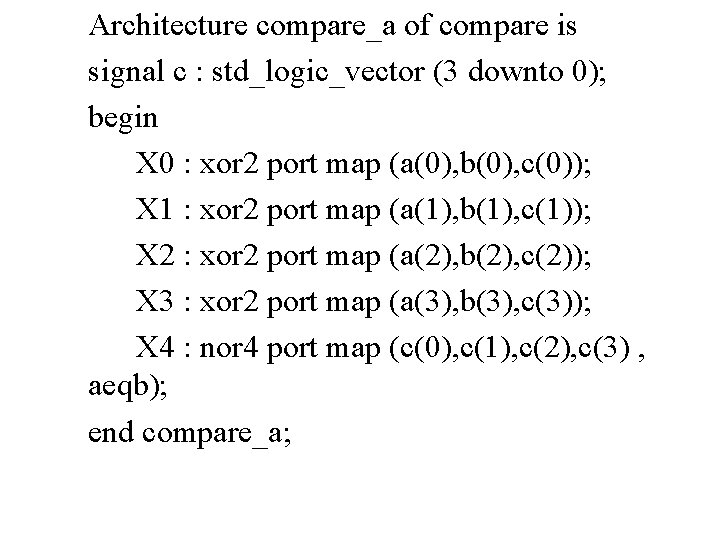

Architecture compare_a of compare is signal c : std_logic_vector (3 downto 0); begin X 0 : xor 2 port map (a(0), b(0), c(0)); X 1 : xor 2 port map (a(1), b(1), c(1)); X 2 : xor 2 port map (a(2), b(2), c(2)); X 3 : xor 2 port map (a(3), b(3), c(3)); X 4 : nor 4 port map (c(0), c(1), c(2), c(3) , aeqb); end compare_a;

A 4 bit comparator

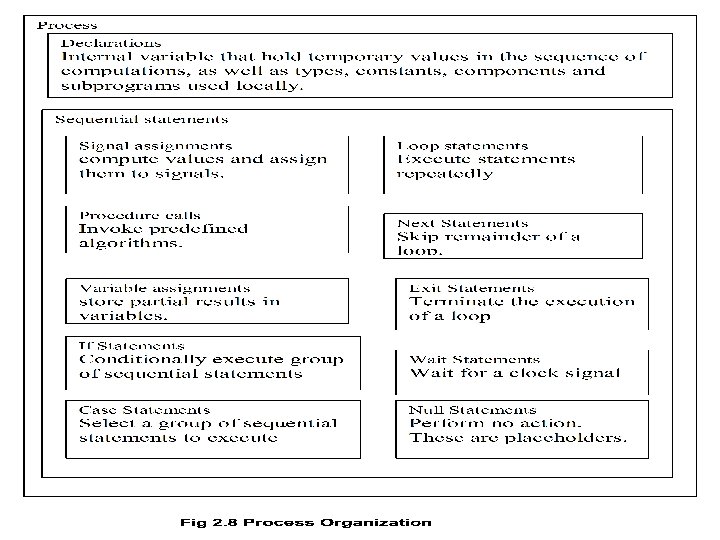

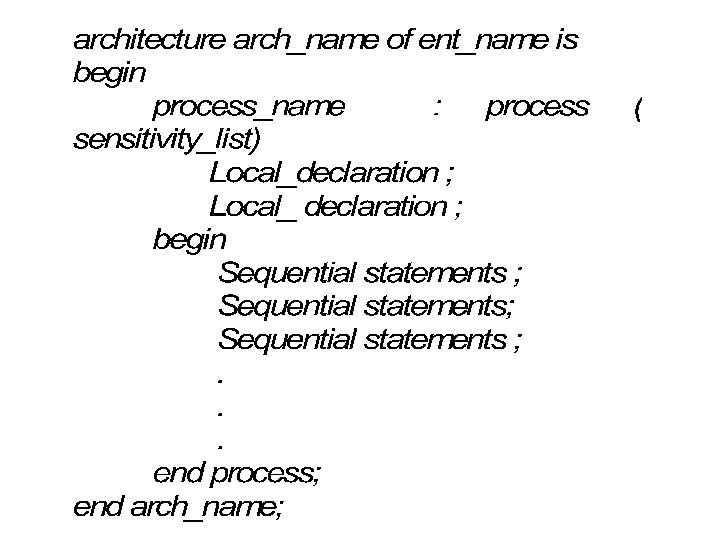

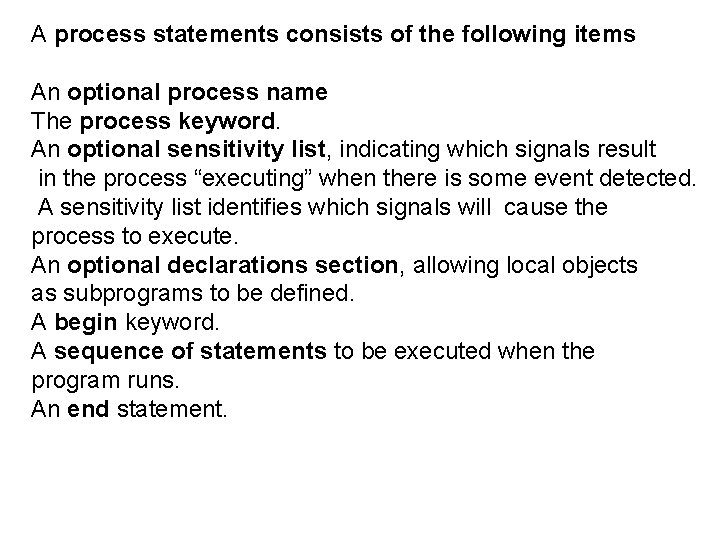

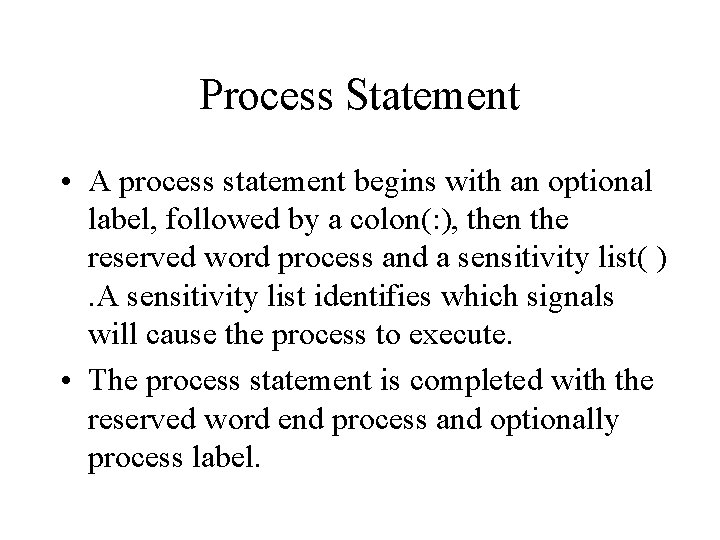

A process statements consists of the following items An optional process name The process keyword. An optional sensitivity list, indicating which signals result in the process “executing” when there is some event detected. A sensitivity list identifies which signals will cause the process to execute. An optional declarations section, allowing local objects as subprograms to be defined. A begin keyword. A sequence of statements to be executed when the program runs. An end statement.

![Process statement with a sensitivity list. [Label : ]Process (sensitivity_signal_list) {constant_declaration} {variable_declaration} begin {sequential Process statement with a sensitivity list. [Label : ]Process (sensitivity_signal_list) {constant_declaration} {variable_declaration} begin {sequential](http://slidetodoc.com/presentation_image_h2/ae7430f774f425bd70d57e183b8ae82e/image-24.jpg)

Process statement with a sensitivity list. [Label : ]Process (sensitivity_signal_list) {constant_declaration} {variable_declaration} begin {sequential statements} end process [label ];

![Process statement without a sensitivity list. [Label : ] Process {constant_declaration} {variable_declaration} begin {sequential Process statement without a sensitivity list. [Label : ] Process {constant_declaration} {variable_declaration} begin {sequential](http://slidetodoc.com/presentation_image_h2/ae7430f774f425bd70d57e183b8ae82e/image-25.jpg)

Process statement without a sensitivity list. [Label : ] Process {constant_declaration} {variable_declaration} begin {sequential statements} end process [label] ;

Process Statement • A process statement begins with an optional label, followed by a colon(: ), then the reserved word process and a sensitivity list( ). A sensitivity list identifies which signals will cause the process to execute. • The process statement is completed with the reserved word end process and optionally process label.

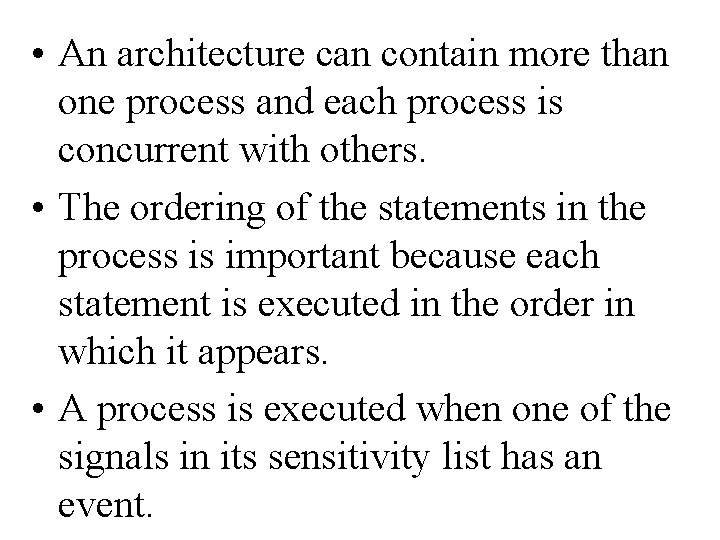

• An architecture can contain more than one process and each process is concurrent with others. • The ordering of the statements in the process is important because each statement is executed in the order in which it appears. • A process is executed when one of the signals in its sensitivity list has an event.

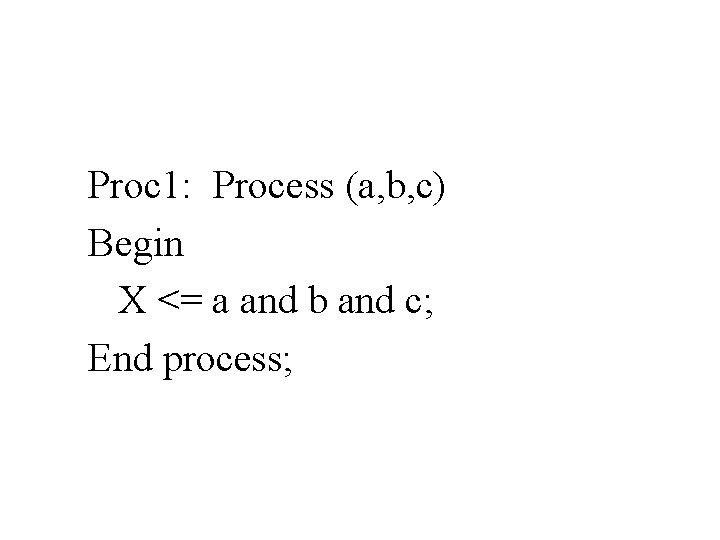

Proc 1: Process (a, b, c) Begin X <= a and b and c; End process;

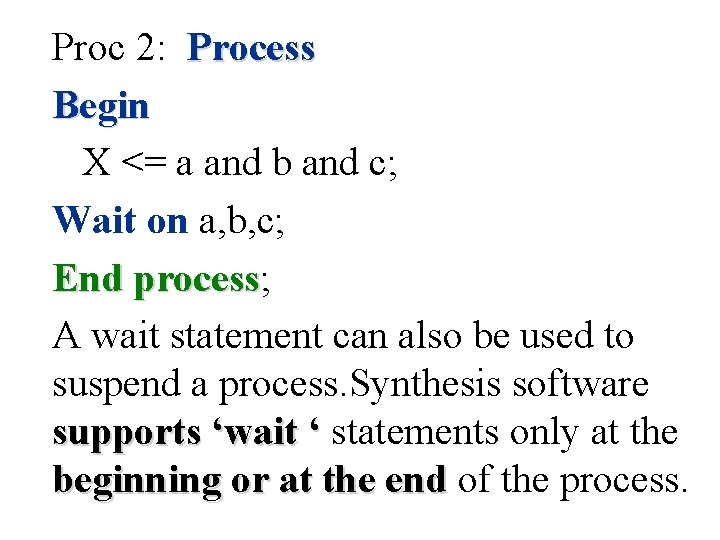

Proc 2: Process Begin X <= a and b and c; Wait on a, b, c; End process; process A wait statement can also be used to suspend a process. Synthesis software supports ‘wait ‘ statements only at the beginning or at the end of the process.

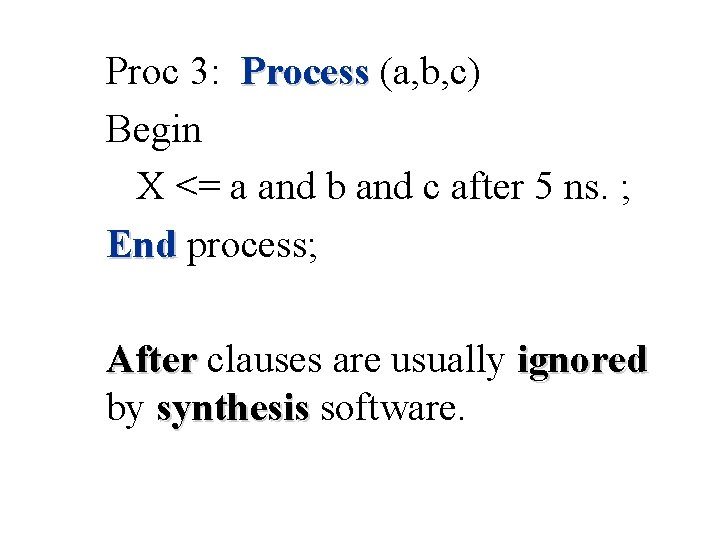

Proc 3: Process (a, b, c) Begin X <= a and b and c after 5 ns. ; End process; After clauses are usually ignored by synthesis software.

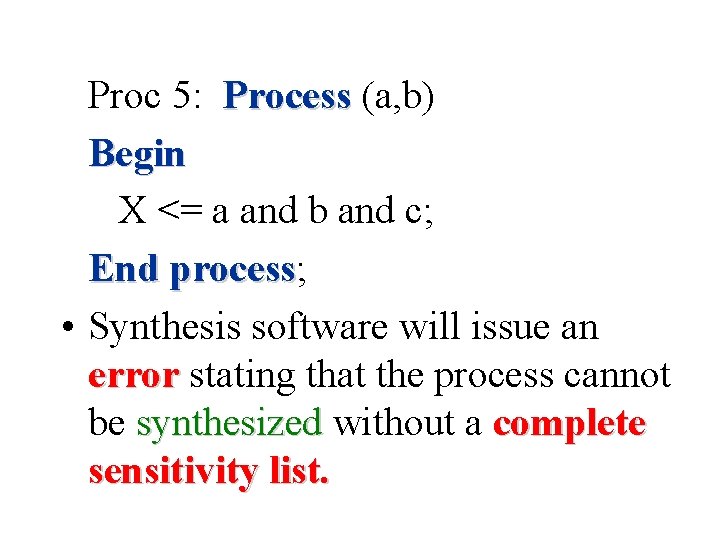

Proc 5: Process (a, b) Begin X <= a and b and c; End process; process • Synthesis software will issue an error stating that the process cannot be synthesized without a complete sensitivity list.

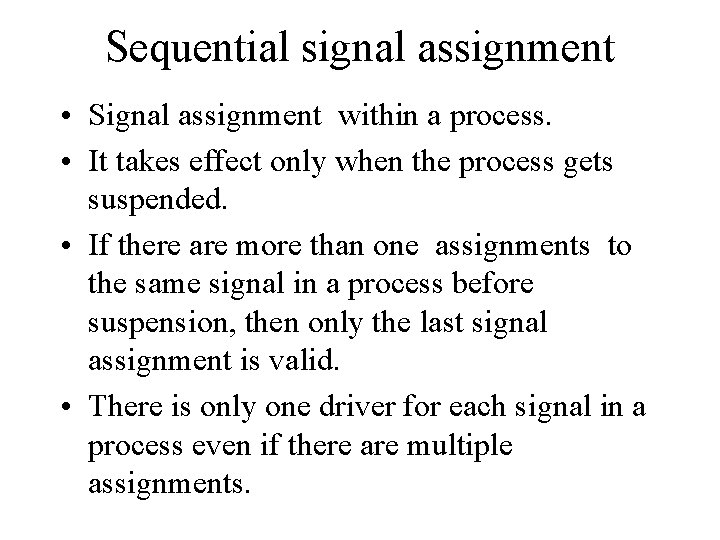

Sequential signal assignment • Signal assignment within a process. • It takes effect only when the process gets suspended. • If there are more than one assignments to the same signal in a process before suspension, then only the last signal assignment is valid. • There is only one driver for each signal in a process even if there are multiple assignments.

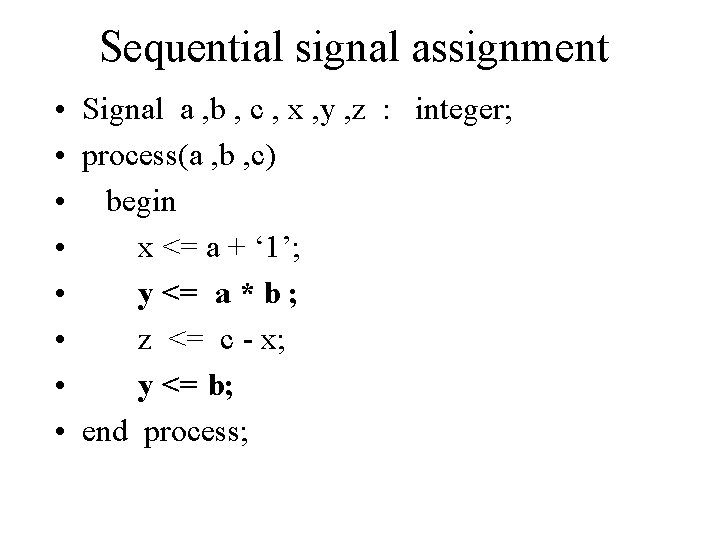

Sequential signal assignment • Signal a , b , c , x , y , z : integer; • process(a , b , c) • begin • x <= a + ‘ 1’; • y <= a * b ; • z <= c - x; • y <= b; • end process;

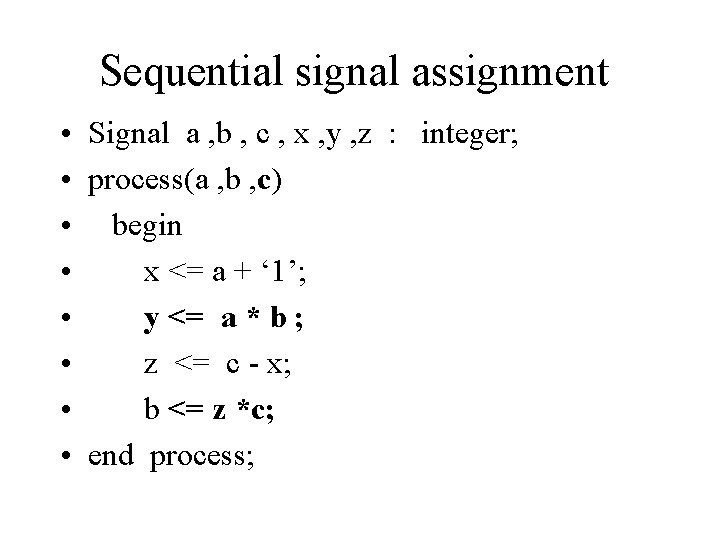

Sequential signal assignment • Signal a , b , c , x , y , z : integer; • process(a , b , c) • begin • x <= a + ‘ 1’; • y <= a * b ; • z <= c - x; • b <= z *c; • end process;

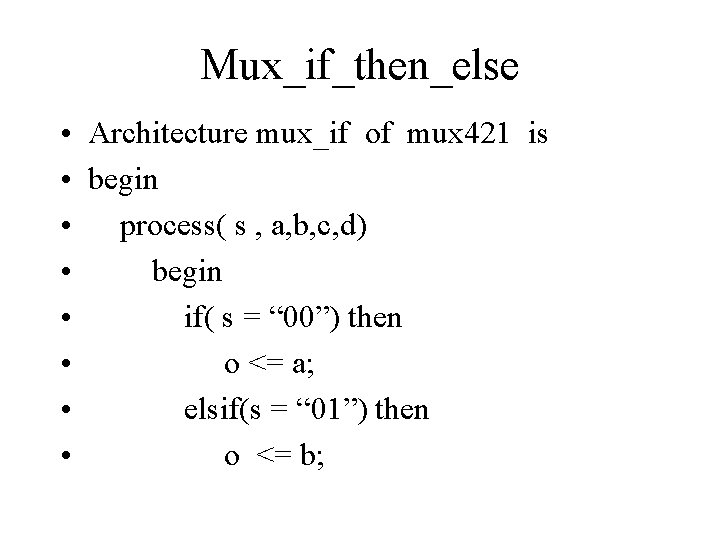

Mux_if_then_else • Architecture mux_if of mux 421 is • begin • process( s , a, b, c, d) • begin • if( s = “ 00”) then • o <= a; • elsif(s = “ 01”) then • o <= b;

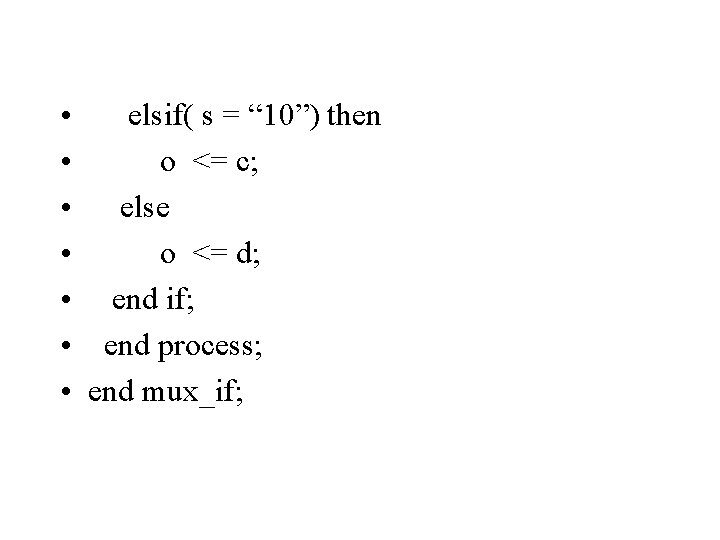

• elsif( s = “ 10”) then • o <= c; • else • o <= d; • end if; • end process; • end mux_if;

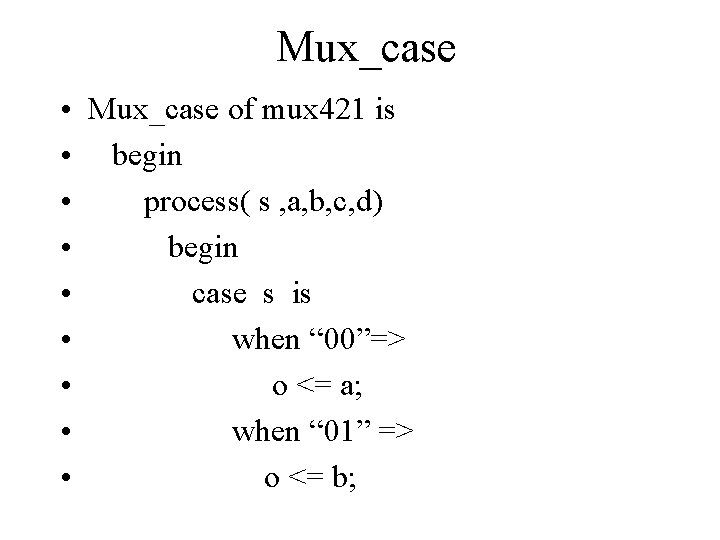

Mux_case • Mux_case of mux 421 is • begin • process( s , a, b, c, d) • begin • case s is • when “ 00”=> • o <= a; • when “ 01” => • o <= b;

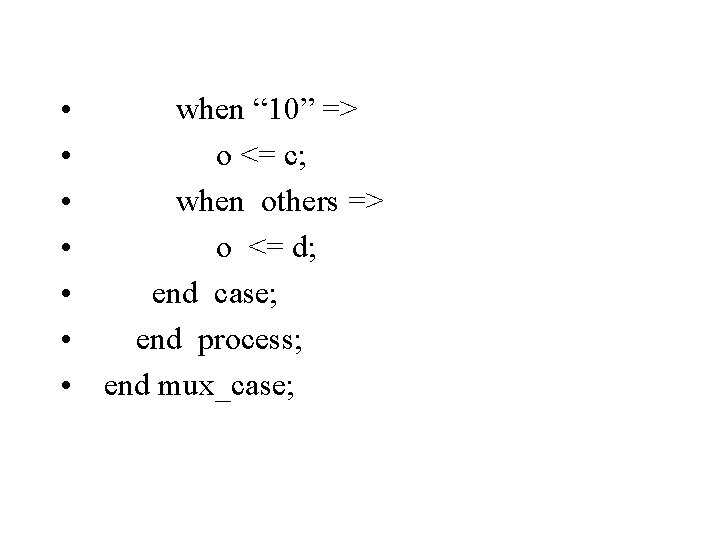

• when “ 10” => • o <= c; • when others => • o <= d; • end case; • end process; • end mux_case;

GENERATE statements • A mechanism for iterative or conditional elaboration of a design. • It is used to specify a group of identical components.

Syntax • Label : for parameter in range generate • [ { declarations} • begin] • { concurrent statements} • end generate [label];

![Syntax • Label : if condition generate • [ { declarations} • begin] • Syntax • Label : if condition generate • [ { declarations} • begin] •](http://slidetodoc.com/presentation_image_h2/ae7430f774f425bd70d57e183b8ae82e/image-41.jpg)

Syntax • Label : if condition generate • [ { declarations} • begin] • { concurrent statements} • end generate [label];

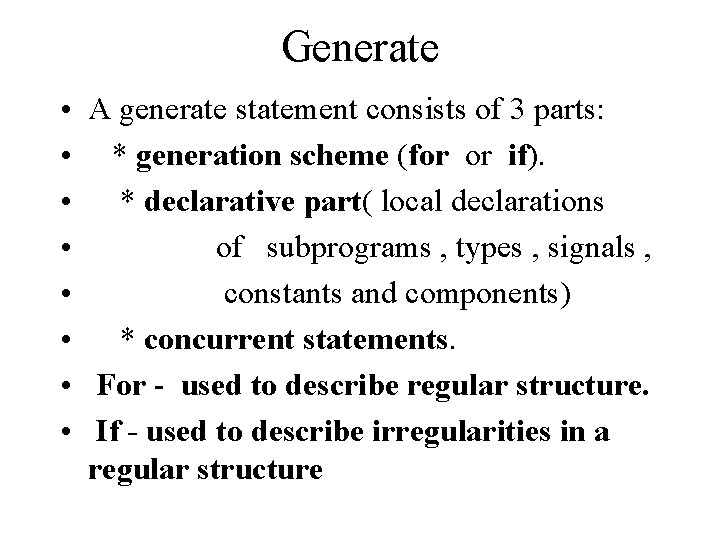

Generate • A generate statement consists of 3 parts: • * generation scheme (for or if). • * declarative part( local declarations • of subprograms , types , signals , • constants and components) • * concurrent statements. • For - used to describe regular structure. • If - used to describe irregularities in a regular structure

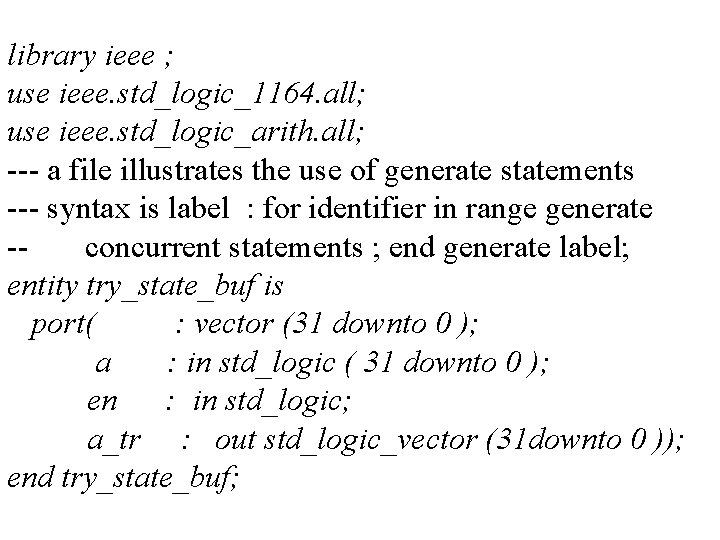

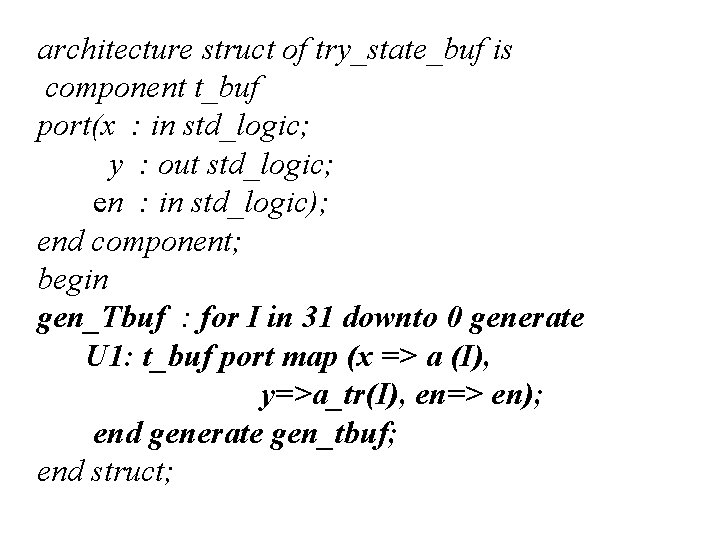

library ieee ; use ieee. std_logic_1164. all; use ieee. std_logic_arith. all; --- a file illustrates the use of generate statements --- syntax is label : for identifier in range generate -concurrent statements ; end generate label; entity try_state_buf is port( : vector (31 downto 0 ); a : in std_logic ( 31 downto 0 ); en : in std_logic; a_tr : out std_logic_vector (31 downto 0 )); end try_state_buf;

architecture struct of try_state_buf is component t_buf port(x : in std_logic; y : out std_logic; en : in std_logic); end component; begin gen_Tbuf : for I in 31 downto 0 generate U 1: t_buf port map (x => a (I), y=>a_tr(I), en=> en); end generate gen_tbuf; end struct;

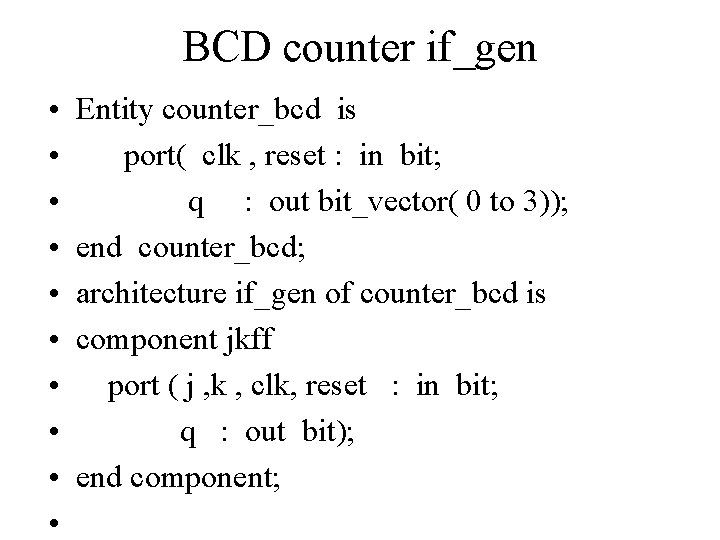

BCD counter if_gen • • • Entity counter_bcd is port( clk , reset : in bit; q : out bit_vector( 0 to 3)); end counter_bcd; architecture if_gen of counter_bcd is component jkff port ( j , k , clk, reset : in bit; q : out bit); end component;

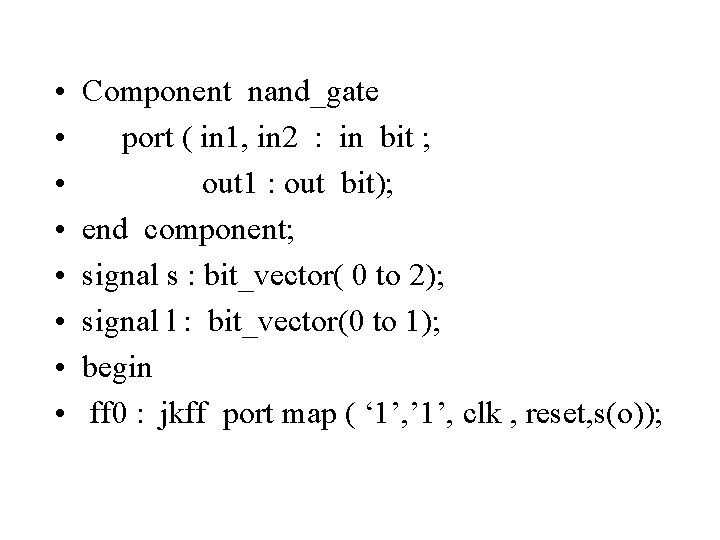

• • Component nand_gate port ( in 1, in 2 : in bit ; out 1 : out bit); end component; signal s : bit_vector( 0 to 2); signal l : bit_vector(0 to 1); begin ff 0 : jkff port map ( ‘ 1’, ’ 1’, clk , reset, s(o));

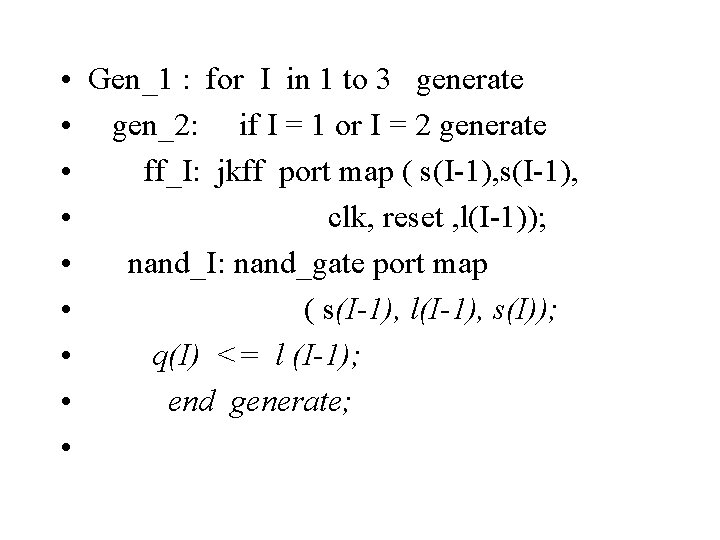

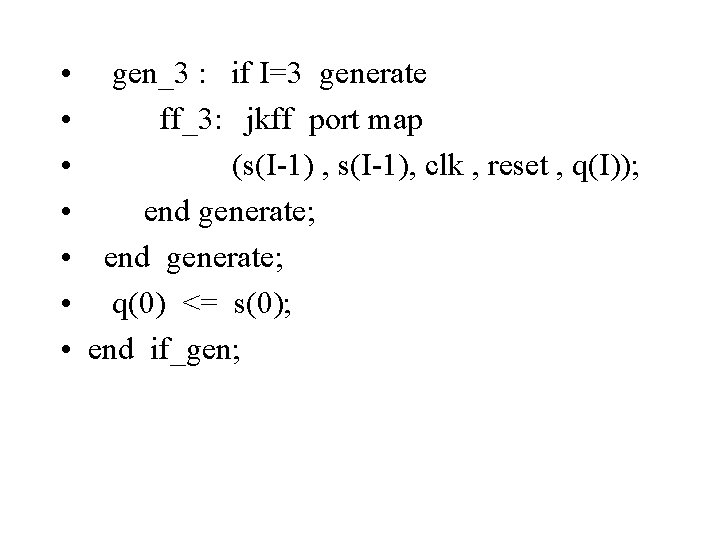

• Gen_1 : for I in 1 to 3 generate • gen_2: if I = 1 or I = 2 generate • ff_I: jkff port map ( s(I-1), • clk, reset , l(I-1)); • nand_I: nand_gate port map • ( s(I-1), l(I-1), s(I)); • q(I) <= l (I-1); • end generate; •

• gen_3 : if I=3 generate • ff_3: jkff port map • (s(I-1) , s(I-1), clk , reset , q(I)); • end generate; • q(0) <= s(0); • end if_gen;

ASSSERT statement • A statement that checks whether a specified condition is TRUE and reports an error if not. • Assert condition • report string • severity_level;

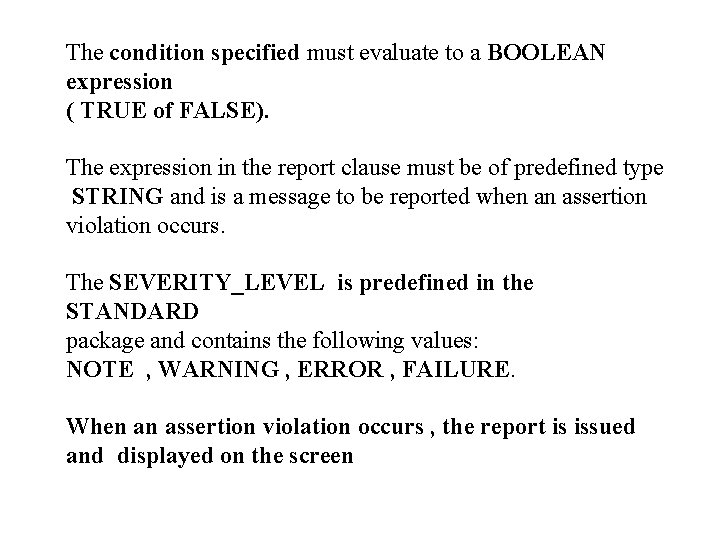

The condition specified must evaluate to a BOOLEAN expression ( TRUE of FALSE). The expression in the report clause must be of predefined type STRING and is a message to be reported when an assertion violation occurs. The SEVERITY_LEVEL is predefined in the STANDARD package and contains the following values: NOTE , WARNING , ERROR , FAILURE. When an assertion violation occurs , the report is issued and displayed on the screen

• Assert not ( s = ‘ 1’ and r = ‘ 1’) • report” both values of s and r are • equal to ‘ 1’”; • severity error;

Assertion Statement • A statement that checks that a specified condition is TRUE and reports an error if it is not. • Syntax • assert condition • report string • severity_level

Assert statement • Has three optional field • The condition must evaluate to a Boolean Value( TRUE or FALSE). • If it is false an assertion violation has occurred. • The expression specified in the report clause must be of predefined type STRING and is the message to be reported when assertion violation occurred.

Assert statement • The Severity_level type is specified in the STANDARD package. It contains four values: • NOTE • WARNING • ERROR • FAILURE

Assert Statements • Assert statements are not only sequential but can also be concurrent. • A concurrent Assert statement represents a passive process statement containing the specified assertion statement

Assert Statements • Assert not ( S = ‘ 1’ and R = ‘ 1’ ) • report “ Both values of signals S and R equal to ‘ 1’ ” • Severity ERROR; • When the values of Signals S and R are Equal to ‘ 1’, the message is displayed on the screen and the simulation is stopped

Assert Statement • Assert Opcode = “ 0000” • Report “ illegal code of operation” • Severity FAILURE;

Assert statements • The message is displayed when the condition is not met. • The message should be opposite to the condition. • Concurrent assert statements is a passive process and can be specified in an entity. • Synthesis tools generally Asseretion statements

- Slides: 60