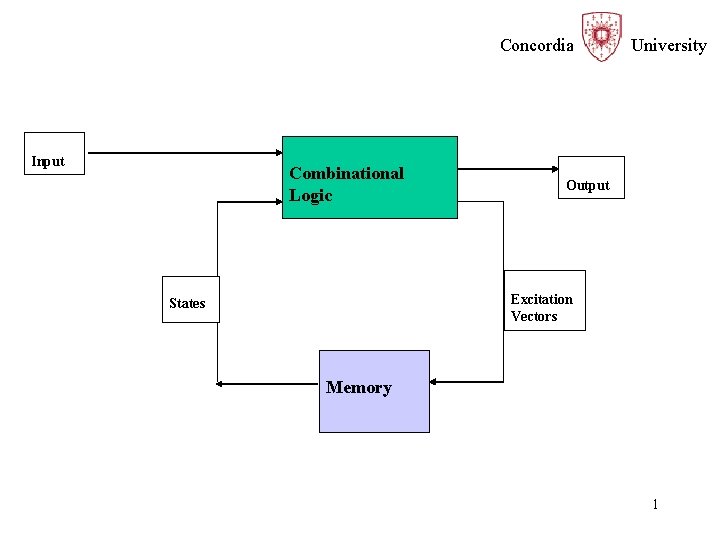

Concordia Input Combinational Logic University Output Excitation Vectors

Concordia Input Combinational Logic University Output Excitation Vectors States Memory 1

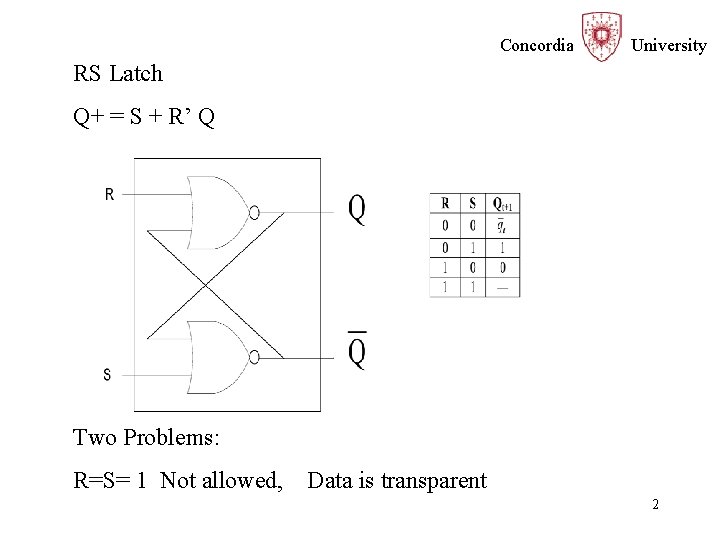

Concordia University RS Latch Q+ = S + R’ Q Two Problems: R=S= 1 Not allowed, Data is transparent 2

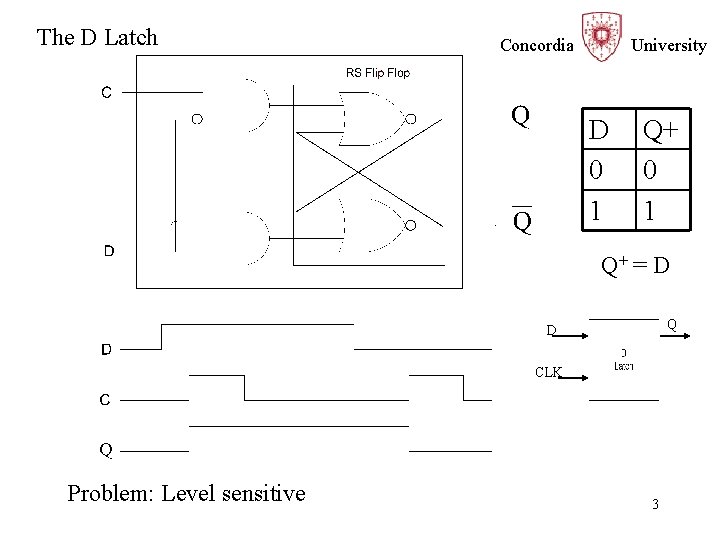

The D Latch Concordia University D 0 1 Q+ = D Q D CLK Problem: Level sensitive 3

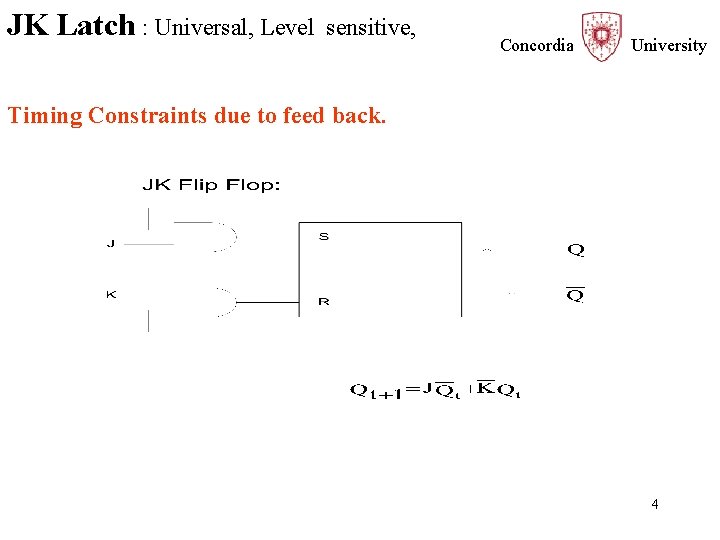

JK Latch : Universal, Level sensitive, Concordia University Timing Constraints due to feed back. 4

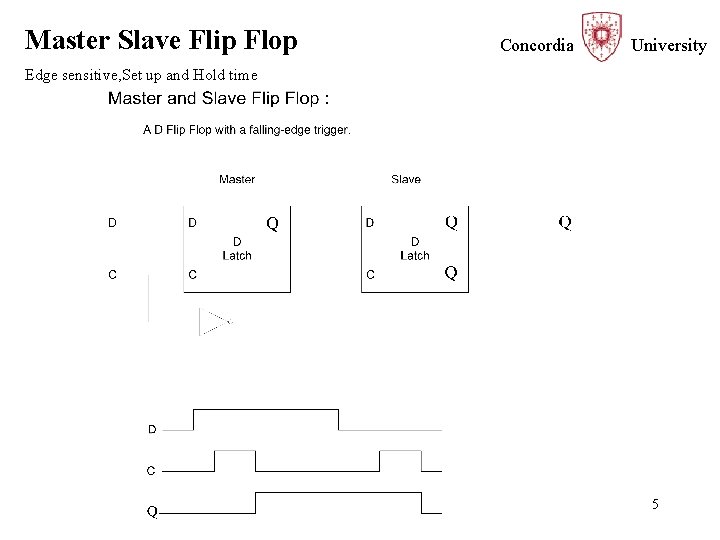

Master Slave Flip Flop Concordia University Edge sensitive, Set up and Hold time 5

Master Slave Flip Flop Edge sensitive, -Falling Edge Concordia Set Up and Hold Time constraints University Path to setup data Master D Slave Q D D Latch C C Q D Latch C Q Path to hold data D C 6 Q

Edge triggered Flip Flop: Concordia University Set up and Hold time Constraints 7

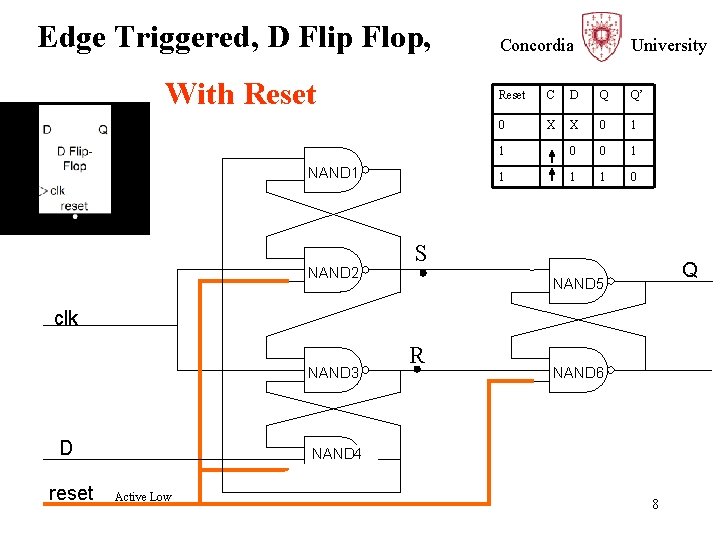

Edge Triggered, D Flip Flop, With Reset NAND 1 NAND 2 Concordia University Reset C D Q Q’ 0 X X 0 1 1 0 S Q NAND 5 clk NAND 3 D reset R NAND 6 NAND 4 Active Low 8

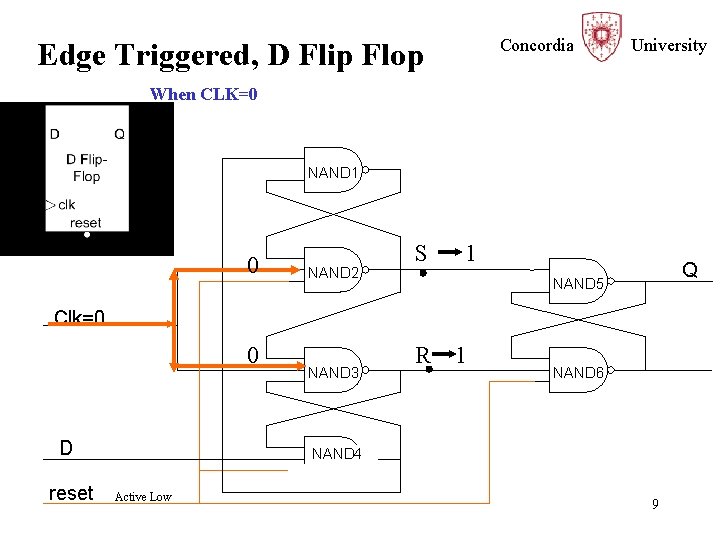

Concordia Edge Triggered, D Flip Flop University When CLK=0 NAND 1 0 NAND 2 S 1 Q NAND 5 Clk=0 0 D reset NAND 3 R 1 NAND 6 NAND 4 Active Low 9

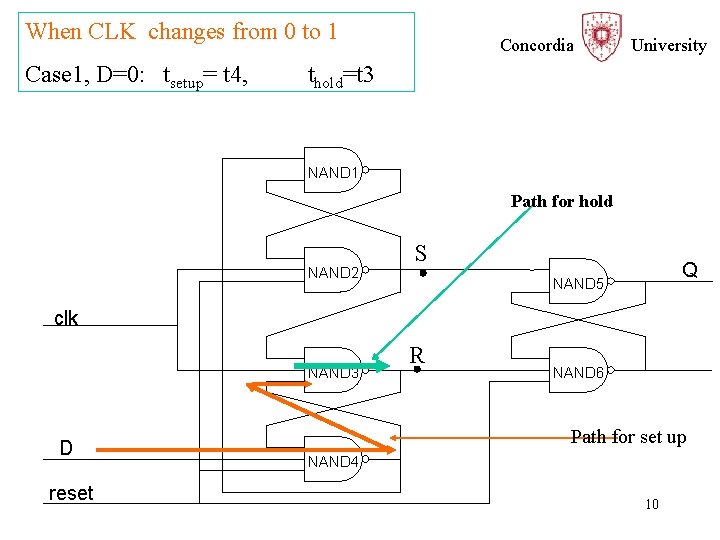

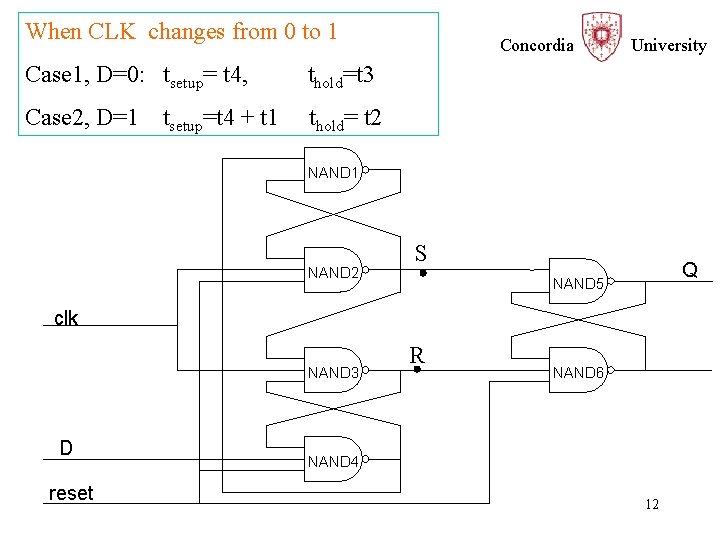

When CLK changes from 0 to 1 Case 1, D=0: tsetup= t 4, Concordia University thold=t 3 NAND 1 Path for hold NAND 2 S Q NAND 5 clk NAND 3 D reset R NAND 6 Path for set up NAND 4 10

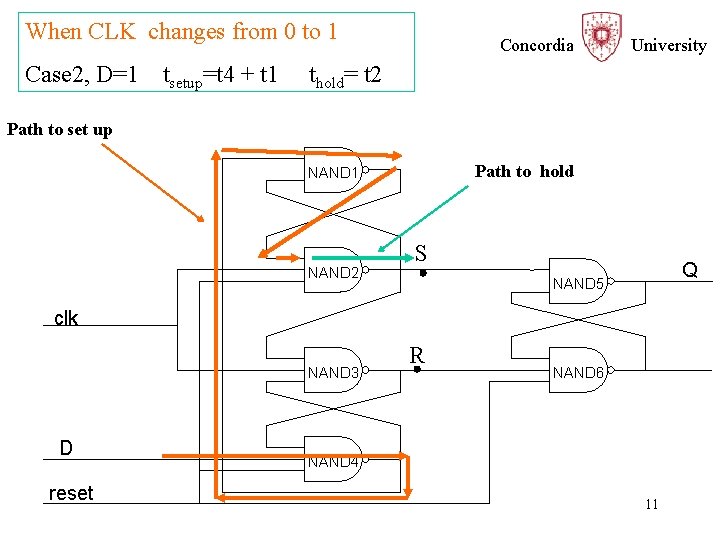

When CLK changes from 0 to 1 Case 2, D=1 tsetup=t 4 + t 1 Concordia University thold= t 2 Path to set up Path to hold NAND 1 NAND 2 S Q NAND 5 clk NAND 3 D reset R NAND 6 NAND 4 11

When CLK changes from 0 to 1 Case 1, D=0: tsetup= t 4, thold=t 3 Case 2, D=1 thold= t 2 tsetup=t 4 + t 1 Concordia University NAND 1 NAND 2 S Q NAND 5 clk NAND 3 D reset R NAND 6 NAND 4 12

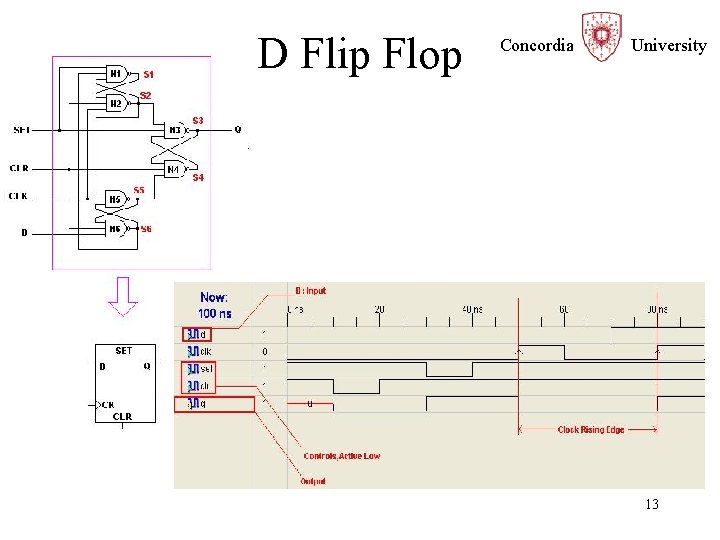

D Flip Flop Concordia University 13

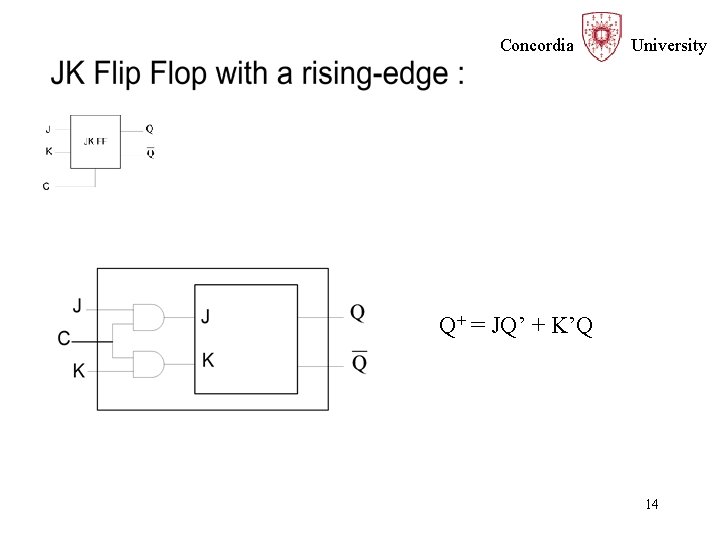

Concordia University Q+ = JQ’ + K’Q 14

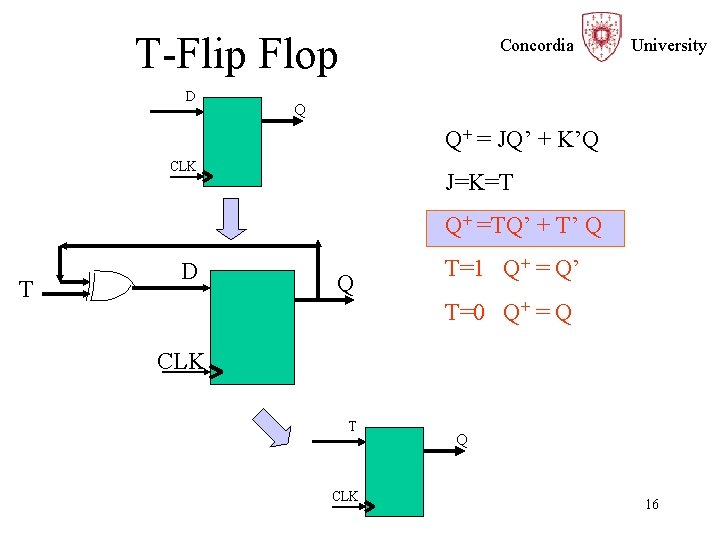

T-Flip Flop Concordia University Q+ = JQ’ + K’Q J=K=T Q+ =TQ’ + T’ Q T J Q K T=1 Q+ = Q’ T=0 Q+ = Q CLK T CLK Q 15

T-Flip Flop D Concordia University Q Q+ = JQ’ + K’Q CLK J=K=T Q+ =TQ’ + T’ Q T D Q T=1 Q+ = Q’ T=0 Q+ = Q CLK T CLK Q 16

- Slides: 16