Conception des circuits CMOS analogiques Conception transmetteur de

- Slides: 10

Conception des circuits CMOS analogiques Conception transmetteur de puissance sans fil entièrement intégré Alexandre Boyer alexandre. boyer@insa-toulouse. fr www. alexandre-boyer. fr 2015 -2016 135 avenue de Rangueil – 31077 Toulouse cedex 4 – Tel : 05. 61. 55. 95. 13 – Fax : 05. 61. 55. 95. 00 - www. insa-toulouse. fr

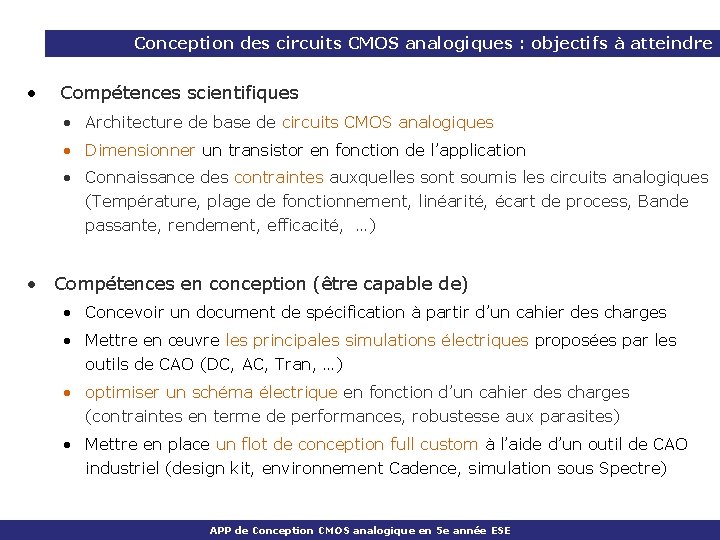

Conception des circuits CMOS analogiques : objectifs à atteindre • Compétences scientifiques • Architecture de base de circuits CMOS analogiques • Dimensionner un transistor en fonction de l’application • Connaissance des contraintes auxquelles sont soumis les circuits analogiques (Température, plage de fonctionnement, linéarité, écart de process, Bande passante, rendement, efficacité, …) • Compétences en conception (être capable de) • Concevoir un document de spécification à partir d’un cahier des charges • Mettre en œuvre les principales simulations électriques proposées par les outils de CAO (DC, AC, Tran, …) • optimiser un schéma électrique en fonction d’un cahier des charges (contraintes en terme de performances, robustesse aux parasites) • Mettre en place un flot de conception full custom à l’aide d’un outil de CAO industriel (design kit, environnement Cadence, simulation sous Spectre) APP de Conception CMOS analogique en 5 e année ESE

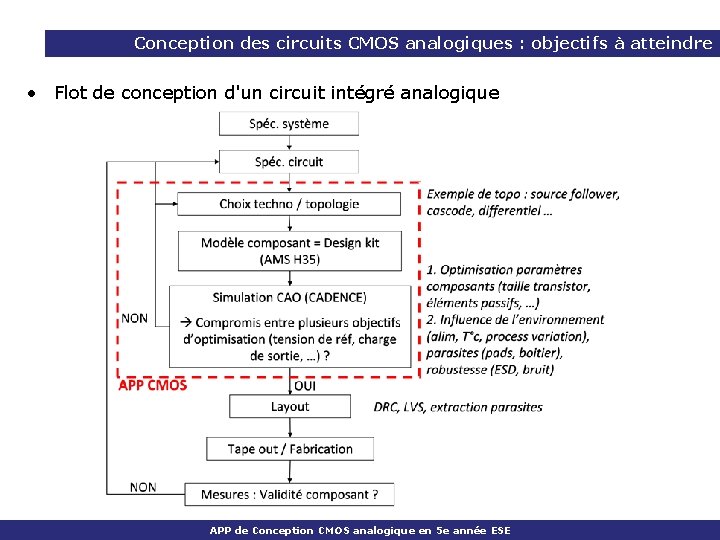

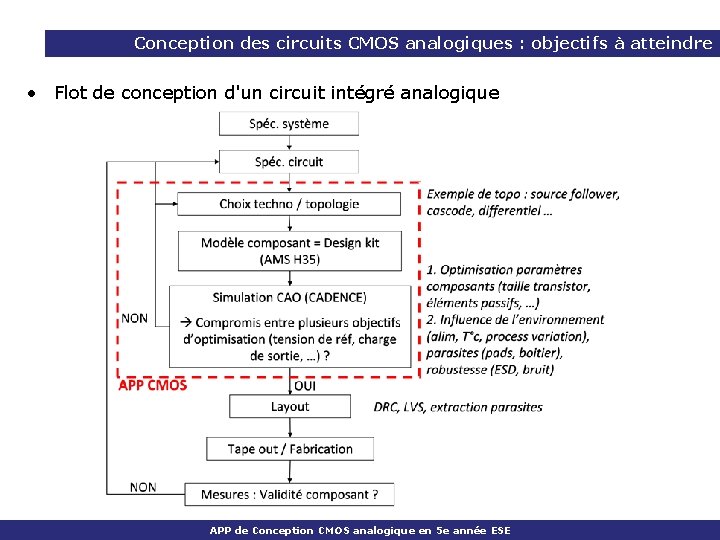

Conception des circuits CMOS analogiques : objectifs à atteindre • Flot de conception d'un circuit intégré analogique APP de Conception CMOS analogique en 5 e année ESE

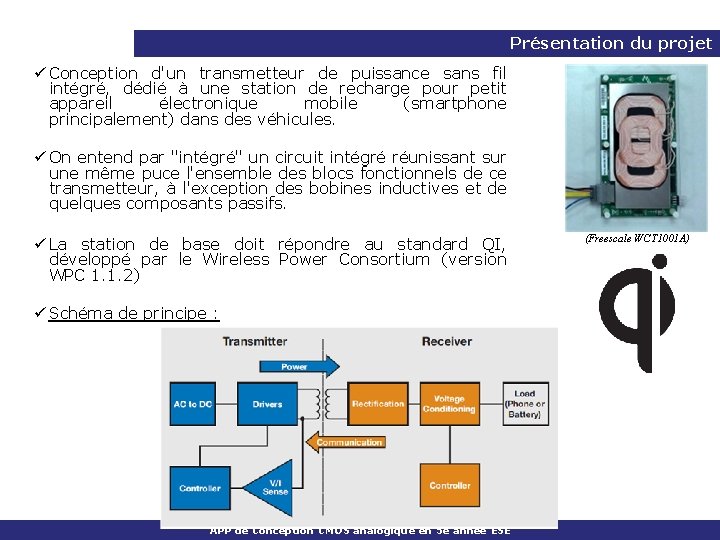

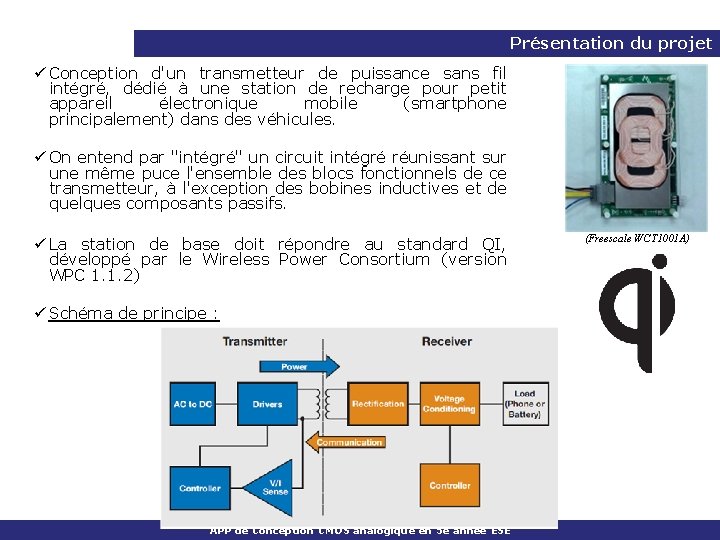

Présentation du projet ü Conception d'un transmetteur de puissance sans fil intégré, dédié à une station de recharge pour petit appareil électronique mobile (smartphone principalement) dans des véhicules. ü On entend par "intégré" un circuit intégré réunissant sur une même puce l'ensemble des blocs fonctionnels de ce transmetteur, à l'exception des bobines inductives et de quelques composants passifs. ü La station de base doit répondre au standard QI, développé par le Wireless Power Consortium (version WPC 1. 1. 2) ü Schéma de principe : APP de Conception CMOS analogique en 5 e année ESE (Freescale WCT 1001 A)

Présentation du projet üCahier des charges détaillé dans Sujet_APP_CMOS_analogique_2015 -16. pdf üTaches : 1. Fournir un rapport de spécifications détaillées du composant. Ce document devra être rédigé en anglais et suivre la trame qui vous est imposée (Specification_report_WPT_Gpe. X_2015. doc). 2. Proposer et optimiser une schématique du circuit sous CADENCE. A l’issue de cette étape, un rapport donnant les performances attendues du circuit sera délivré. Ce document devra être rédigé en anglais. APP de Conception CMOS analogique en 5 e année ESE

Support üLes documents suivants vous sont fournis pour vous aider à réaliser ce projet : ü Version électronique du livre : Gray, Hurst, Lewis, Meyer, "Analysis and Design of Analog Integrated Circuits - 5 th Edition" (en priorité les chapitres 4, 6, 7 et 9) ü QI Specifications, "System Description Wireless Power Transfer - Vol 1: Low Power - Part 1: Interface Definition - version 1. 1. 2", June 2013 ü ENG-238, "0. 35 µm 50 V CMOS Process Parameters - revision 6. 0", Austria Miko. Systems, 2009 ü ENG-298, "0. 35 µm 50 V CMOS Parasitic Devices - revision 3. 0", Austria Miko. Systems, 2014 ü ENG-314, "0. 35 µm HV ESD Design Rules - revision 2. 0", Austria Miko. Systems, 2010 ü ENG-236, "0. 35 µm LV ESD Design Rules - revision 2. 0", Austria Miko. Systems, 2010 ü CMOS design report - Aniba Benkhalfia de Reviers Saint-Martin. pdf : le rapport de conception d'un groupe d'étudiants de 2014 -2015. Le travail présente la conception d'une référence de tension badgap. ü Ceux-ci peuvent être téléchargés sur la page http: //www. alexandreboyer. fr/enseignements. htm. APP de Conception CMOS analogique en 5 e année ESE

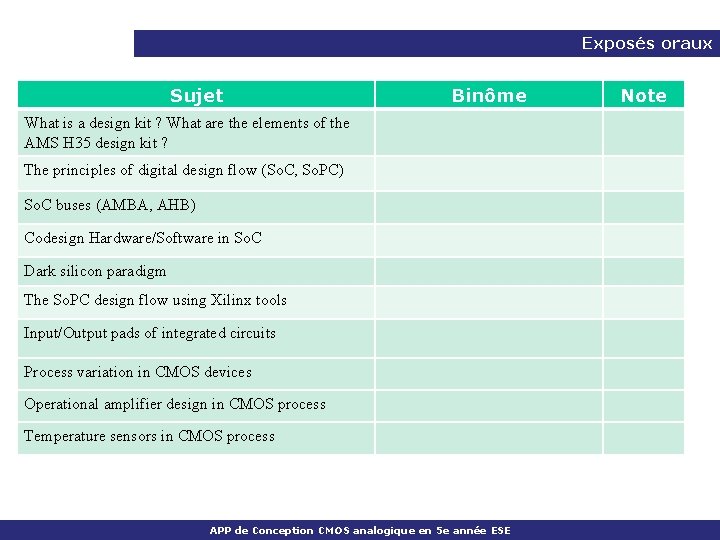

Evaluation • Auto-évaluation A mi parcours une séance de restructuration afin de résoudre les points bloquants et de répondre à vos questions • Evaluation (couplage avec l’enseignement d’anglais) • Exposé oral en binôme (sujets liés à la conception CMOS) • Evaluation du projet (doc de spécification, rapport de conception) • Exposé en groupe (conception finale) APP de Conception CMOS analogique en 5 e année ESE

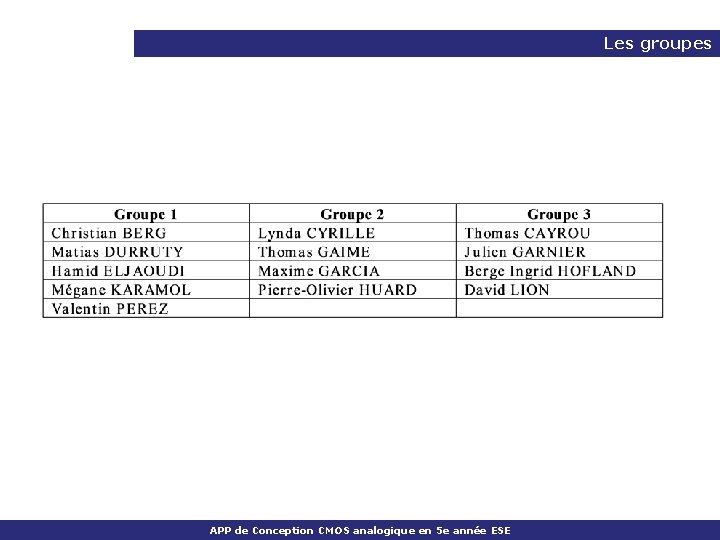

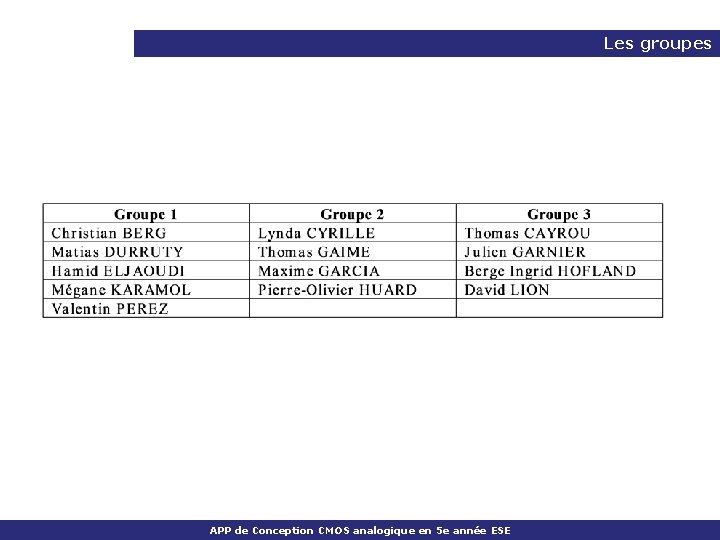

Les groupes APP de Conception CMOS analogique en 5 e année ESE

Déroulement APP de Conception CMOS analogique en 5 e année ESE

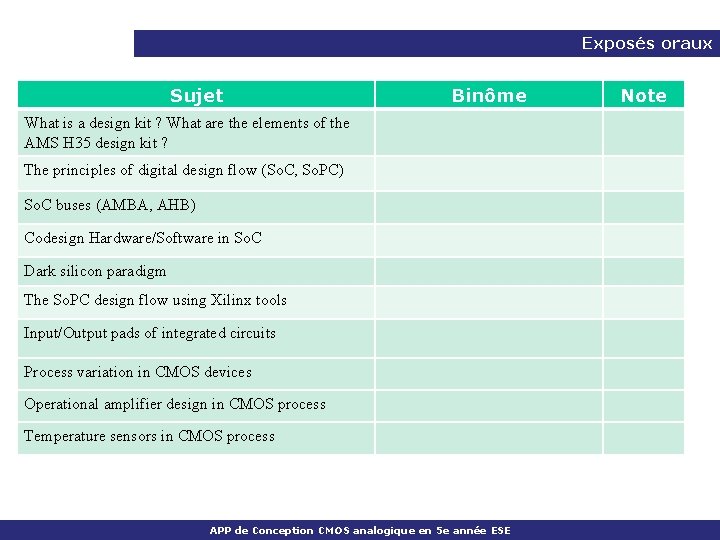

Exposés oraux Sujet Binôme What is a design kit ? What are the elements of the AMS H 35 design kit ? The principles of digital design flow (So. C, So. PC) So. C buses (AMBA, AHB) Codesign Hardware/Software in So. C Dark silicon paradigm The So. PC design flow using Xilinx tools Input/Output pads of integrated circuits Process variation in CMOS devices Operational amplifier design in CMOS process Temperature sensors in CMOS process APP de Conception CMOS analogique en 5 e année ESE Note