Concentrator and Preprocessing Status Javier Collado Departamento de

- Slides: 9

Concentrator and Pre-processing Status Javier Collado Departamento de Ing. Electrónica. Universitat de València Instituto de Física Corpuscular. CSIC-UV AGATA Week 2018 – Strasbourg (France)

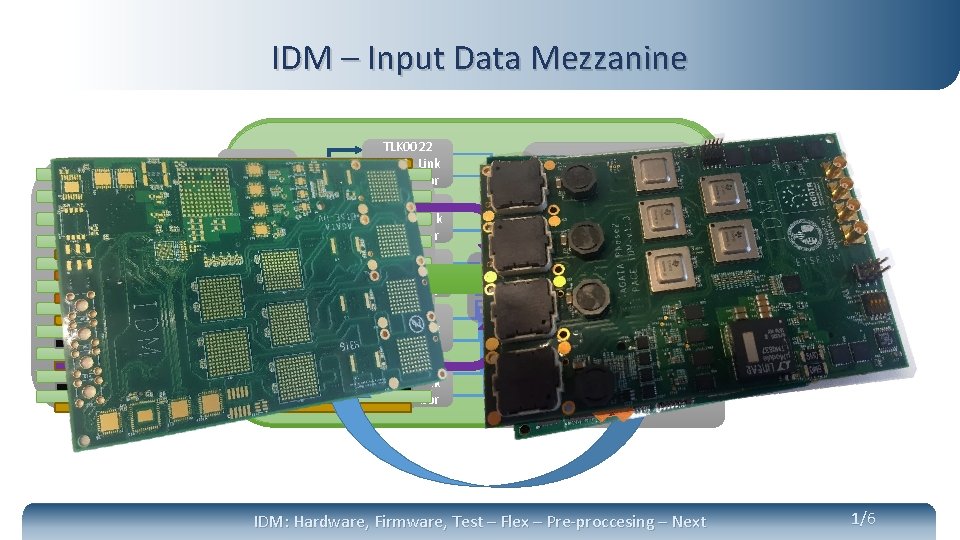

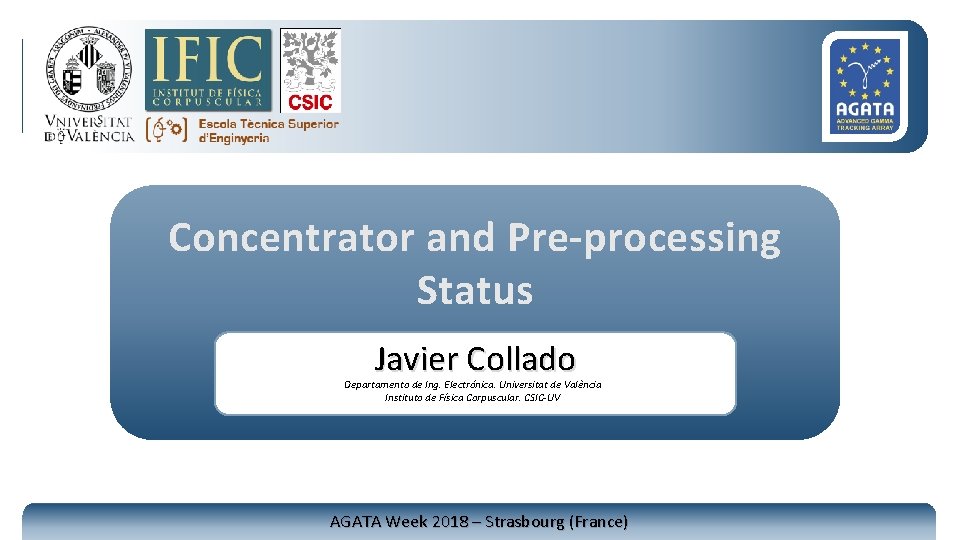

IDM – Input Data Mezzanine FPGA Control ICE 40 LP 8 k –CM 121 Low Power TLK 0022 2 x(4: 1) Link Aggregator TLK 0022 Input Data Mezzanine 2 x(4: 1) Link Aggregator (IDM-A 0)8 Gbps FMC-A 0 TOP Mini. POD GND High Speed Signals GND Mini. POD POWER Mini. POD Low Speed Signals GND High Speed Signals Mini. POD GND BOTTTOM TLK 0022 2 x(4: 1) Link Aggregator Power TLK 0022 2 x(4: 1) Link Aggregator FMC (HPC) SAMTEC SEARAY SEAM 400 pin 28+ Gbps IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next 1/6

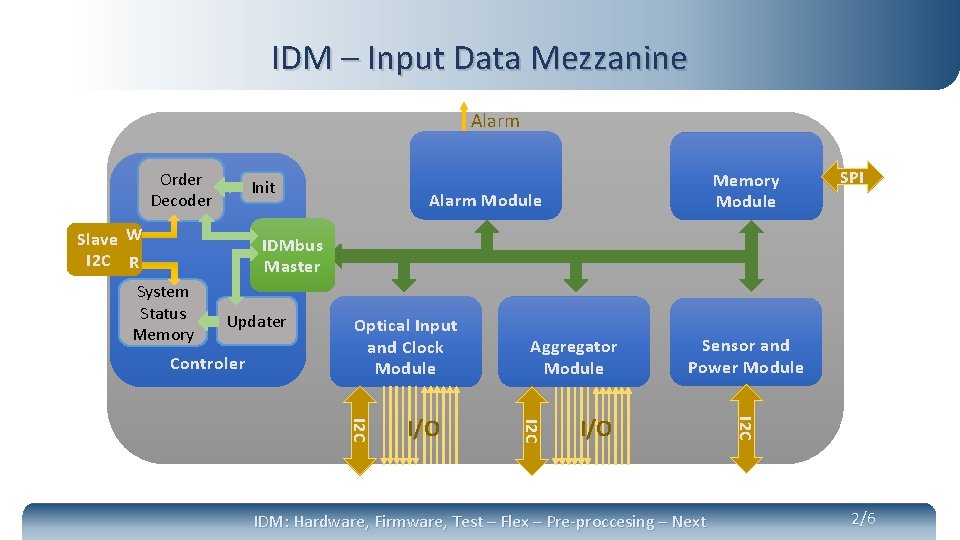

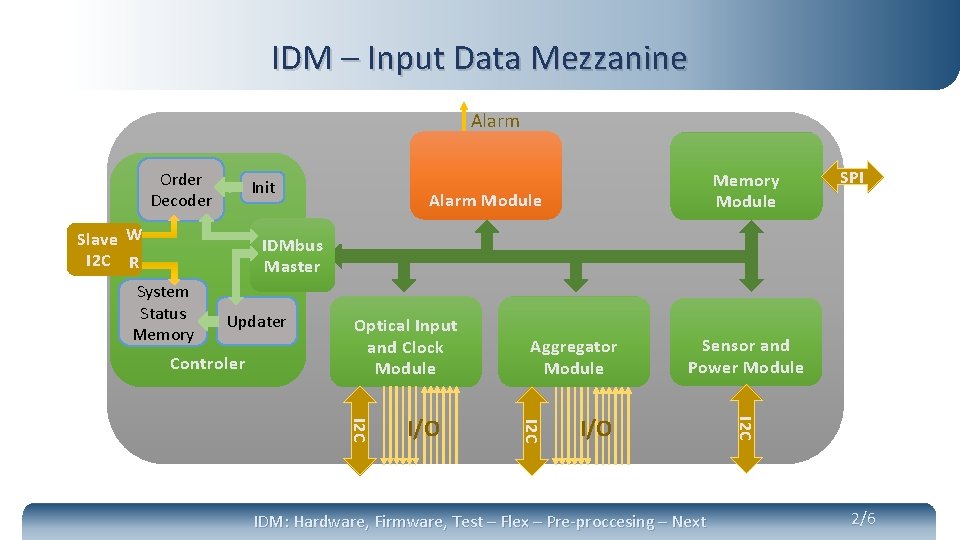

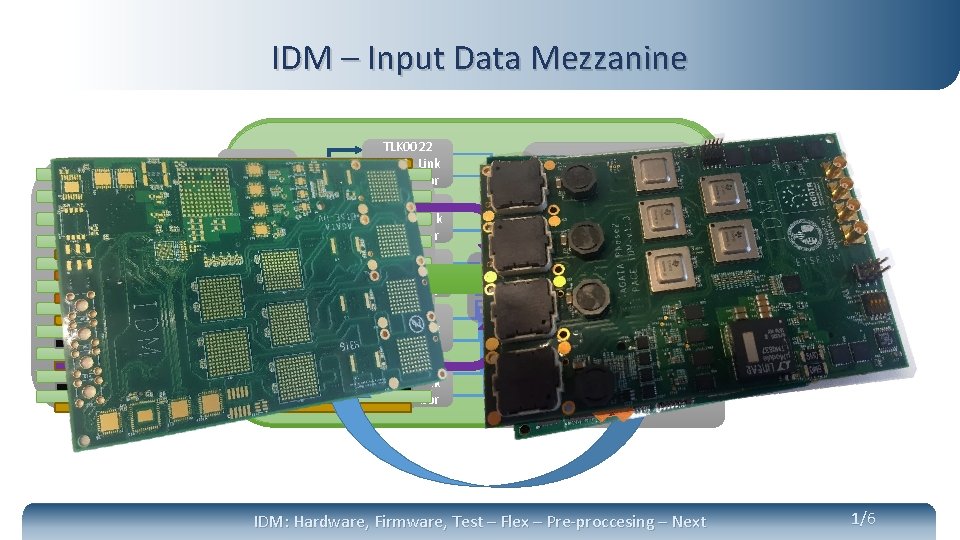

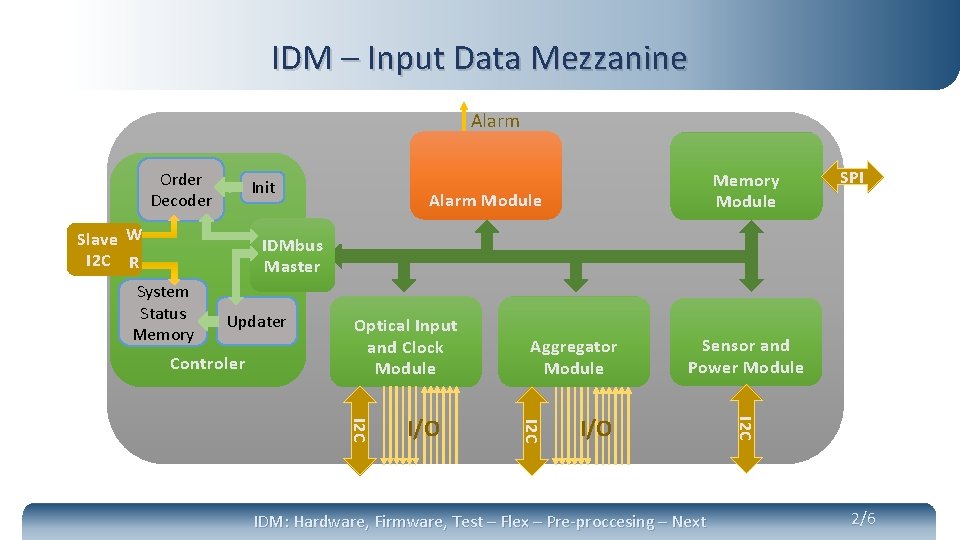

IDM – Input Data Mezzanine Alarm Order Decoder Init Slave W I 2 C R Memory Module Alarm Module SPI IDMbus Master System Status Memory Updater Controler Optical Input and Clock Module Sensor and Power Module I/O IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next I 2 C I/O Aggregator Module 2/6

IDM – Input Data Mezzanine Alarm Order Decoder Init Slave W I 2 C R Memory Module Alarm Module SPI IDMbus Master System Status Memory Updater Controler Optical Input and Clock Module Sensor and Power Module I/O IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next I 2 C I/O Aggregator Module 2/6

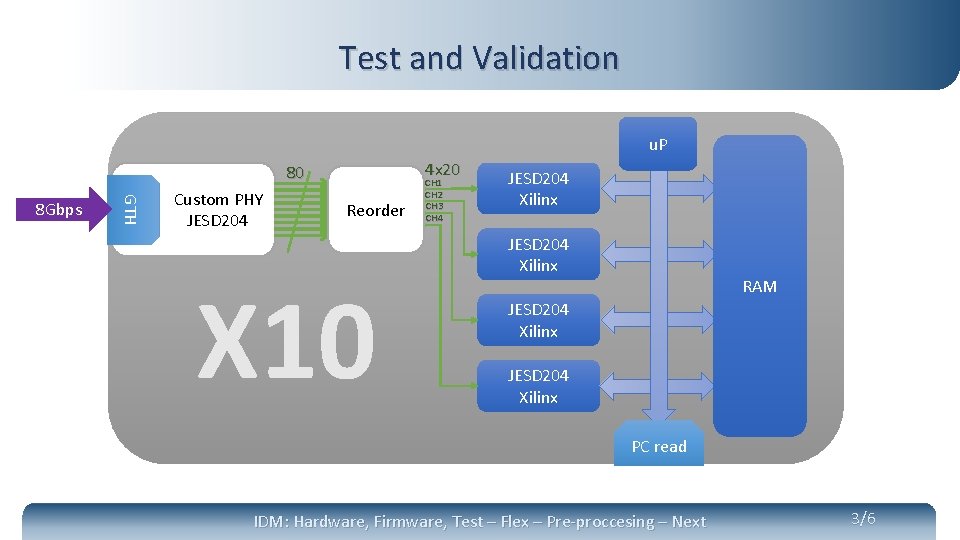

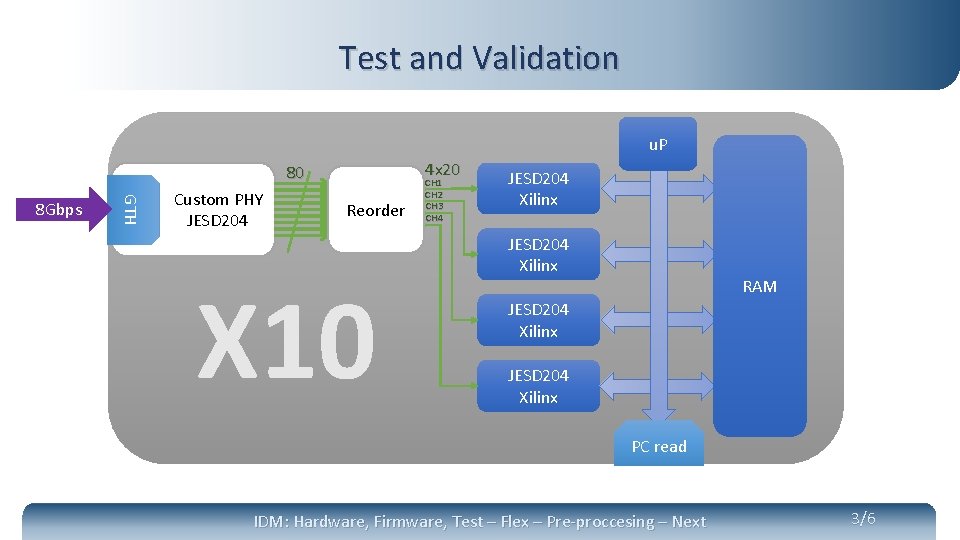

Test and Validation u. P 4 x 20 80 GTH 8 Gbps Custom PHY JESD 204 Reorder X 10 CH 1 CH 2 CH 3 CH 4 JESD 204 Xilinx RAM JESD 204 Xilinx PC read IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next 3/6

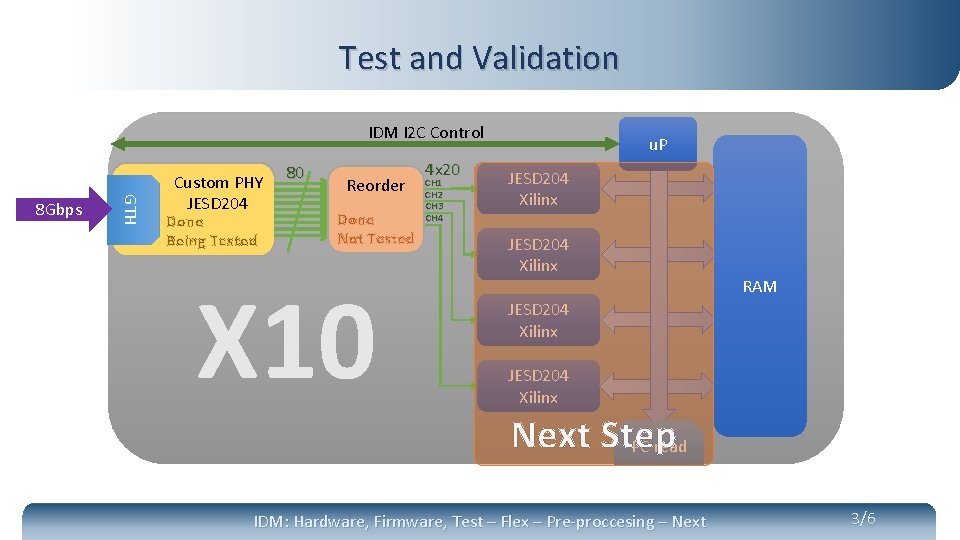

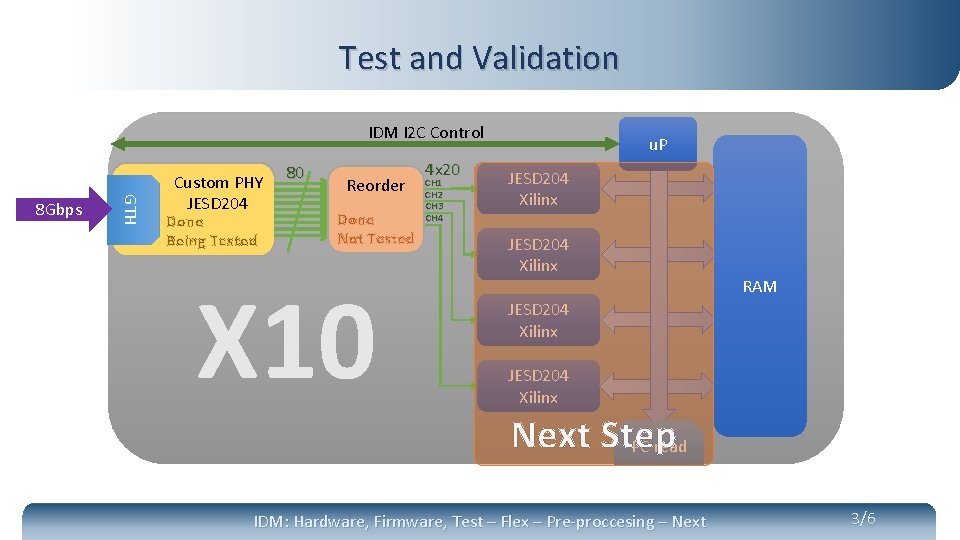

Test and Validation IDM I 2 C Control GTH 8 Gbps Custom PHY JESD 204 Done Being Tested 80 Reorder Done Not Tested X 10 4 x 20 CH 1 CH 2 CH 3 CH 4 u. P JESD 204 Xilinx RAM JESD 204 Xilinx Next Step PC read IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next 3/6

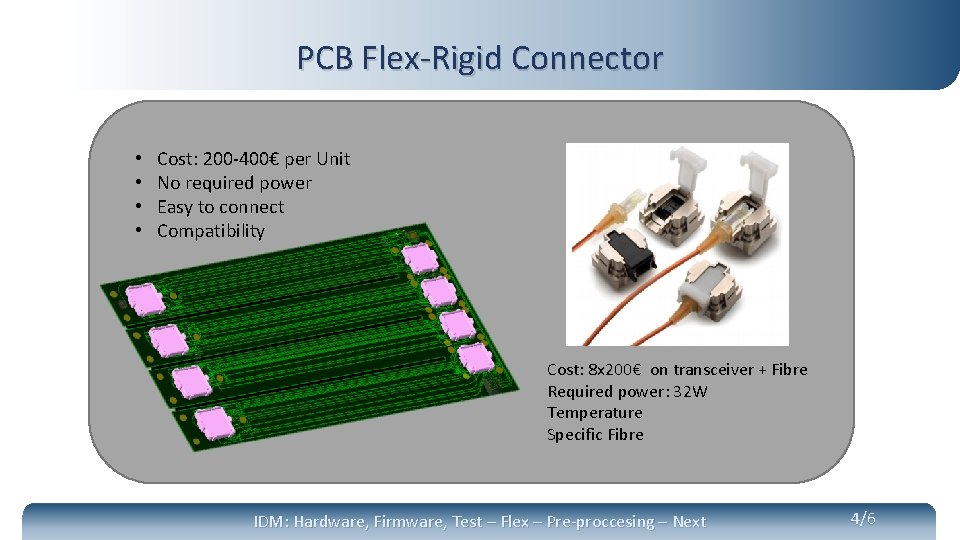

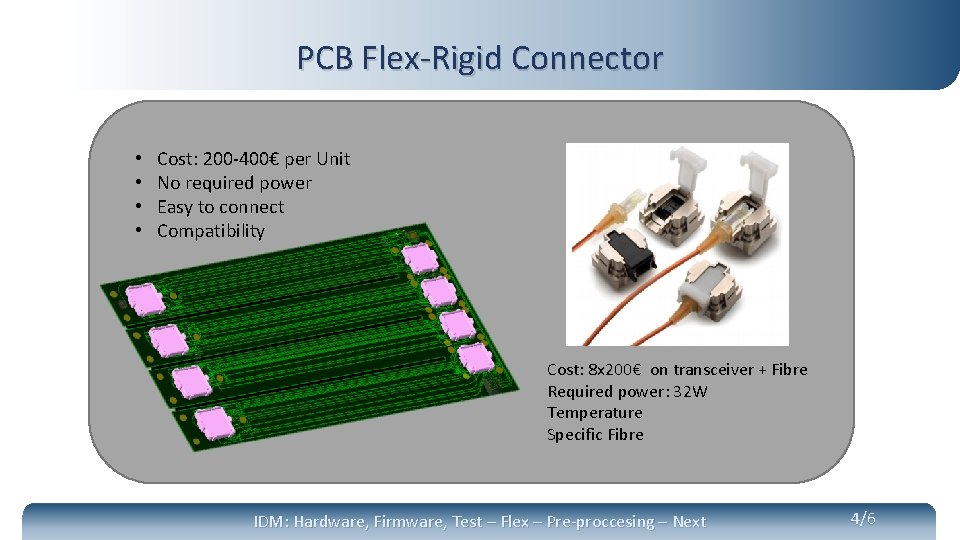

PCB Flex-Rigid Connector IDM I 2 C Control • • Cost: 200 -400€ per Unit. Flex No required power Rigid Easy to connect PCB Compatibility Cost: 8 x 200€ on transceiver + Fibre Required power: 32 W Temperature Specific Fibre IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next 4/6

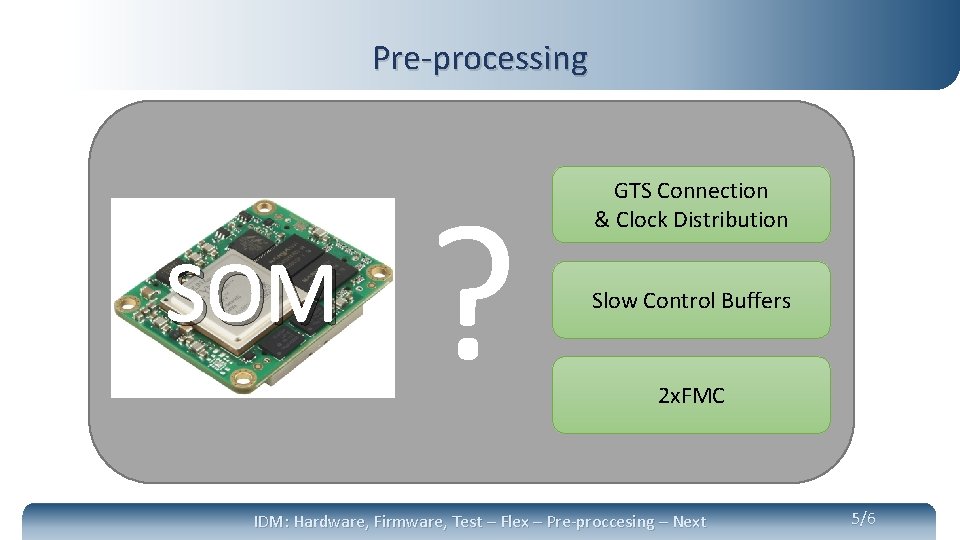

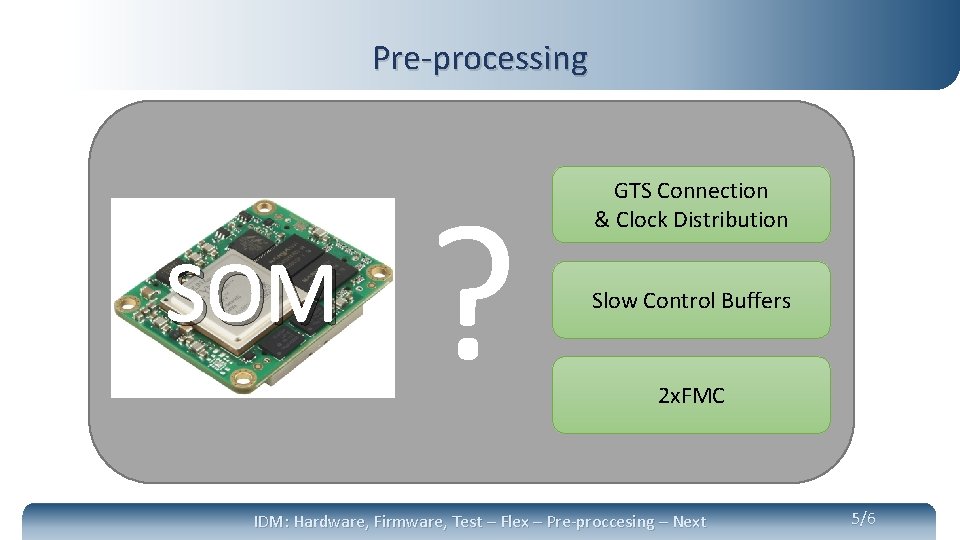

Pre-processing SOM ? GTS Connection & Clock Distribution Slow Control Buffers 2 x. FMC IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next 5/6

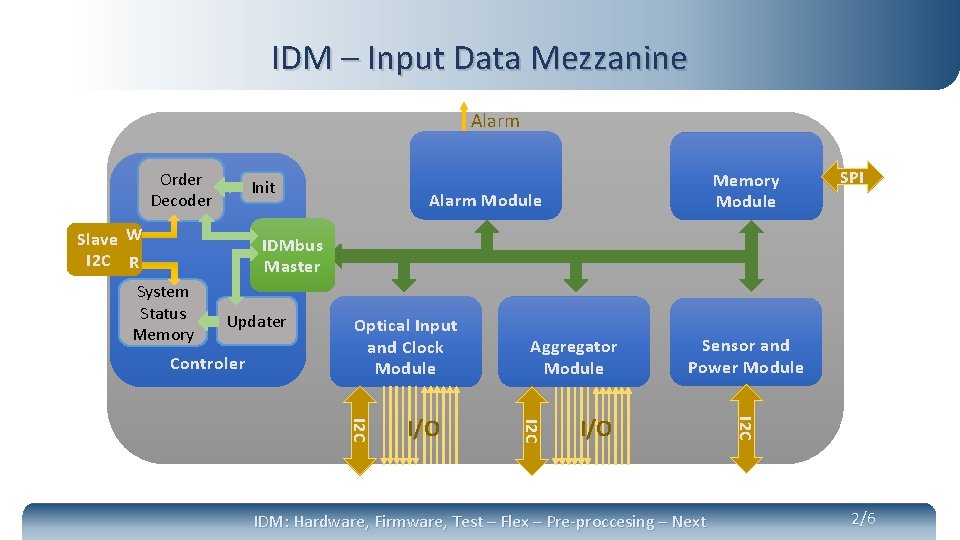

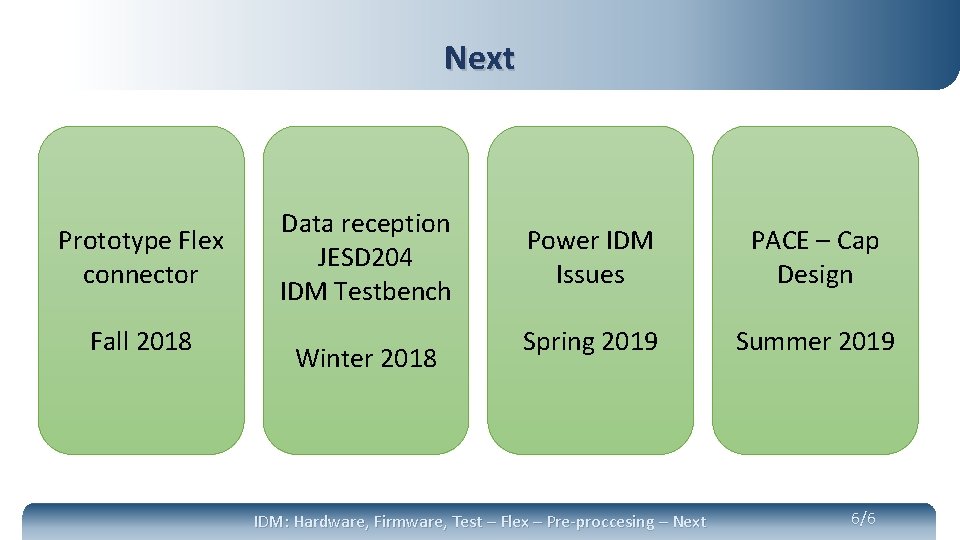

Next Prototype Flex connector Fall 2018 Data reception JESD 204 IDM Testbench Winter 2018 Power IDM Issues PACE – Cap Design Spring 2019 Summer 2019 IDM: Hardware, Firmware, Test – Flex – Pre-proccesing – Next 6/6