Computing Paths to the Future Roger Goff Dell

- Slides: 9

Computing Paths to the Future Roger Goff Dell Global CERN/LHC Technologist +1 970 672 1252 | Roger_Goff@dell. com

Computing System Trends • Processors –Multi-core -> Many core › In 2005, the first dual-core x 86 processors were released › In 2010, AMD released 12 -core x 86 processors • Increasing RAM capacity (larger DIMMs, not necessarily more DIMM slots) • Increasing RAM speed: 1333 Mhz -> 1600 MHz soon • Faster IO subsystems: PCIe Gen 2 -> PCIe Gen 3 • Faster interconnects: 10 Gb. E & 40 Gb IB -> 100 Gb soon • As core counts are growing, CPU clock speeds are slowing • Memory speeds not keeping up with HPC demands on large core count processors • Local disk speeds not keeping up 2 Dell CERN/LHC Program

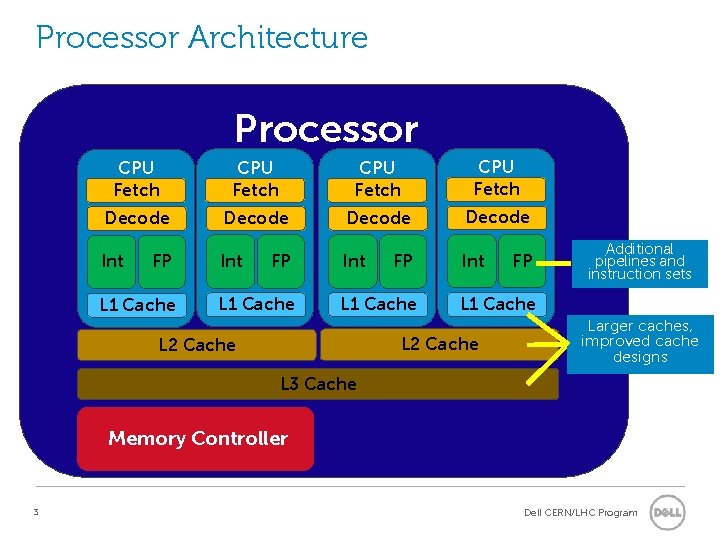

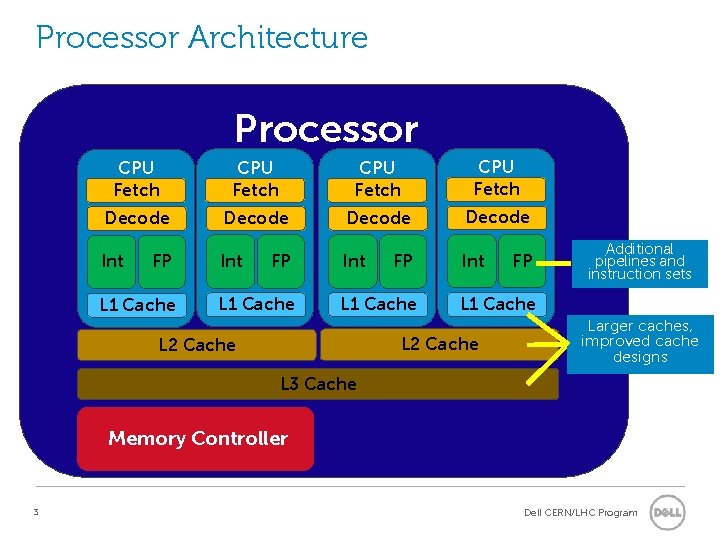

Processor Architecture Processor CPU Fetch Decode Int Int FP L 1 Cache Additional pipelines and instruction sets L 1 Cache L 2 Cache FP Larger caches, improved cache designs L 3 Cache Memory Controller 3 Dell CERN/LHC Program

Performance Improvement • Processor frequency boosts under low power situations • Intel Hyperthreading • SSDs • Application Parallelism is the key – Required to take advantage of the increasing CPU core counts – Co-processors are here to stay › GPU Computing (n. Vidia & AMD), MIC (Intel), Clearspeed, FPGAs – Lots of threads, lots of FLOPs, local memory › Challenges: – Can your application take advantage of them? Amdahl’s law is still the law! – What co-processors will survive? – How will we program them? – n. Vidia CUDA, Open. CL, Open. MP? • Balanced system performance is critical! – Understanding Byte: FLOP ratios for applications to optimize system performance and utilization › GB Memory: core, Memory BW: core, Disk BW: core, Network BW: core 4 Dell CERN/LHC Program

Natural Evolution of Processors Memory Controller 5 Dell CERN/LHC Program

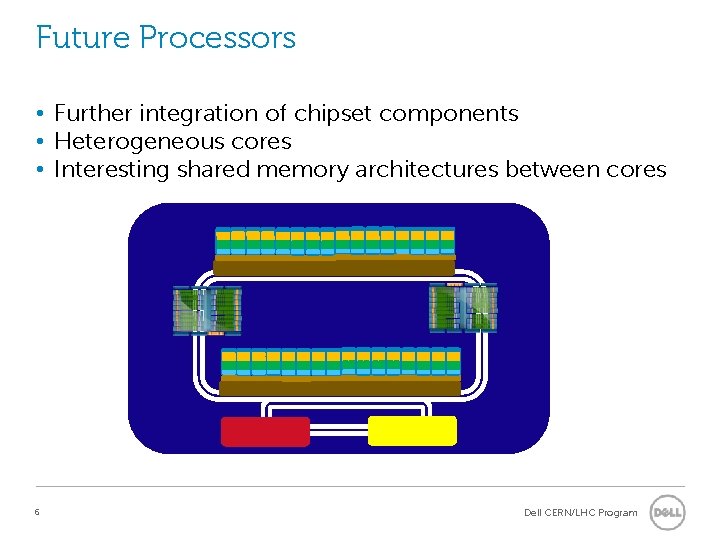

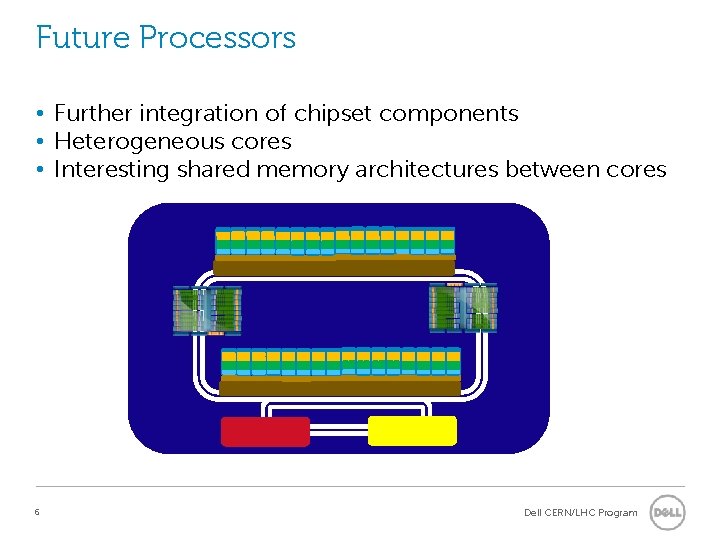

Future Processors • Further integration of chipset components • Heterogeneous cores • Interesting shared memory architectures between cores 6 Dell CERN/LHC Program

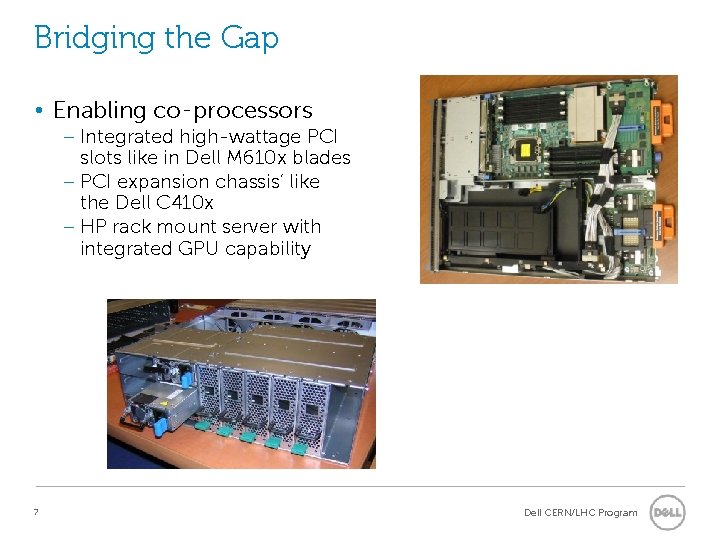

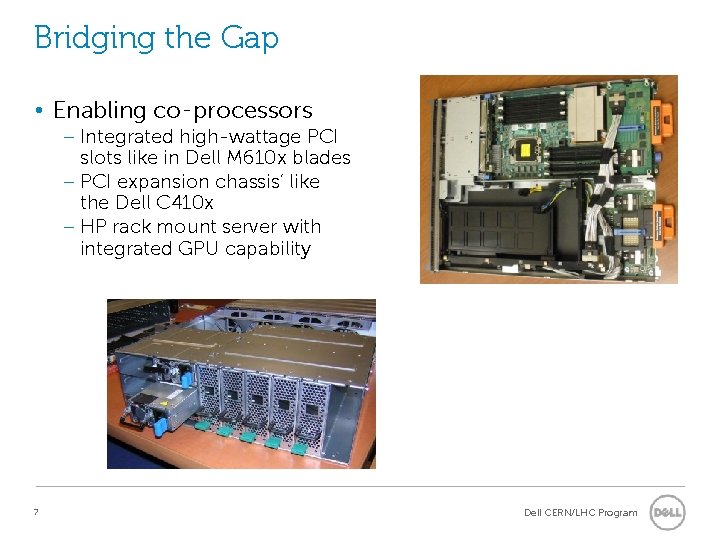

Bridging the Gap • Enabling co-processors – Integrated high-wattage PCI slots like in Dell M 610 x blades – PCI expansion chassis’ like the Dell C 410 x – HP rack mount server with integrated GPU capability 7 Dell CERN/LHC Program

Final Takeaways 1. 2. 3. 4. 8 CPU cores are not getting faster. Co-processors are here to stay. Heterogeneous processors are inevitable. Preparing applications for extreme parallelism will enable users to get the most out of future systems. Dell CERN/LHC Program

Thank you! Roger Goff Dell Global CERN/LHC Technologist +1 970 672 1252 | Roger_Goff@dell. com