Computers Central Processor Unit Basic Computer System Processor

Computers Central Processor Unit

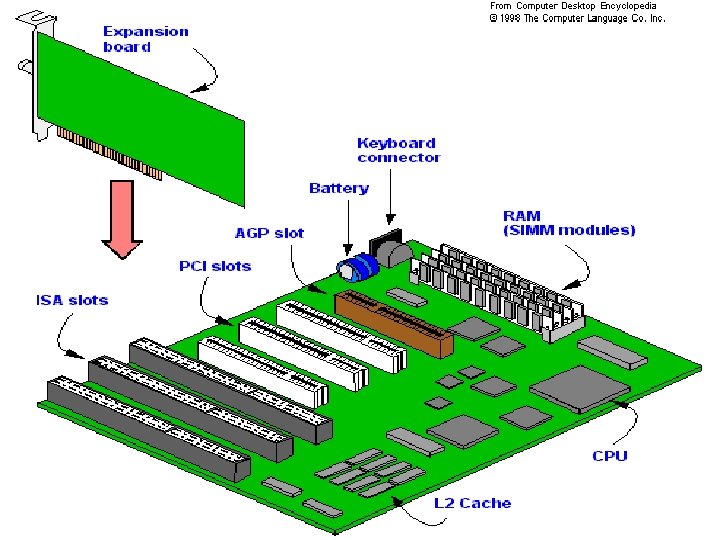

Basic Computer System Processor ALU CNTL. . . BUS Interconnections I/O module CONTROLLER MAIN MEMORY Memory BUS

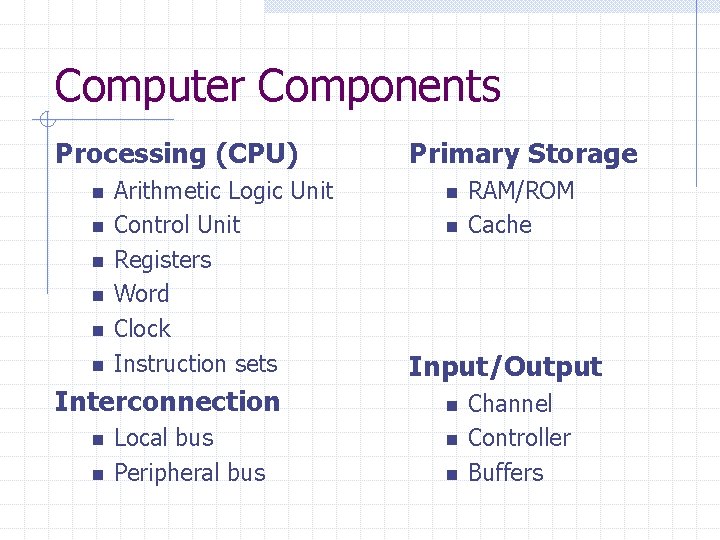

Computer Components Processing (CPU) n n n Arithmetic Logic Unit Control Unit Registers Word Clock Instruction sets Interconnection n n Local bus Peripheral bus Primary Storage n n RAM/ROM Cache Input/Output n n n Channel Controller Buffers

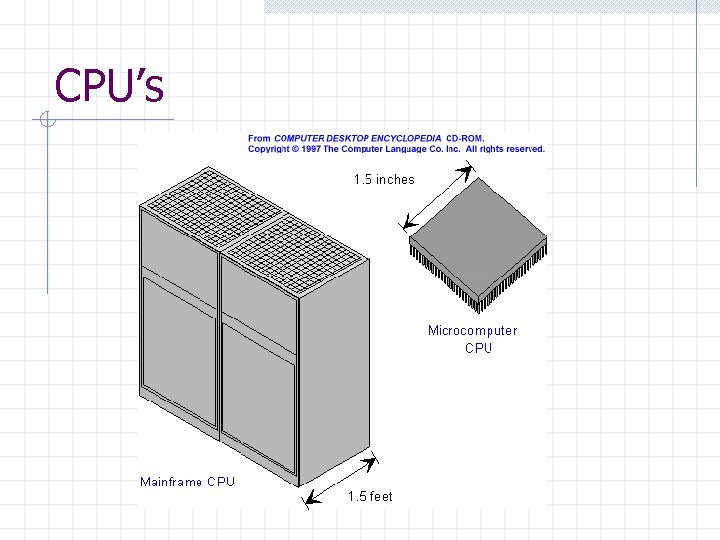

CPU’s

Inside the CPU Registers

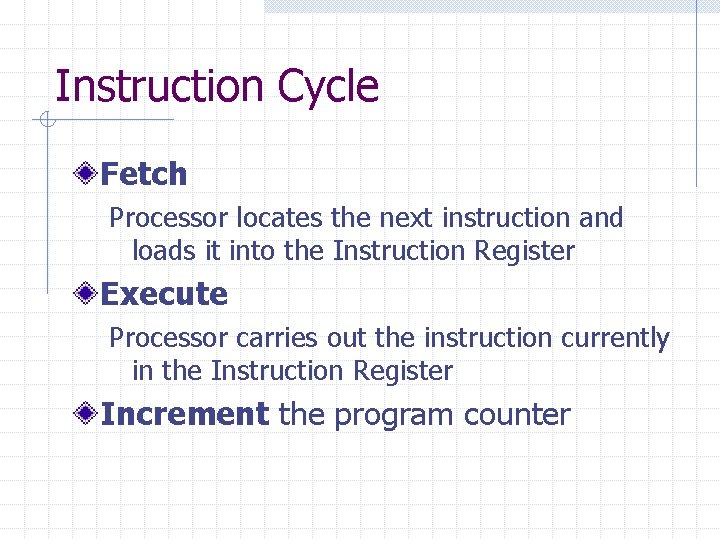

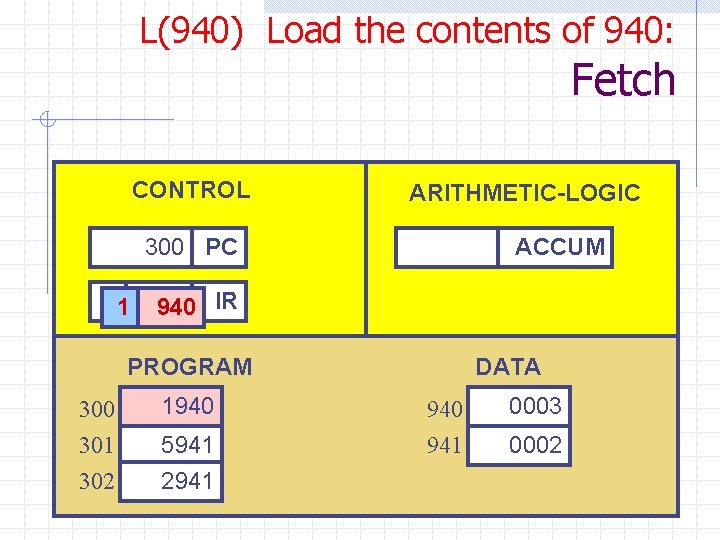

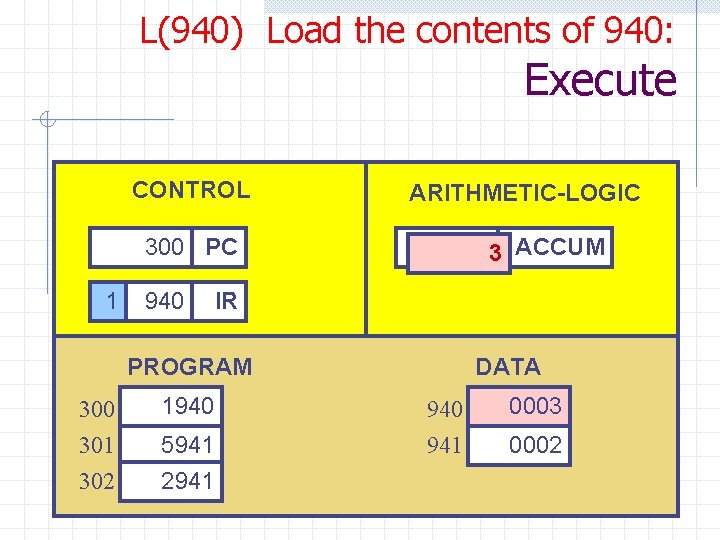

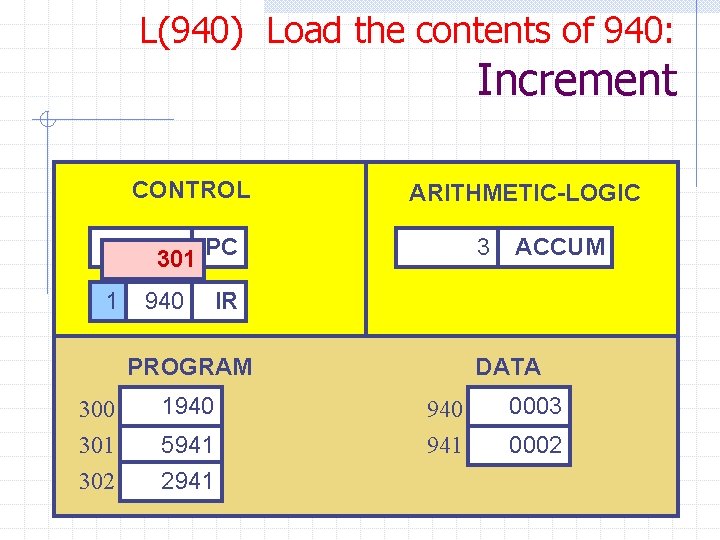

Instruction Cycle Fetch Processor locates the next instruction and loads it into the Instruction Register Execute Processor carries out the instruction currently in the Instruction Register Increment the program counter

CPU Cycle Increment Program Counter Start FETCH EXECUTE Halt

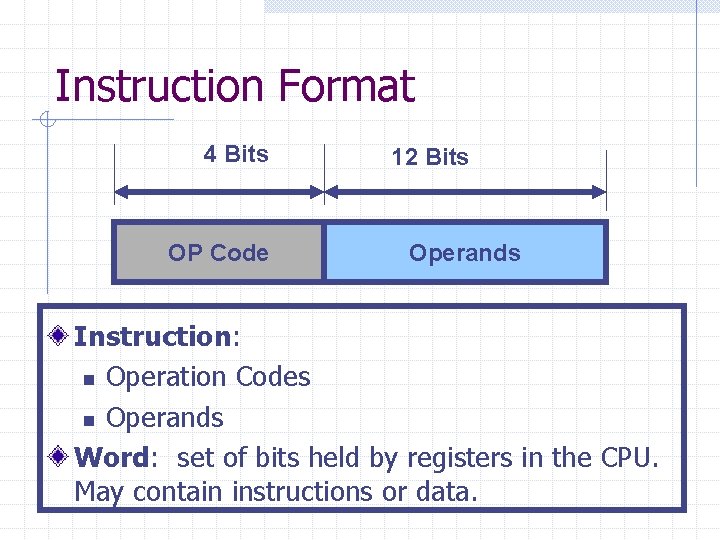

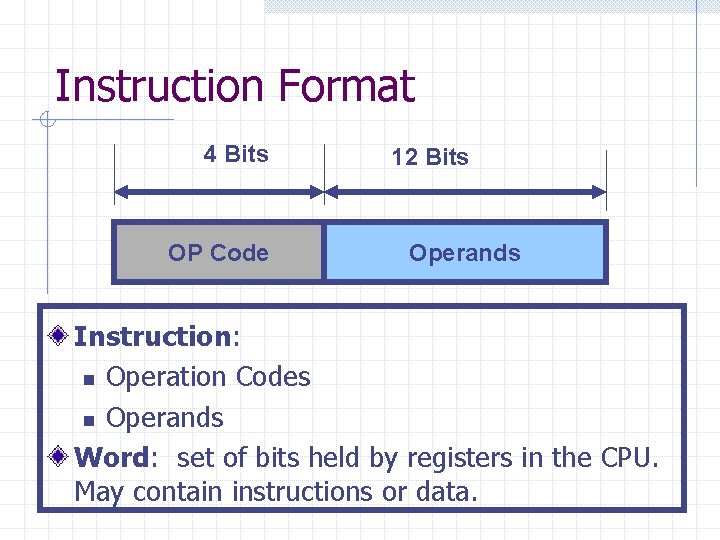

Instruction Format 4 Bits OP Code 12 Bits Operands Instruction: n Operation Codes n Operands Word: set of bits held by registers in the CPU. May contain instructions or data.

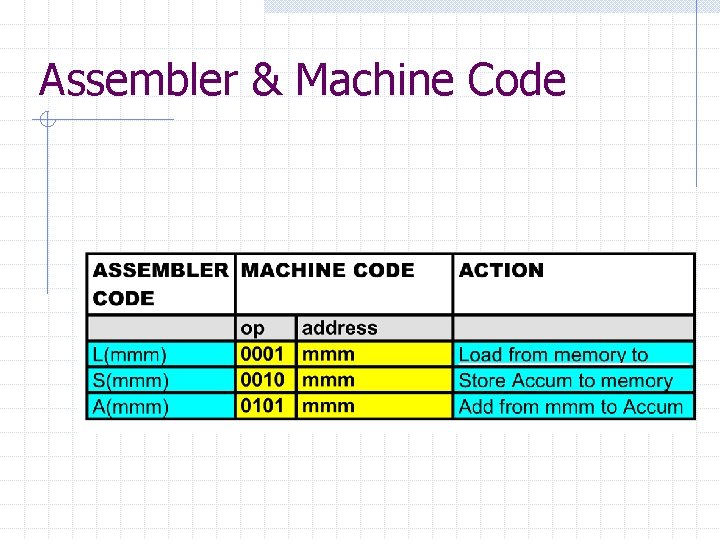

Assembler & Machine Code

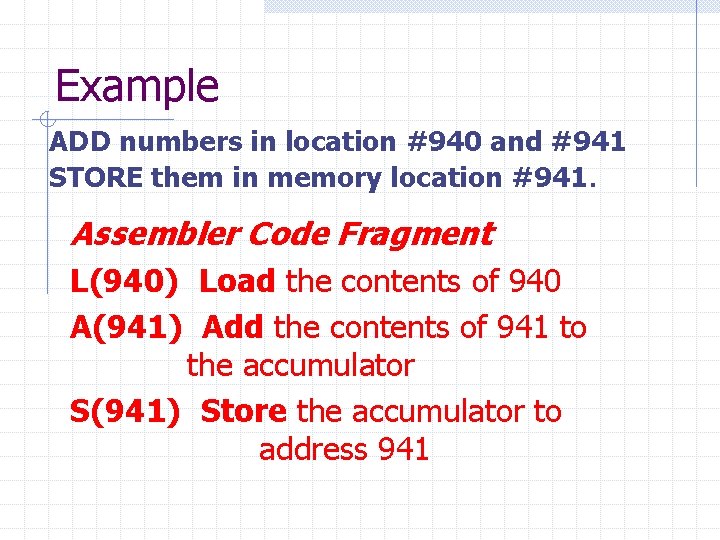

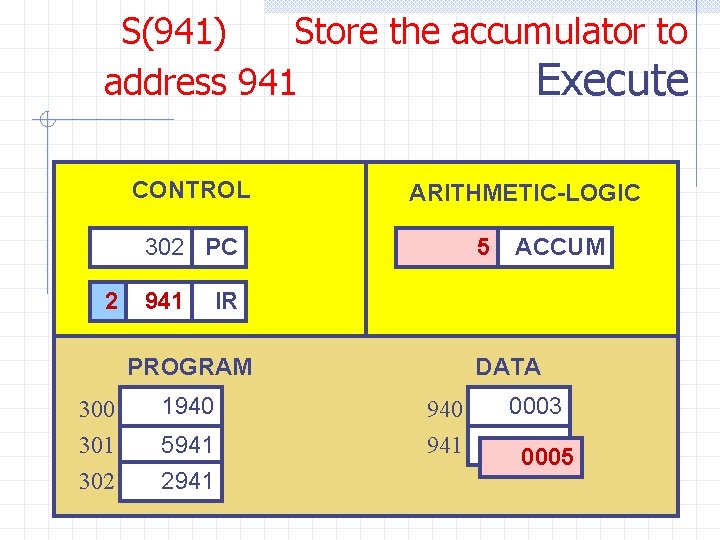

Example ADD numbers in location #940 and #941 STORE them in memory location #941. Assembler Code Fragment L(940) Load the contents of 940 A(941) Add the contents of 941 to the accumulator S(941) Store the accumulator to address 941

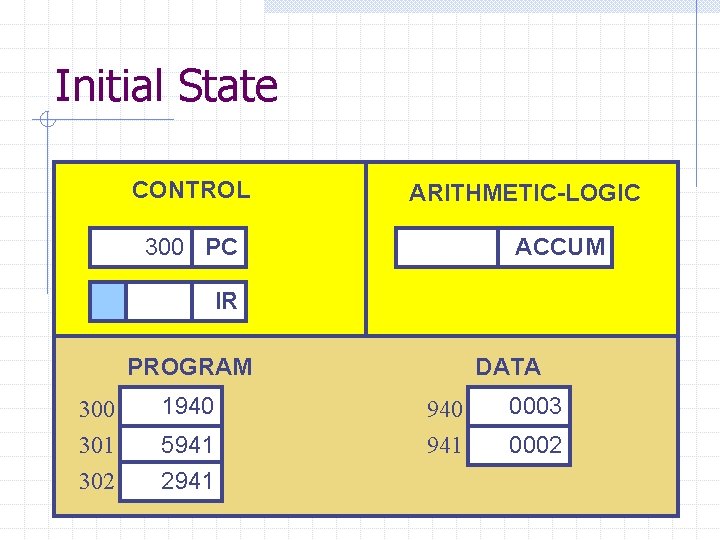

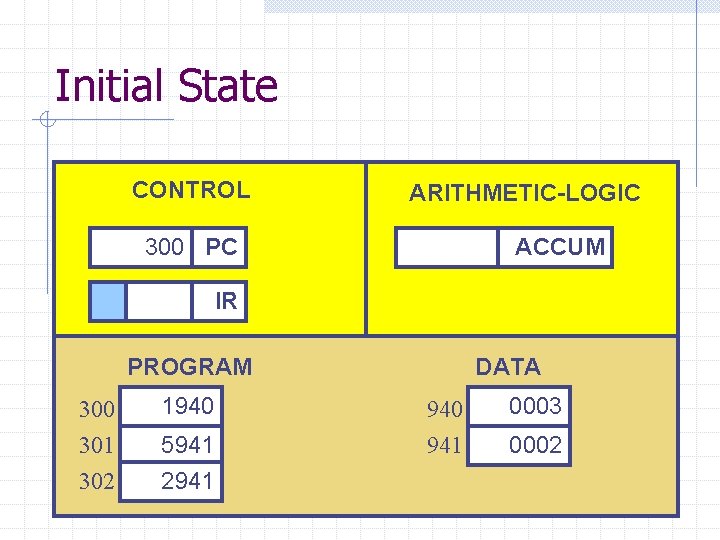

Initial State CONTROL ARITHMETIC-LOGIC 300 PC ACCUM IR PROGRAM 300 301 302 1940 5941 2941 DATA 940 941 0003 0002

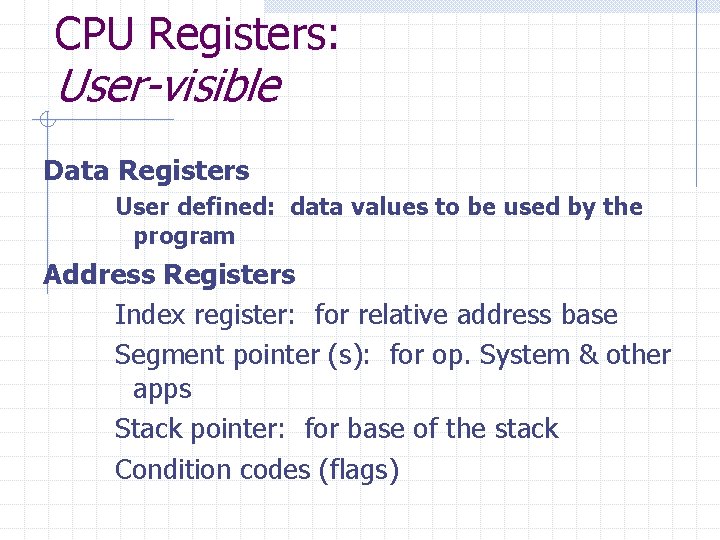

CPU Registers: User-visible Data Registers User defined: data values to be used by the program Address Registers Index register: for relative address base Segment pointer (s): for op. System & other apps Stack pointer: for base of the stack Condition codes (flags)

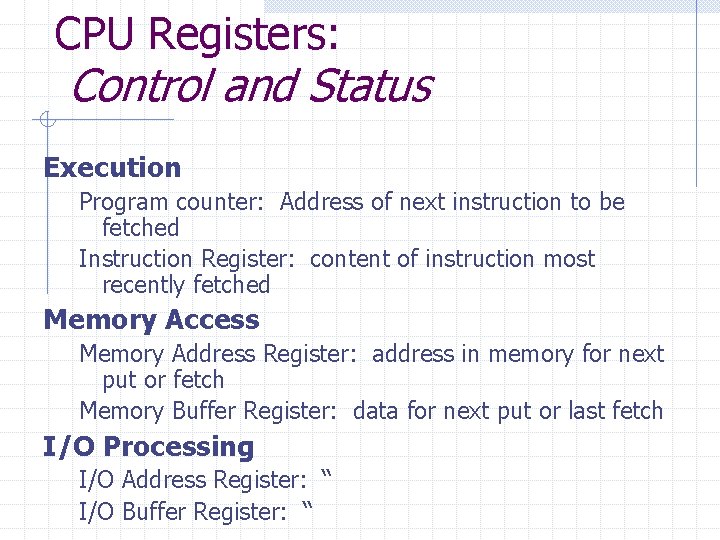

CPU Registers: Control and Status Execution Program counter: Address of next instruction to be fetched Instruction Register: content of instruction most recently fetched Memory Access Memory Address Register: address in memory for next put or fetch Memory Buffer Register: data for next put or last fetch I/O Processing I/O Address Register: “ I/O Buffer Register: “

Initial State CONTROL ARITHMETIC-LOGIC 300 PC ACCUM IR PROGRAM 300 301 302 1940 5941 2941 DATA 940 941 0003 0002

L(940) Load the contents of 940: Fetch CONTROL ARITHMETIC-LOGIC 300 PC 1 ACCUM 940 IR PROGRAM 300 301 302 1940 5941 2941 DATA 940 941 0003 0002

L(940) Load the contents of 940: Execute CONTROL ARITHMETIC-LOGIC 300 PC 1 940 3 ACCUM IR PROGRAM 300 301 302 1940 5941 2941 DATA 940 941 0003 0002

L(940) Load the contents of 940: Increment CONTROL ARITHMETIC-LOGIC 300 301 PC 1 940 3 IR PROGRAM 300 301 302 1940 5941 2941 ACCUM DATA 940 941 0003 0002

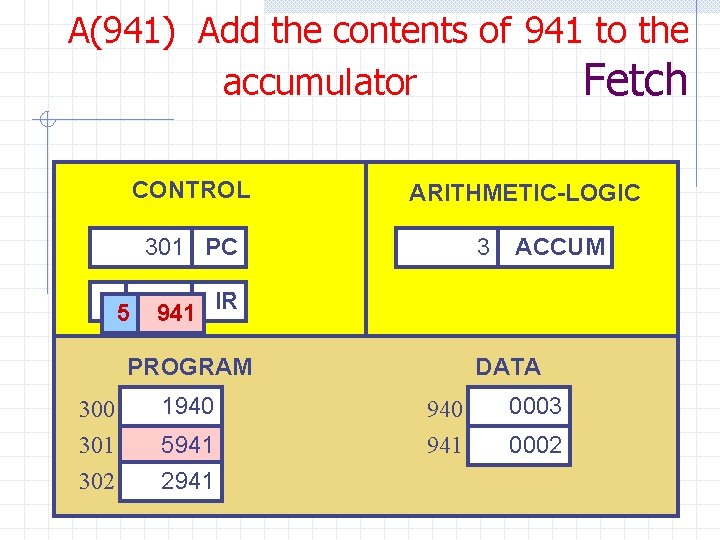

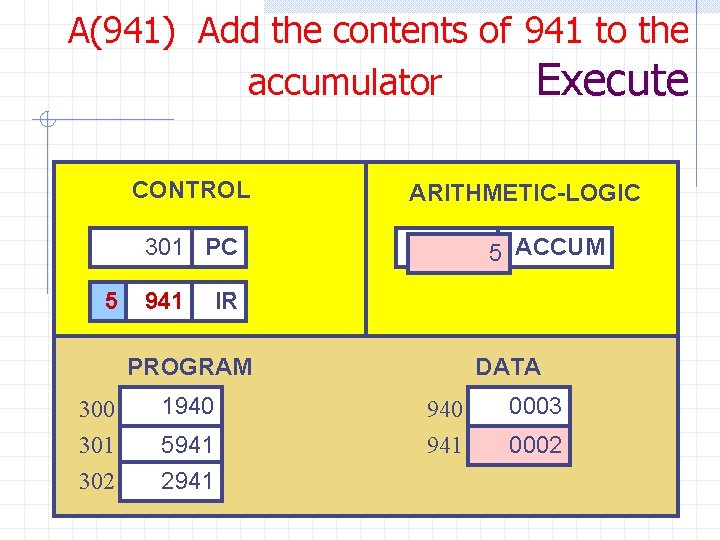

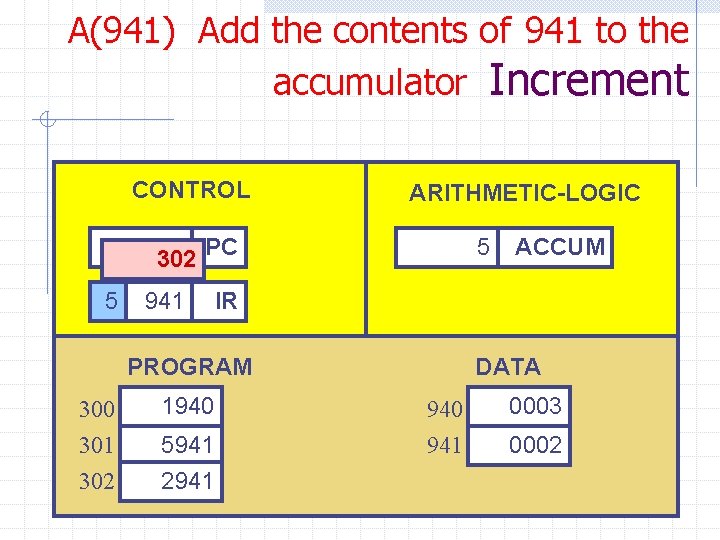

A(941) Add the contents of 941 to the accumulator Fetch CONTROL ARITHMETIC-LOGIC 301 PC 5 3 941 IR PROGRAM 300 301 302 ACCUM 1940 5941 2941 DATA 940 941 0003 0002

A(941) Add the contents of 941 to the accumulator Execute CONTROL ARITHMETIC-LOGIC 301 PC 5 941 35 ACCUM IR PROGRAM 300 301 302 1940 5941 2941 DATA 940 941 0003 0002

A(941) Add the contents of 941 to the accumulator Increment CONTROL ARITHMETIC-LOGIC 301 302 PC 5 941 5 IR PROGRAM 300 301 302 1940 5941 2941 ACCUM DATA 940 941 0003 0002

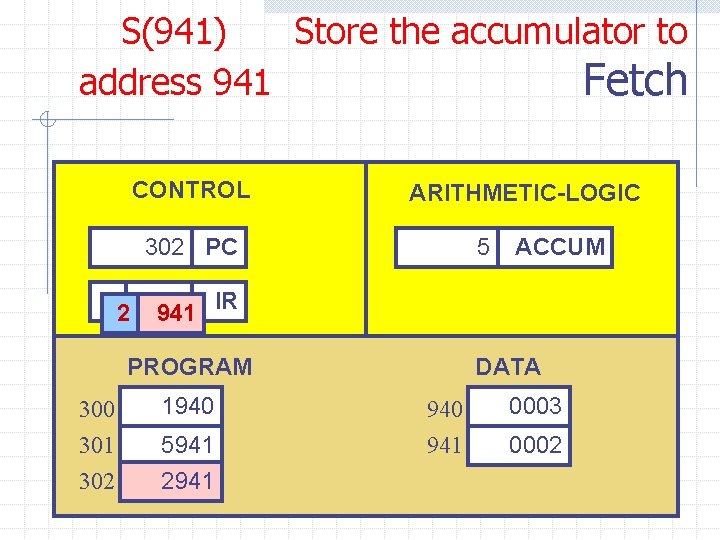

S(941) Store the accumulator to address 941 Fetch CONTROL ARITHMETIC-LOGIC 302 PC 2 5 941 IR PROGRAM 300 301 302 ACCUM 1940 5941 2941 DATA 940 941 0003 0002

S(941) Store the accumulator to address 941 Execute CONTROL ARITHMETIC-LOGIC 302 PC 2 941 5 IR PROGRAM 300 301 302 1940 5941 2941 ACCUM DATA 940 941 0003 0002 0005

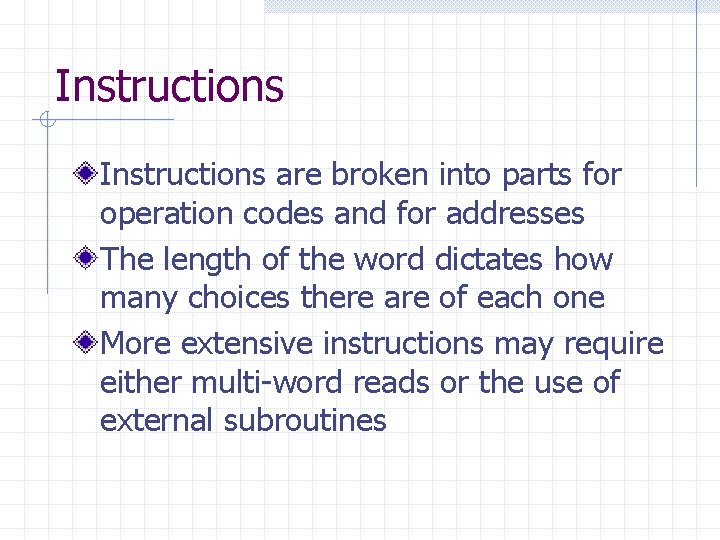

Instructions are broken into parts for operation codes and for addresses The length of the word dictates how many choices there are of each one More extensive instructions may require either multi-word reads or the use of external subroutines

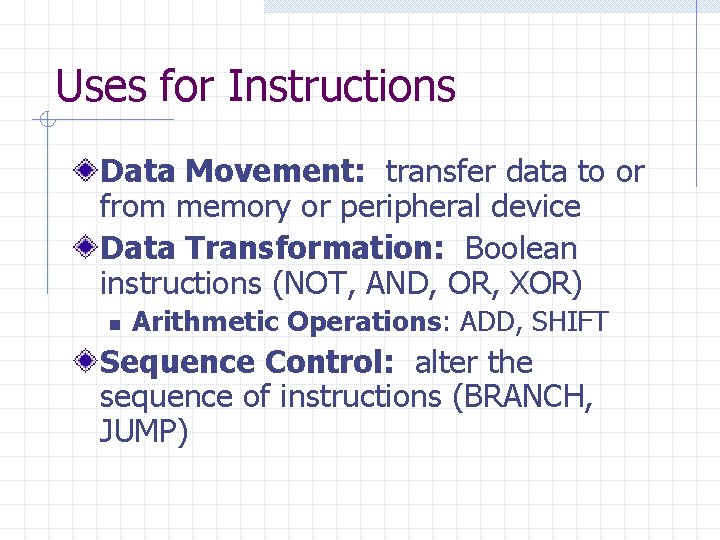

Uses for Instructions Data Movement: transfer data to or from memory or peripheral device Data Transformation: Boolean instructions (NOT, AND, OR, XOR) n Arithmetic Operations: ADD, SHIFT Sequence Control: alter the sequence of instructions (BRANCH, JUMP)

Instruction Format 4 Bits OP Code 12 Bits Operands Instruction: n Operation Codes n Operands Word: set of bits held by registers in the CPU. May contain instructions or data.

Assembler & Machine Code Machine code and assembler code are the same except that machine code uses the binary representations Assembler requires managing memory and registers directly Machine language (assembler) activates chip instructions and microcode instructions stored on ROM

Assembler & Machine Code

Clock Rate z. System timing pulse frequency z. Measured in hertz (HZ) – cycles per second z. Cycle time = 1/clock rate z. Don’t confuse with instruction execution rate (MIPS, MFLOPS)

Word Size Amount of data CPU processes at one time How much faster is a 64 -bit processor than a 32 -bit? What’s the ratio of associated computer components?

The Physical CPU Tubes -> transistors -> integrated circuits-> microchips Microprocessors n All circuits and connections needed to implement a CPU

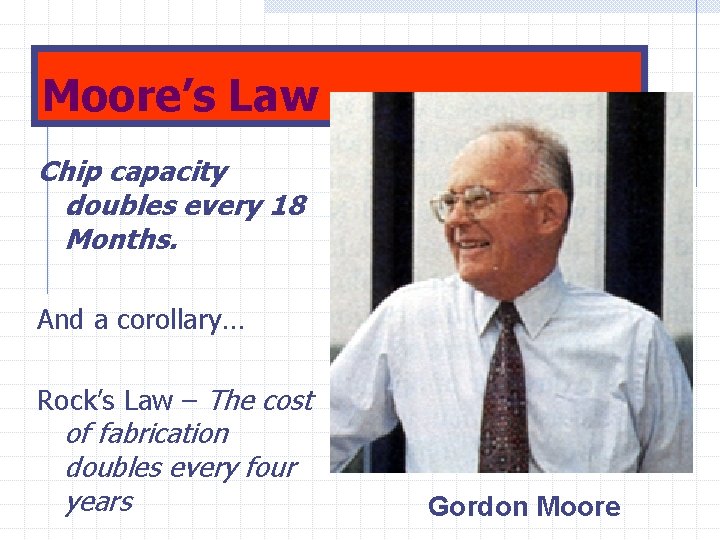

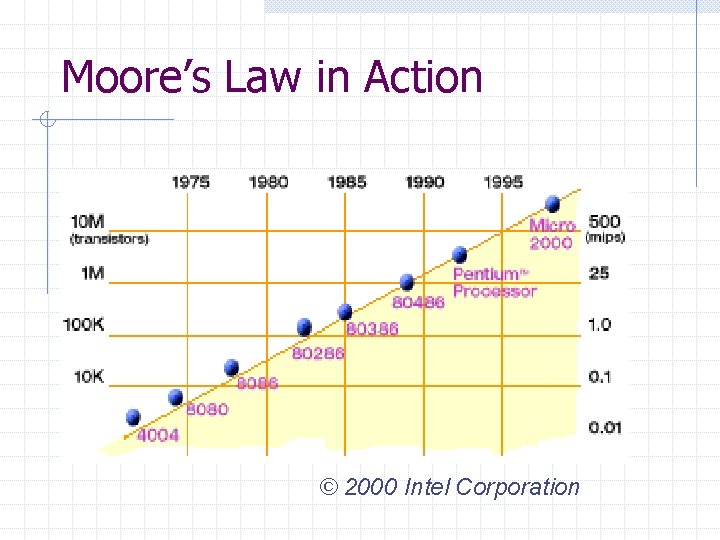

Moore’s Law Chip capacity doubles every 18 Months. And a corollary… Rock’s Law – The cost of fabrication doubles every four years Gordon Moore

Moore’s Law in Action © 2000 Intel Corporation

Computer Theory Mathematical foundations of computing w. Turing Machines w. Von Neumann Architecture

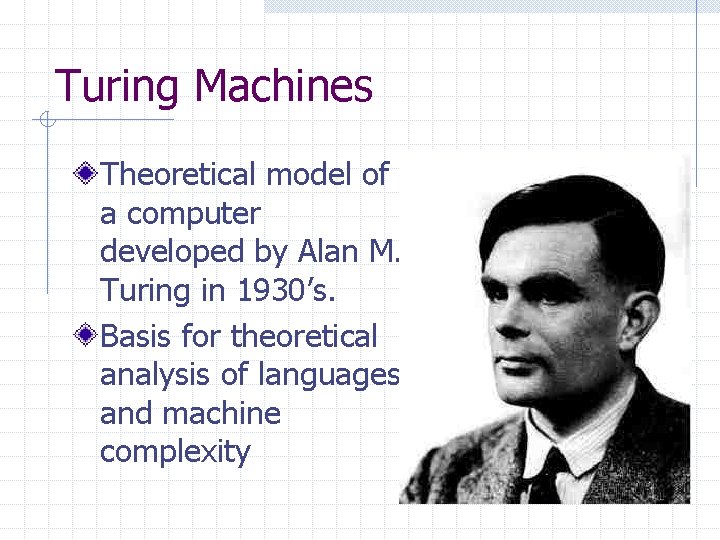

Turing Machines Theoretical model of a computer developed by Alan M. Turing in 1930’s. Basis for theoretical analysis of languages and machine complexity

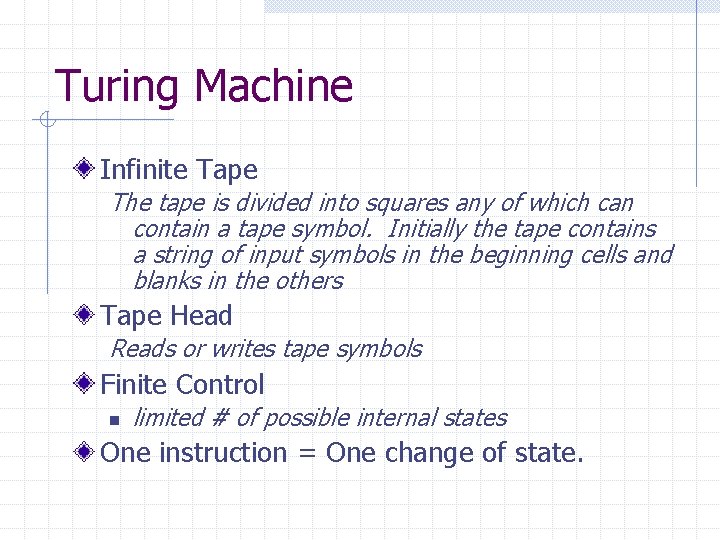

Turing Machine Infinite Tape The tape is divided into squares any of which can contain a tape symbol. Initially the tape contains a string of input symbols in the beginning cells and blanks in the others Tape Head Reads or writes tape symbols Finite Control n limited # of possible internal states One instruction = One change of state.

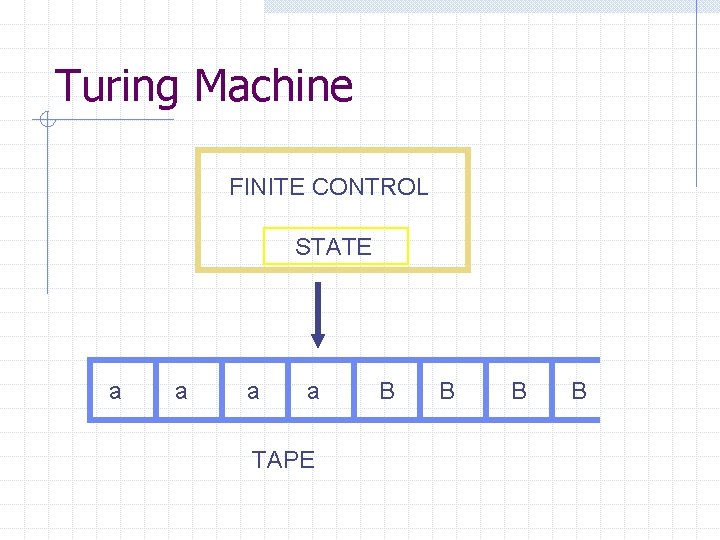

Turing Machine FINITE CONTROL STATE a a TAPE B B

Von Neumann Architecture: Stored Program Machine n CPU n Fast Memory n Slow Storage n Binary Program: executed in sequence Computer behavior is determined by stored programs.

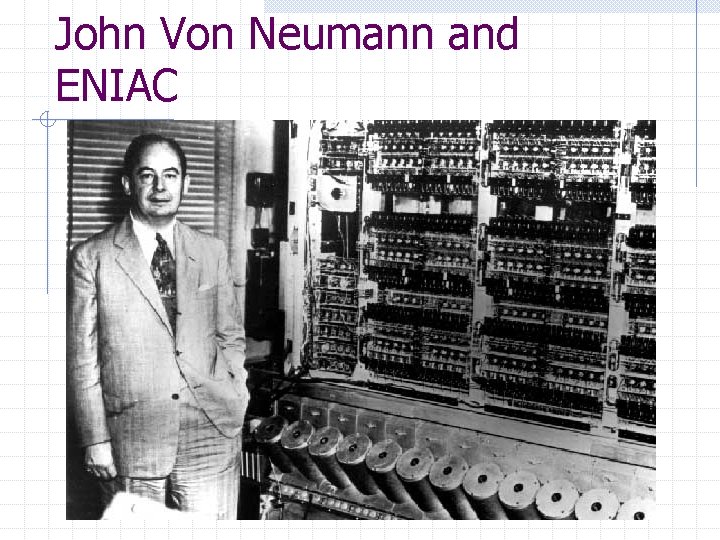

John Von Neumann and ENIAC

- Slides: 40