Computerorientierte Physik VORLESUNG Zeit jeweils Mo 9 40

- Slides: 13

Computerorientierte Physik VORLESUNG • Zeit: jeweils Mo. 9. 40 - 11. 10 Uhr Ort: Hörsaal 5. 01, Institut für Experimentalphysik, Universitätsplatz 5, A-8010 Graz

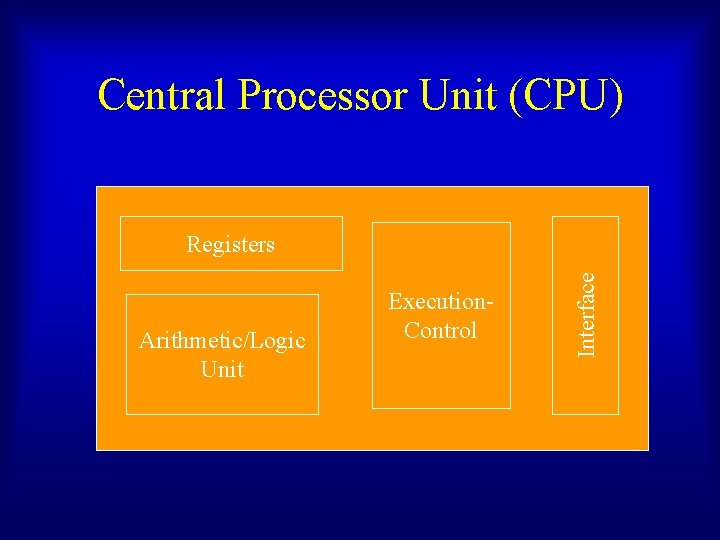

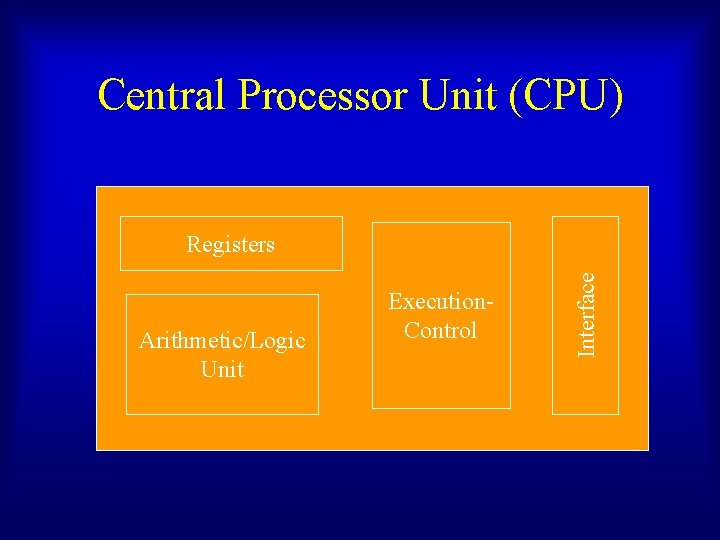

Central Processor Unit (CPU) Arithmetic/Logic Unit Execution. Control Interface Registers

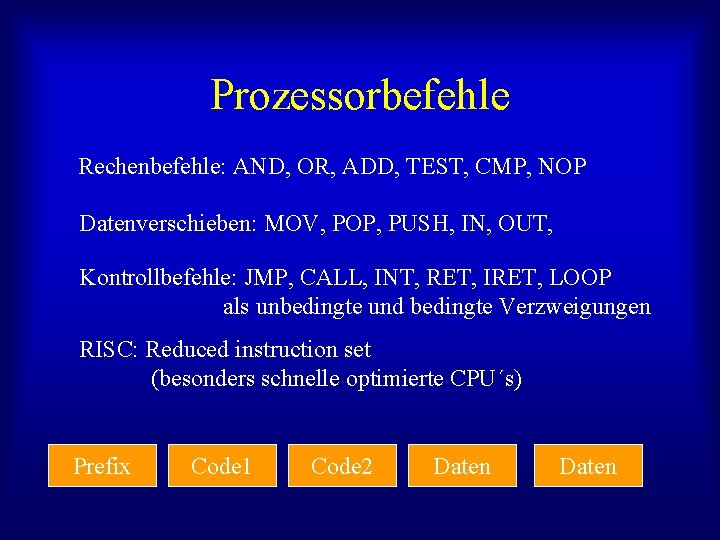

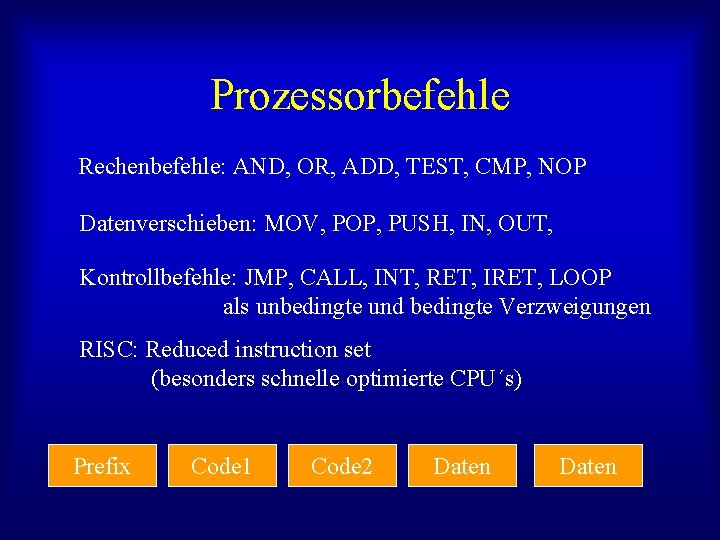

Prozessorbefehle Rechenbefehle: AND, OR, ADD, TEST, CMP, NOP Datenverschieben: MOV, POP, PUSH, IN, OUT, Kontrollbefehle: JMP, CALL, INT, RET, IRET, LOOP als unbedingte und bedingte Verzweigungen RISC: Reduced instruction set (besonders schnelle optimierte CPU´s) Prefix Code 1 Code 2 Daten

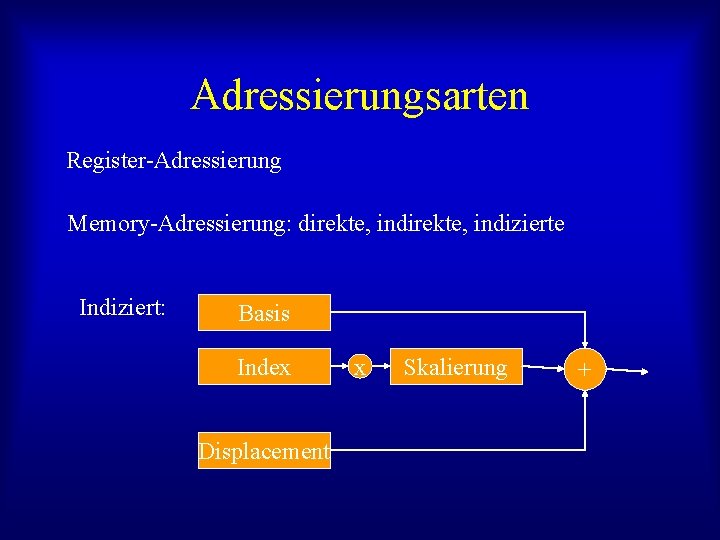

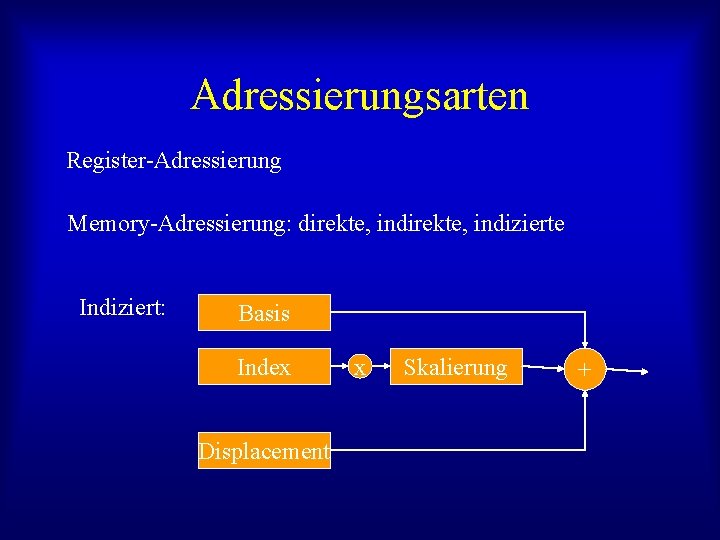

Adressierungsarten Register-Adressierung Memory-Adressierung: direkte, indizierte Indiziert: Basis Index Displacement x Skalierung +

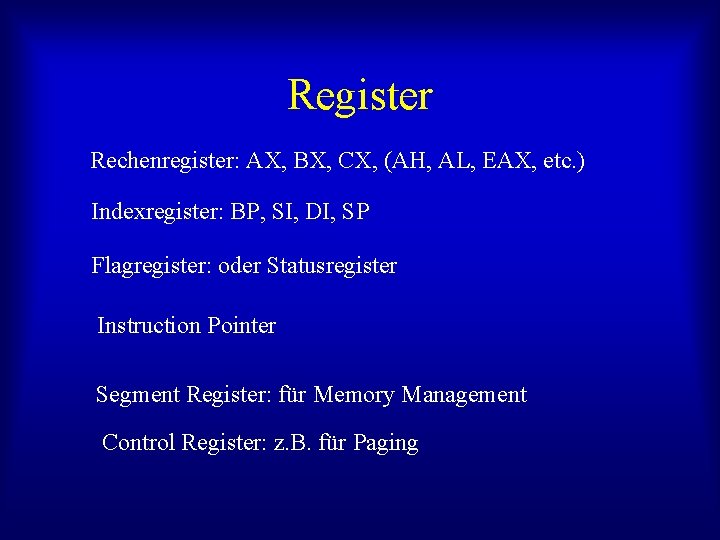

Register Rechenregister: AX, BX, CX, (AH, AL, EAX, etc. ) Indexregister: BP, SI, DI, SP Flagregister: oder Statusregister Instruction Pointer Segment Register: für Memory Management Control Register: z. B. für Paging

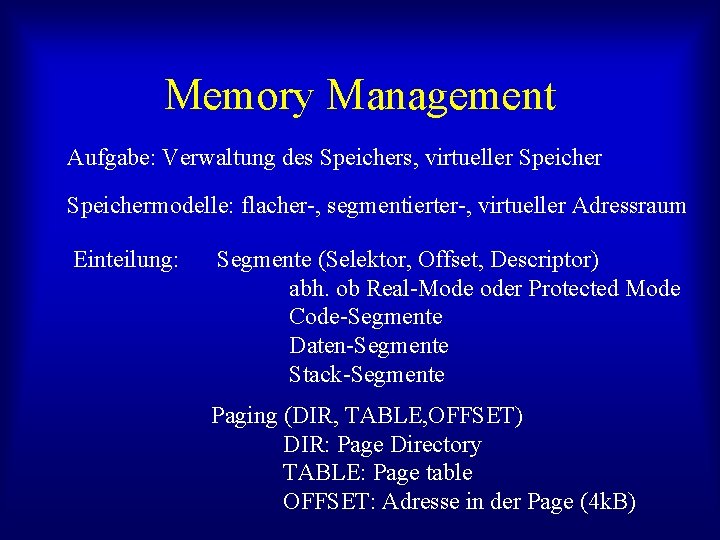

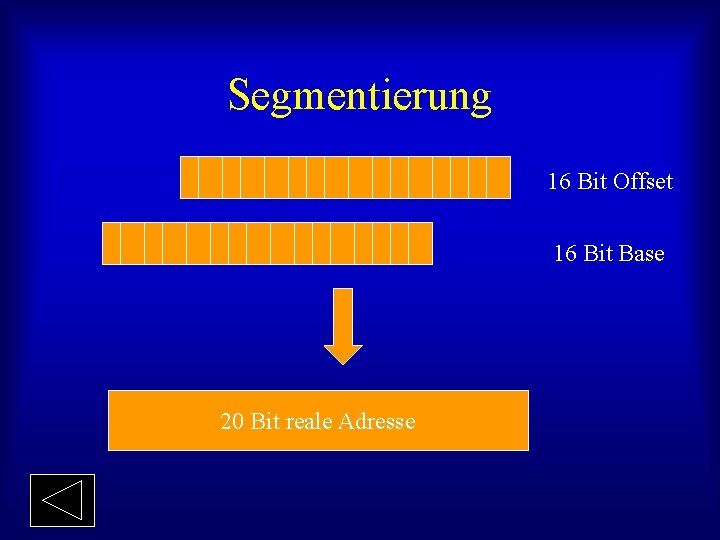

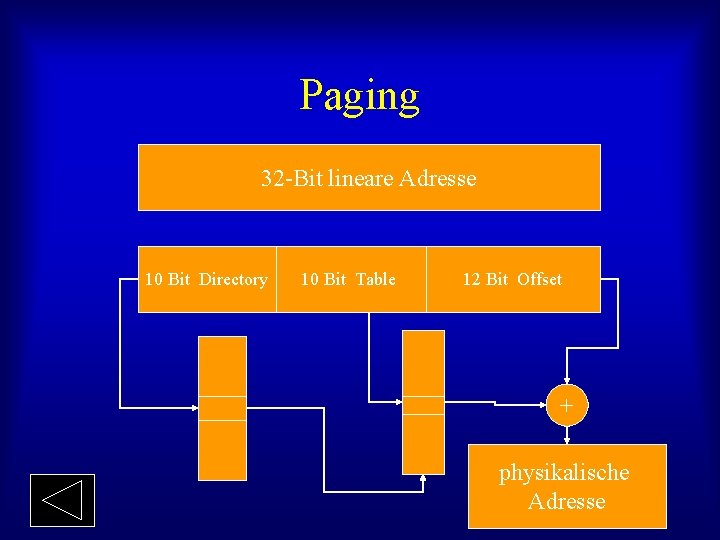

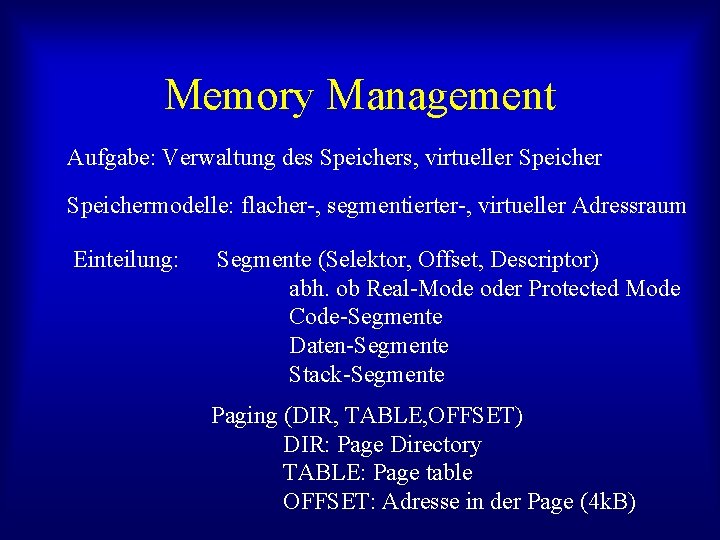

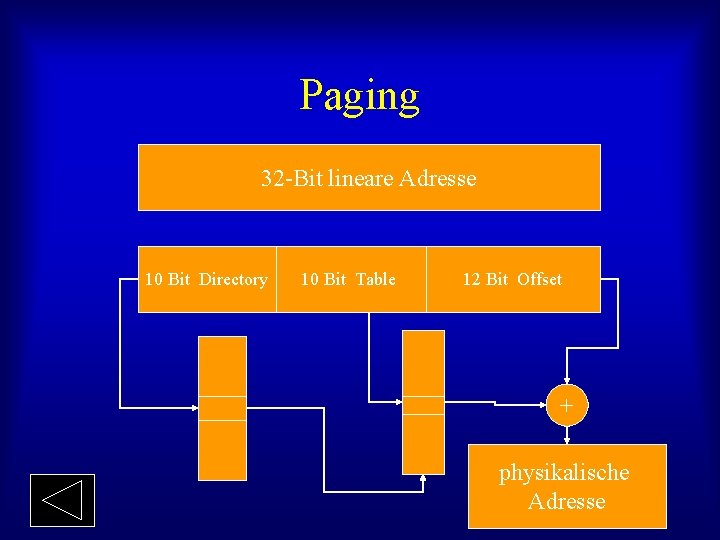

Memory Management Aufgabe: Verwaltung des Speichers, virtueller Speichermodelle: flacher-, segmentierter-, virtueller Adressraum Einteilung: Segmente (Selektor, Offset, Descriptor) abh. ob Real-Mode oder Protected Mode Code-Segmente Daten-Segmente Stack-Segmente Paging (DIR, TABLE, OFFSET) DIR: Page Directory TABLE: Page table OFFSET: Adresse in der Page (4 k. B)

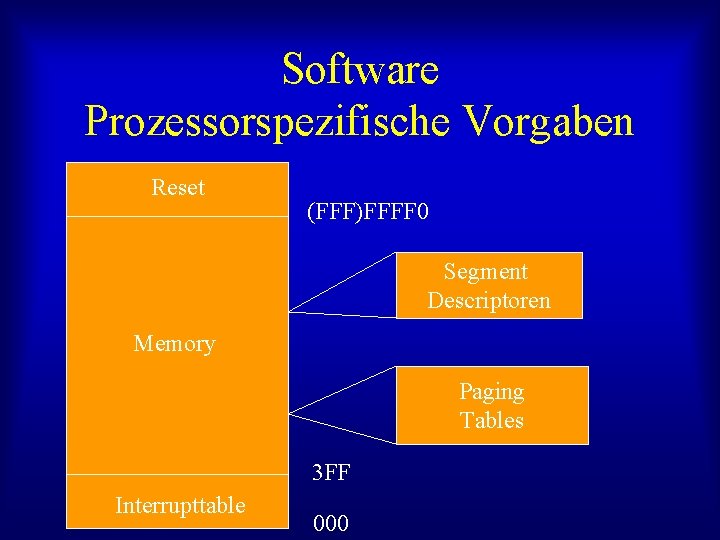

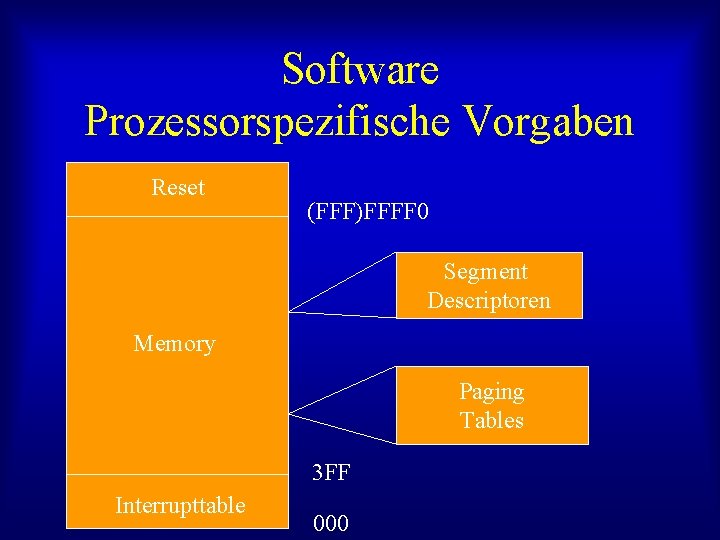

Software Prozessorspezifische Vorgaben Reset (FFF)FFFF 0 Segment Descriptoren Memory Paging Tables 3 FF Interrupttable 000

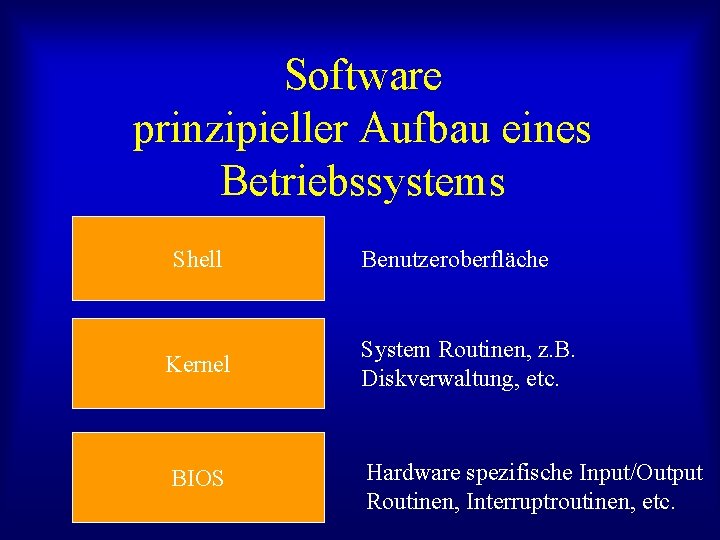

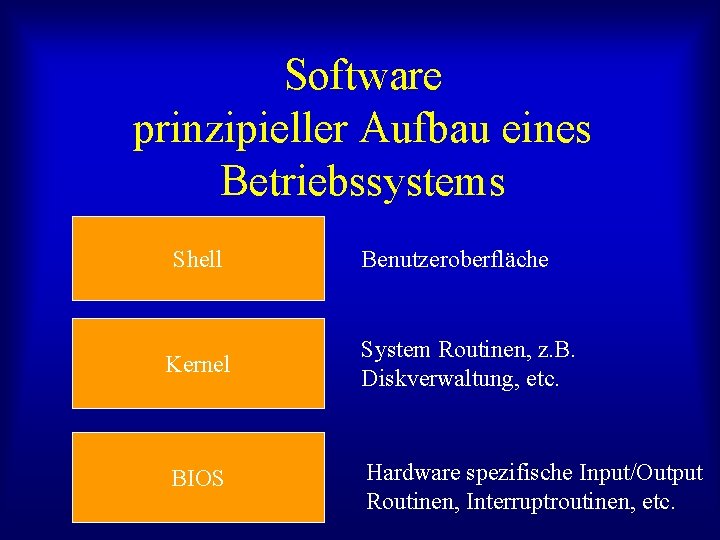

Software prinzipieller Aufbau eines Betriebssystems Shell Benutzeroberfläche Kernel System Routinen, z. B. Diskverwaltung, etc. BIOS Hardware spezifische Input/Output Routinen, Interruptroutinen, etc.

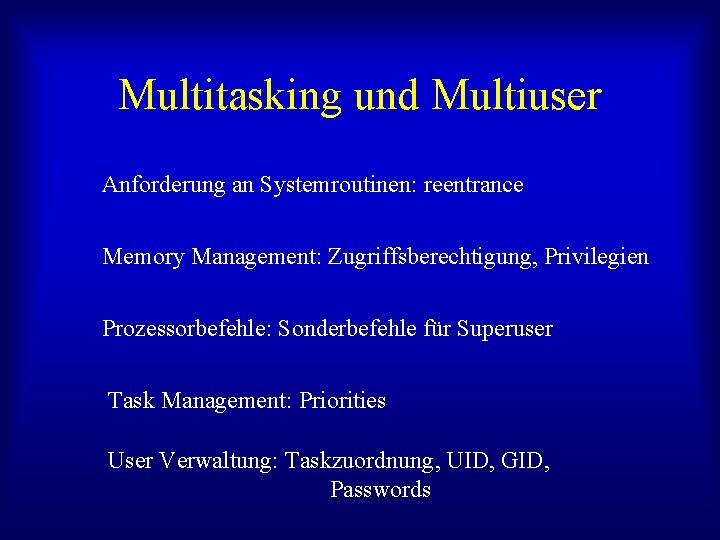

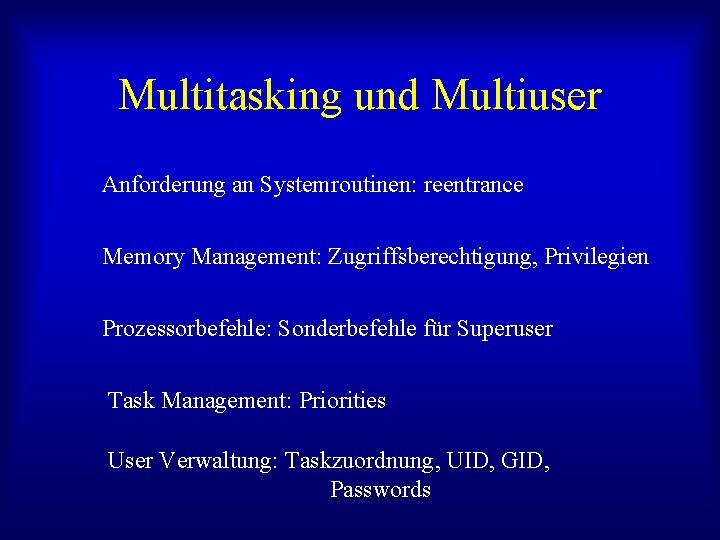

Multitasking und Multiuser Anforderung an Systemroutinen: reentrance Memory Management: Zugriffsberechtigung, Privilegien Prozessorbefehle: Sonderbefehle für Superuser Task Management: Priorities User Verwaltung: Taskzuordnung, UID, GID, Passwords

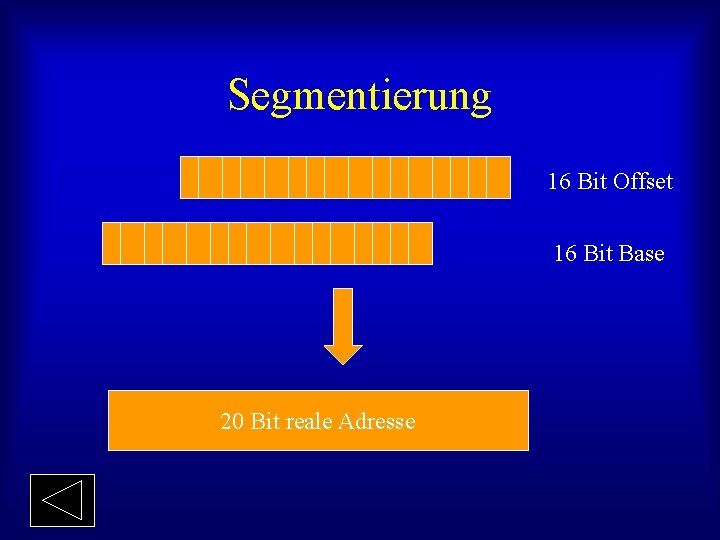

Segmentierung 16 Bit Offset 16 Bit Base 20 Bit reale Adresse

Paging 32 -Bit lineare Adresse 10 Bit Directory 10 Bit Table 12 Bit Offset + physikalische Adresse