Computerorientierte Physik VORLESUNG Zeit jeweils Mo 9 40

- Slides: 17

Computerorientierte Physik VORLESUNG • Zeit: jeweils Mo. 9. 40 - 11. 10 Uhr Ort: Hörsaal 5. 01, Institut für Experimentalphysik, Universitätsplatz 5, A-8010 Graz

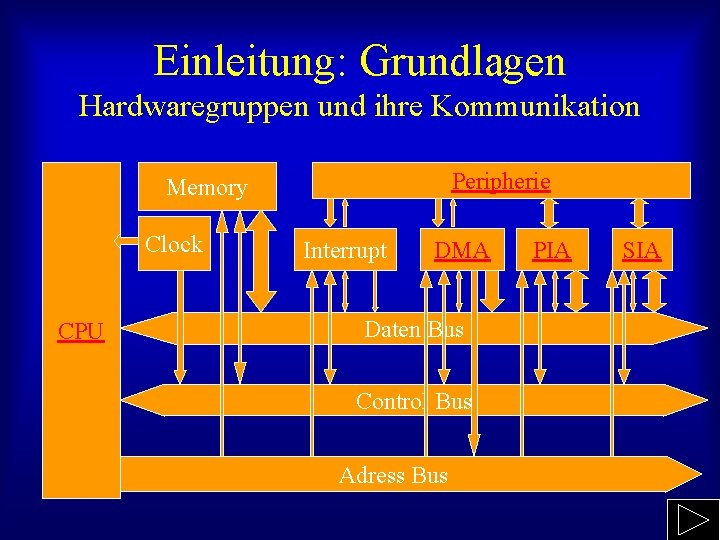

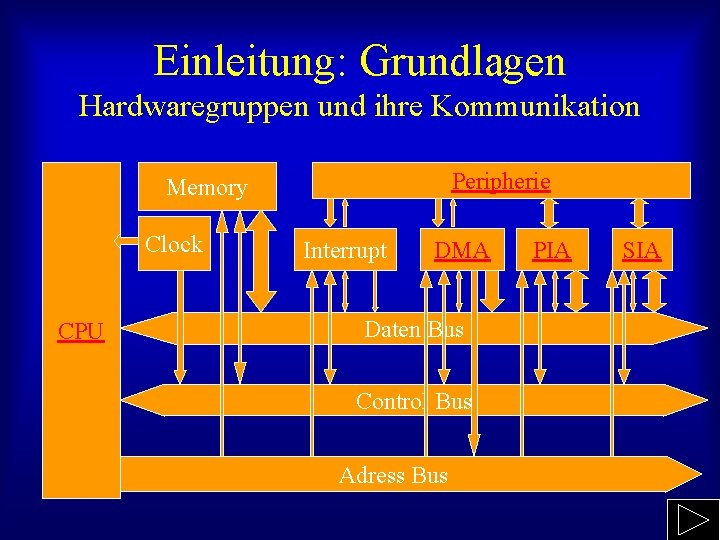

Einleitung: Grundlagen Hardwaregruppen und ihre Kommunikation Peripherie Memory Clock CPU Interrupt DMA Daten Bus Control Bus Adress Bus PIA SIA

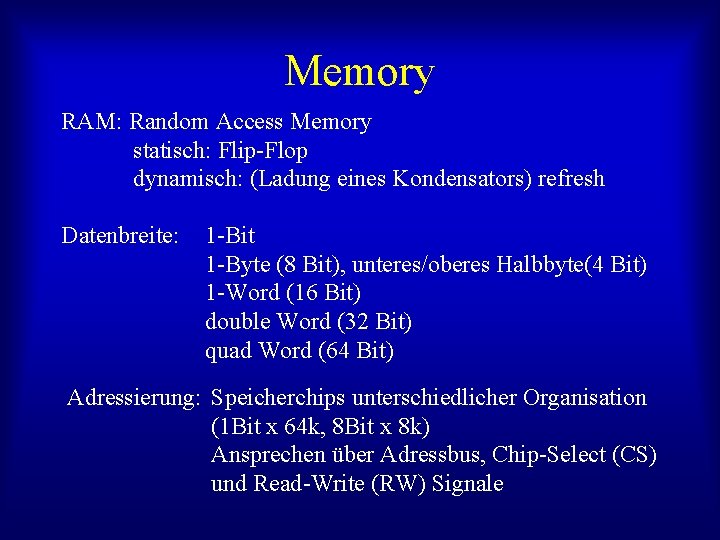

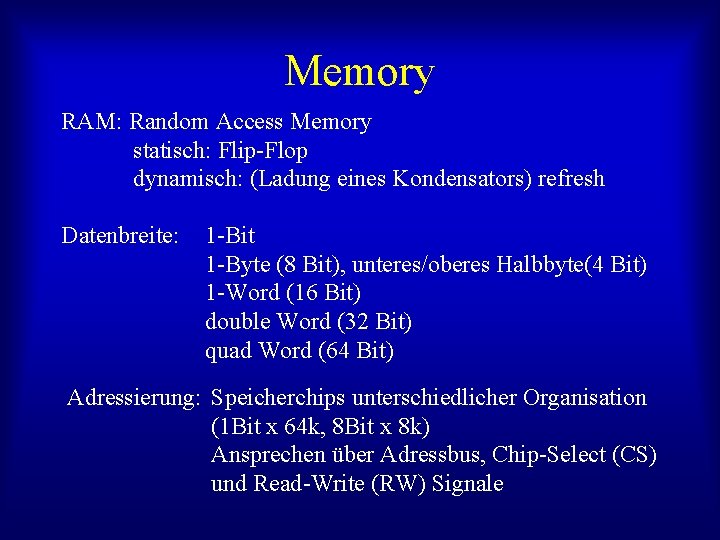

Memory RAM: Random Access Memory statisch: Flip-Flop dynamisch: (Ladung eines Kondensators) refresh Datenbreite: 1 -Bit 1 -Byte (8 Bit), unteres/oberes Halbbyte(4 Bit) 1 -Word (16 Bit) double Word (32 Bit) quad Word (64 Bit) Adressierung: Speicherchips unterschiedlicher Organisation (1 Bit x 64 k, 8 Bit x 8 k) Ansprechen über Adressbus, Chip-Select (CS) und Read-Write (RW) Signale

Memory Organisation 8 x 32 k 8 -Bit bidirektionaler Datenbus (Tri-State-Buffer) Controlbus A 0 -A 12 8 x 8 k Enable, R/W Adressbus CS 8 x 8 k Enable, R/W CS A 0 -A 12 CS Enable, R/W A 13 -A 14 Codierung 8 x 8 k A 0 -A 12 8 x 8 k Enable, R/W CS

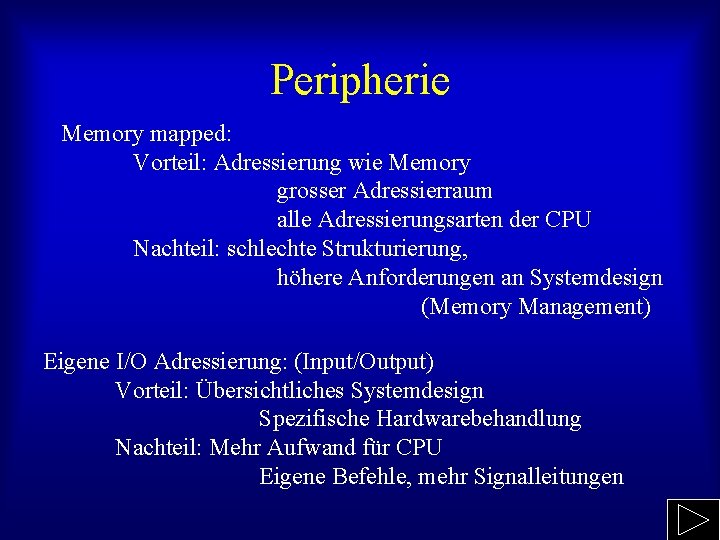

Peripherie Memory mapped: Vorteil: Adressierung wie Memory grosser Adressierraum alle Adressierungsarten der CPU Nachteil: schlechte Strukturierung, höhere Anforderungen an Systemdesign (Memory Management) Eigene I/O Adressierung: (Input/Output) Vorteil: Übersichtliches Systemdesign Spezifische Hardwarebehandlung Nachteil: Mehr Aufwand für CPU Eigene Befehle, mehr Signalleitungen

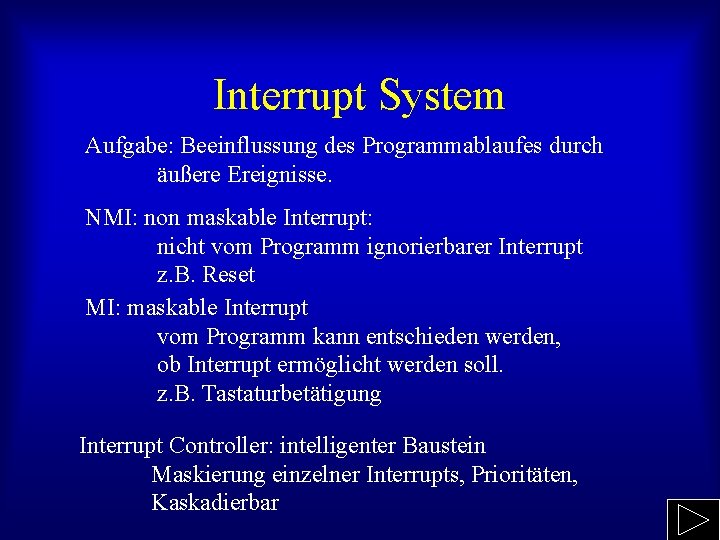

Interrupt System Aufgabe: Beeinflussung des Programmablaufes durch äußere Ereignisse. NMI: non maskable Interrupt: nicht vom Programm ignorierbarer Interrupt z. B. Reset MI: maskable Interrupt vom Programm kann entschieden werden, ob Interrupt ermöglicht werden soll. z. B. Tastaturbetätigung Interrupt Controller: intelligenter Baustein Maskierung einzelner Interrupts, Prioritäten, Kaskadierbar

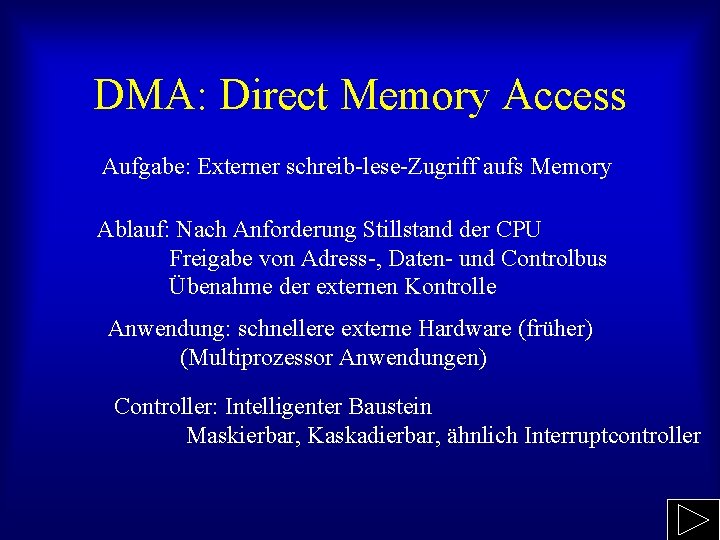

DMA: Direct Memory Access Aufgabe: Externer schreib-lese-Zugriff aufs Memory Ablauf: Nach Anforderung Stillstand der CPU Freigabe von Adress-, Daten- und Controlbus Übenahme der externen Kontrolle Anwendung: schnellere externe Hardware (früher) (Multiprozessor Anwendungen) Controller: Intelligenter Baustein Maskierbar, Kaskadierbar, ähnlich Interruptcontroller

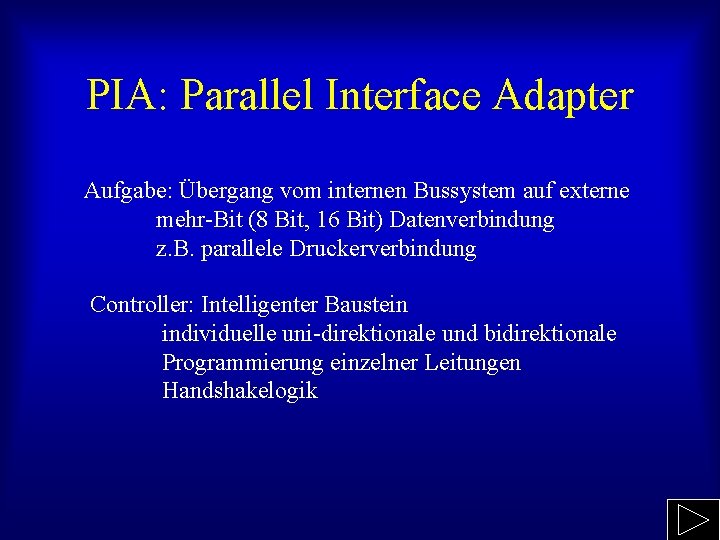

PIA: Parallel Interface Adapter Aufgabe: Übergang vom internen Bussystem auf externe mehr-Bit (8 Bit, 16 Bit) Datenverbindung z. B. parallele Druckerverbindung Controller: Intelligenter Baustein individuelle uni-direktionale und bidirektionale Programmierung einzelner Leitungen Handshakelogik

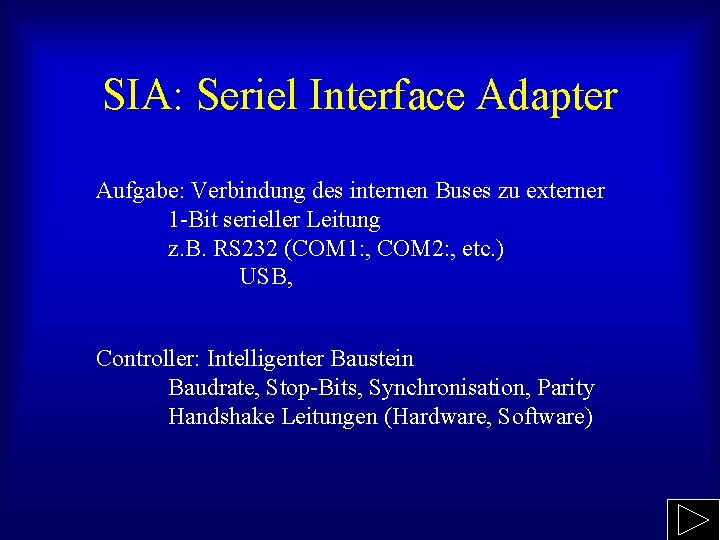

SIA: Seriel Interface Adapter Aufgabe: Verbindung des internen Buses zu externer 1 -Bit serieller Leitung z. B. RS 232 (COM 1: , COM 2: , etc. ) USB, Controller: Intelligenter Baustein Baudrate, Stop-Bits, Synchronisation, Parity Handshake Leitungen (Hardware, Software)

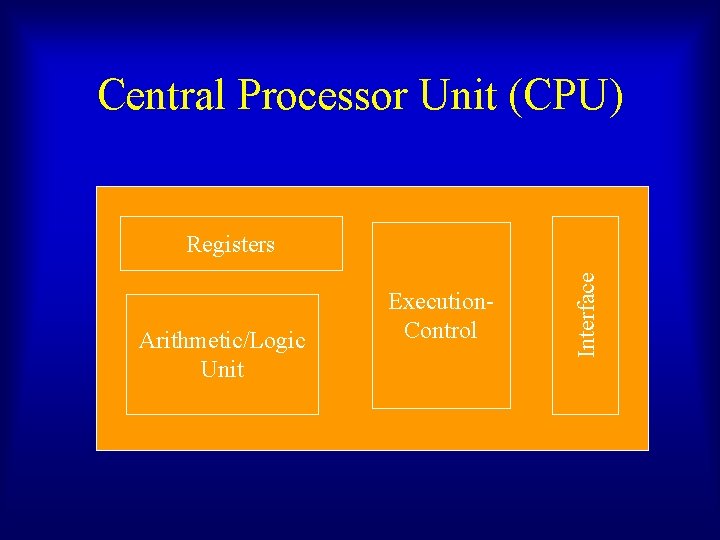

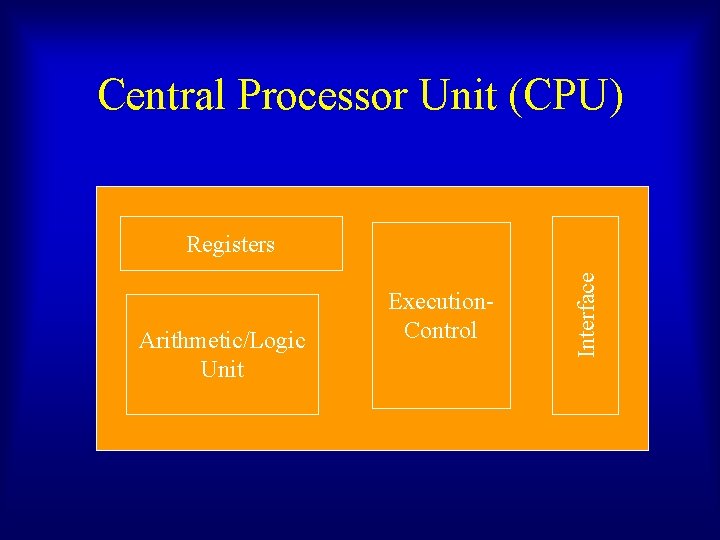

Central Processor Unit (CPU) Arithmetic/Logic Unit Execution. Control Interface Registers

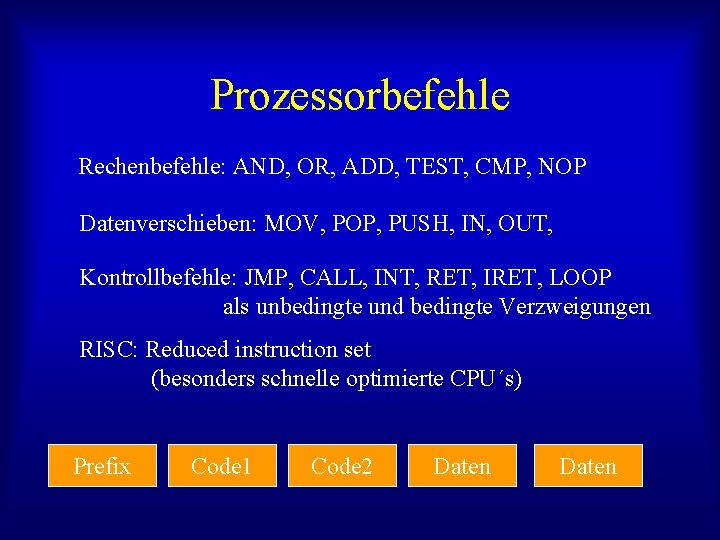

Prozessorbefehle Rechenbefehle: AND, OR, ADD, TEST, CMP, NOP Datenverschieben: MOV, POP, PUSH, IN, OUT, Kontrollbefehle: JMP, CALL, INT, RET, IRET, LOOP als unbedingte und bedingte Verzweigungen RISC: Reduced instruction set (besonders schnelle optimierte CPU´s) Prefix Code 1 Code 2 Daten

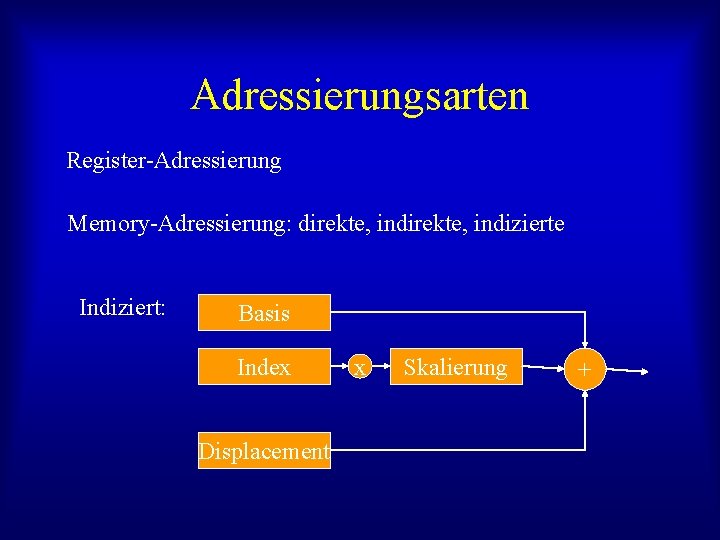

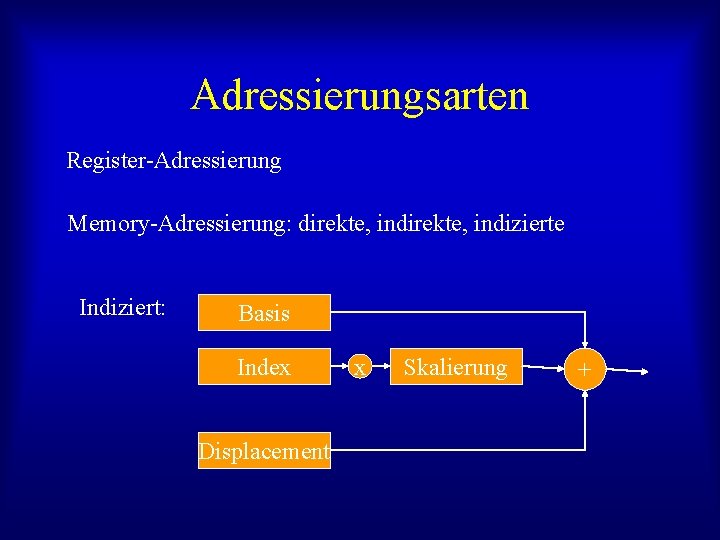

Adressierungsarten Register-Adressierung Memory-Adressierung: direkte, indizierte Indiziert: Basis Index Displacement x Skalierung +

Register Rechenregister: AX, BX, CX, (AH, AL, EAX, etc. ) Indexregister: BP, SI, DI, SP Flagregister: oder Statusregister Instruction Pointer Segment Register: für Memory Management Control Register: z. B. für Paging

Memory Management Aufgabe: Verwaltung des Speichers, virtueller Speichermodelle: flacher-, segmentierter-, virueller Adressraum Einteilung: Segmente (Selektor, Offset, Descriptor) abh. ob Real-Mode oder Protected Mode Code-Segmente Daten-Segmente Stack-Segmente Paging (DIR, TABLE, OFFSET) DIR: Page Directory TABLE: Page table OFFSET: Adresse in der Page (4 k. B)

Computerorientierte Physik Übungen • Zeit: Ort: jeweils Mo. 11. 10 - 11. 55 Uhr bzw. freie Zeitvereinbarung (Projekte) Hörsaal 5. 01, Institut für Experimentalphysik, Universitätsplatz 5, A-8010 Graz

Beispiele • Berechnung und Simulation optischer Geräte (A. Leitner) • • Fourier-Spektroskopie (FTIR) (H. Krenn) Bewegungsanalyse der Handschrift Eintrittsverhalten von Meteoriten in Atmosphäre Analyse von Bewegungsvorgängen mit GPS Höhenvergleich mit Barometer (Hochschwab) • Analyse von Bewegungsvorgängen mit GPS Montainbike-Strecken • Analyse von Bewegungsvorgängen mit GPS Flugzeug