ComputerAided Codesign Methods and Tools Part of HWSW

- Slides: 34

Computer-Aided Co-design Methods and Tools Part of HW/SW Codesign of Embedded Systems Course (CE 40 -226) 13/07/42 Winter. Spring 2001 Codesign of Embedded Systems 1

Today programme n Introduction to HW/SW Codesign n Computer-aided codesign methods and tools Winter-Spring 2001 Codesign of Embedded Systems 2

Motivations n System designer goals n n Satisfy system-level specifications in a short time Maximize system value n n Performance, power consumption, applicability to various user demands Minimize cost n Number of HW parts, size of silicon die, cost of SW development Winter-Spring 2001 Codesign of Embedded Systems 3

Motivations (cont’d) n CAD tools are useful, because n n n Require formal system-level specification => structured design methodology Facilitate HW and SW reuse Support analysis and validation tools Facilitate design-space exploration Overall objective in codesign tool R&D n Provide IDE for concurrent specification, validation, and synthesis of both HW and SW Winter-Spring 2001 Codesign of Embedded Systems 4

Modeling n Model of computation vs. HW/SW language n Computation model: n n Languages: n n n Has an underlying mathematical structure: FSM, Petri net Some are means of expressing a computation model Some don’t have a formal semantics Functional modeling of digital systems n n Normally C or C++, to check generic properties and derive some measure of performance & cost Too general. Do not capture all necessary specifications of HW component Winter-Spring 2001 Codesign of Embedded Systems 5

Modeling (cont’d) n Some specification models n “FSM or interconnection of FSMs” Model n n n Partial-orders of tasks n n n Graphical representation: Statecharts Textual languages: SDL, Esterel HW components: Verilog / VHDL Synchronous data-flows: Silage, DFL A perfect language for system is idealistic Heterogeneity of system components n Conflicting interests of CAD developers and users n Lack of a formalism to capture well all features Winter-Spring 2001 Codesign of Embedded Systems 6 n

Validation n n Validation vs. verification Approaches to validation n Formal verification Simulation (co-simulation) Emulation Winter-Spring 2001 Codesign of Embedded Systems 7

Validation (cont’d) n Simulation n n cannot ensure correctness, but still useful Heterogeneity n Weakly heterogeneous n n n Lumped, GP computing systems. Simple control systems Can be simulated by extending HDL simulators Strongly heteroneous n n Cellular phones, avionics Require specialized simulation environments Winter-Spring 2001 Codesign of Embedded Systems 8

Validation (cont’d) n Simulator features for weakly heterogeneous systems n n Adequate timing accuracy Fast execution Visibility of internal registers for debugging Strategy 1: Use HDL simulator + HDL models for processor and ASICs n Long HW simulation time for each instruction: accuracy vs. speed tradeoff Winter-Spring 2001 Codesign of Embedded Systems 9

Validation (cont’d) n Strategy 2: avoid processor HDL model n n Use HW/SW comm. Protocol SW is compiled and communicates with the HDL simulator which models ASIC HDL simulator is bottle-neck Internal registers not visible Winter-Spring 2001 Codesign of Embedded Systems 10

Validation (cont’d) n Strategy 3: Emulate HW on a reconfigurable platform n n Automatic partitioning tools to minimize system-simulation time have been developed Visibility of internal states is limited => probable slow debugging Winter-Spring 2001 Codesign of Embedded Systems 11

Validation (cont’d) n Simulation of strongly heterogeneous and distributed systems n Specialized simulators: Ptolemy n n Extesible, OO kernel Supports several computation models Models are not implemented in simulation kernel, but in domains that can interact without knowing their semantics Some developed domains: data-flow, discreteevent. More domains are user-insertable. Winter-Spring 2001 Codesign of Embedded Systems 12

Synthesis n n n What’s Synthesis/Co-Synthesis System-level Partitioning Hardware synthesis Software synthesis and retargetable compilation Interface synthesis Winter-Spring 2001 Codesign of Embedded Systems 13

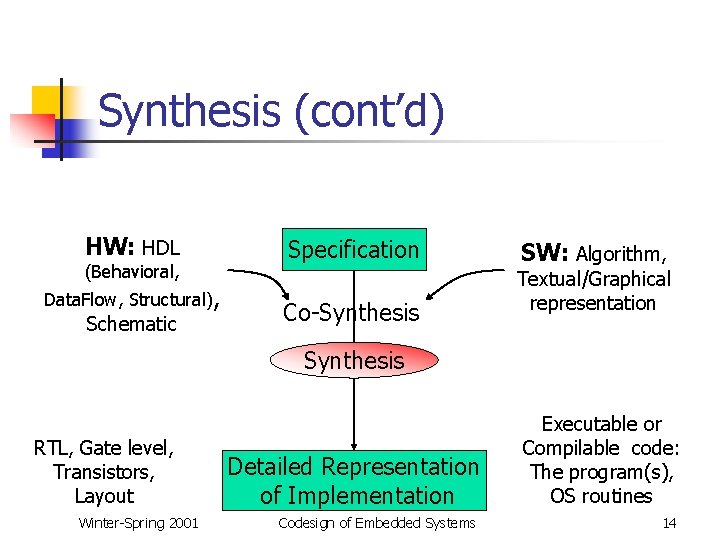

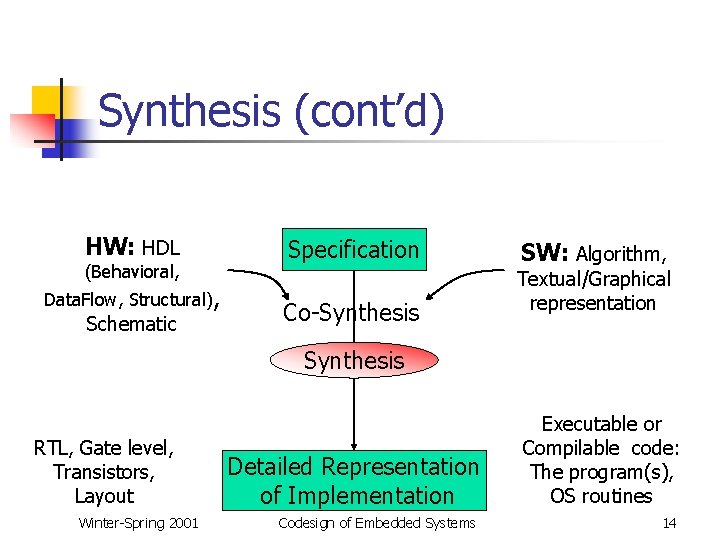

Synthesis (cont’d) HW: HDL (Behavioral, Data. Flow, Structural), Schematic Specification Co-Synthesis SW: Algorithm, Textual/Graphical representation Synthesis RTL, Gate level, Transistors, Layout Winter-Spring 2001 Detailed Representation of Implementation Executable or Compilable code: The program(s), OS routines Codesign of Embedded Systems 14

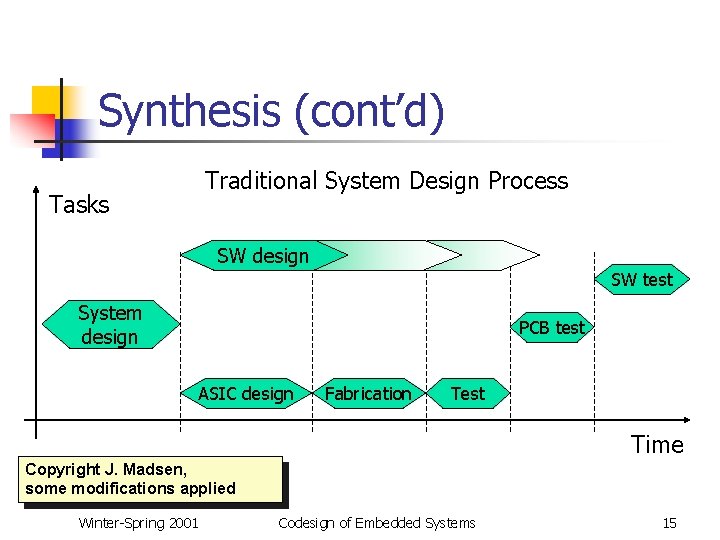

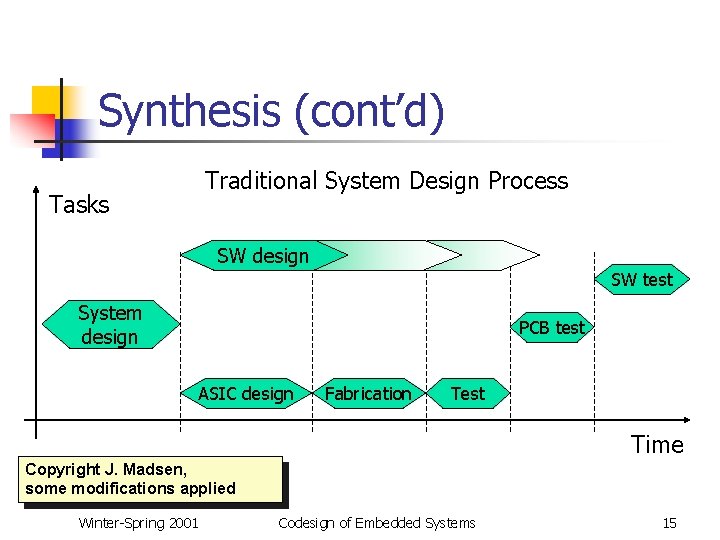

Synthesis (cont’d) Traditional System Design Process Tasks SW design SW test System design PCB test ASIC design Fabrication Test Time Copyright J. Madsen, some modifications applied Winter-Spring 2001 Codesign of Embedded Systems 15

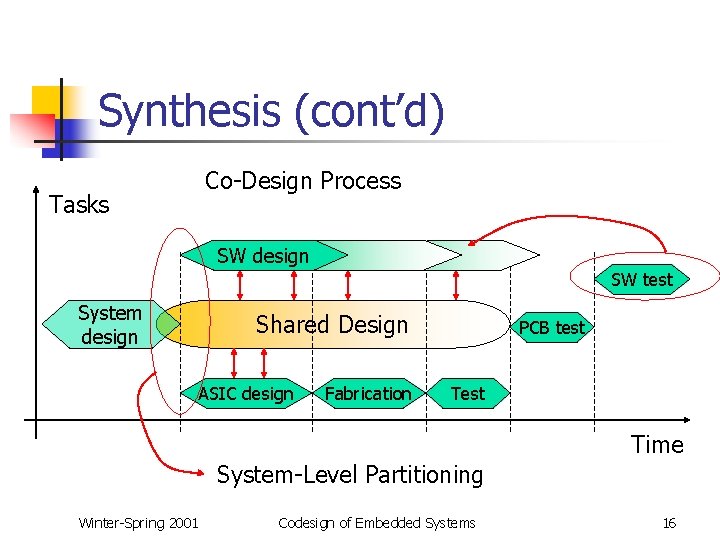

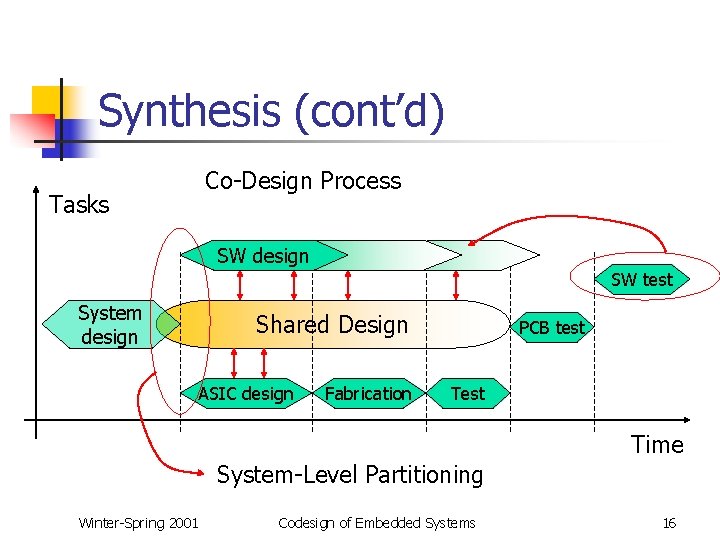

Synthesis (cont’d) Co-Design Process Tasks SW design SW test System design Shared Design ASIC design Fabrication PCB test Time System-Level Partitioning Winter-Spring 2001 Codesign of Embedded Systems 16

Synthesis (cont’d) Some special cases n Synthesis of ISPs n n HLS techniques are applicable to high-level models of processors Many high-level decisions are not automatic yet n Example: Pipeline organization, Datapath design n Reason: n n Few new ISPs compared to ASICs Performance is very sensitive High production-volume recovers high design costs HLS is, however, used for control functions Winter-Spring 2001 Codesign of Embedded Systems 17

Synthesis (cont’d) Some special cases n Design of compilers n Corresponds to the processor architecture n n n Compilers are co-designed with processors Automated tools for synthesis of pipeline control unit + compiler Synthesis of lumped embedded systems n n Natural evolution of HLS Uniform specification + manually or automatically partitioning into HW+SW+interface Winter-Spring 2001 Codesign of Embedded Systems 18

Synthesis (cont’d) System-Level Partitioning n One extreme: Full HW solution n Other extreme: Full SW solution n n High performance due to Parallelism High cost and long time of ASIC fabrication High-performance, low-cost processors Operation serialization Lack of support for specific tasks Best solution is a mix of HW and SW Winter-Spring 2001 Codesign of Embedded Systems 19

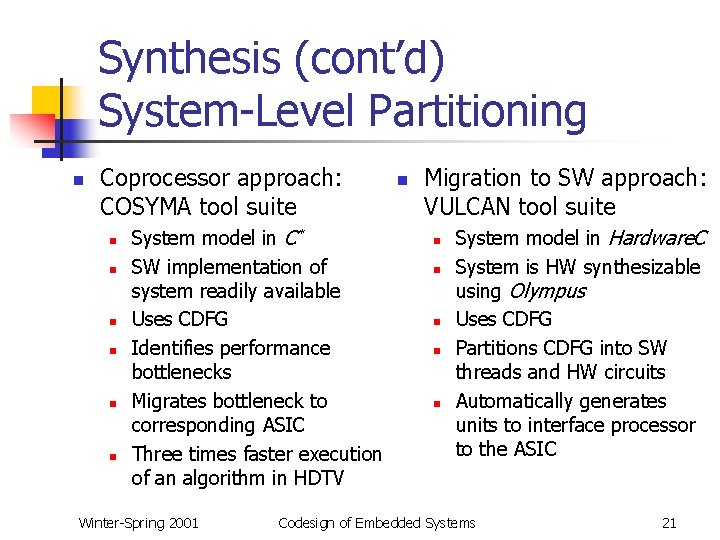

Synthesis (cont’d) System-Level Partitioning n Major approaches to Partitioning n n n Co-synthesis of dedicated co-processors for SW execution acceleration Migration of non-critical functions to SW Complementary objectives n n Maximize performance Minimize system cost, subject to required performance Winter-Spring 2001 Codesign of Embedded Systems 20

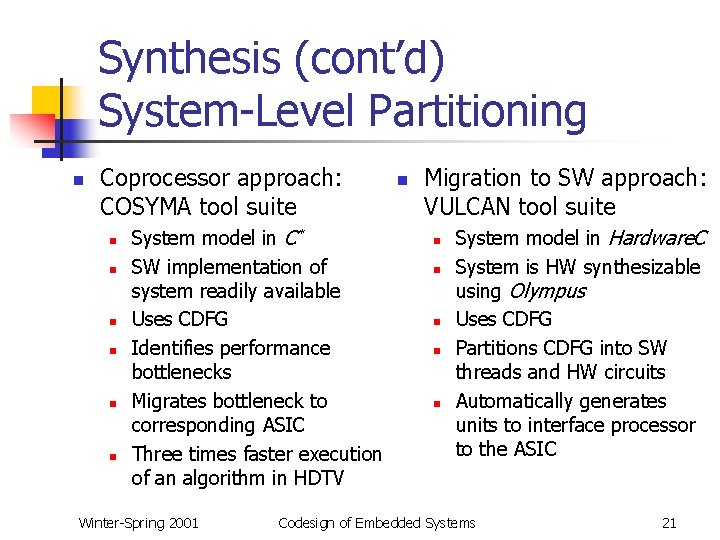

Synthesis (cont’d) System-Level Partitioning n Coprocessor approach: COSYMA tool suite n n n System model in C* SW implementation of system readily available Uses CDFG Identifies performance bottlenecks Migrates bottleneck to corresponding ASIC Three times faster execution of an algorithm in HDTV Winter-Spring 2001 n Migration to SW approach: VULCAN tool suite n n n System model in Hardware. C System is HW synthesizable using Olympus Uses CDFG Partitions CDFG into SW threads and HW circuits Automatically generates units to interface processor to the ASIC Codesign of Embedded Systems 21

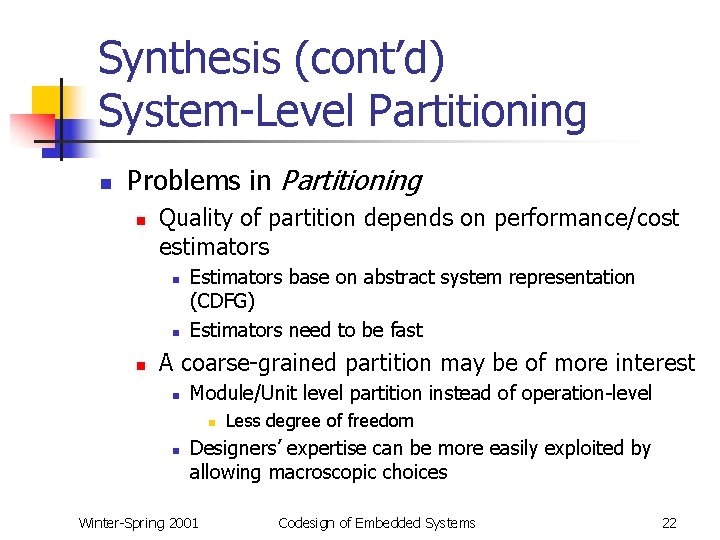

Synthesis (cont’d) System-Level Partitioning n Problems in Partitioning n Quality of partition depends on performance/cost estimators n n n Estimators base on abstract system representation (CDFG) Estimators need to be fast A coarse-grained partition may be of more interest n Module/Unit level partition instead of operation-level n n Less degree of freedom Designers’ expertise can be more easily exploited by allowing macroscopic choices Winter-Spring 2001 Codesign of Embedded Systems 22

Synthesis (cont’d) HW synthesis n Mostly based on Graph-theoretic approaches and algorithms n (To be presented as an extra class) Winter-Spring 2001 Codesign of Embedded Systems 23

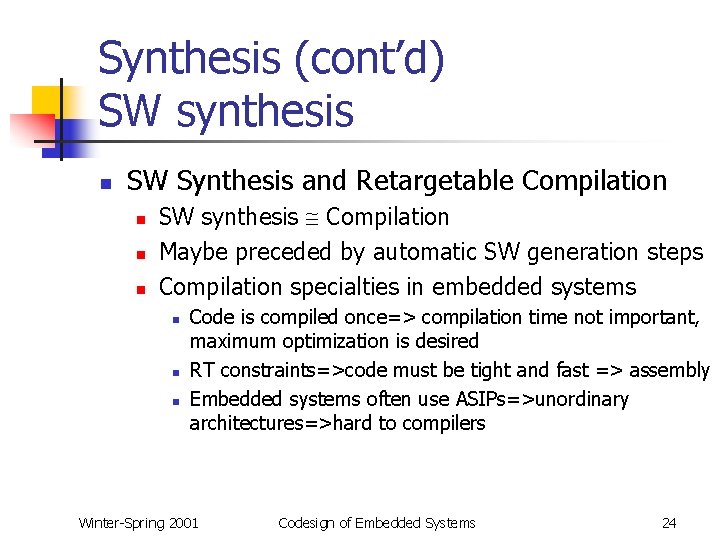

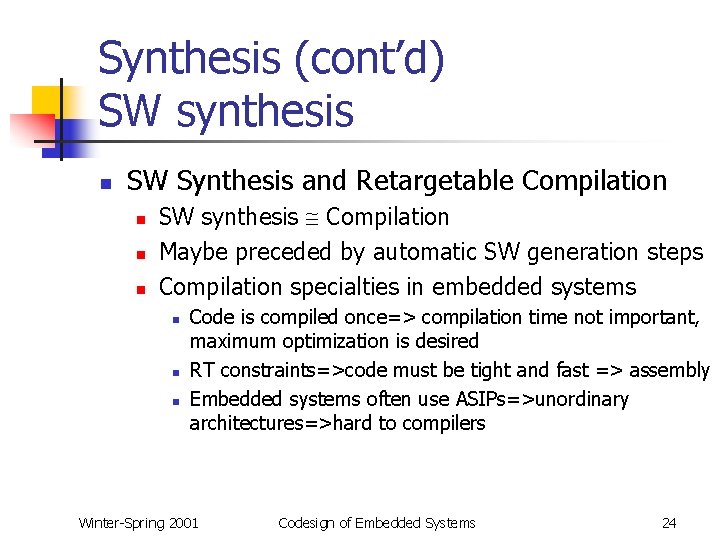

Synthesis (cont’d) SW synthesis n SW Synthesis and Retargetable Compilation n SW synthesis Compilation Maybe preceded by automatic SW generation steps Compilation specialties in embedded systems n n n Code is compiled once=> compilation time not important, maximum optimization is desired RT constraints=>code must be tight and fast => assembly Embedded systems often use ASIPs=>unordinary architectures=>hard to compilers Winter-Spring 2001 Codesign of Embedded Systems 24

Synthesis (cont’d) SW synthesis n Retargetable Compilers n Developing a new compiler for each new ASIP is unreasonable=>retargetable compilers n Classification according to retargeting time n Portable compiler n Compiler-compiler n Machine-independent compiler Winter-Spring 2001 Codesign of Embedded Systems 25

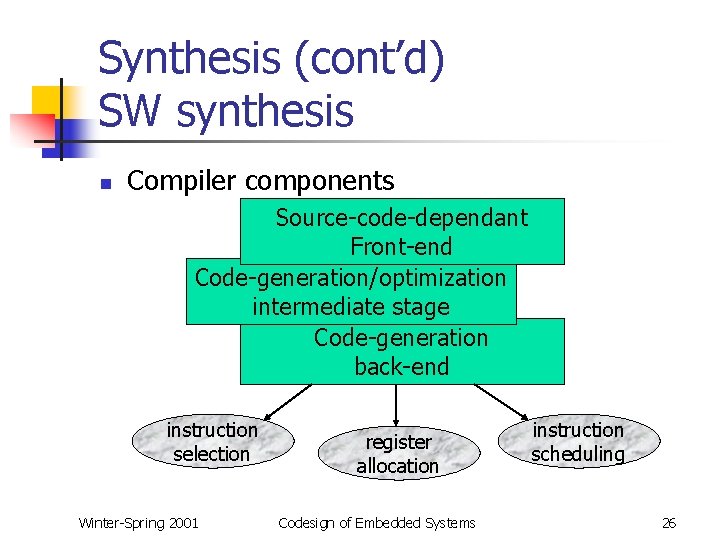

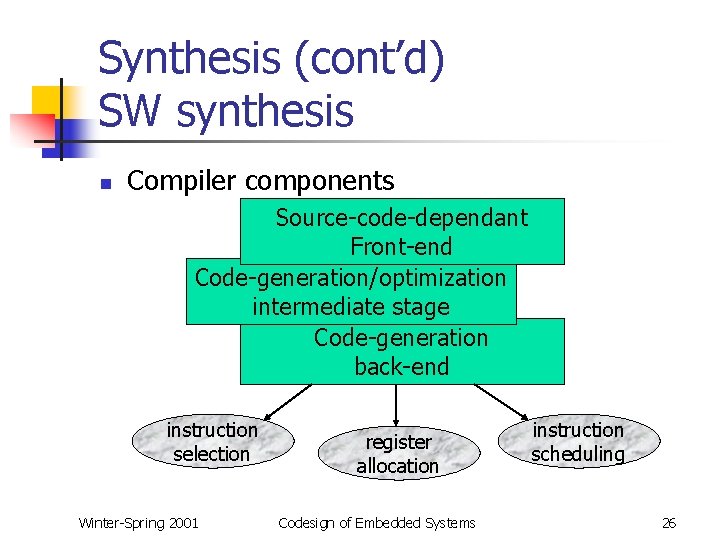

Synthesis (cont’d) SW synthesis n Compiler components Source-code-dependant Front-end Code-generation/optimization intermediate stage Code-generation back-end instruction selection Winter-Spring 2001 register allocation Codesign of Embedded Systems instruction scheduling 26

Synthesis (cont’d) SW synthesis n Other topics in retargetable compilation n Micro-programmed ASIPs n Compacting the micro-program n n Winter-Spring 2001 Determine ILP (Instruction-Level Parallelism) Encoding of each word Codesign of Embedded Systems 27

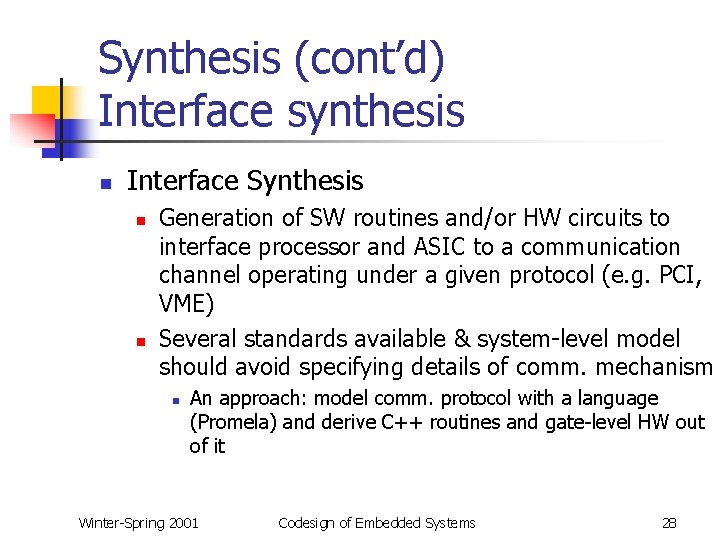

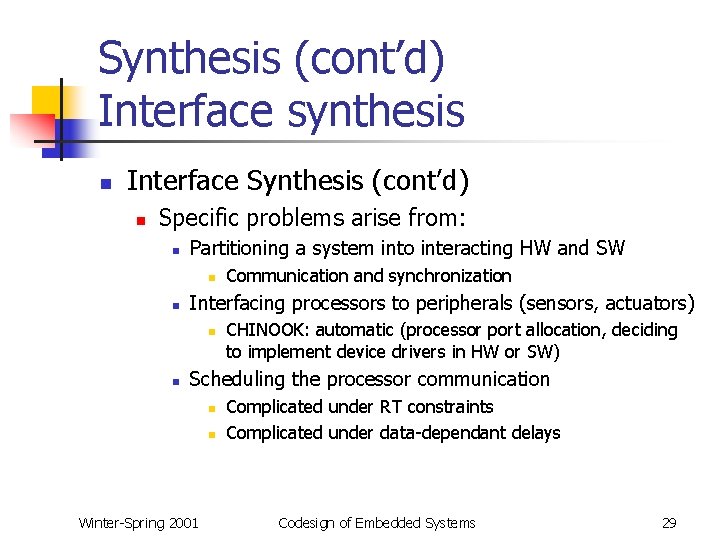

Synthesis (cont’d) Interface synthesis n Interface Synthesis n n Generation of SW routines and/or HW circuits to interface processor and ASIC to a communication channel operating under a given protocol (e. g. PCI, VME) Several standards available & system-level model should avoid specifying details of comm. mechanism n An approach: model comm. protocol with a language (Promela) and derive C++ routines and gate-level HW out of it Winter-Spring 2001 Codesign of Embedded Systems 28

Synthesis (cont’d) Interface synthesis n Interface Synthesis (cont’d) n Specific problems arise from: n Partitioning a system into interacting HW and SW n n Interfacing processors to peripherals (sensors, actuators) n n Communication and synchronization CHINOOK: automatic (processor port allocation, deciding to implement device drivers in HW or SW) Scheduling the processor communication n n Winter-Spring 2001 Complicated under RT constraints Complicated under data-dependant delays Codesign of Embedded Systems 29

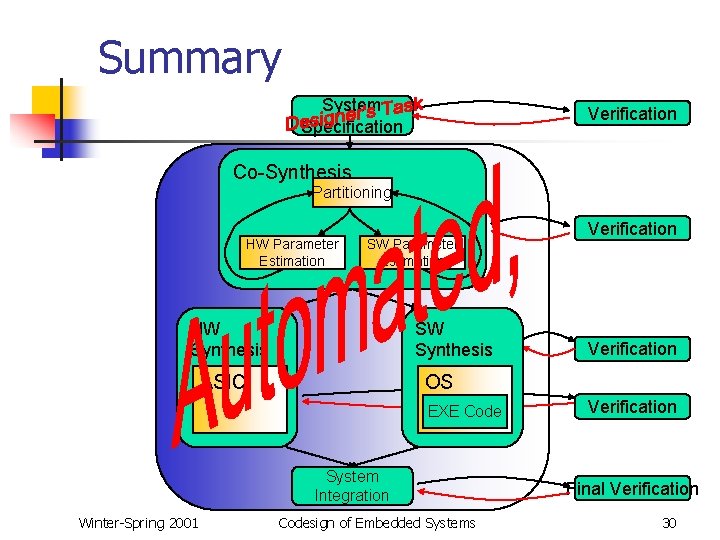

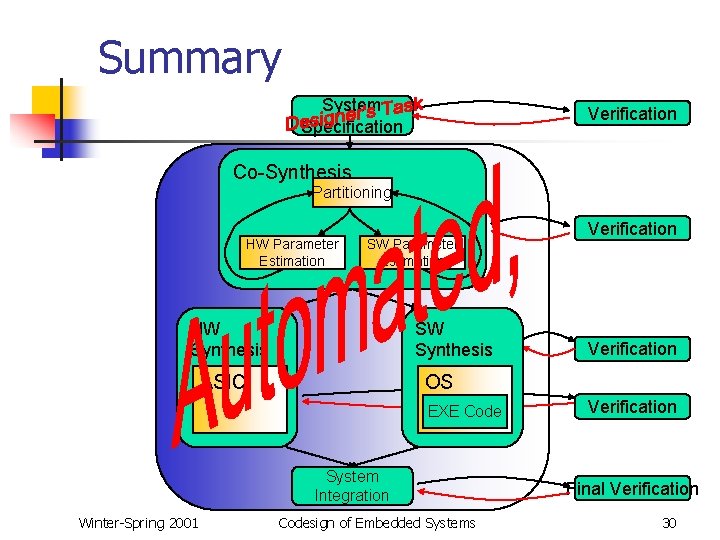

Summary System Specification Verification Co-Synthesis Partitioning HW Parameter Estimation SW Parameter Estimation HW Synthesis SW Synthesis ASIC Verification OS EXE Code System Integration Winter-Spring 2001 Verification Codesign of Embedded Systems Verification Final Verification 30

Summary (cont’d) n n n CAD Tools are essential to progress in electrical system design Design of digital components of systems benefit from HW/SW Codesign At present, Codesign CAD support is still weak n n n Co-simulators commercially available Others (co-synthesis, verification, IDEs, etc) growing up Impact of CAD tools on system-level design will be more profound than their impact on IC design Winter-Spring 2001 Codesign of Embedded Systems 31

What we learned today n CAD tools are essential to success in this field n n They must support Modeling (specification), Validation, and Synthesis in a single integrated environment Major constituents of codesign n Modeling (Specification( Validation (Verification( Synthesis (Co-synthesis( n n Winter-Spring 2001 System-level partitioning HW synthesis SW synthesis Interface synthesis Codesign of Embedded Systems 32

Complementary notes n Postponed Verilog Short Course n Instructor: n n Farshid Soheili, Emad Semicon. Co. First session n Saturday: Esfand 13 th n n “CE-202” room, 15 o’clock Take the first chapter of De. Micheli’s book from “Publications Room” Winter-Spring 2001 Codesign of Embedded Systems 33

Complementary notes (cont’d) n Optional paper presentation n Any subtopic from last and today programme: n n Computer-Aided Codesign Methods and Tools Project n Today is date to choose and announce your partner for the final project Winter-Spring 2001 Codesign of Embedded Systems 34