COMPUTER SYSTEMS An Integrated Approach to Architecture and

- Slides: 34

COMPUTER SYSTEMS An Integrated Approach to Architecture and Operating Systems Chapter 10 Input/Output and Stable Storage ©Copyright 2008 Umakishore Ramachandran and William D. Leahy Jr.

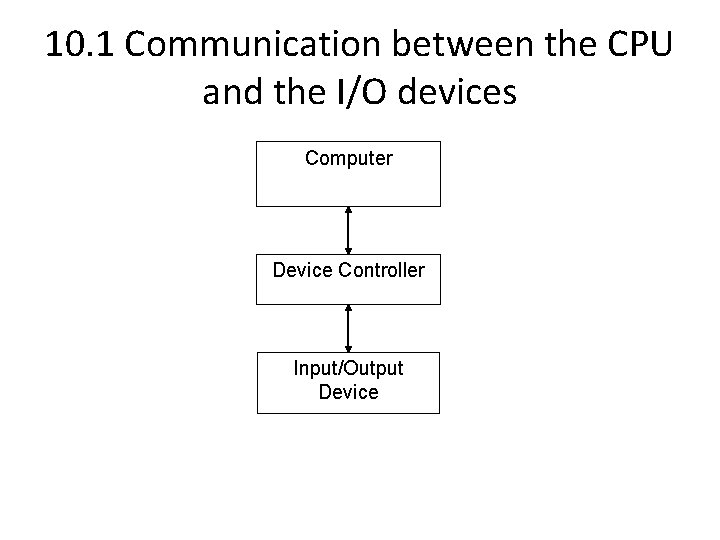

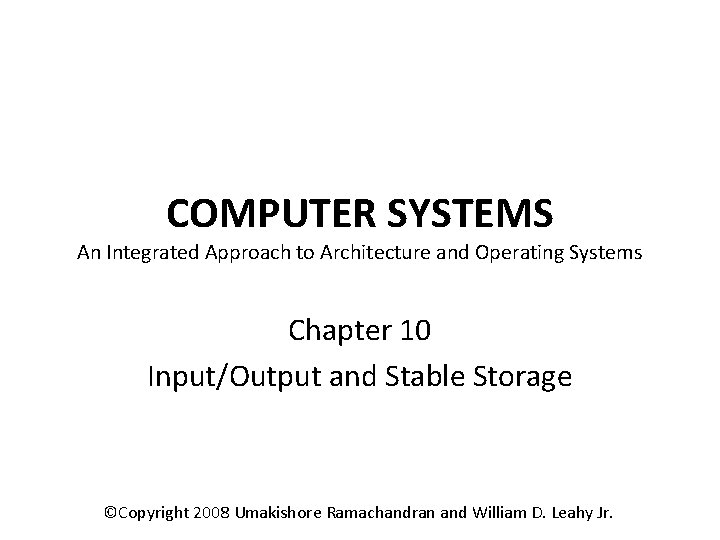

10. 1 Communication between the CPU and the I/O devices Computer Device Controller Input/Output Device

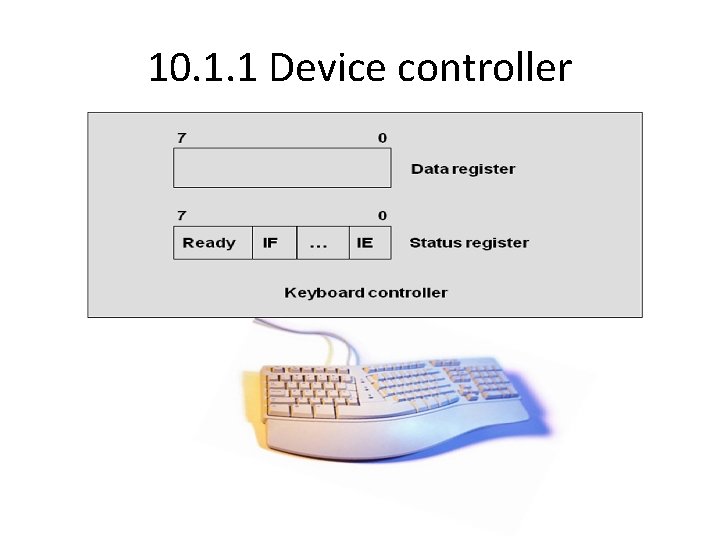

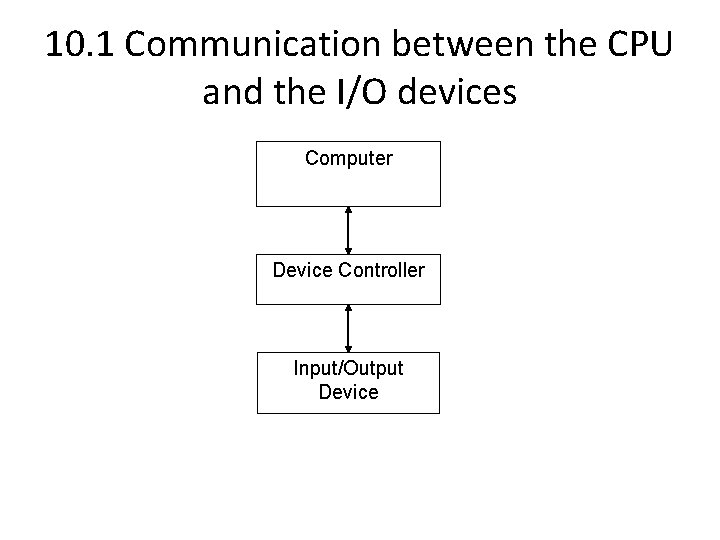

10. 1. 1 Device controller

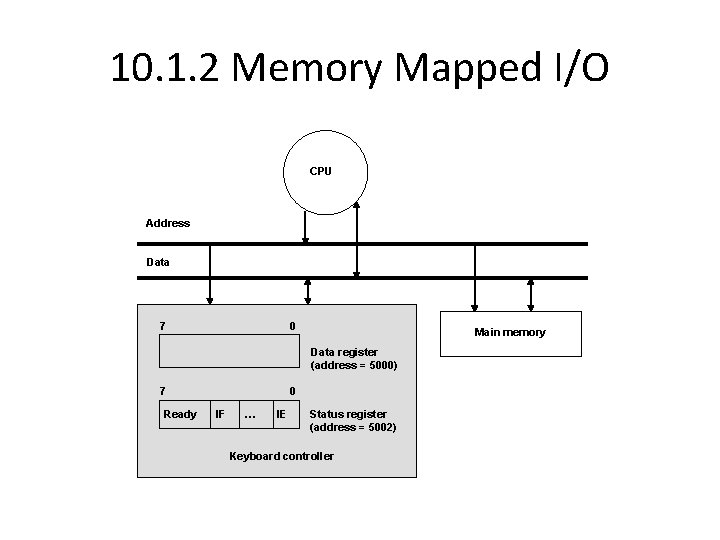

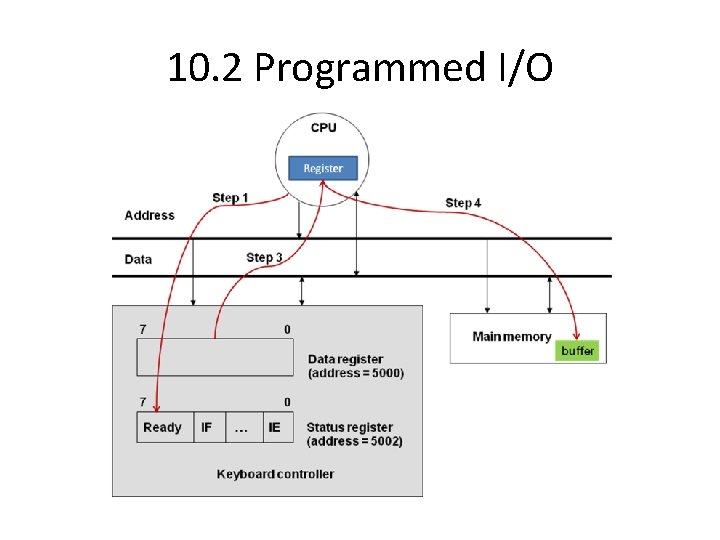

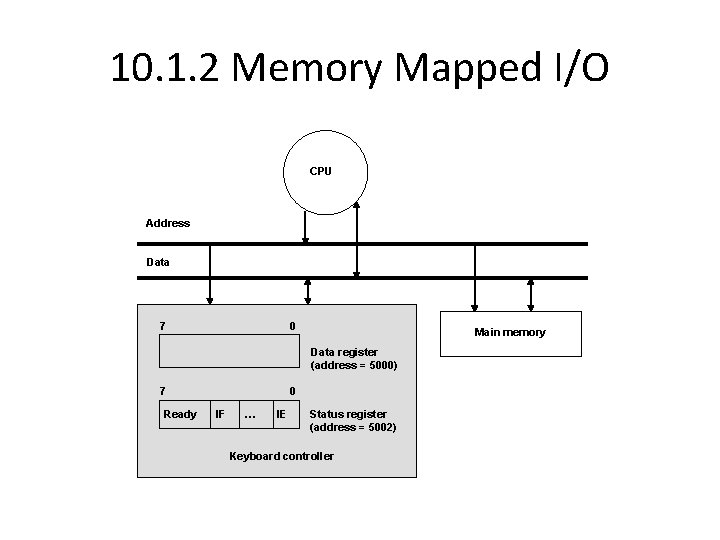

10. 1. 2 Memory Mapped I/O CPU Address Data 7 0 Main memory Data register (address = 5000) 7 Ready 0 IF … IE Status register (address = 5002) Keyboard controller

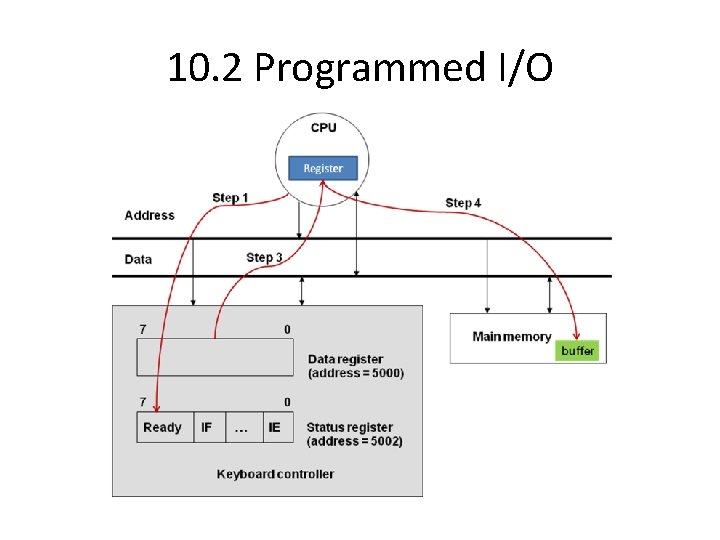

10. 2 Programmed I/O

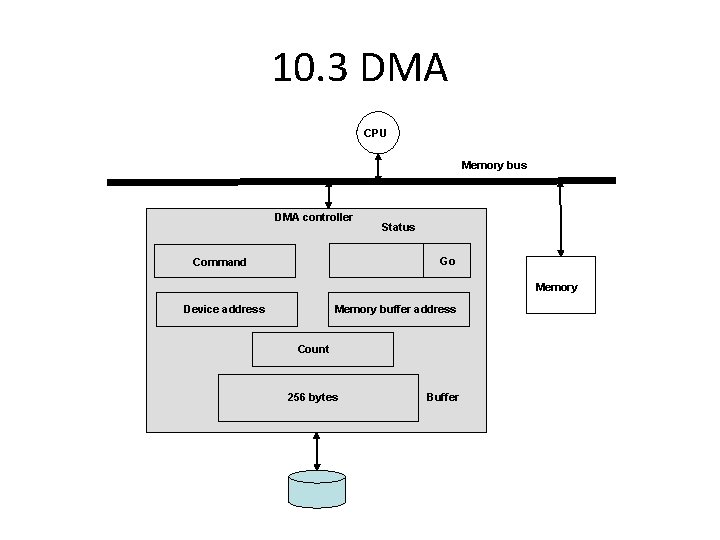

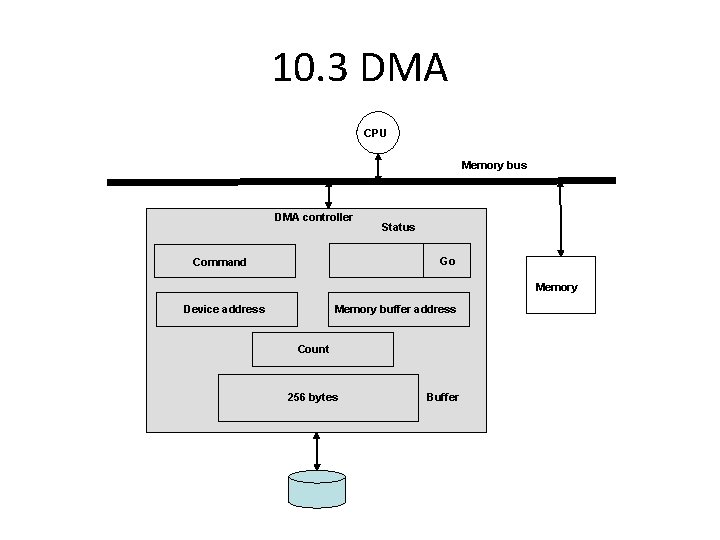

10. 3 DMA CPU Memory bus DMA controller Status Go Command Memory Device address Memory buffer address Count 256 bytes Buffer

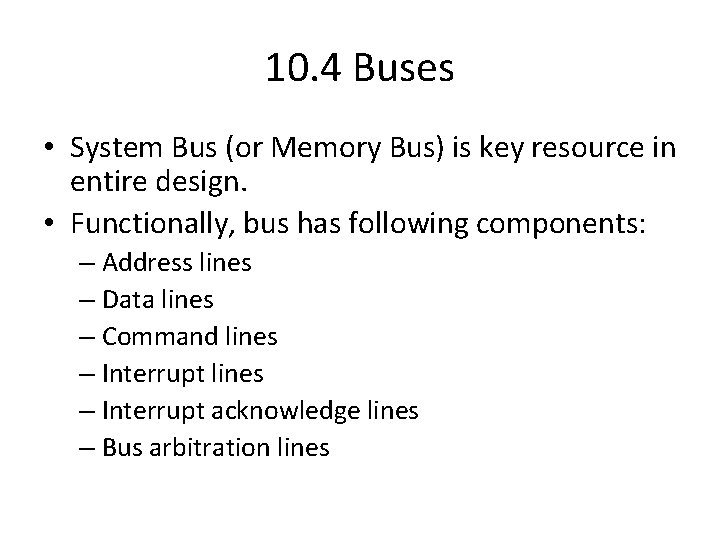

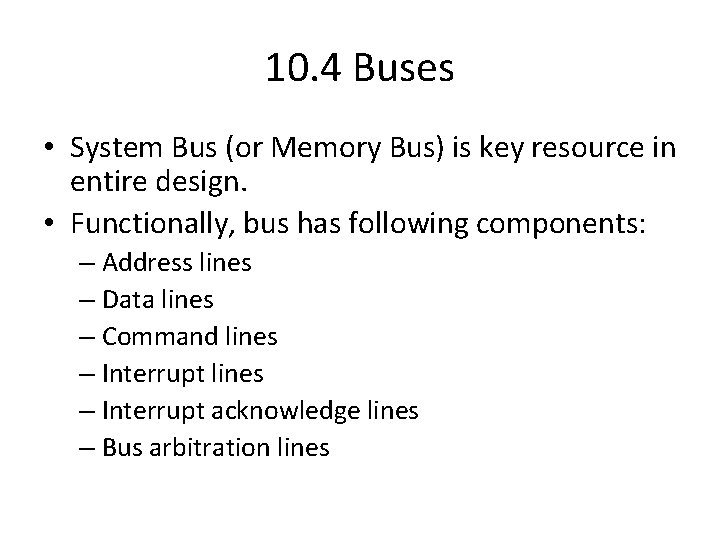

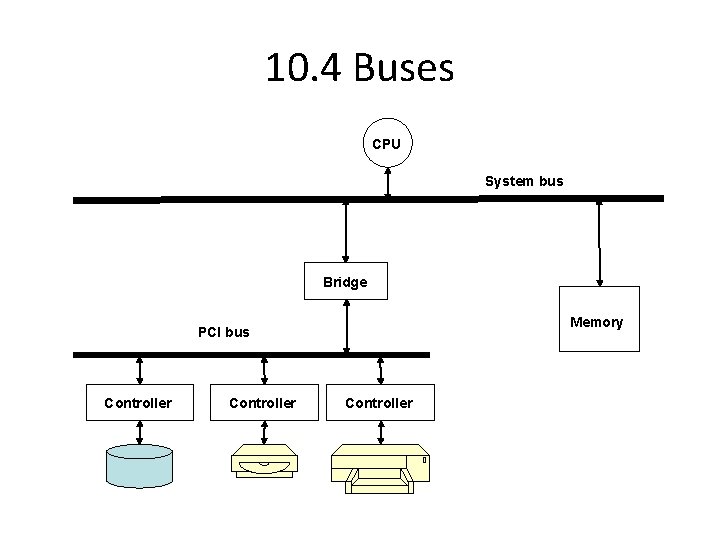

10. 4 Buses • System Bus (or Memory Bus) is key resource in entire design. • Functionally, bus has following components: – Address lines – Data lines – Command lines – Interrupt acknowledge lines – Bus arbitration lines

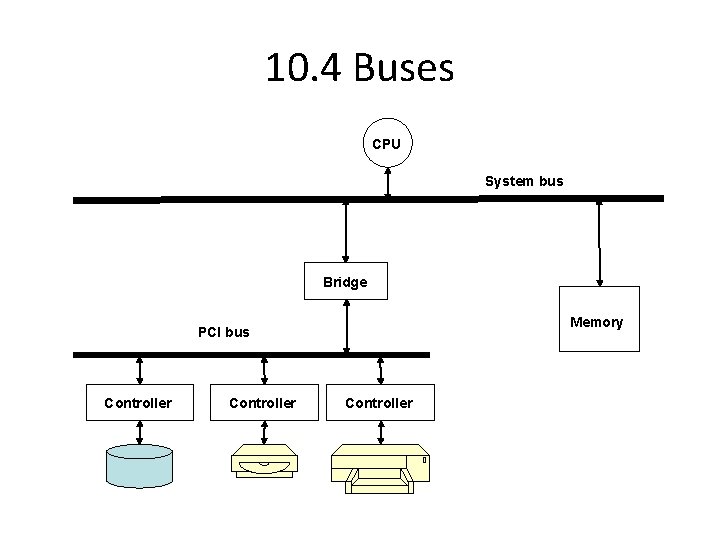

10. 4 Buses CPU System bus Bridge Memory PCI bus Controller

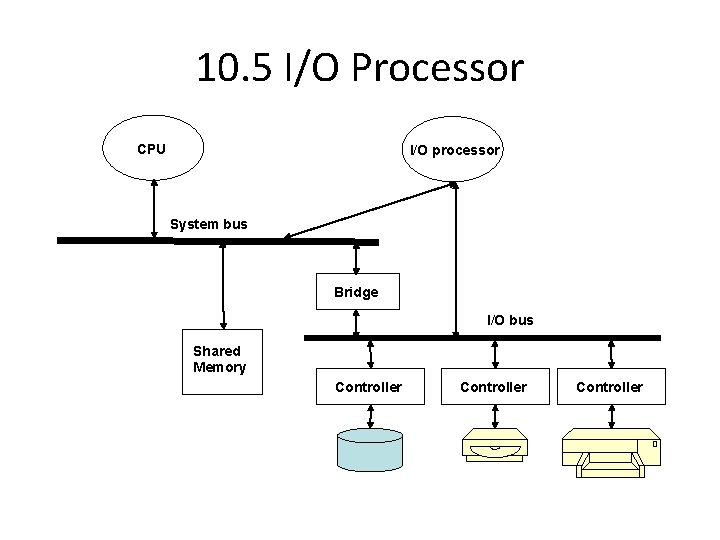

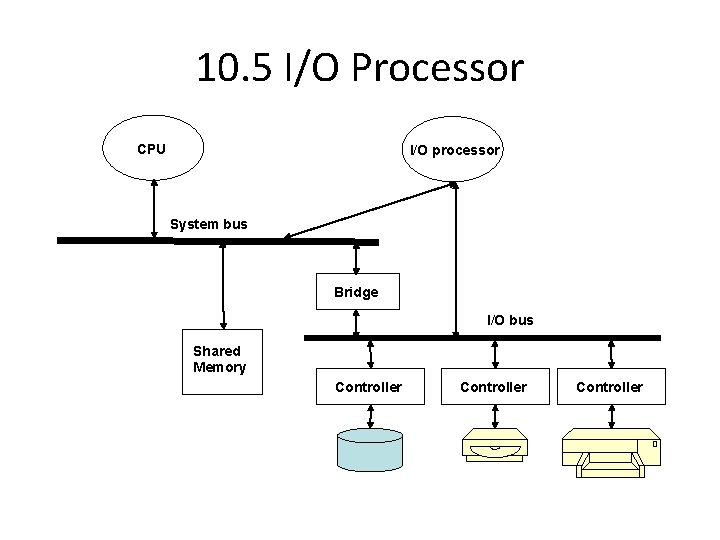

10. 5 I/O Processor CPU I/O processor System bus Bridge I/O bus Shared Memory Controller

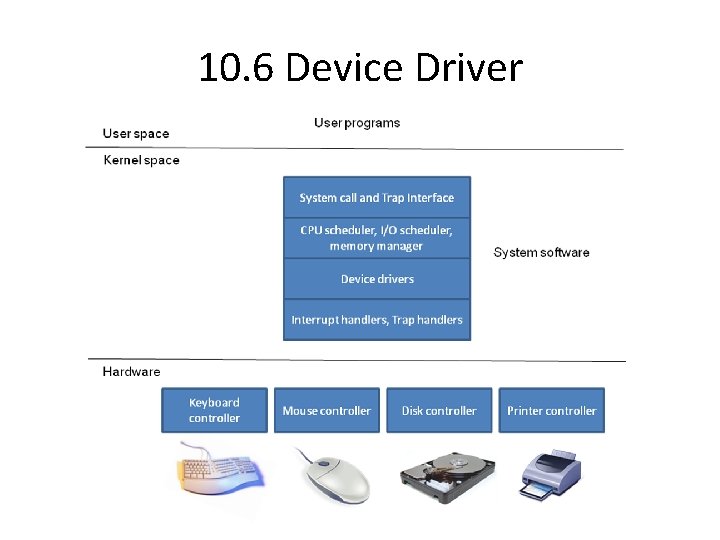

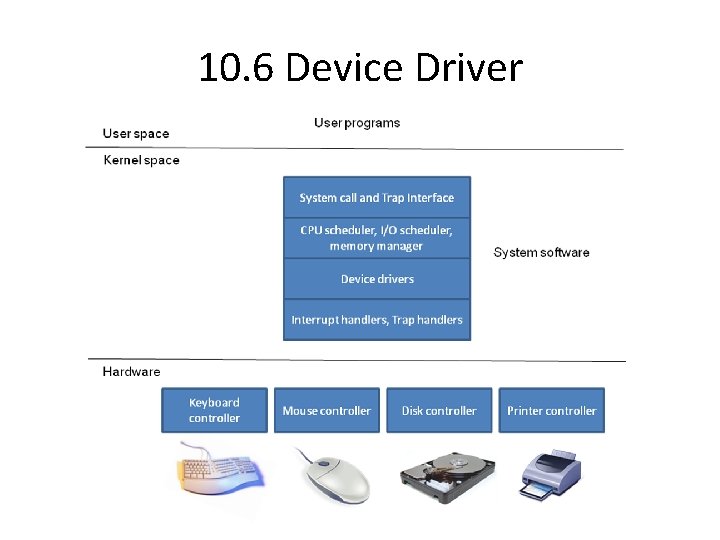

10. 6 Device Driver

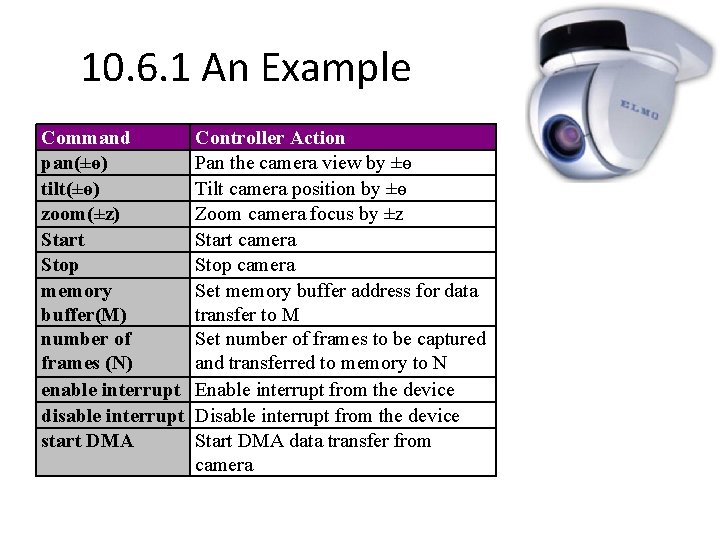

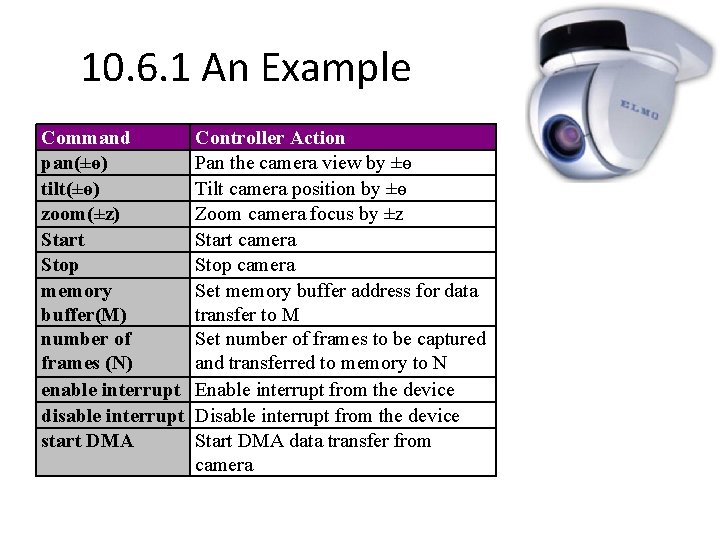

10. 6. 1 An Example Command pan(±ɵ) tilt(±ɵ) zoom(±z) Start Stop memory buffer(M) number of frames (N) enable interrupt disable interrupt start DMA Controller Action Pan the camera view by ±ɵ Tilt camera position by ±ɵ Zoom camera focus by ±z Start camera Stop camera Set memory buffer address for data transfer to M Set number of frames to be captured and transferred to memory to N Enable interrupt from the device Disable interrupt from the device Start DMA data transfer from camera

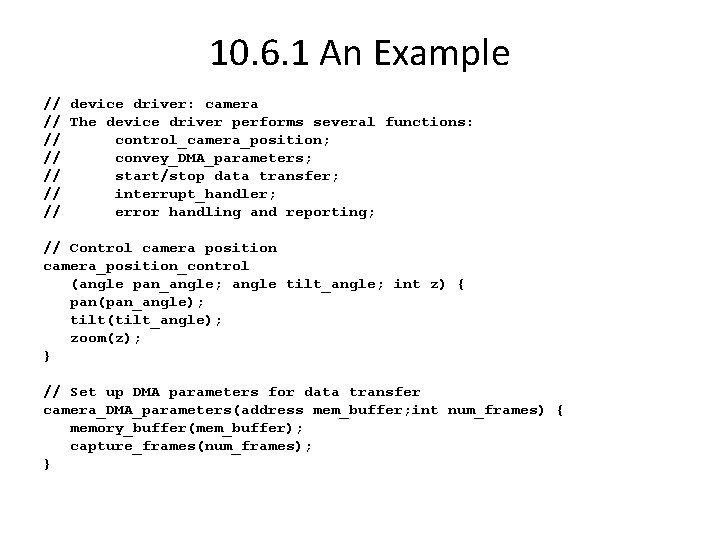

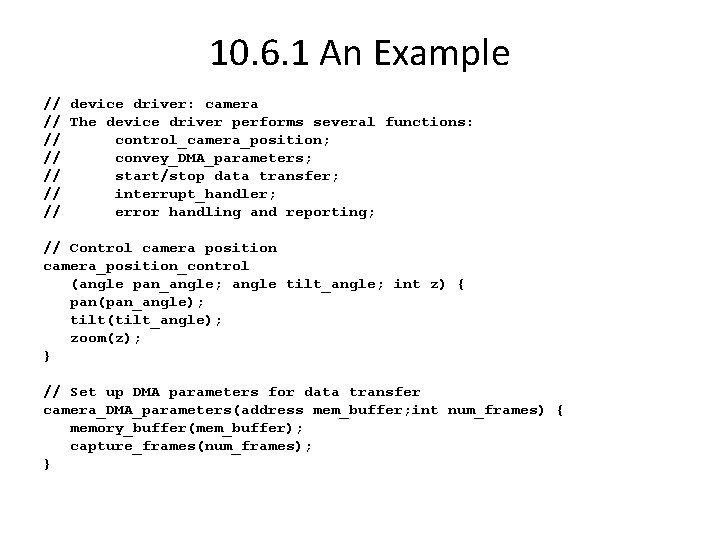

10. 6. 1 An Example // device driver: camera // The device driver performs several functions: // control_camera_position; // convey_DMA_parameters; // start/stop data transfer; // interrupt_handler; // error handling and reporting; // Control camera position camera_position_control (angle pan_angle; angle tilt_angle; int z) { pan(pan_angle); tilt(tilt_angle); zoom(z); } // Set up DMA parameters for data transfer camera_DMA_parameters(address mem_buffer; int num_frames) { memory_buffer(mem_buffer); capture_frames(num_frames); }

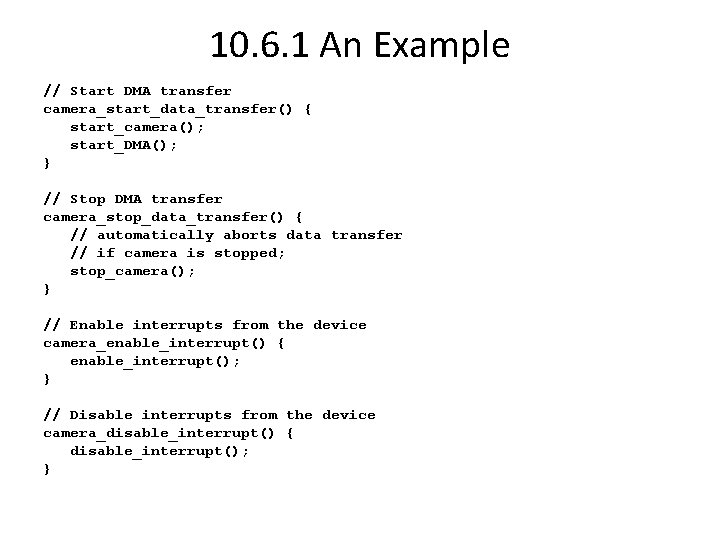

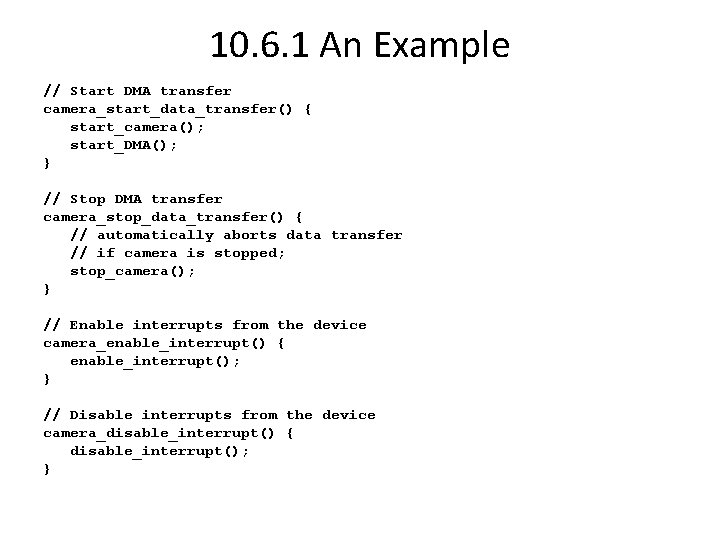

10. 6. 1 An Example // Start DMA transfer camera_start_data_transfer() { start_camera(); start_DMA(); } // Stop DMA transfer camera_stop_data_transfer() { // automatically aborts data transfer // if camera is stopped; stop_camera(); } // Enable interrupts from the device camera_enable_interrupt() { enable_interrupt(); } // Disable interrupts from the device camera_disable_interrupt() { disable_interrupt(); }

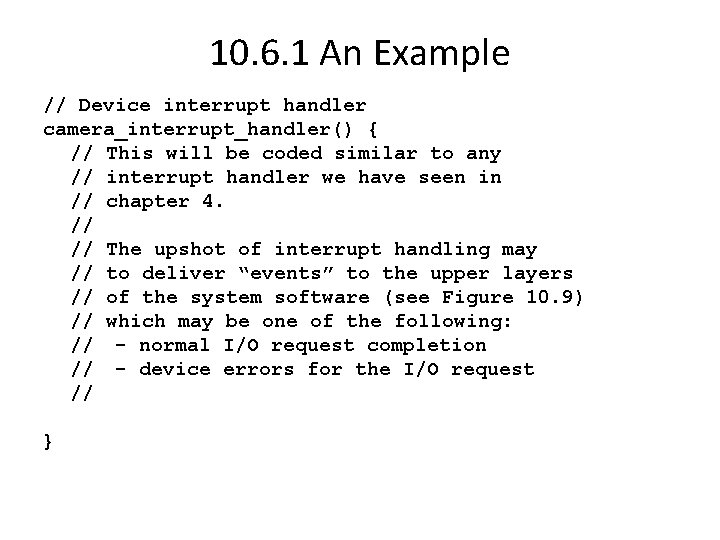

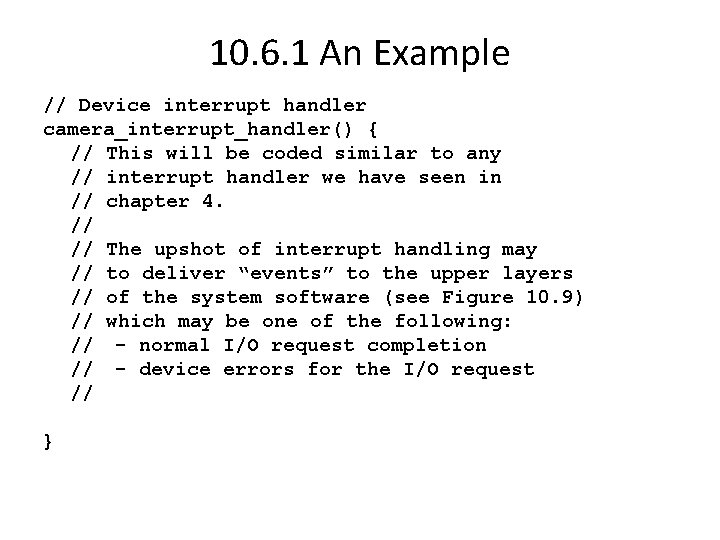

10. 6. 1 An Example // Device interrupt handler camera_interrupt_handler() { // This will be coded similar to any // interrupt handler we have seen in // chapter 4. // // The upshot of interrupt handling may // to deliver “events” to the upper layers // of the system software (see Figure 10. 9) // which may be one of the following: // - normal I/O request completion // - device errors for the I/O request // }

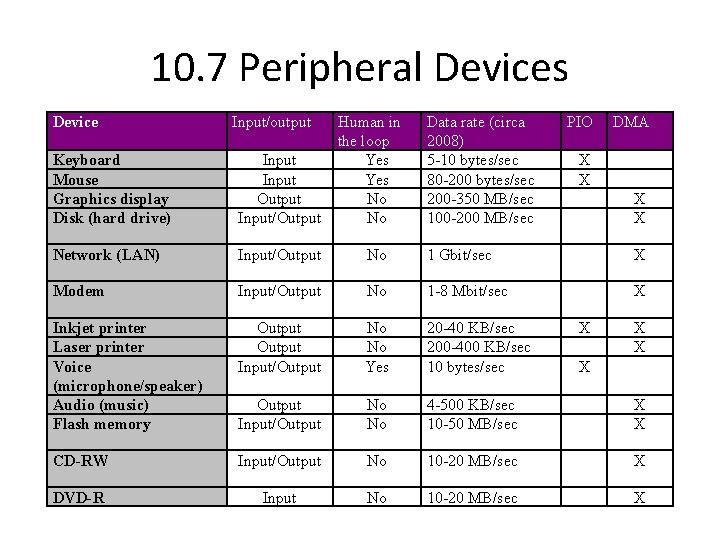

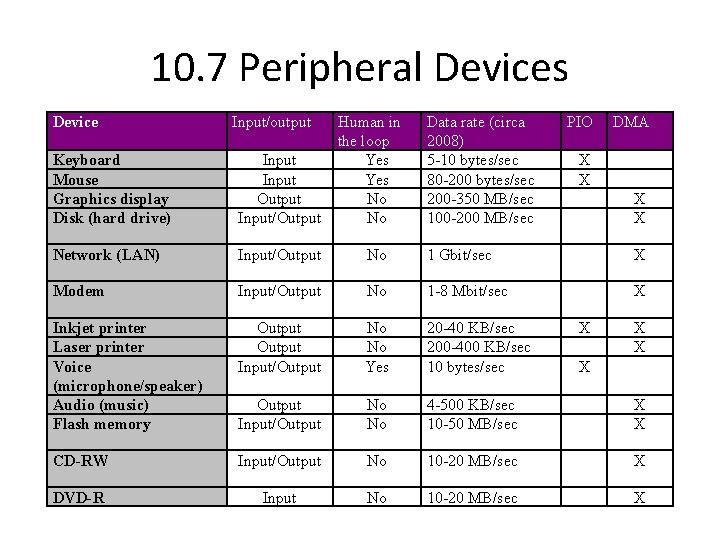

10. 7 Peripheral Devices Device Input/output Human in the loop Yes No No Data rate (circa 2008) 5 -10 bytes/sec 80 -200 bytes/sec 200 -350 MB/sec 100 -200 MB/sec PIO DMA Keyboard Mouse Graphics display Disk (hard drive) Input Output Input/Output X X Network (LAN) Input/Output No 1 Gbit/sec X Modem Input/Output No 1 -8 Mbit/sec X Inkjet printer Laser printer Voice (microphone/speaker) Audio (music) Flash memory Output Input/Output No No Yes 20 -40 KB/sec 200 -400 KB/sec 10 bytes/sec Output Input/Output No No 4 -500 KB/sec 10 -50 MB/sec X X CD-RW Input/Output No 10 -20 MB/sec X DVD-R Input No 10 -20 MB/sec X X X X

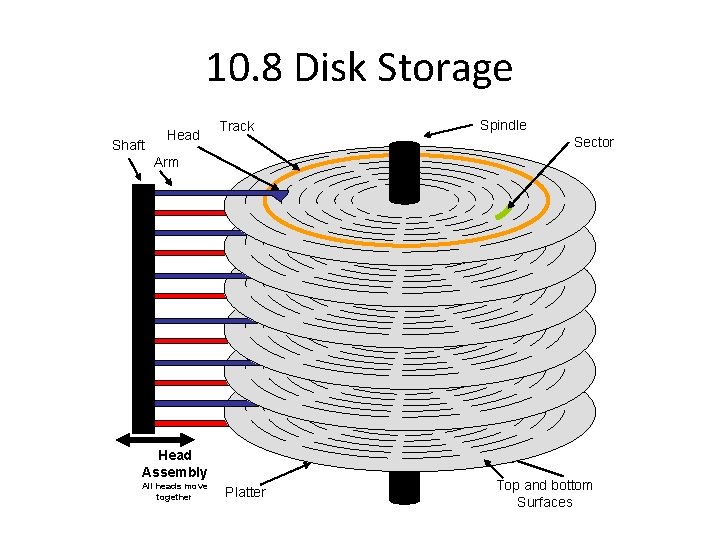

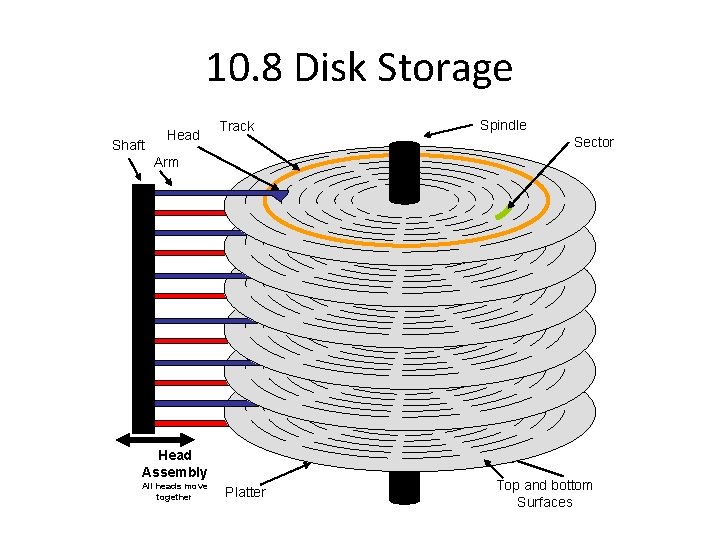

10. 8 Disk Storage Shaft Head Track Spindle Sector Arm Head Assembly All heads move together Platter Top and bottom Surfaces

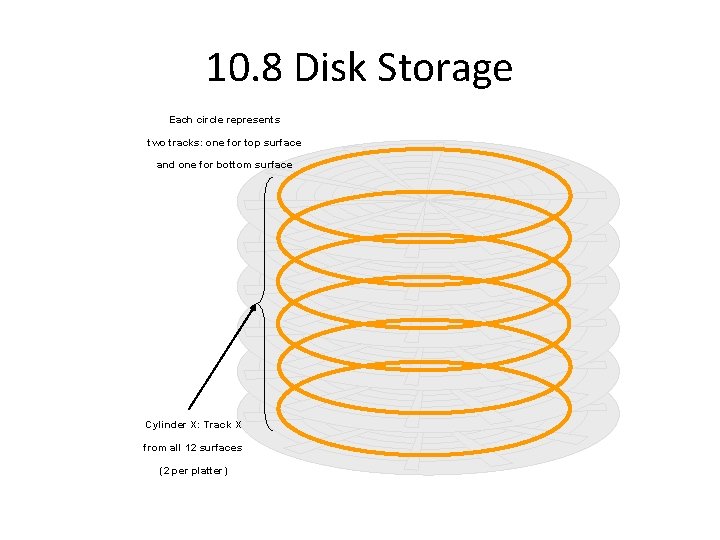

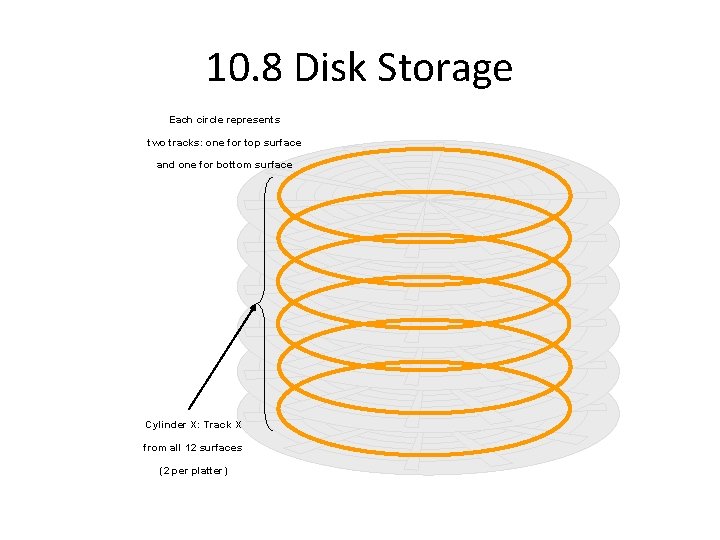

10. 8 Disk Storage Each circle represents two tracks: one for top surface and one for bottom surface Cylinder X: Track X from all 12 surfaces (2 per platter)

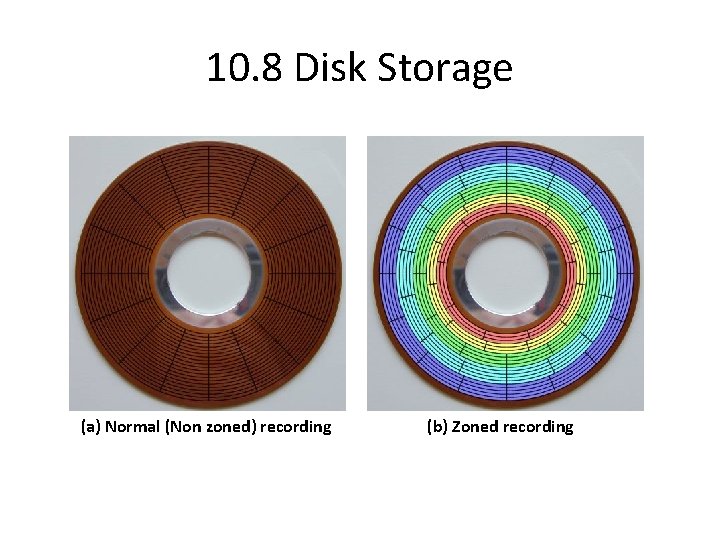

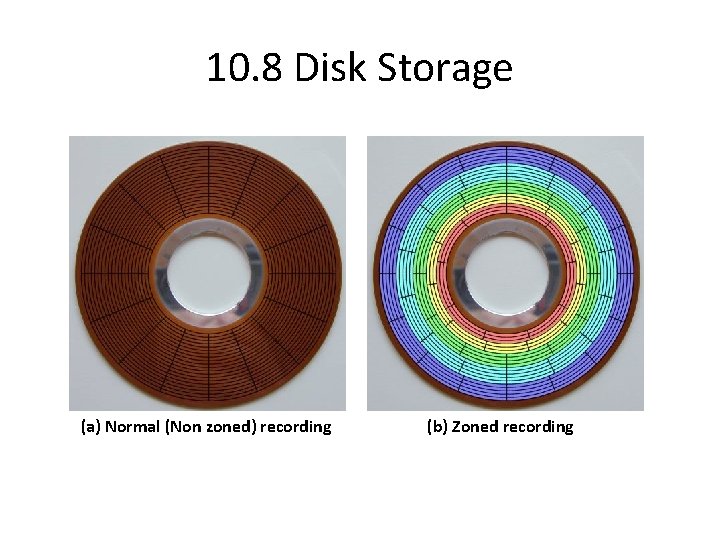

10. 8 Disk Storage (a) Normal (Non zoned) recording (b) Zoned recording

10. 8. 1 Saga of Disk Technology Disk recording: (a) Longitudinal recording; (b) PMR

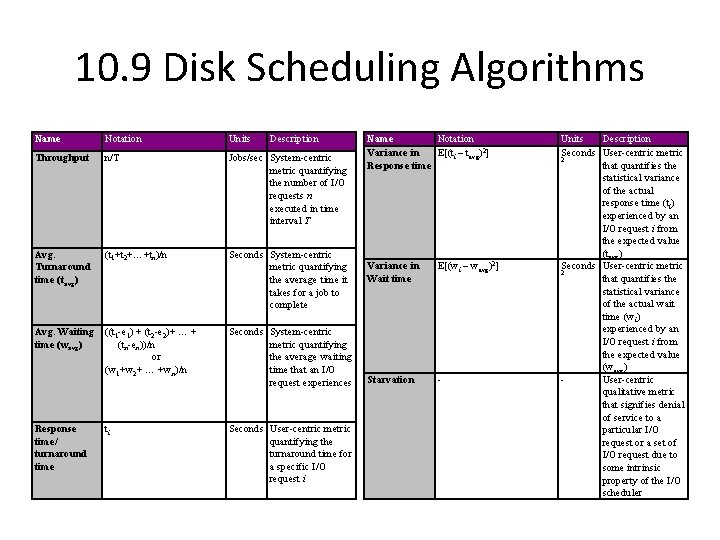

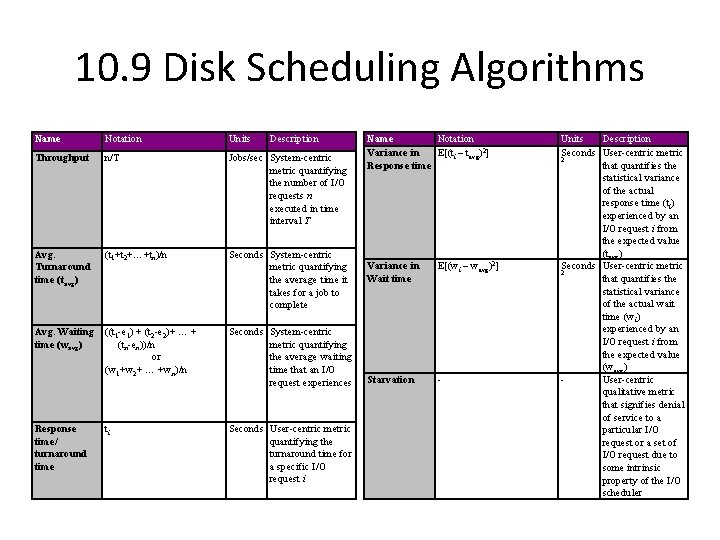

10. 9 Disk Scheduling Algorithms Name Notation Units Throughput n/T Jobs/sec System-centric metric quantifying the number of I/O requests n executed in time interval T Avg. Turnaround time (tavg) (t 1+t 2+…+tn)/n Seconds System-centric metric quantifying the average time it takes for a job to complete Avg. Waiting time (wavg) ((t 1 -e 1) + (t 2 -e 2)+ … + (tn-en))/n or (w 1+w 2+ … +wn)/n Seconds System-centric metric quantifying the average waiting time that an I/O request experiences ti Seconds User-centric metric quantifying the turnaround time for a specific I/O request i Response time/ turnaround time Description Name Notation Variance in E[(ti – tavg)2] Response time Variance in Wait time E[(wi – wavg)2] Starvation - Units Description Seconds User-centric metric 2 that quantifies the statistical variance of the actual response time (ti) experienced by an I/O request i from the expected value (tavg) Seconds User-centric metric 2 that quantifies the statistical variance of the actual wait time (wi) experienced by an I/O request i from the expected value (wavg) User-centric qualitative metric that signifies denial of service to a particular I/O request or a set of I/O request due to some intrinsic property of the I/O scheduler

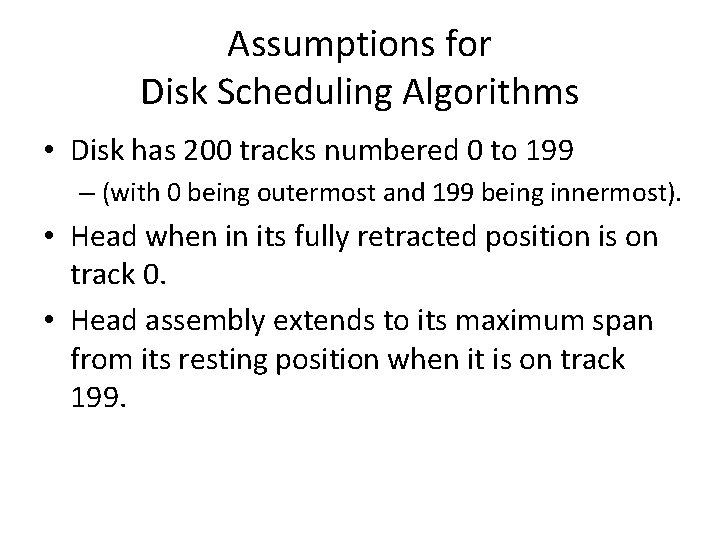

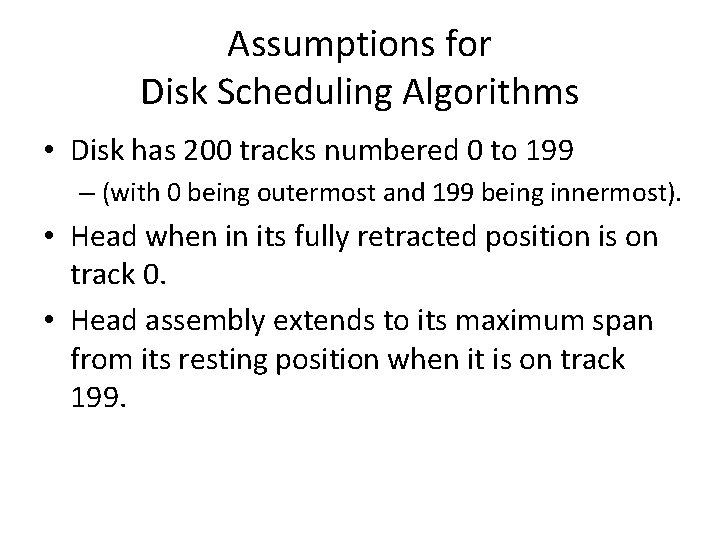

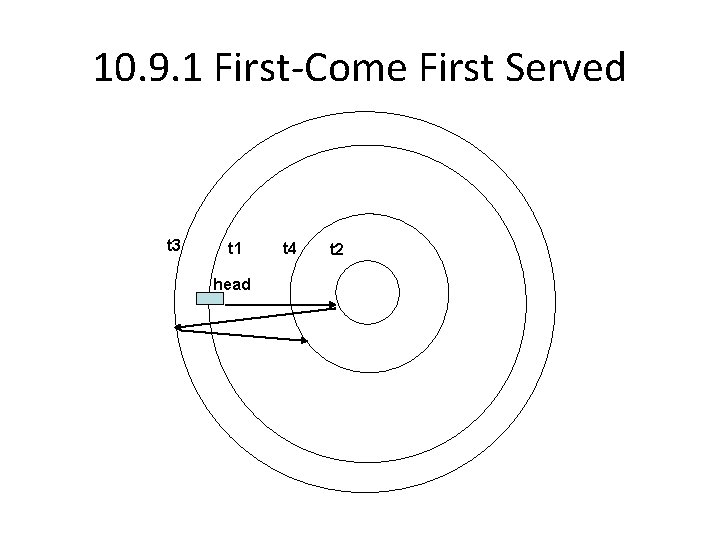

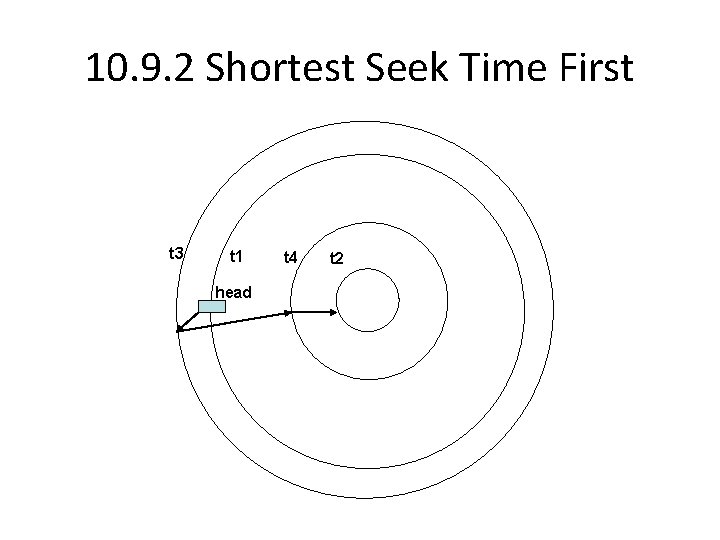

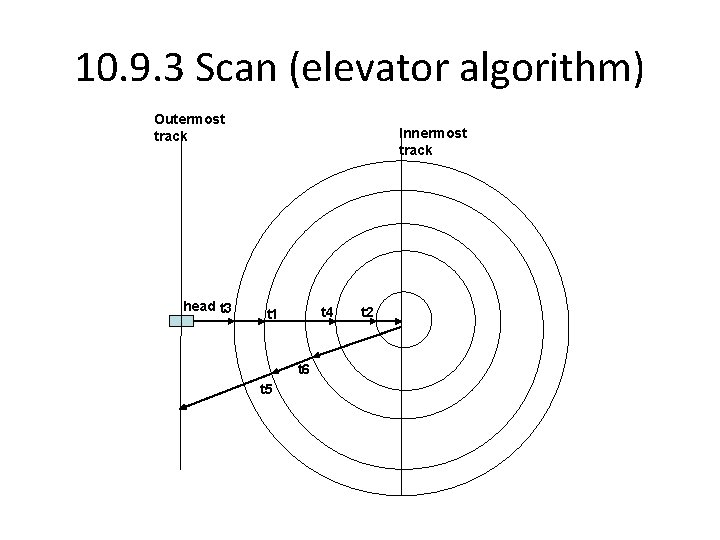

Assumptions for Disk Scheduling Algorithms • Disk has 200 tracks numbered 0 to 199 – (with 0 being outermost and 199 being innermost). • Head when in its fully retracted position is on track 0. • Head assembly extends to its maximum span from its resting position when it is on track 199.

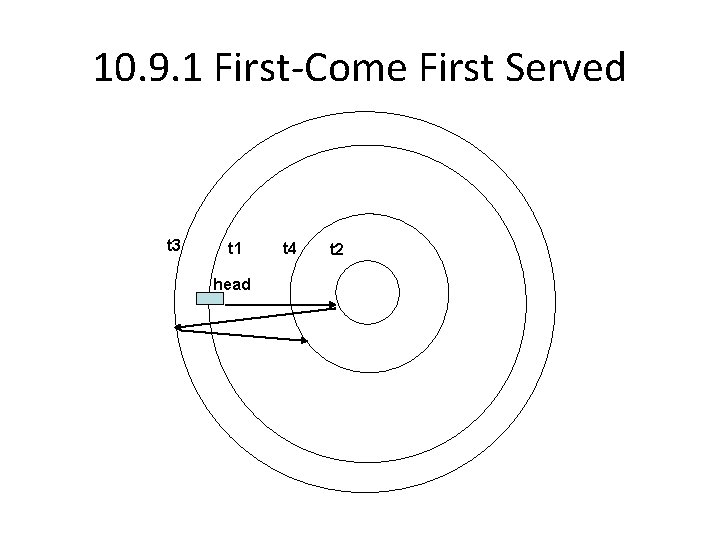

10. 9. 1 First-Come First Served t 3 t 1 head t 4 t 2

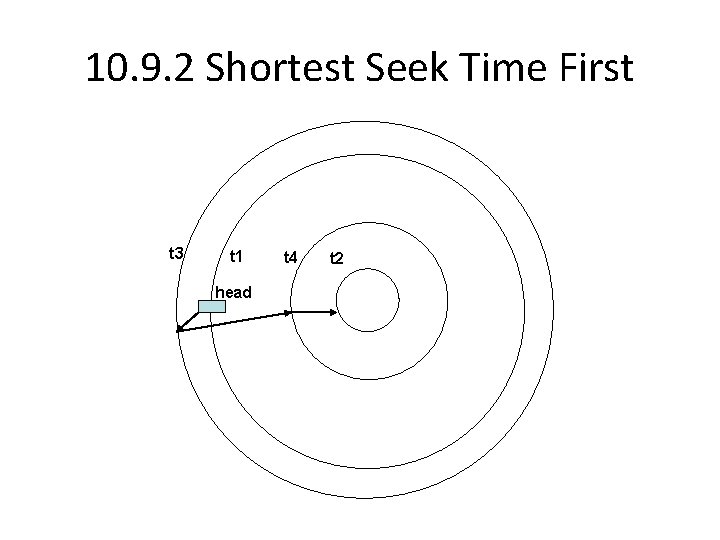

10. 9. 2 Shortest Seek Time First t 3 t 1 head t 4 t 2

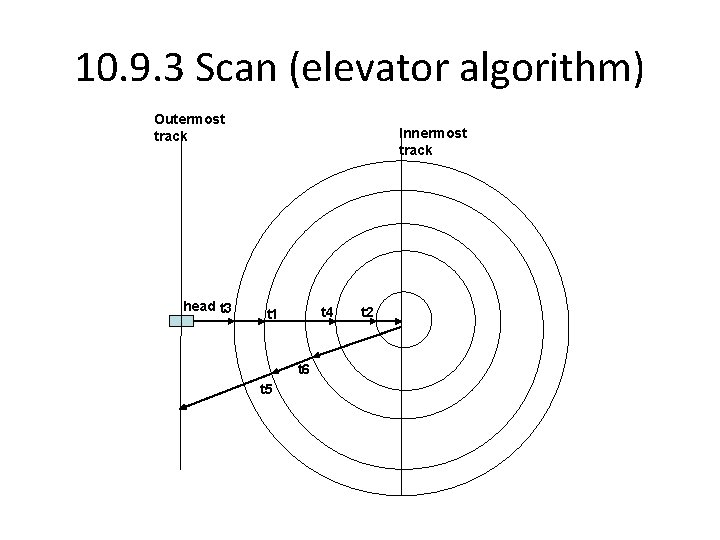

10. 9. 3 Scan (elevator algorithm) Outermost track head t 3 Innermost track t 4 t 1 t 6 t 5 t 2

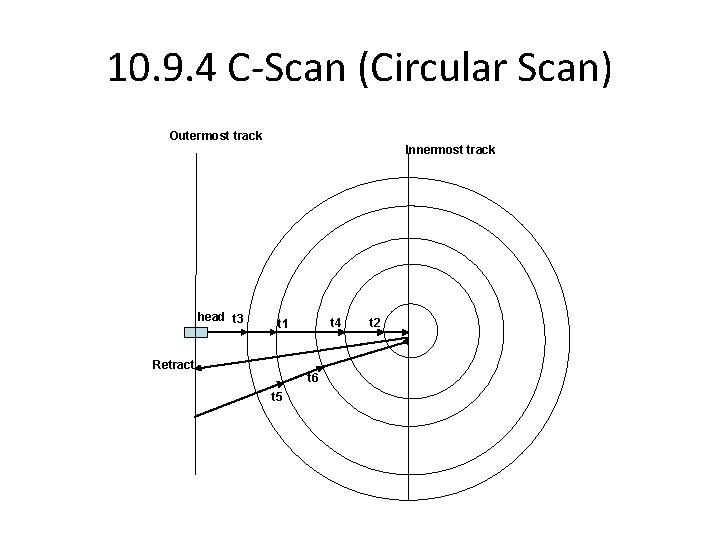

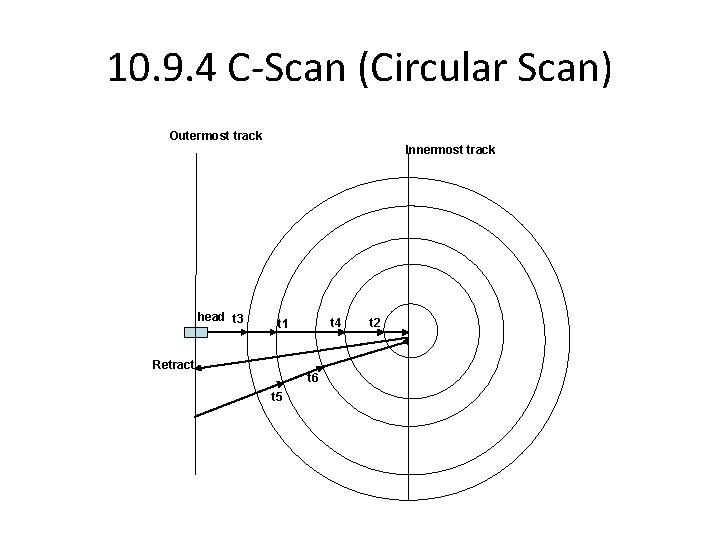

10. 9. 4 C-Scan (Circular Scan) Outermost track Innermost track head t 3 t 4 t 1 Retract t 6 t 5 t 2

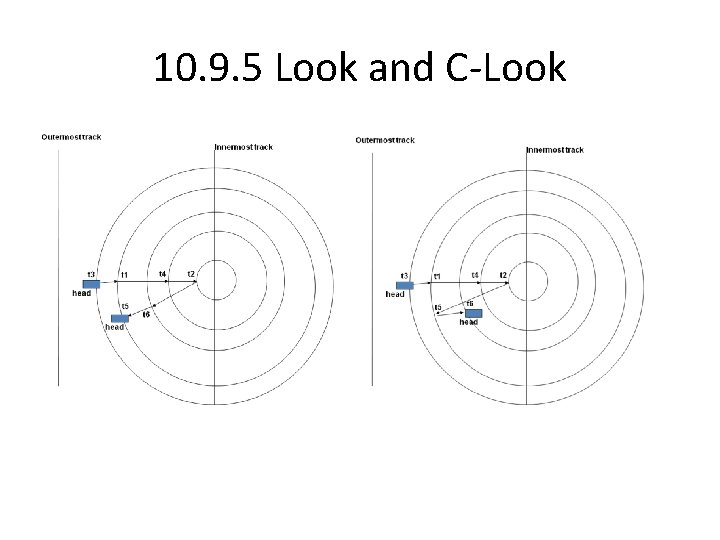

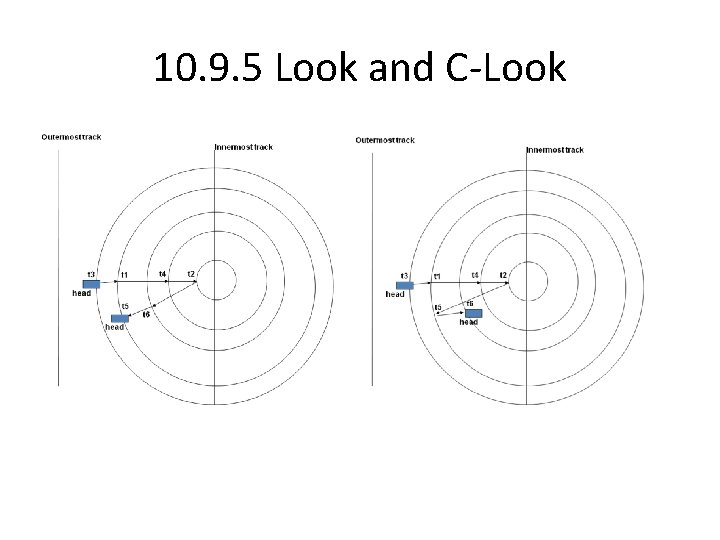

10. 9. 5 Look and C-Look

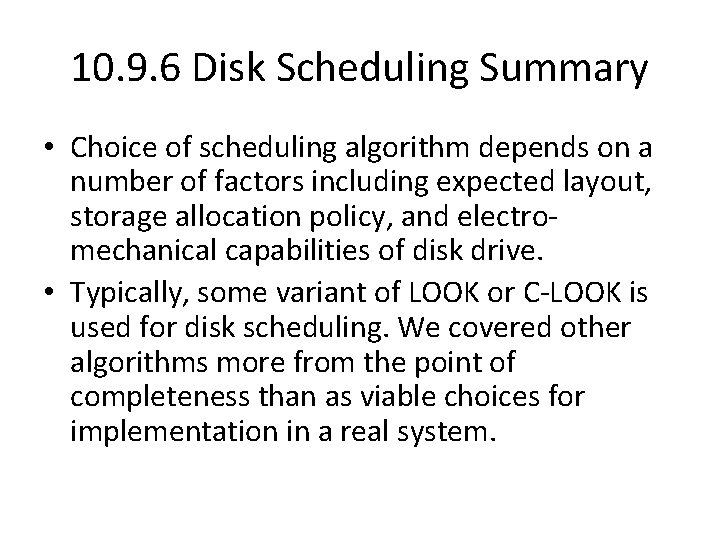

10. 9. 6 Disk Scheduling Summary • Choice of scheduling algorithm depends on a number of factors including expected layout, storage allocation policy, and electromechanical capabilities of disk drive. • Typically, some variant of LOOK or C-LOOK is used for disk scheduling. We covered other algorithms more from the point of completeness than as viable choices for implementation in a real system.

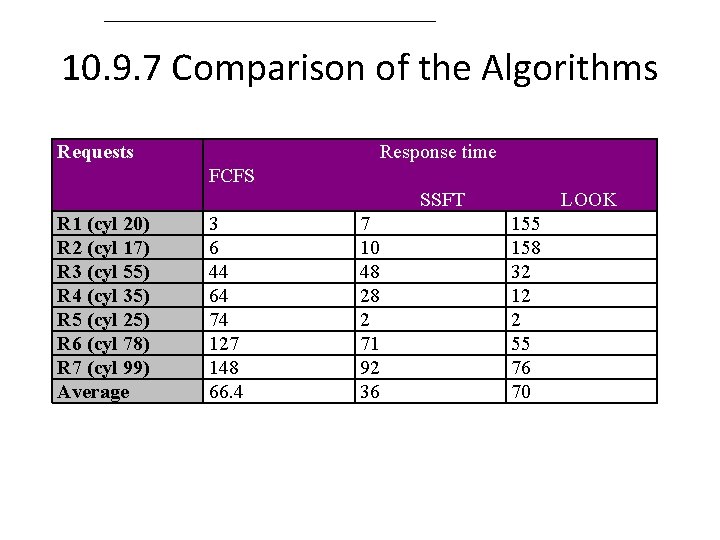

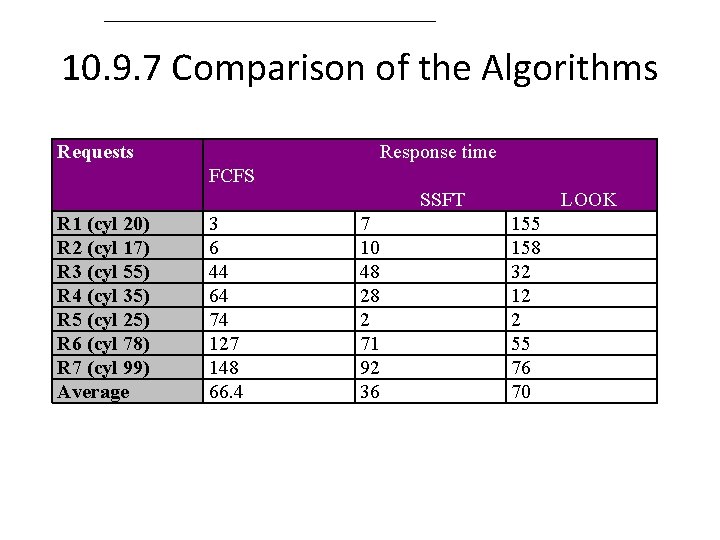

10. 9. 7 Comparison of the Algorithms Requests Response time FCFS SSFT R 1 (cyl 20) R 2 (cyl 17) R 3 (cyl 55) R 4 (cyl 35) R 5 (cyl 25) R 6 (cyl 78) R 7 (cyl 99) Average 3 6 44 64 74 127 148 66. 4 7 10 48 28 2 71 92 36 LOOK 155 158 32 12 2 55 76 70

10. 10 Solid State Drive

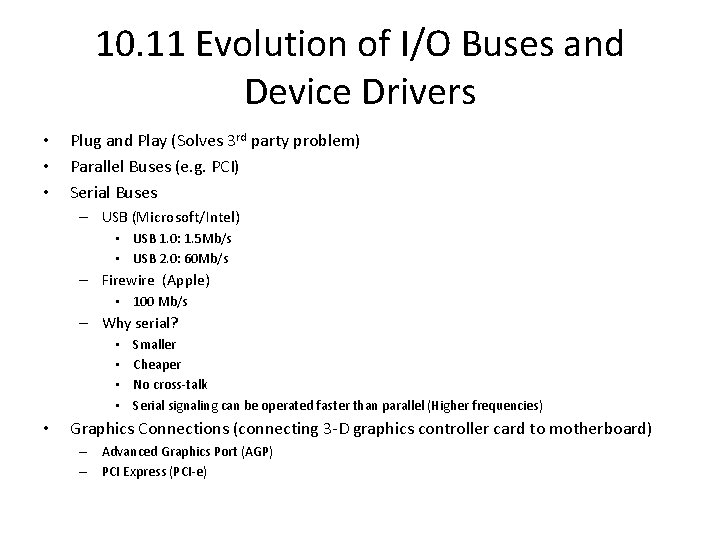

10. 11 Evolution of I/O Buses and Device Drivers • • • Plug and Play (Solves 3 rd party problem) Parallel Buses (e. g. PCI) Serial Buses – USB (Microsoft/Intel) • USB 1. 0: 1. 5 Mb/s • USB 2. 0: 60 Mb/s – Firewire (Apple) • 100 Mb/s – Why serial? • • • Smaller Cheaper No cross-talk Serial signaling can be operated faster than parallel (Higher frequencies) Graphics Connections (connecting 3 -D graphics controller card to motherboard) – Advanced Graphics Port (AGP) – PCI Express (PCI-e)

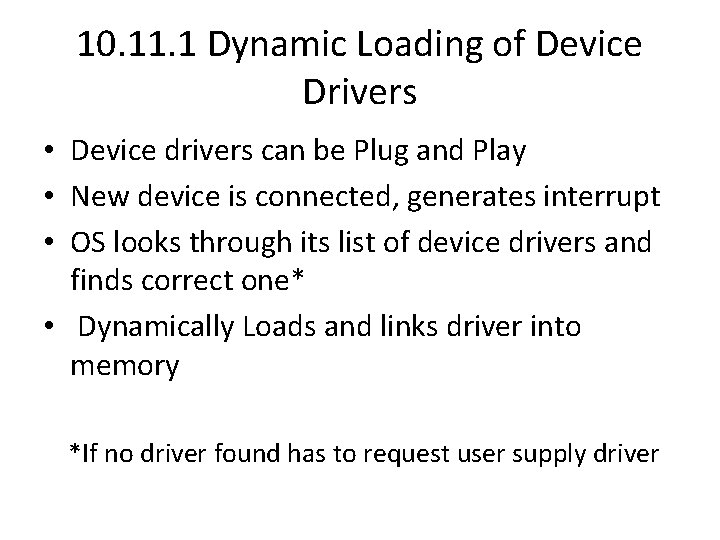

10. 11. 1 Dynamic Loading of Device Drivers • Device drivers can be Plug and Play • New device is connected, generates interrupt • OS looks through its list of device drivers and finds correct one* • Dynamically Loads and links driver into memory *If no driver found has to request user supply driver

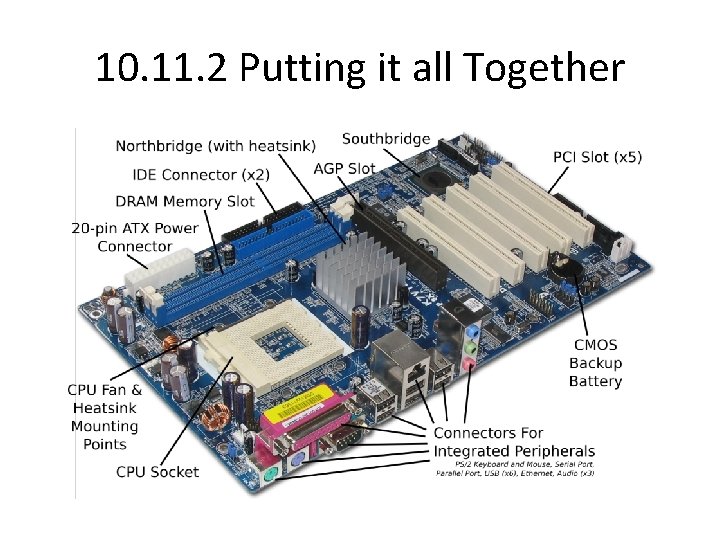

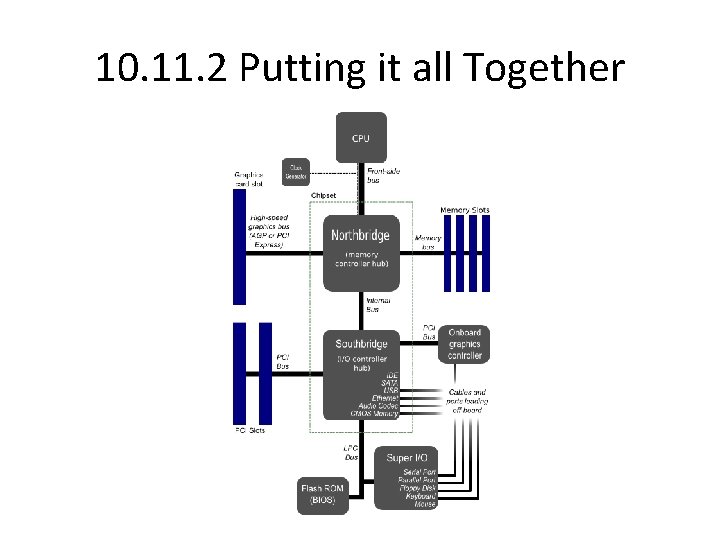

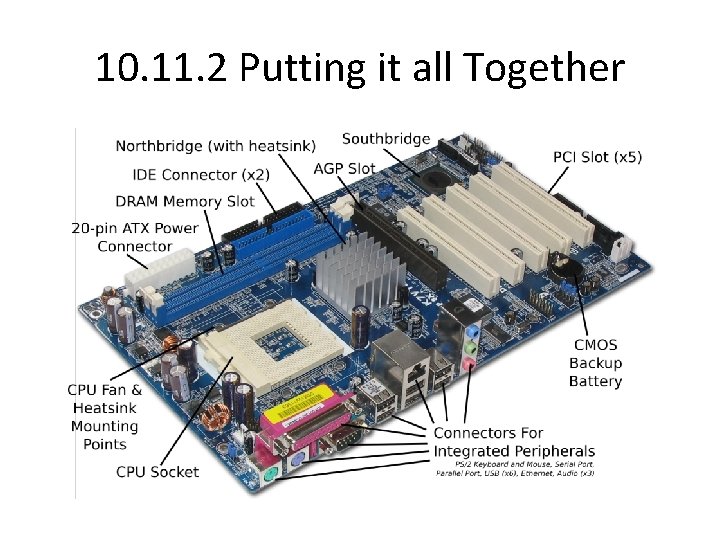

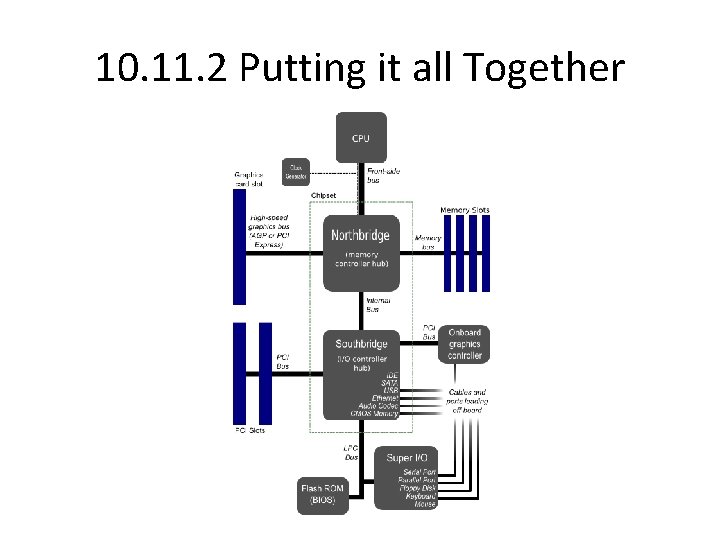

10. 11. 2 Putting it all Together

10. 11. 2 Putting it all Together

10. 12 Summary • Mechanisms for communication between processor and I/O devices including programmed I/O and DMA. • Device controllers and device drivers. • Buses in general and evolution of I/O buses in particular, found in modern computer systems. • Disk storage and disk-scheduling algorithms.