Computer System Architecture By Morris Mano Chapter 5

Computer System Architecture By Morris Mano Chapter 5 Basic Computer Organization and Design

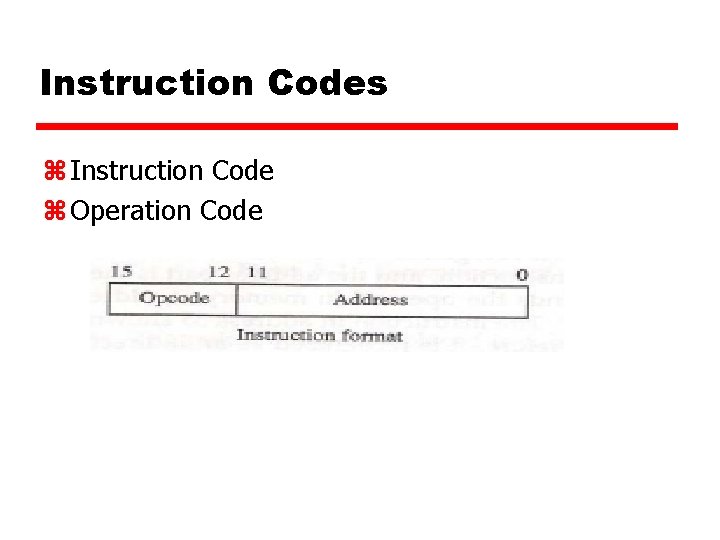

Instruction Codes z Instruction Code z Operation Code

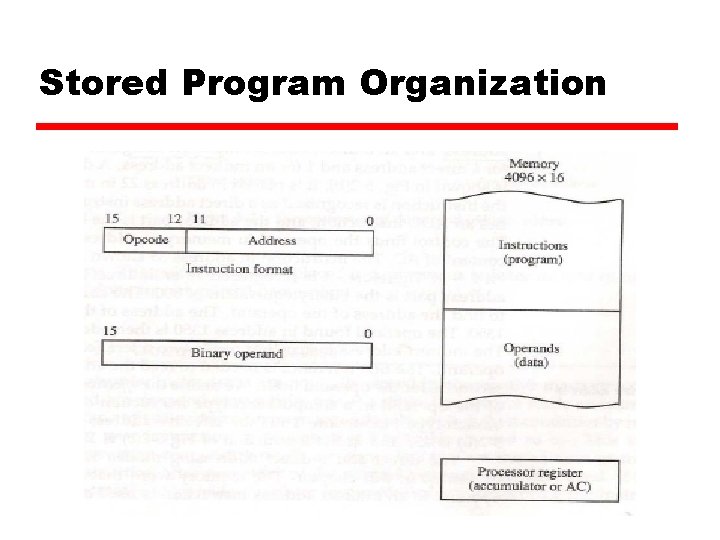

Stored Program Organization

Addressing Modes z Immediate z Direct z Indirect z Register Indirect

Immediate Addressing z Operand is part of instruction z Operand = address field z e. g. ADD 5 y. Add 5 to contents of accumulator y 5 is operand z No memory reference to fetch data z Fast z Limited range

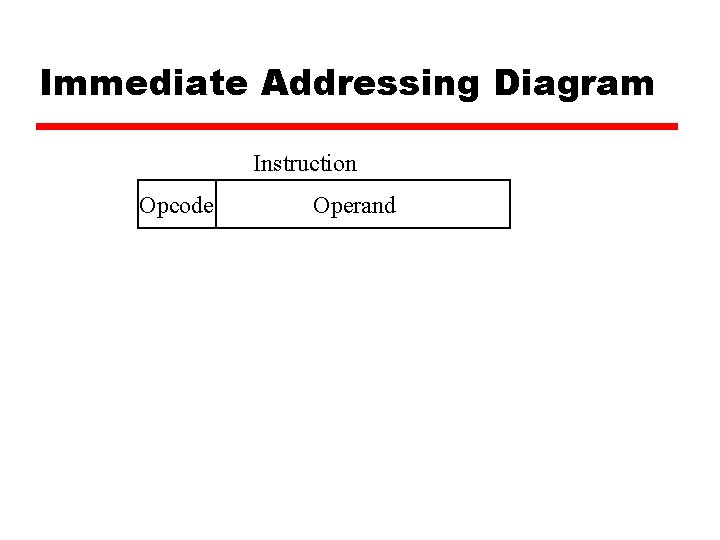

Immediate Addressing Diagram Instruction Opcode Operand

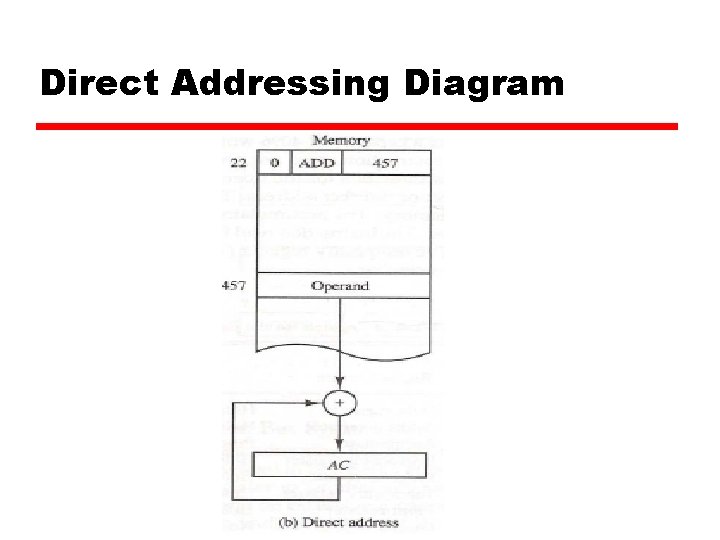

Direct Addressing z Address field contains address of operand z Effective address (EA) = address field (A) z e. g. ADD A y. Add contents of cell A to accumulator y. Look in memory at address A for operand z Single memory reference to access data z No additional calculations to work out effective address z Limited address space

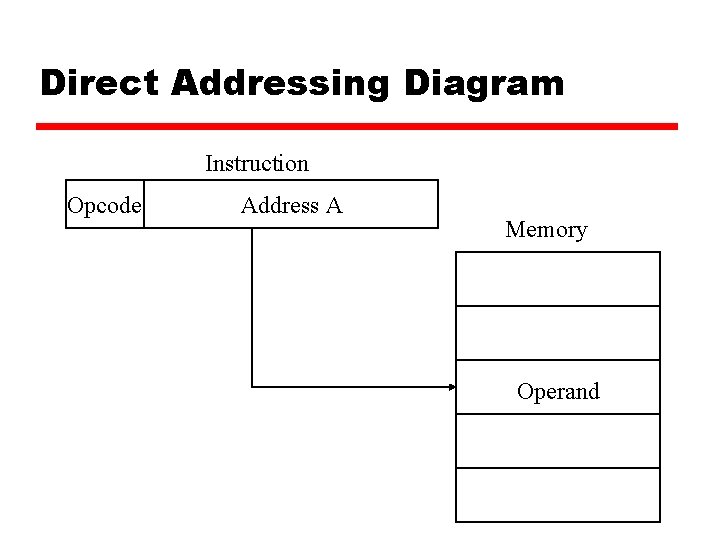

Direct Addressing Diagram Instruction Opcode Address A Memory Operand

Direct Addressing Diagram

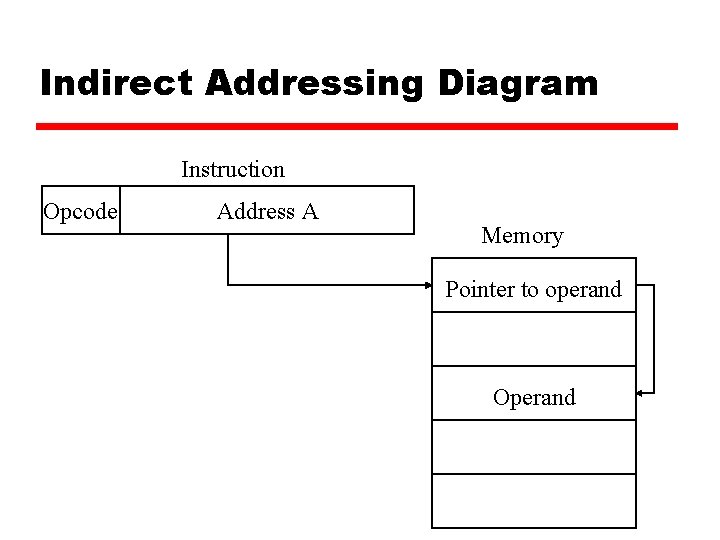

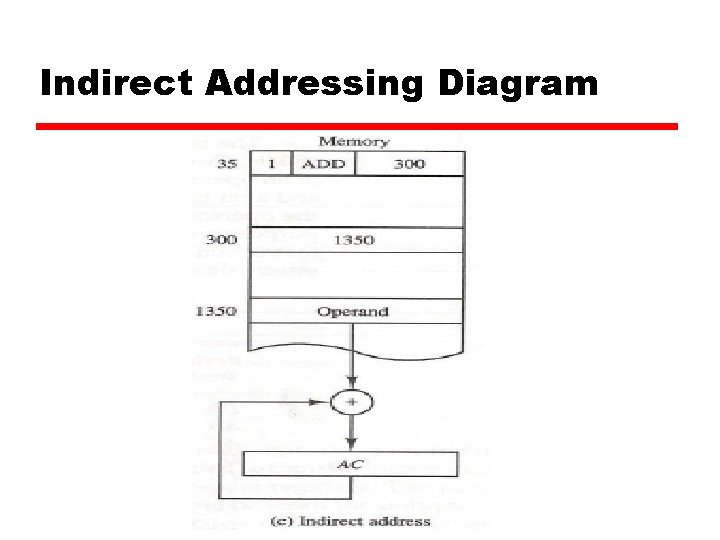

Indirect Addressing (1) z Memory cell pointed to by address field contains the address of (pointer to) the operand z EA = (A) y. Look in A, find address (A) and look there for operand z e. g. ADD (A) y. Add contents of cell pointed to by contents of A to accumulator

Indirect Addressing (2) z Large address space z 2 n where n = word length z May be nested, multilevel, cascaded ye. g. EA = (((A))) x. Draw the diagram yourself z Multiple memory accesses to find operand z Hence slower

Indirect Addressing Diagram Instruction Opcode Address A Memory Pointer to operand Operand

Indirect Addressing Diagram

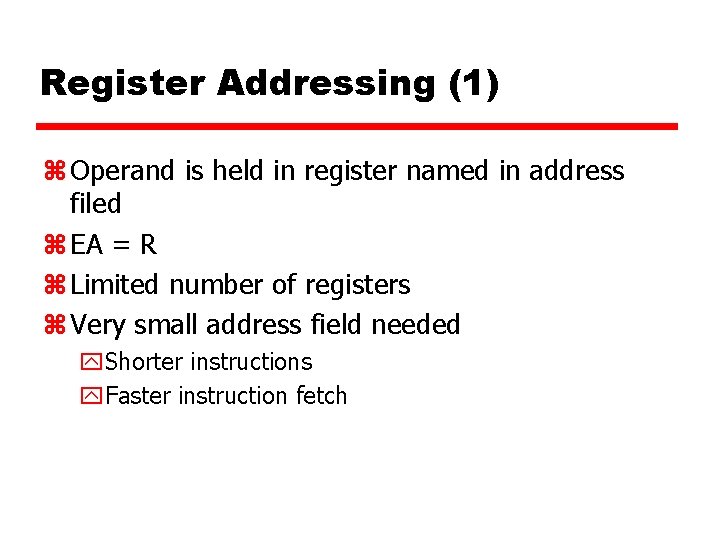

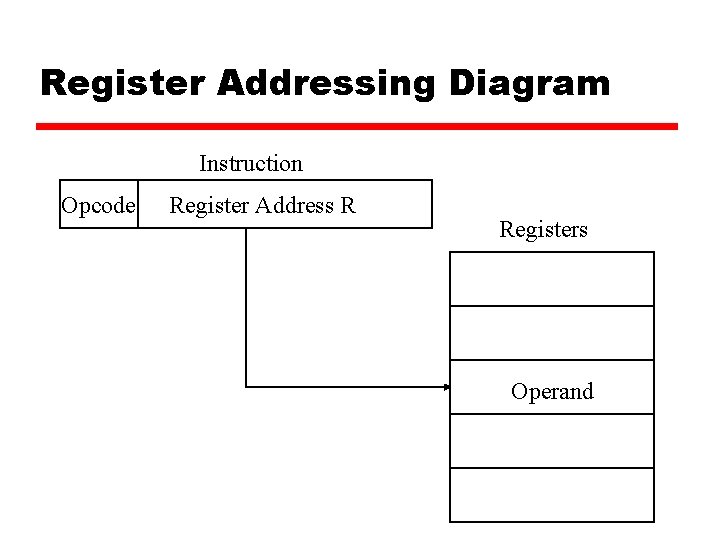

Register Addressing (1) z Operand is held in register named in address filed z EA = R z Limited number of registers z Very small address field needed y. Shorter instructions y. Faster instruction fetch

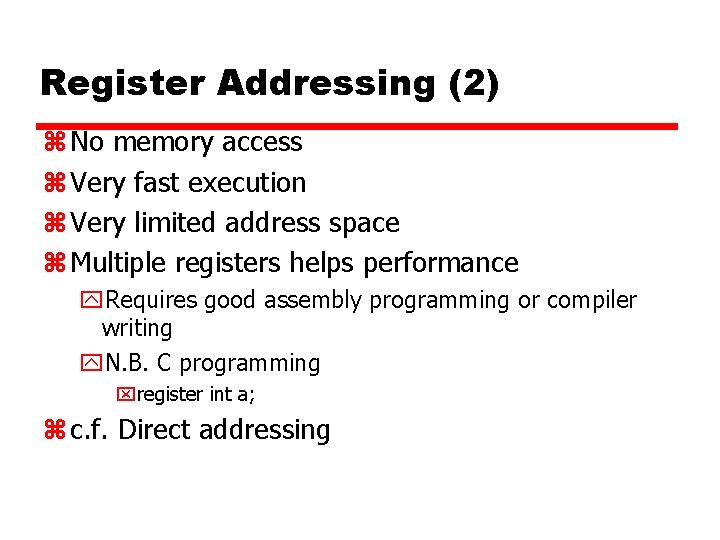

Register Addressing (2) z No memory access z Very fast execution z Very limited address space z Multiple registers helps performance y. Requires good assembly programming or compiler writing y. N. B. C programming xregister int a; z c. f. Direct addressing

Register Addressing Diagram Instruction Opcode Register Address R Registers Operand

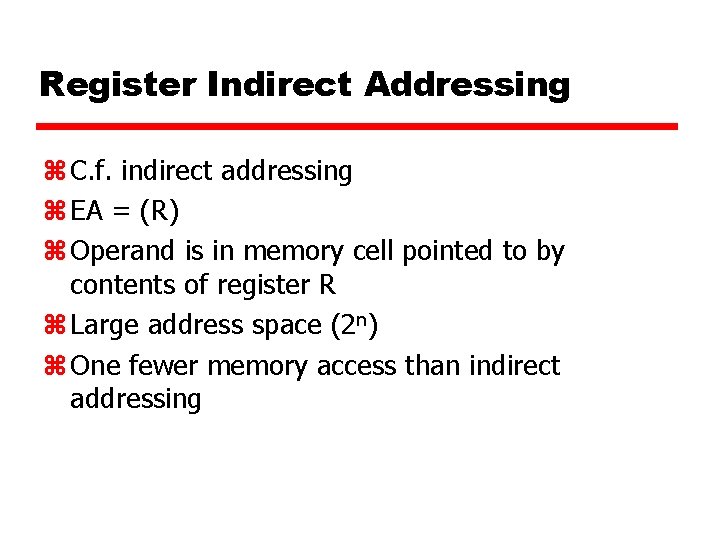

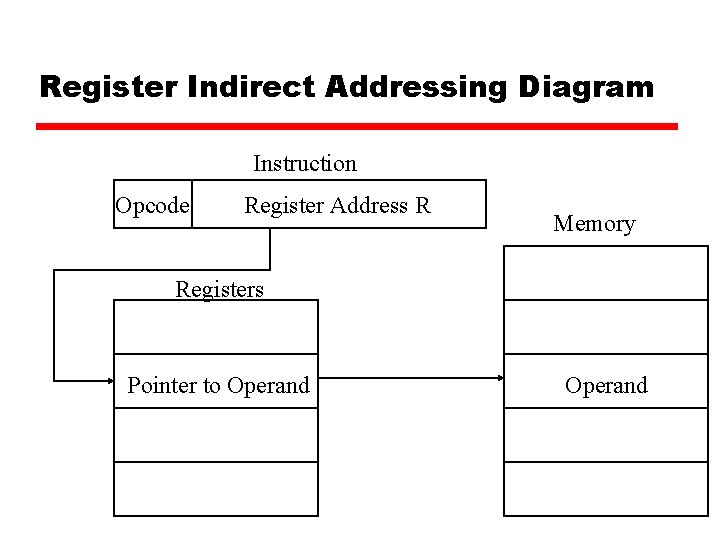

Register Indirect Addressing z C. f. indirect addressing z EA = (R) z Operand is in memory cell pointed to by contents of register R z Large address space (2 n) z One fewer memory access than indirect addressing

Register Indirect Addressing Diagram Instruction Opcode Register Address R Memory Registers Pointer to Operand

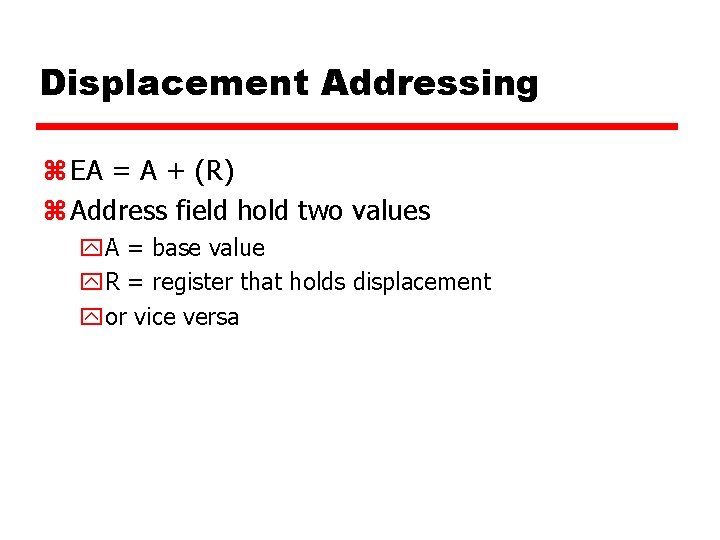

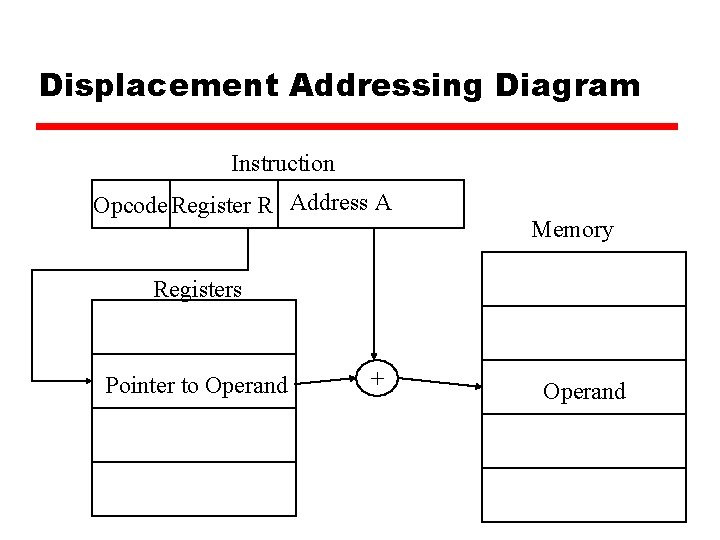

Displacement Addressing z EA = A + (R) z Address field hold two values y. A = base value y. R = register that holds displacement yor vice versa

Displacement Addressing Diagram Instruction Opcode Register R Address A Memory Registers Pointer to Operand + Operand

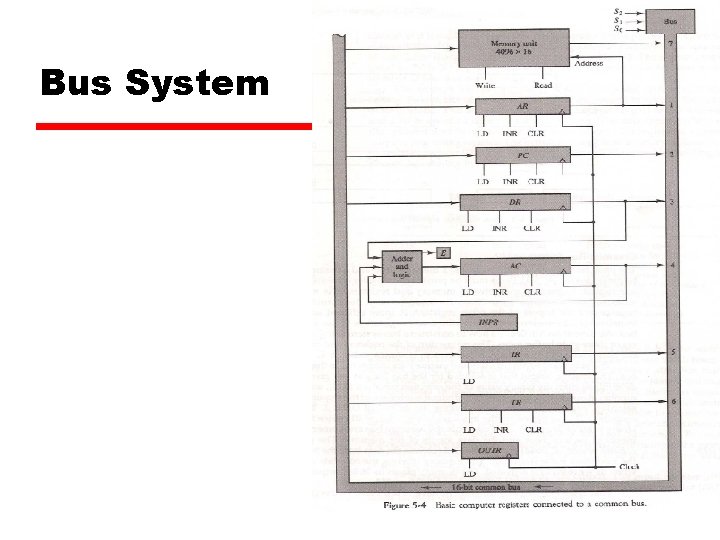

Bus System

Computer Instructions

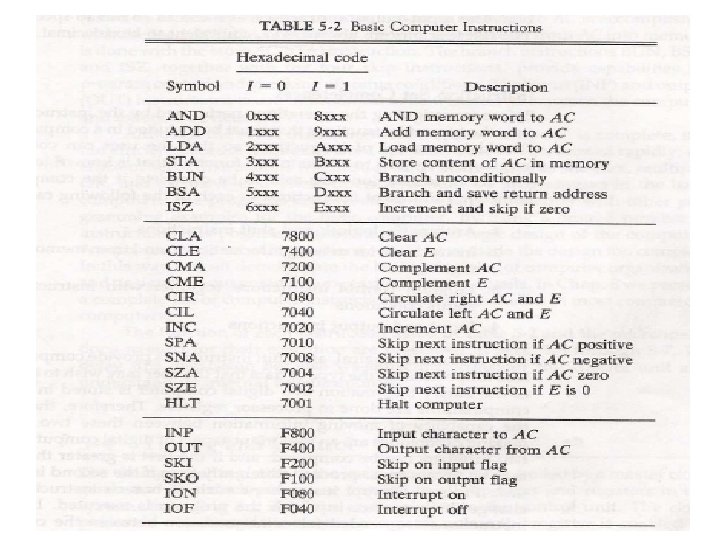

Instruction Set Completeness 1. Arithmetic, logical and shift instructions 2. Instructions for moving information to and from memory and processor registers 3. Program control instructions together with instructions that check status conditions 4. Input and output instructions

Timing and Control z Clock Pulses z Control Organization y Hardwired Control y Micro-programmed Control z Control Unit z Timing Signals

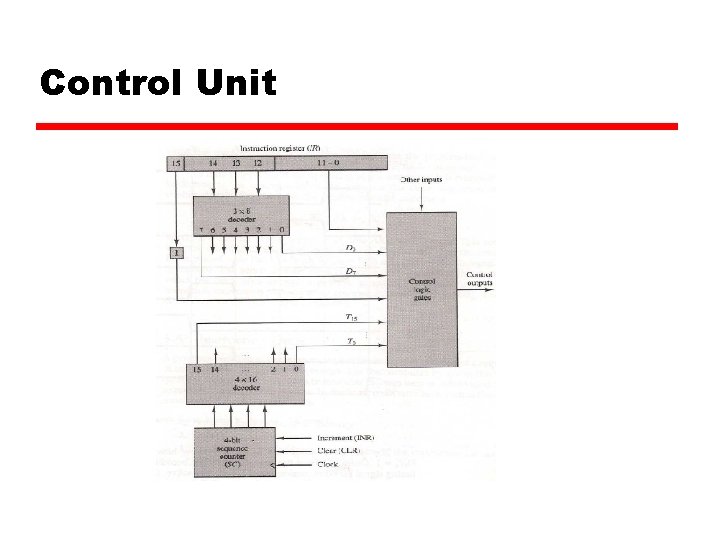

Control Unit

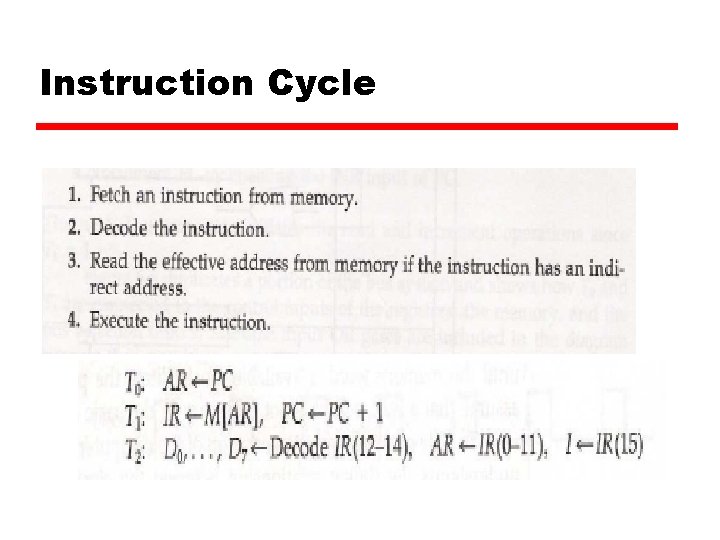

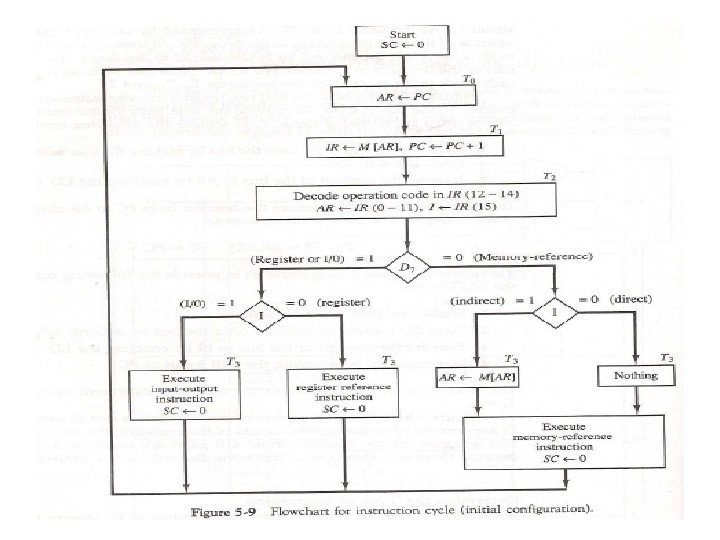

Instruction Cycle

Memory Reference Instructions z AND to AC z ADD to AC z LDA (Load to AC) z STA (Store AC) z BUN ( branch unconditionally) z BSA ( branch and save return address)

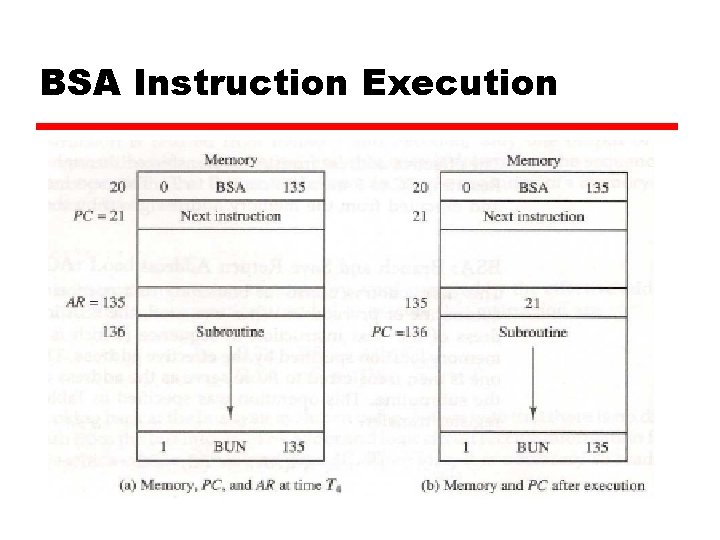

BSA Instruction Execution

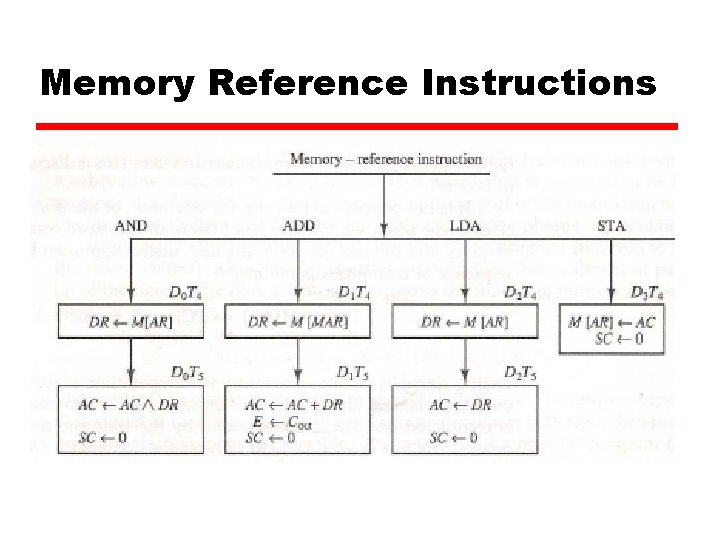

Memory Reference Instructions

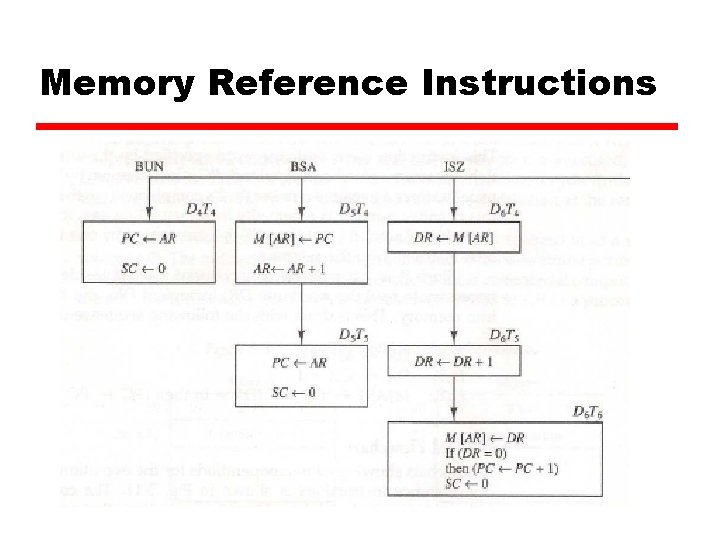

Memory Reference Instructions

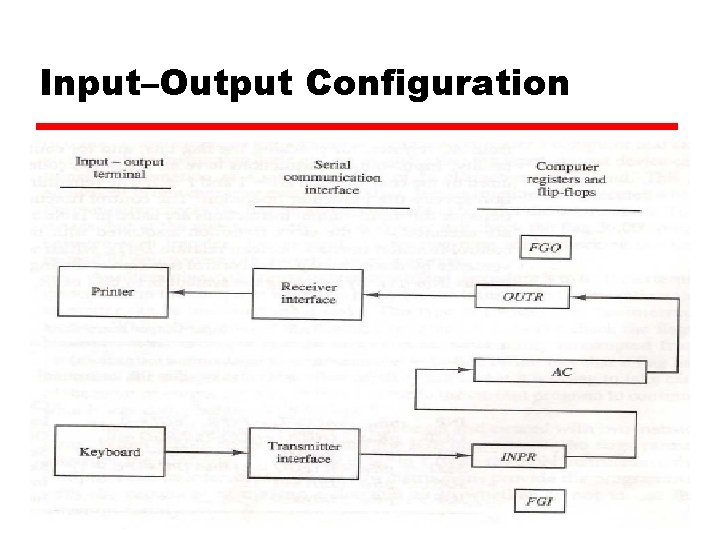

Input–Output Configuration

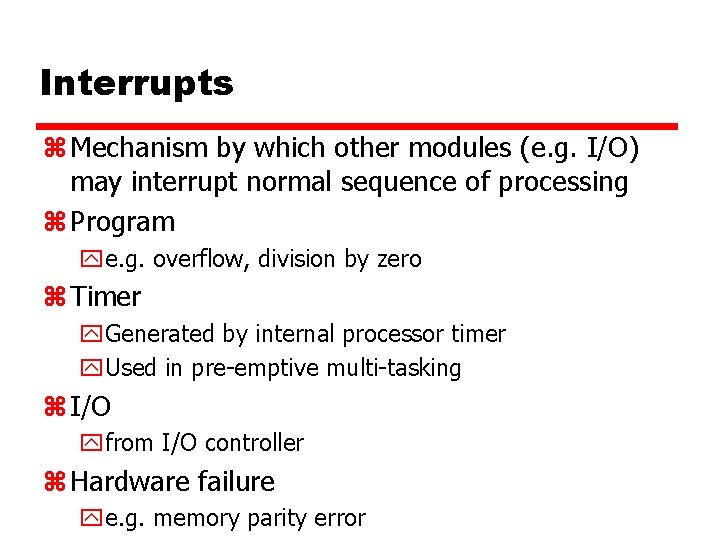

Interrupts z Mechanism by which other modules (e. g. I/O) may interrupt normal sequence of processing z Program ye. g. overflow, division by zero z Timer y. Generated by internal processor timer y. Used in pre-emptive multi-tasking z I/O yfrom I/O controller z Hardware failure ye. g. memory parity error

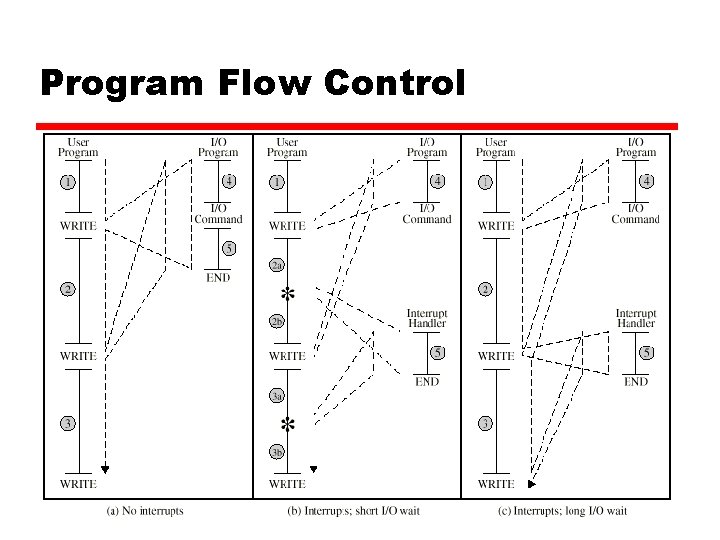

Program Flow Control

Interrupt Cycle z Added to instruction cycle z Processor checks for interrupt y. Indicated by an interrupt signal z If no interrupt, fetch next instruction z If interrupt pending: y. Suspend execution of current program y. Save context y. Set PC to start address of interrupt handler routine y. Process interrupt y. Restore context and continue interrupted program

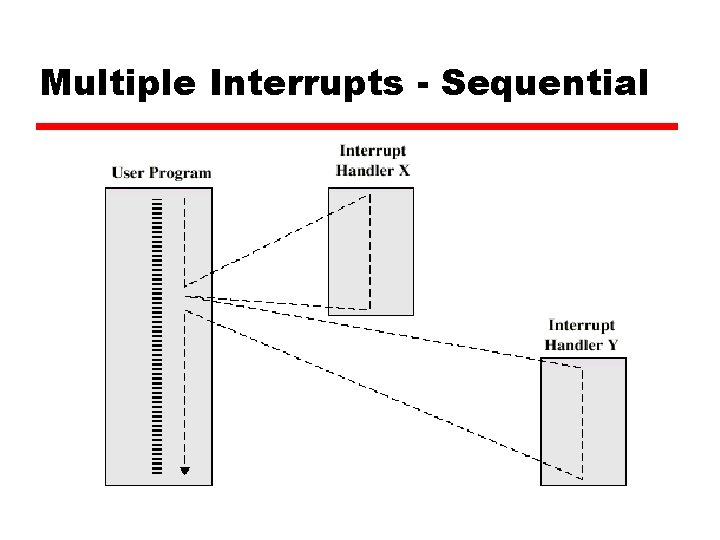

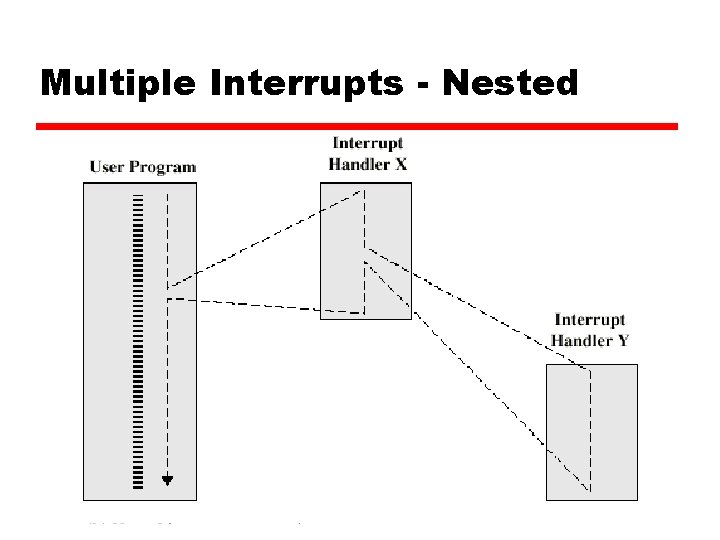

Multiple Interrupts z Disable interrupts y. Processor will ignore further interrupts whilst processing one interrupt y. Interrupts remain pending and are checked after first interrupt has been processed y. Interrupts handled in sequence as they occur z Define priorities y. Low priority interrupts can be interrupted by higher priority interrupts y. When higher priority interrupt has been processed, processor returns to previous interrupt

Multiple Interrupts - Sequential

Multiple Interrupts - Nested

- Slides: 40