Computer Organization CSC 405 Bus Structure System Bus

Computer Organization CSC 405 Bus Structure

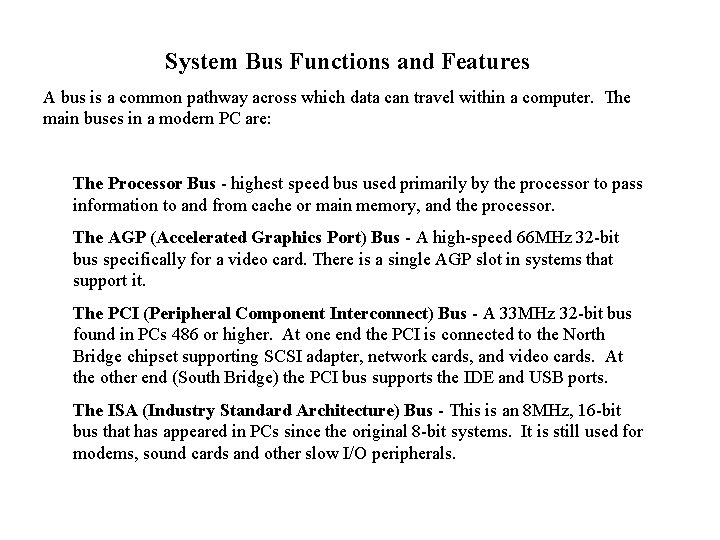

System Bus Functions and Features A bus is a common pathway across which data can travel within a computer. The main buses in a modern PC are: The Processor Bus - highest speed bus used primarily by the processor to pass information to and from cache or main memory, and the processor. The AGP (Accelerated Graphics Port) Bus - A high-speed 66 MHz 32 -bit bus specifically for a video card. There is a single AGP slot in systems that support it. The PCI (Peripheral Component Interconnect) Bus - A 33 MHz 32 -bit bus found in PCs 486 or higher. At one end the PCI is connected to the North Bridge chipset supporting SCSI adapter, network cards, and video cards. At the other end (South Bridge) the PCI bus supports the IDE and USB ports. The ISA (Industry Standard Architecture) Bus - This is an 8 MHz, 16 -bit bus that has appeared in PCs since the original 8 -bit systems. It is still used for modems, sound cards and other slow I/O peripherals.

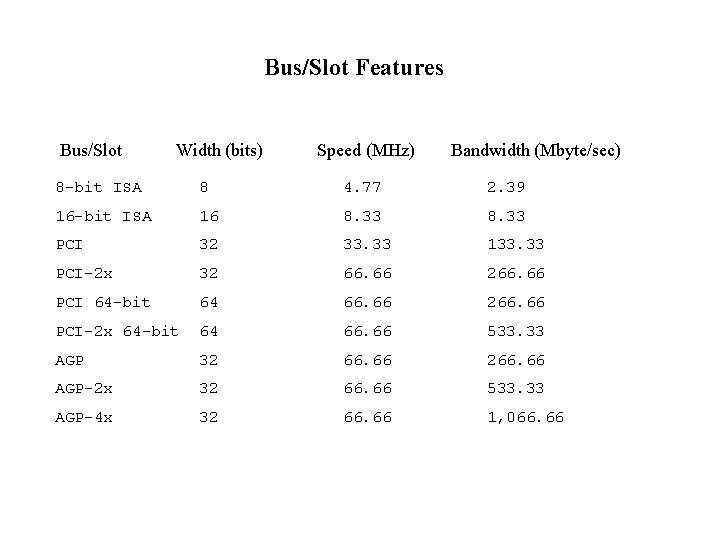

Bus/Slot Features Bus/Slot Width (bits) Speed (MHz) Bandwidth (Mbyte/sec) 8 -bit ISA 8 4. 77 2. 39 16 -bit ISA 16 8. 33 PCI 32 33. 33 133. 33 PCI-2 x 32 66. 66 266. 66 PCI 64 -bit 64 66. 66 266. 66 PCI-2 x 64 -bit 64 66. 66 533. 33 AGP 32 66. 66 266. 66 AGP-2 x 32 66. 66 533. 33 AGP-4 x 32 66. 66 1, 066. 66

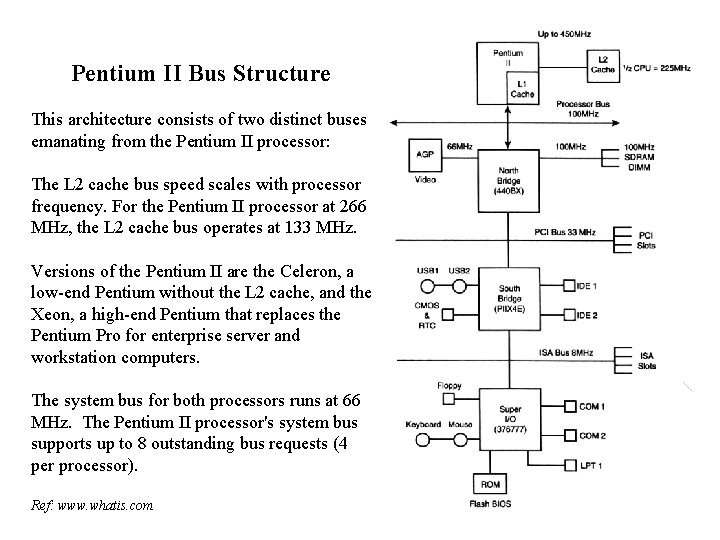

Pentium II Bus Structure This architecture consists of two distinct buses emanating from the Pentium II processor: The L 2 cache bus speed scales with processor frequency. For the Pentium II processor at 266 MHz, the L 2 cache bus operates at 133 MHz. Versions of the Pentium II are the Celeron, a low-end Pentium without the L 2 cache, and the Xeon, a high-end Pentium that replaces the Pentium Pro for enterprise server and workstation computers. The system bus for both processors runs at 66 MHz. The Pentium II processor's system bus supports up to 8 outstanding bus requests (4 per processor). Ref: www. whatis. com

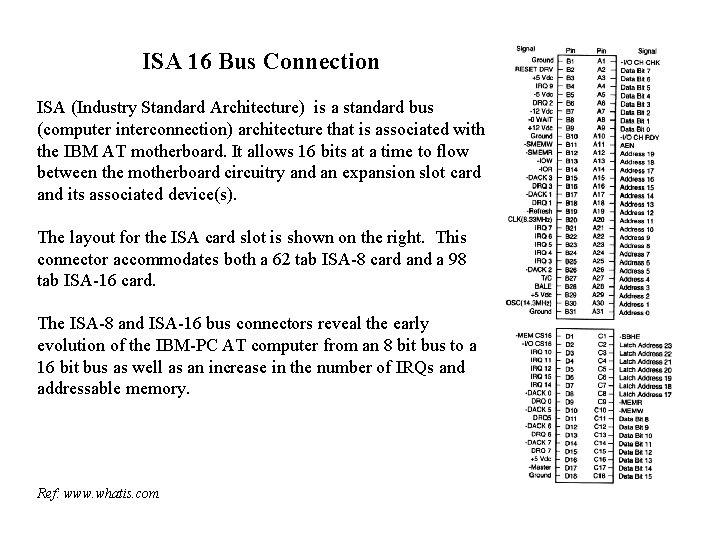

ISA 16 Bus Connection ISA (Industry Standard Architecture) is a standard bus (computer interconnection) architecture that is associated with the IBM AT motherboard. It allows 16 bits at a time to flow between the motherboard circuitry and an expansion slot card and its associated device(s). The layout for the ISA card slot is shown on the right. This connector accommodates both a 62 tab ISA-8 card and a 98 tab ISA-16 card. The ISA-8 and ISA-16 bus connectors reveal the early evolution of the IBM-PC AT computer from an 8 bit bus to a 16 bit bus as well as an increase in the number of IRQs and addressable memory. Ref: www. whatis. com

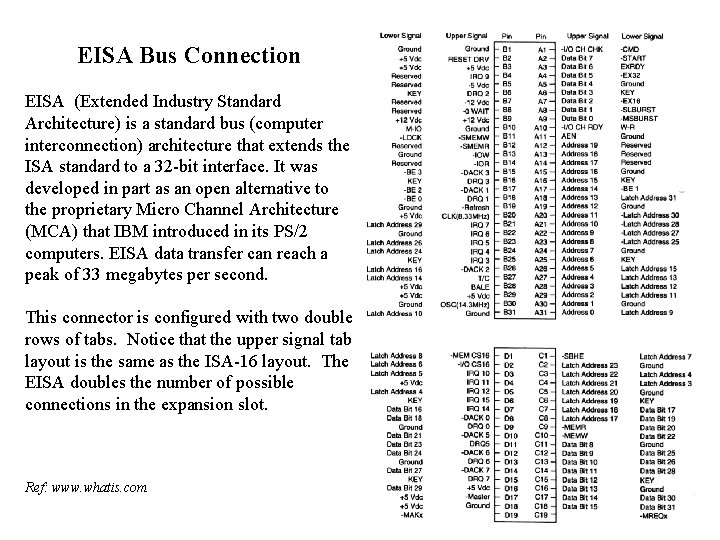

EISA Bus Connection EISA (Extended Industry Standard Architecture) is a standard bus (computer interconnection) architecture that extends the ISA standard to a 32 -bit interface. It was developed in part as an open alternative to the proprietary Micro Channel Architecture (MCA) that IBM introduced in its PS/2 computers. EISA data transfer can reach a peak of 33 megabytes per second. This connector is configured with two double rows of tabs. Notice that the upper signal tab layout is the same as the ISA-16 layout. The EISA doubles the number of possible connections in the expansion slot. Ref: www. whatis. com

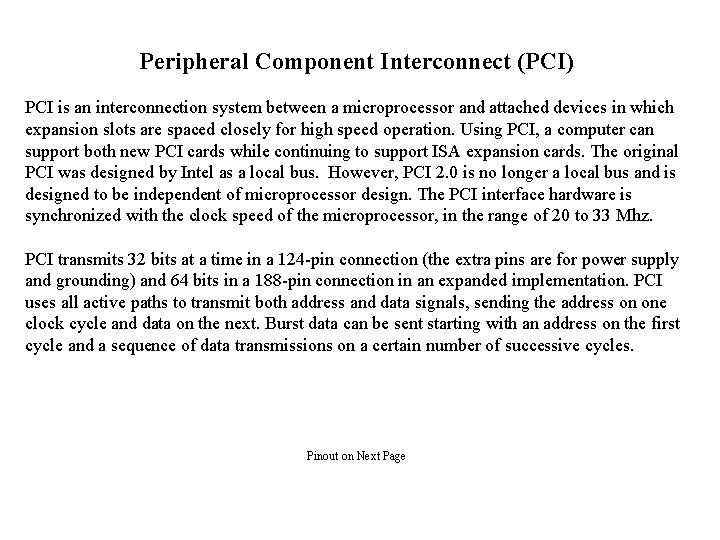

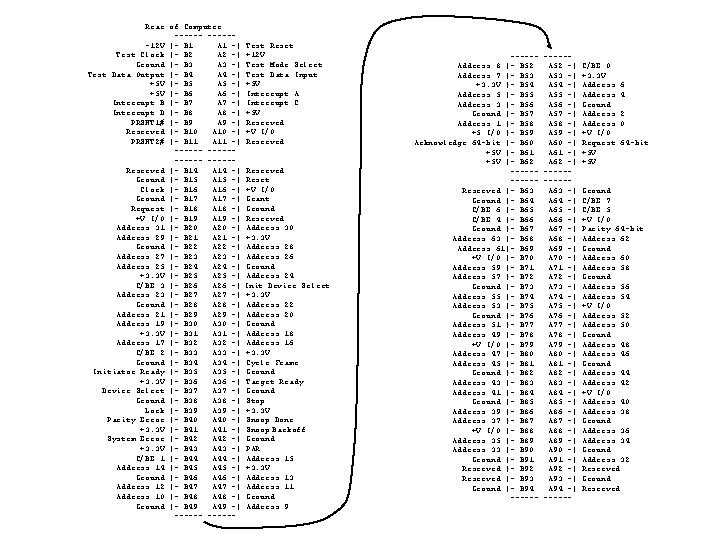

Peripheral Component Interconnect (PCI) PCI is an interconnection system between a microprocessor and attached devices in which expansion slots are spaced closely for high speed operation. Using PCI, a computer can support both new PCI cards while continuing to support ISA expansion cards. The original PCI was designed by Intel as a local bus. However, PCI 2. 0 is no longer a local bus and is designed to be independent of microprocessor design. The PCI interface hardware is synchronized with the clock speed of the microprocessor, in the range of 20 to 33 Mhz. PCI transmits 32 bits at a time in a 124 -pin connection (the extra pins are for power supply and grounding) and 64 bits in a 188 -pin connection in an expanded implementation. PCI uses all active paths to transmit both address and data signals, sending the address on one clock cycle and data on the next. Burst data can be sent starting with an address on the first cycle and a sequence of data transmissions on a certain number of successive cycles. Pinout on Next Page

Rear of Computer : ------: -12 V |- B 1 A 1 -| Test Clock |- B 2 A 2 -| Ground |- B 3 A 3 -| Test Data Output |- B 4 A 4 -| +5 V |- B 5 A 5 -| +5 V |- B 6 A 6 -| Interrupt B |- B 7 A 7 -| Interrupt D |- B 8 A 8 -| PRSNT 1# |- B 9 A 9 -| Reserved |- B 10 A 10 -| PRSNT 2# |- B 11 A 11 -| : ------: Reserved |- B 14 A 14 -| Ground |- B 15 A 15 -| Clock |- B 16 A 16 -| Ground |- B 17 A 17 -| Request |- B 18 A 18 -| +V I/O |- B 19 A 19 -| Address 31 |- B 20 A 20 -| Address 29 |- B 21 A 21 -| Ground |- B 22 A 22 -| Address 27 |- B 23 A 23 -| Address 25 |- B 24 A 24 -| +3. 3 V |- B 25 A 25 -| C/BE 3 |- B 26 A 26 -| Address 23 |- B 27 A 27 -| Ground |- B 28 A 28 -| Address 21 |- B 29 A 29 -| Address 19 |- B 30 A 30 -| +3. 3 V |- B 31 A 31 -| Address 17 |- B 32 A 32 -| C/BE 2 |- B 33 A 33 -| Ground |- B 34 A 34 -| Initiator Ready |- B 35 A 35 -| +3. 3 V |- B 36 A 36 -| Device Select |- B 37 A 37 -| Ground |- B 38 A 38 -| Lock |- B 39 A 39 -| Parity Error |- B 40 A 40 -| +3. 3 V |- B 41 A 41 -| System Error |- B 42 A 42 -| +3. 3 V |- B 43 A 43 -| C/BE 1 |- B 44 A 44 -| Address 14 |- B 45 A 45 -| Ground |- B 46 A 46 -| Address 12 |- B 47 A 47 -| Address 10 |- B 48 A 48 -| Ground |- B 49 A 49 -| : ------: Test Reset +12 V Test Mode Select Test Data Input +5 V Interrupt A Interrupt C +5 V Reserved +V I/O Reserved Reset +V I/O Grant Ground Reserved Address 30 +3. 3 V Address 28 Address 26 Ground Address 24 Init Device Select +3. 3 V Address 22 Address 20 Ground Address 18 Address 16 +3. 3 V Cycle Frame Ground Target Ready Ground Stop +3. 3 V Snoop Done Snoop Backoff Ground PAR Address 15 +3. 3 V Address 13 Address 11 Ground Address 9 : ------: |- B 52 A 52 -| |- B 53 A 53 -| |- B 54 A 54 -| |- B 55 A 55 -| |- B 56 A 56 -| |- B 57 A 57 -| |- B 58 A 58 -| |- B 59 A 59 -| |- B 60 A 60 -| |- B 61 A 61 -| |- B 62 A 62 -| : ------: Reserved |- B 63 A 63 -| Ground |- B 64 A 64 -| C/BE 6 |- B 65 A 65 -| C/BE 4 |- B 66 A 66 -| Ground |- B 67 A 67 -| Address 63 |- B 68 A 68 -| Address 61|- B 69 A 69 -| +V I/O |- B 70 A 70 -| Address 59 |- B 71 A 71 -| Address 57 |- B 72 A 72 -| Ground |- B 73 A 73 -| Address 55 |- B 74 A 74 -| Address 53 |- B 75 A 75 -| Ground |- B 76 A 76 -| Address 51 |- B 77 A 77 -| Address 49 |- B 78 A 78 -| +V I/O |- B 79 A 79 -| Address 47 |- B 80 A 80 -| Address 45 |- B 81 A 81 -| Ground |- B 82 A 82 -| Address 43 |- B 83 A 83 -| Address 41 |- B 84 A 84 -| Ground |- B 85 A 85 -| Address 39 |- B 86 A 86 -| Address 37 |- B 87 A 87 -| +V I/O |- B 88 A 88 -| Address 35 |- B 89 A 89 -| Address 33 |- B 90 A 90 -| Ground |- B 91 A 91 -| Reserved |- B 92 A 92 -| Reserved |- B 93 A 93 -| Ground |- B 94 A 94 -| : ------: Address 8 Address 7 +3. 3 V Address 5 Address 3 Ground Address 1 +5 I/O Acknowledge 64 -bit +5 V C/BE 0 +3. 3 V Address Ground Address +V I/O Request +5 V 6 4 2 0 64 -bit Ground C/BE 7 C/BE 5 +V I/O Parity 64 -bit Address 62 Ground Address 60 Address 58 Ground Address 56 Address 54 +V I/O Address 52 Address 50 Ground Address 48 Address 46 Ground Address 44 Address 42 +V I/O Address 40 Address 38 Ground Address 36 Address 34 Ground Address 32 Reserved Ground Reserved

AGP (Accelerated Graphics Port) is a bus specification that enables 3 -D graphics to display quickly on ordinary personal computers. AGP is a special interface designed to convey 3 -D images (for example, from Web sites or CD-ROMs) much more quickly and smoothly than is possible today on any computer other than an expensive graphics workstation. The interface uses your computer's main storage (RAM) for refreshing the monitor image and to support the texture mapping, z-buffering, and alpha blending required for 3 -D image display. The AGP main memory use is dynamic, meaning that when not being used for accelerated graphics, main memory is restored to use by the operating system or other applications. Ref: www. whatis. com

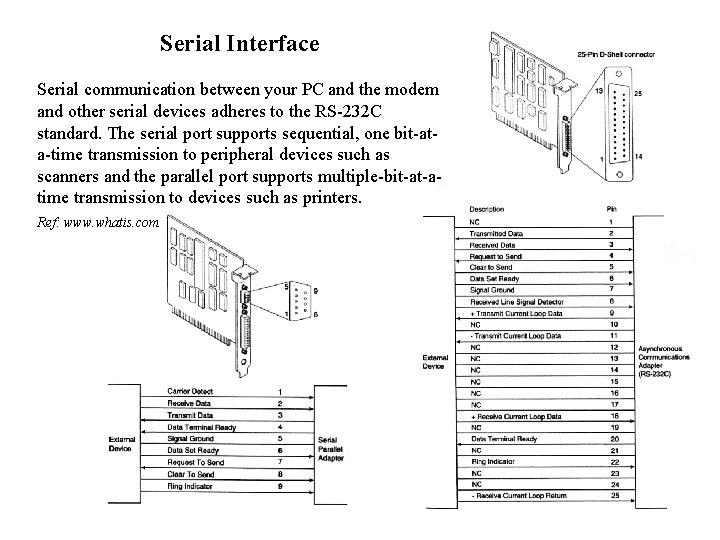

Serial Interface Serial communication between your PC and the modem and other serial devices adheres to the RS-232 C standard. The serial port supports sequential, one bit-ata-time transmission to peripheral devices such as scanners and the parallel port supports multiple-bit-at-atime transmission to devices such as printers. Ref: www. whatis. com

- Slides: 10