Computer Organization CS 224 Fall 2012 Lesson 23

![Instruction Fetch (IF) RTL q Common RTL operations l Fetch instruction Mem[PC]; l Fetch Instruction Fetch (IF) RTL q Common RTL operations l Fetch instruction Mem[PC]; l Fetch](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-3.jpg)

![Add RTL q Add instruction add rd, rs, rt Bits Mem[PC]; Fetch instruction from Add RTL q Add instruction add rd, rs, rt Bits Mem[PC]; Fetch instruction from](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-5.jpg)

![Sub RTL q Sub instruction sub rd, rs, rt Bits Mem[PC]; Fetch instruction from Sub RTL q Sub instruction sub rd, rs, rt Bits Mem[PC]; Fetch instruction from](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-6.jpg)

![Datapath: Reg-Reg Operations q R[rd] <- R[rs] op R[rt]; l ALU control and Reg. Datapath: Reg-Reg Operations q R[rd] <- R[rs] op R[rt]; l ALU control and Reg.](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-7.jpg)

![Load RTL q Load instruction lw rt, rs, imm Fetch instruction from memory Mem[PC]; Load RTL q Load instruction lw rt, rs, imm Fetch instruction from memory Mem[PC];](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-10.jpg)

![Store RTL q Store instruction sw rt, rs, imm Fetch instruction from memory Mem[PC]; Store RTL q Store instruction sw rt, rs, imm Fetch instruction from memory Mem[PC];](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-12.jpg)

![Branch RTL q Branch instruction beq rs, rt, imm Fetch instruction from memory Mem[PC]; Branch RTL q Branch instruction beq rs, rt, imm Fetch instruction from memory Mem[PC];](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-14.jpg)

![The Next Address q PC is byte-addressed in instruction memory l Sequential PC[31: 0] The Next Address q PC is byte-addressed in instruction memory l Sequential PC[31: 0]](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-16.jpg)

![Jump RTL q Jump instruction j target Mem[PC]; Fetch instruction from memory PC[31: 2] Jump RTL q Jump instruction j target Mem[PC]; Fetch instruction from memory PC[31: 2]](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-19.jpg)

- Slides: 22

Computer Organization CS 224 Fall 2012 Lesson 23

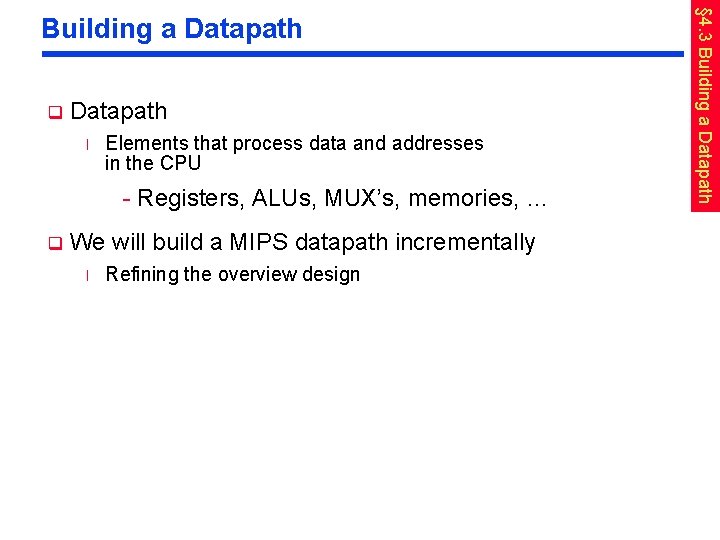

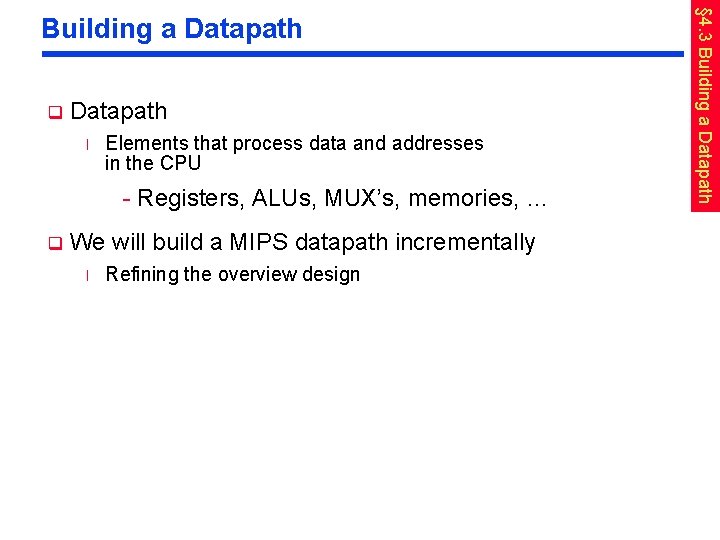

q Datapath l Elements that process data and addresses in the CPU - Registers, ALUs, MUX’s, memories, … q We will build a MIPS datapath incrementally l Refining the overview design § 4. 3 Building a Datapath

![Instruction Fetch IF RTL q Common RTL operations l Fetch instruction MemPC l Fetch Instruction Fetch (IF) RTL q Common RTL operations l Fetch instruction Mem[PC]; l Fetch](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-3.jpg)

Instruction Fetch (IF) RTL q Common RTL operations l Fetch instruction Mem[PC]; l Fetch instruction from memory Update program counter - Sequential PC <- PC + 4; Calculate next address

Datapath: Instruction Fetch Unit Clk PC Address Instruction Memory Adder 4 Instruction Word 32

![Add RTL q Add instruction add rd rs rt Bits MemPC Fetch instruction from Add RTL q Add instruction add rd, rs, rt Bits Mem[PC]; Fetch instruction from](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-5.jpg)

Add RTL q Add instruction add rd, rs, rt Bits Mem[PC]; Fetch instruction from memory R[rd] <- R[rs] + R[rt]; PC <- PC + 4; Add operation Calculate next address 6 5 OP=0 rs 5 rt second first source register 5 5 6 rd sa function result shift code register amount (=32)

![Sub RTL q Sub instruction sub rd rs rt Bits MemPC Fetch instruction from Sub RTL q Sub instruction sub rd, rs, rt Bits Mem[PC]; Fetch instruction from](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-6.jpg)

Sub RTL q Sub instruction sub rd, rs, rt Bits Mem[PC]; Fetch instruction from memory R[rd] <- R[rs] - R[rt]; PC <- PC + 4; Sub operation Calculate next address 6 5 OP=0 rs 5 rt second first source register 5 5 6 rd sa function result shift code register amount (=34)

![Datapath RegReg Operations q Rrd Rrs op Rrt l ALU control and Reg Datapath: Reg-Reg Operations q R[rd] <- R[rs] op R[rt]; l ALU control and Reg.](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-7.jpg)

Datapath: Reg-Reg Operations q R[rd] <- R[rs] op R[rt]; l ALU control and Reg. Wr coming from Control Unit, based on decoded instruction l Ra, Rb, and Rw from rs, rt, rd fields Reg. Wr Rd Rs Rt Instruction 5 5 Rw Ra Rb 32 32 -bit Registers bus. A 32 bus. B 32 ALU bus. W 32 Clk 5 ALU control Result 32

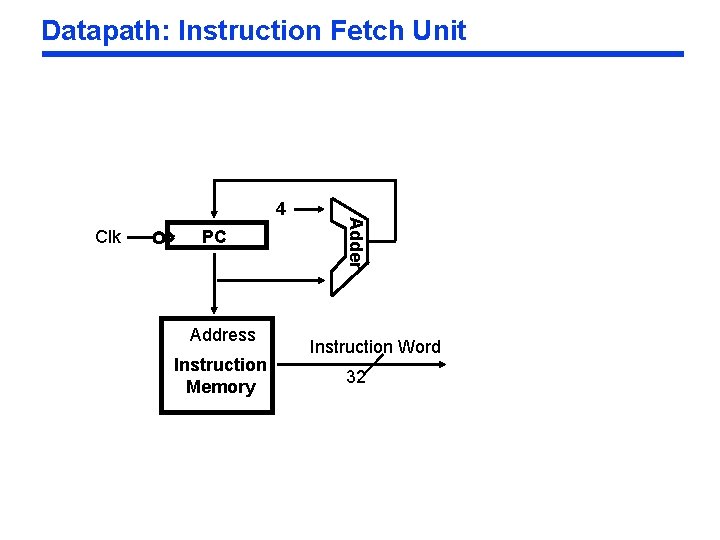

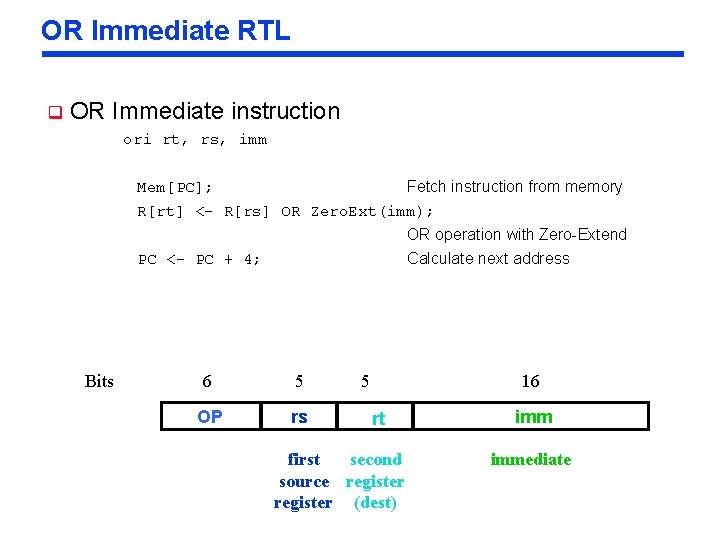

OR Immediate RTL q OR Immediate instruction ori rt, rs, imm Fetch instruction from memory Mem[PC]; R[rt] <- R[rs] OR Zero. Ext(imm); OR operation with Zero-Extend PC <- PC + 4; Calculate next address Bits 6 5 OP rs 5 16 rt second first source register (dest) immediate

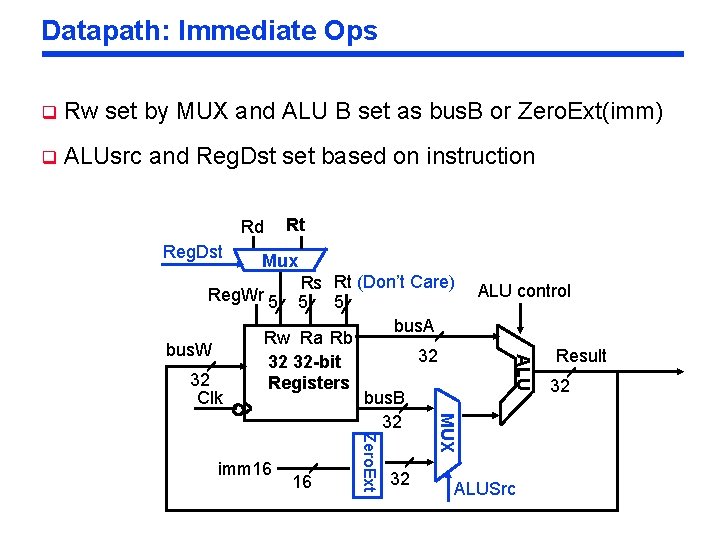

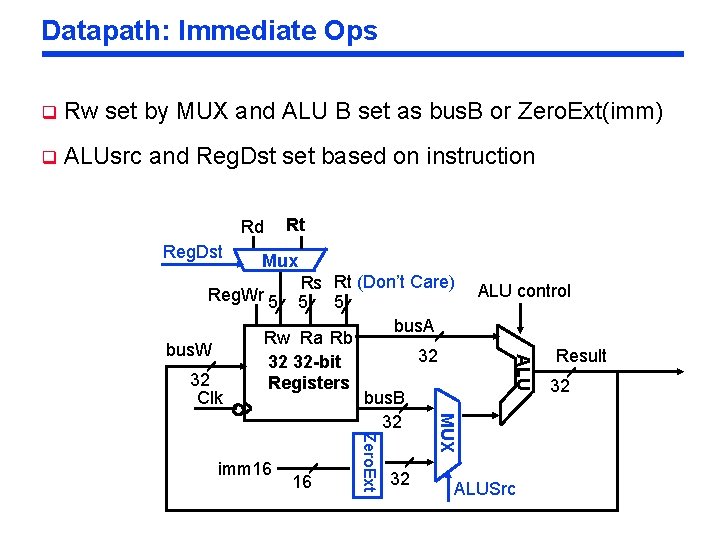

Datapath: Immediate Ops q Rw set by MUX and ALU B set as bus. B or Zero. Ext(imm) q ALUsrc and Reg. Dst set based on instruction Rd Reg. Dst Rt Mux ALU 16 Zero. Ext imm 16 ALU control MUX Rs Rt (Don’t Care) Reg. Wr 5 5 5 bus. A Rw Ra Rb bus. W 32 32 32 -bit 32 Registers bus. B Clk 32 32 ALUSrc Result 32

![Load RTL q Load instruction lw rt rs imm Fetch instruction from memory MemPC Load RTL q Load instruction lw rt, rs, imm Fetch instruction from memory Mem[PC];](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-10.jpg)

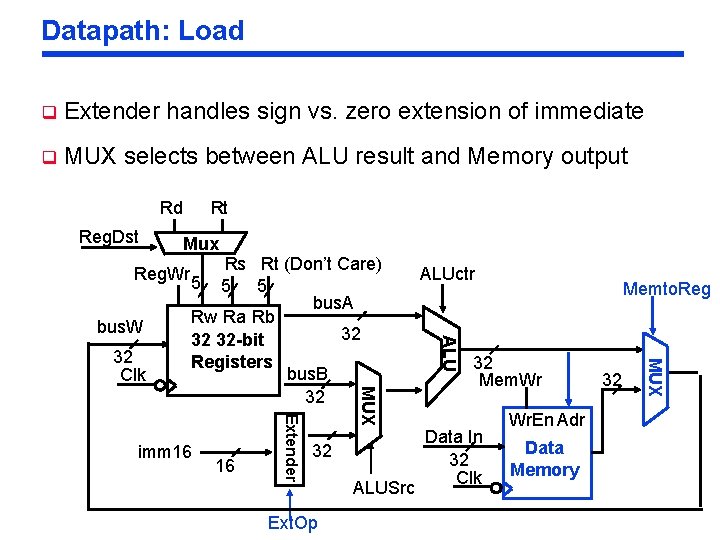

Load RTL q Load instruction lw rt, rs, imm Fetch instruction from memory Mem[PC]; Addr <- R[rs]+ Sign. Ext(imm); Compute memory address Bits R[rt] <- Mem[Addr]; Load data into register PC <- PC + 4; Calculate next address 6 5 OP rs 5 16 rt second first source register (dest) immediate

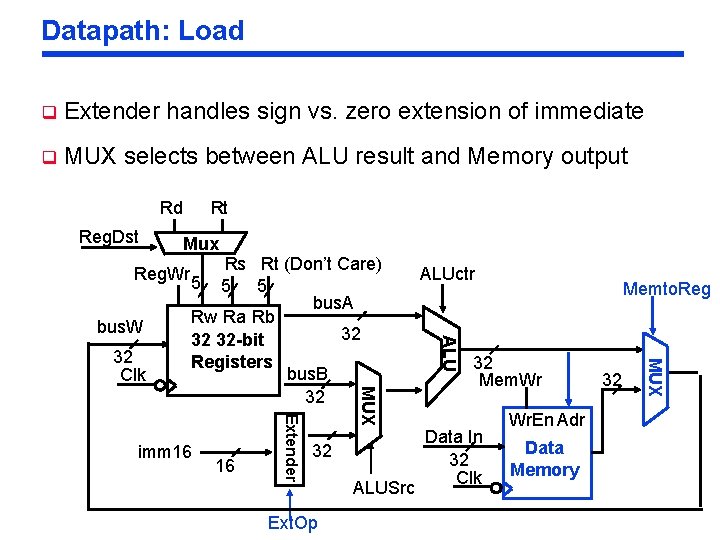

Datapath: Load q Extender handles sign vs. zero extension of immediate q MUX selects between ALU result and Memory output Rt Rd Reg. Dst Mux bus. W MUX 16 Extender imm 16 32 Ext. Op ALUSrc Memto. Reg 32 Mem. Wr Data In 32 Clk Wr. En Adr Data Memory 32 MUX 32 Clk ALUctr ALU Rs Rt (Don’t Care) 5 5 bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 32 Reg. Wr 5

![Store RTL q Store instruction sw rt rs imm Fetch instruction from memory MemPC Store RTL q Store instruction sw rt, rs, imm Fetch instruction from memory Mem[PC];](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-12.jpg)

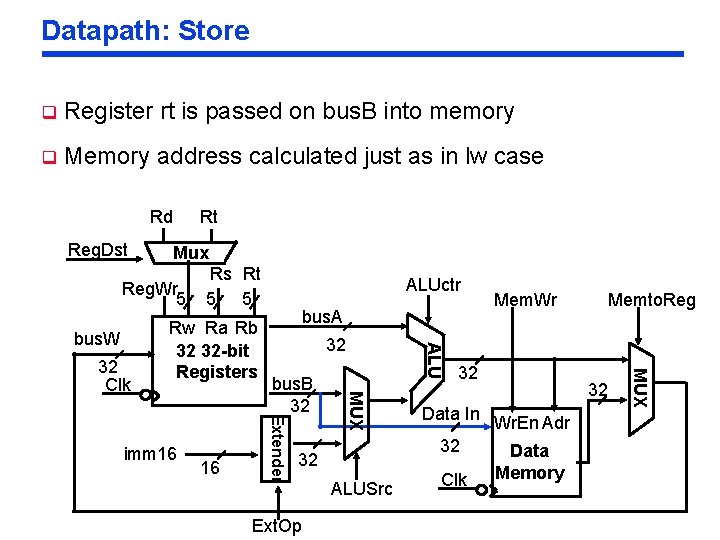

Store RTL q Store instruction sw rt, rs, imm Fetch instruction from memory Mem[PC]; Addr <- R[rs]+ Sign. Ext(imm); Compute memory addr Bits Mem[Addr] <- R[rt]; Load data into register PC <- PC + 4; Calculate next address 6 5 OP rs 5 16 rt second first source register immediate

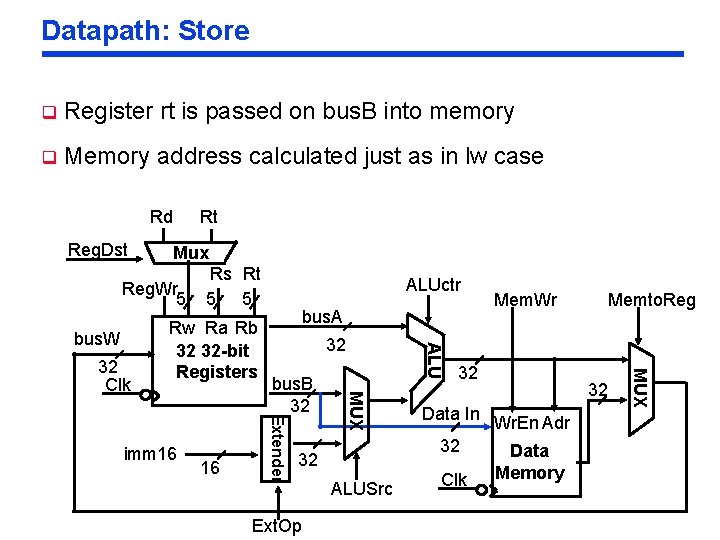

Datapath: Store q Register rt is passed on bus. B into memory q Memory address calculated just as in lw case Rd Reg. Dst Mux Reg. Wr 5 16 32 bus. B 32 Extender imm 16 bus. A Ext. Op 32 Data In 32 32 ALUSrc Mem. Wr Clk Memto. Reg 32 Wr. En Adr Data Memory MUX Rw Ra Rb 32 32 -bit Registers ALUctr MUX 32 Clk Rs Rt 5 5 ALU bus. W Rt

![Branch RTL q Branch instruction beq rs rt imm Fetch instruction from memory MemPC Branch RTL q Branch instruction beq rs, rt, imm Fetch instruction from memory Mem[PC];](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-14.jpg)

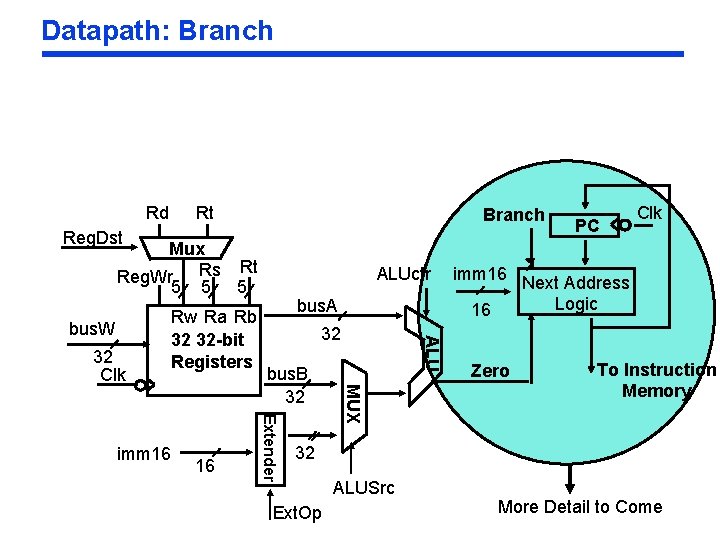

Branch RTL q Branch instruction beq rs, rt, imm Fetch instruction from memory Mem[PC]; Diff <- R[rs] – R[rt]; Calculate branch condition if (Diff eq 0) Test if equal PC <- PC + 4 + Sign. Ext(imm)*4; Calculate PC Relative address else PC <- PC + 4; Calculate next address Bits 6 5 5 16 OP rs rt imm first source second source immediate

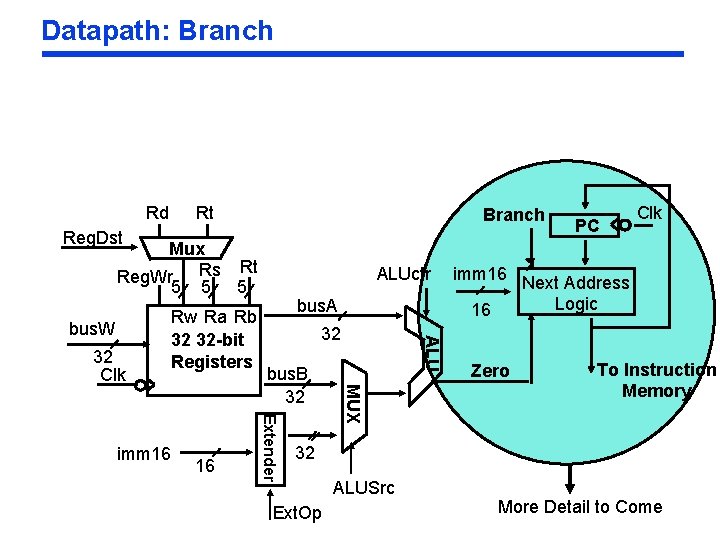

Datapath: Branch Rt Rd Branch Reg. Dst Mux Rt Reg. Wr Rs 5 5 5 16 bus. B 32 Extender imm 16 32 MUX 32 Clk bus. A ALU bus. W Rw Ra Rb 32 32 -bit Registers ALUctr PC Clk imm 16 Next Address Logic 16 Zero To Instruction Memory 32 Ext. Op ALUSrc More Detail to Come

![The Next Address q PC is byteaddressed in instruction memory l Sequential PC31 0 The Next Address q PC is byte-addressed in instruction memory l Sequential PC[31: 0]](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-16.jpg)

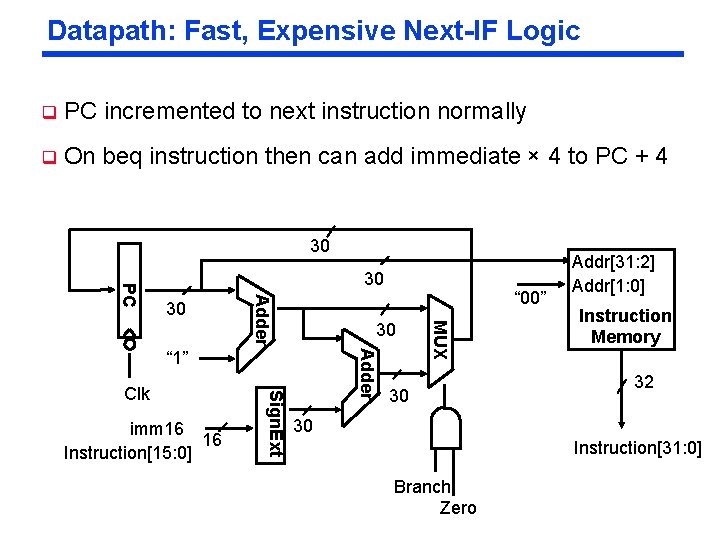

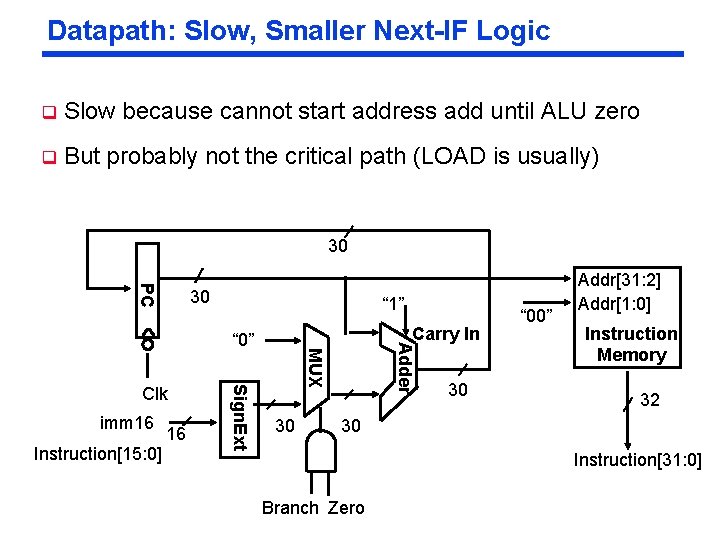

The Next Address q PC is byte-addressed in instruction memory l Sequential PC[31: 0] = PC[31: 0] + 4 l Branch operation PC[31: 0] = PC[31: 0] + 4 + Sign. Ext(imm) × 4 q Instruction Addresses l PC is byte addressed, but instructions are 4 bytes long l Therefore 2 LSBs of the 32 bit PC are always 0 l No reason to have hardware keep the 2 LSBs Þ Simplify hardware by using 30 bit PC - Sequential PC[31: 2] = PC[31: 2] + 1 - Branch operation PC[31: 2] = PC[31: 2] + 1 + Sign. Ext(imm)

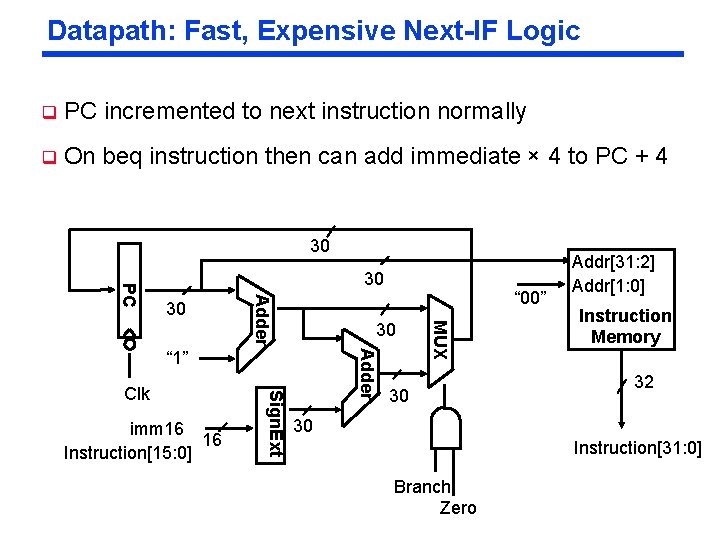

Datapath: Fast, Expensive Next-IF Logic q PC incremented to next instruction normally q On beq instruction then can add immediate × 4 to PC + 4 30 30 30 Sign. Ext imm 16 16 Instruction[15: 0] Adder “ 1” Clk “ 00” MUX Adder PC 30 30 Addr[31: 2] Addr[1: 0] Instruction Memory 32 30 Instruction[31: 0] Branch Zero

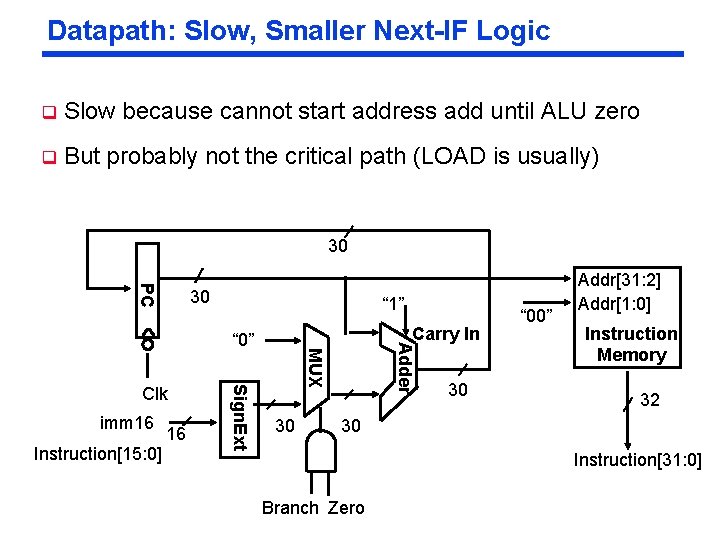

Datapath: Slow, Smaller Next-IF Logic q Slow because cannot start address add until ALU zero q But probably not the critical path (LOAD is usually) 30 PC 30 “ 1” Instruction[15: 0] 16 MUX imm 16 Sign. Ext Clk Adder Carry In “ 0” 30 30 “ 00” Addr[31: 2] Addr[1: 0] Instruction Memory 32 30 Instruction[31: 0] Branch Zero

![Jump RTL q Jump instruction j target MemPC Fetch instruction from memory PC31 2 Jump RTL q Jump instruction j target Mem[PC]; Fetch instruction from memory PC[31: 2]](https://slidetodoc.com/presentation_image_h/1684b5c8145a798ce214cd03ca272b5e/image-19.jpg)

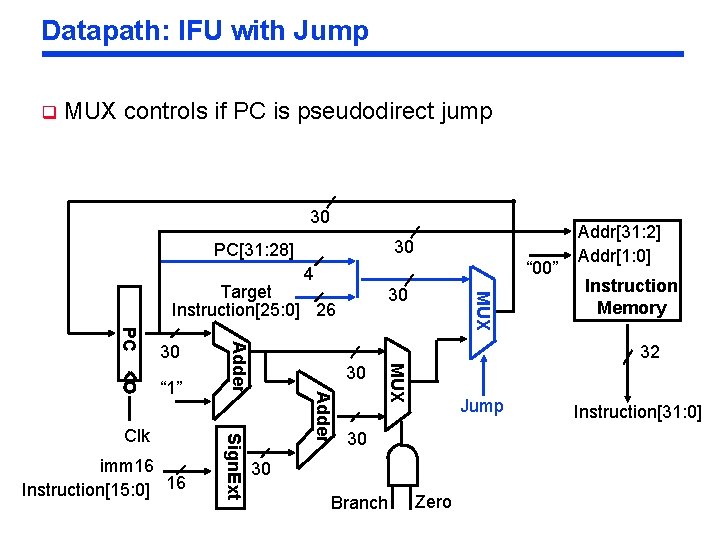

Jump RTL q Jump instruction j target Mem[PC]; Fetch instruction from memory PC[31: 2] <- PC[31: 28] || target[25: 0]; Bits Calculate next address 6 26 OP target jump target address

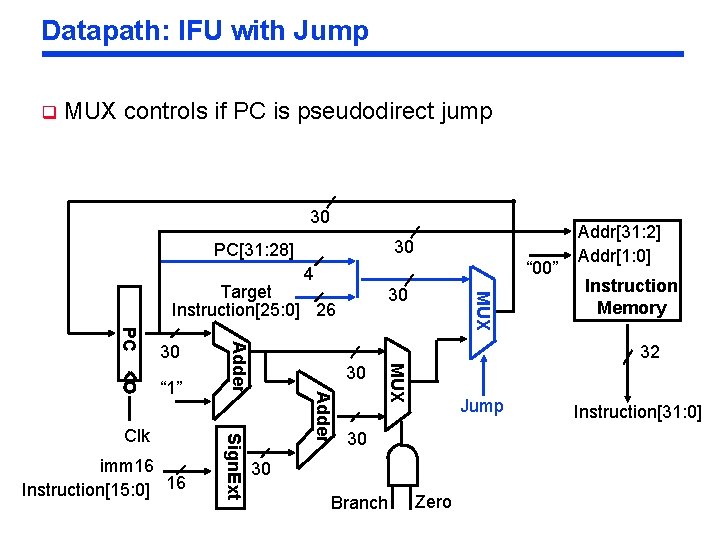

Datapath: IFU with Jump q MUX controls if PC is pseudodirect jump 30 30 PC[31: 28] “ 00” 4 Target Instruction[25: 0] 26 MUX 30 MUX imm 16 Instruction[15: 0] 16 Sign. Ext Clk Instruction Memory 32 Adder “ 1” Adder PC 30 30 Addr[31: 2] Addr[1: 0] Jump 30 30 Branch Zero Instruction[31: 0]

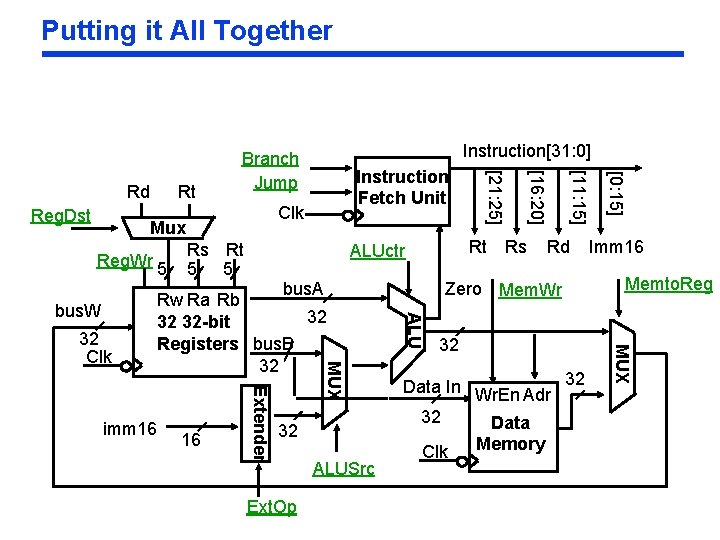

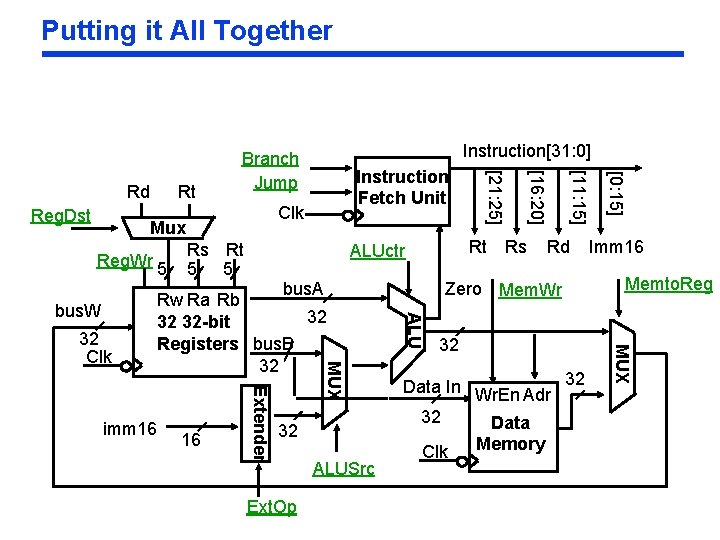

Putting it All Together Reg. Wr 5 bus. A 16 Extender imm 16 32 Ext. Op ALUSrc Rs Rd Zero Mem. Wr 32 Data In Wr. En Adr 32 32 Data Clk Memory Imm 16 Memto. Reg MUX Rw Ra Rb 32 32 32 -bit Registers bus. B 32 MUX 32 Clk Rt ALUctr ALU bus. W Rs Rt 5 5 [0: 15] Mux [11: 15] Clk [16: 20] Reg. Dst Instruction Fetch Unit [21: 25] Rt Rd Instruction[31: 0] Branch Jump

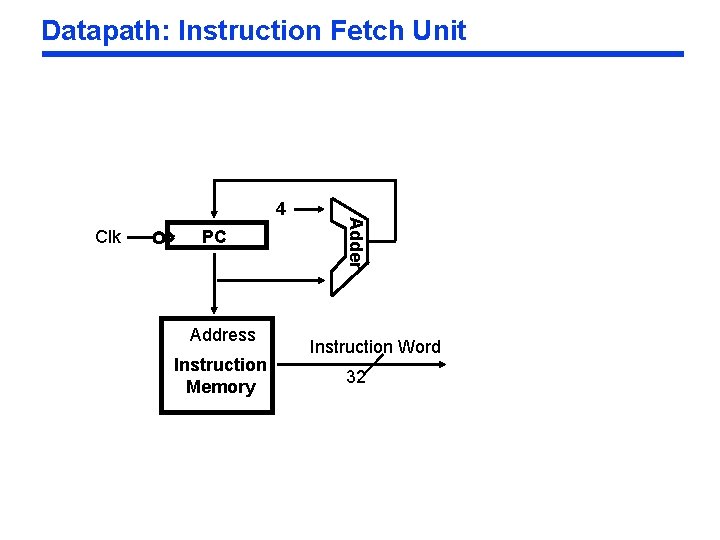

A Real MIPS Datapath