Computer Organization Assembly Language Organization of the Personal

Computer Organization & Assembly Language Organization of the Personal Computers

Outline Memory Registers 2

Memory 3

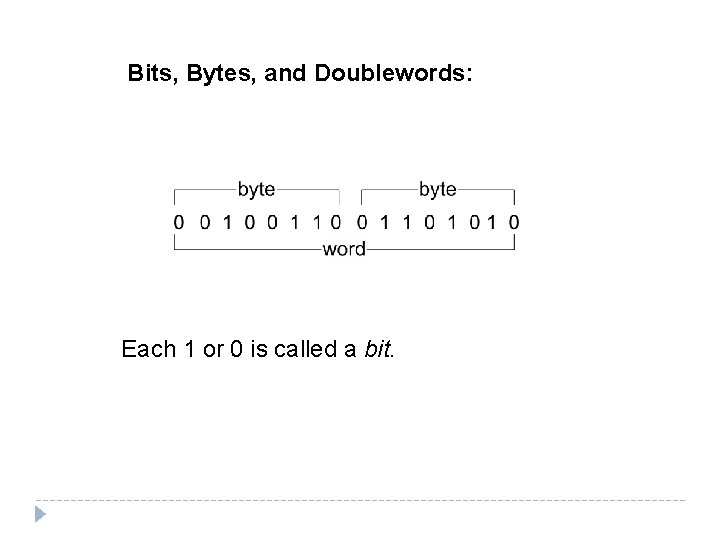

Bits, Bytes, and Doublewords: Each 1 or 0 is called a bit.

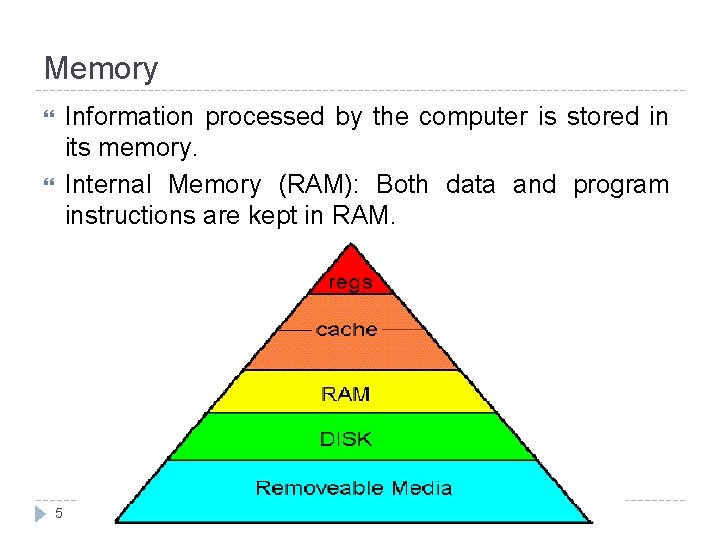

Memory Information processed by the computer is stored in its memory. Internal Memory (RAM): Both data and program instructions are kept in RAM. 5

Contd. . Memory is organized into a collection of bytes. Each byte is identified by a number – Address Number of bits in an address depends on the processor Example: - Intel 8086: 20 -bit address, Intel 80286: 24 -bit address Data stored in a memory byte – Contents Number of bits used in the address determines the number of bytes that can be accessed by the processor. Example: If processor uses 20 - bit address, it can access 220 = 1048576 bytes = 1 MB of memory 6

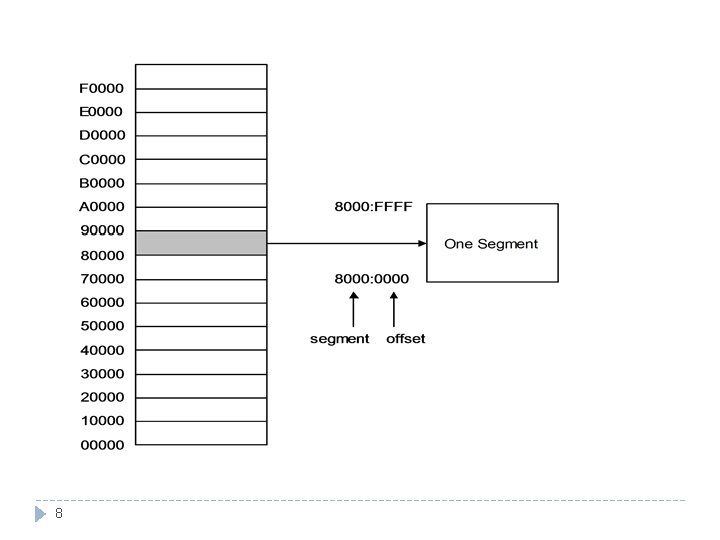

Memory Segments A memory segment is a block of 216 (or 64 K) consecutive memory bytes. Each segment has a number. Within a segment, memory location is specified by an offset. This is the number of bytes from the beginning of the segment. 7

8

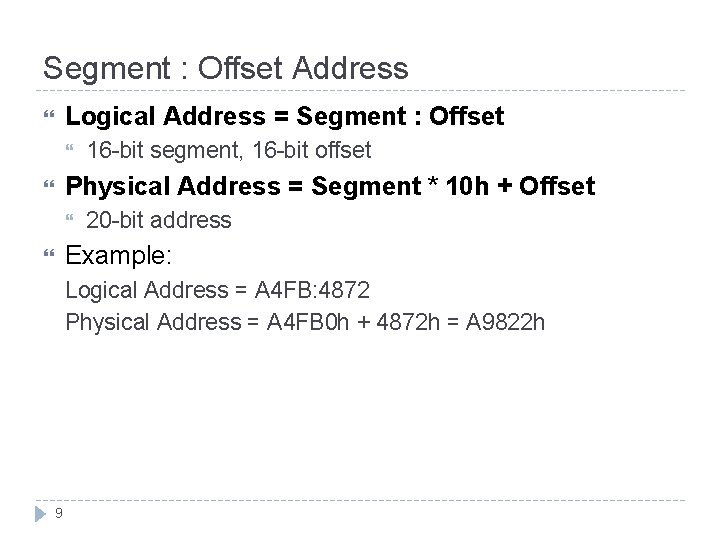

Segment : Offset Address Logical Address = Segment : Offset 16 -bit segment, 16 -bit offset Physical Address = Segment * 10 h + Offset 20 -bit address Example: Logical Address = A 4 FB: 4872 Physical Address = A 4 FB 0 h + 4872 h = A 9822 h 9

Program Segments A typical machine language program is loaded into following different memory segments: Code Segment Data Segment Stack is a data structure used by processor to implement procedure calls. 10

Registers 11

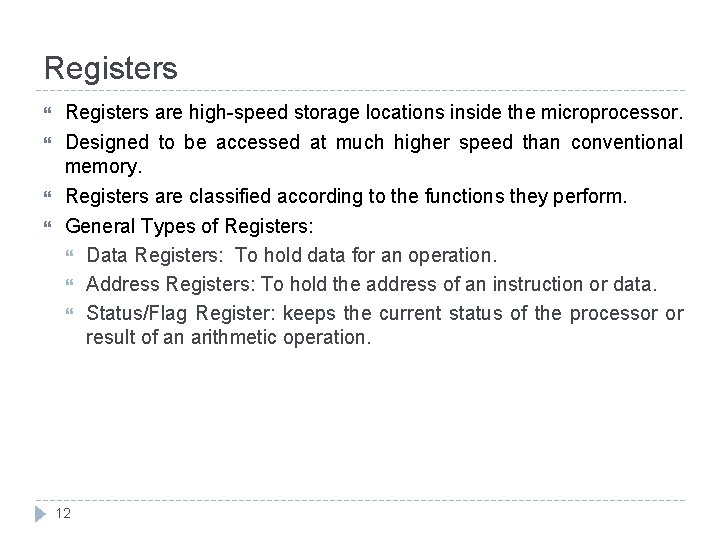

Registers Registers are high-speed storage locations inside the microprocessor. Designed to be accessed at much higher speed than conventional memory. Registers are classified according to the functions they perform. General Types of Registers: Data Registers: To hold data for an operation. Address Registers: To hold the address of an instruction or data. Status/Flag Register: keeps the current status of the processor or result of an arithmetic operation. 12

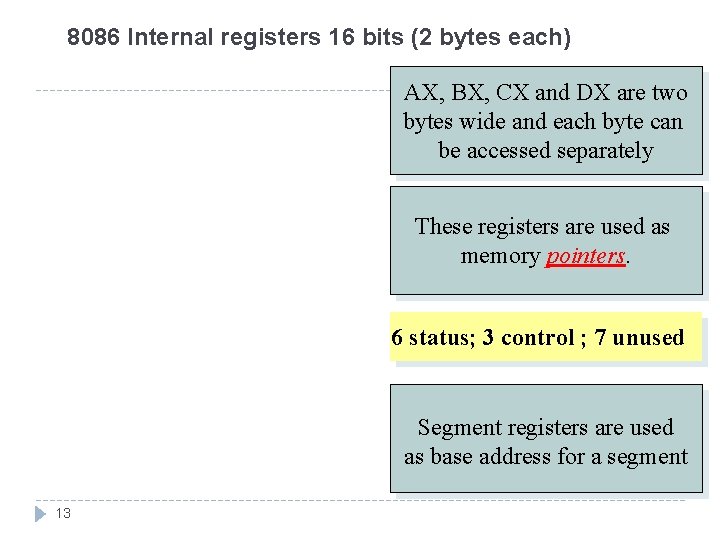

8086 Internal registers 16 bits (2 bytes each) AX, BX, CX and DX are two bytes wide and each byte can be accessed separately These registers are used as memory pointers. 6 status; 3 control ; 7 unused Segment registers are used as base address for a segment 13

General Purpose/Data Registers Following four registers are available to the programmer for general data manipulation: AX (Accumulator): Used in arithmetic, logic and data transfer instructions. Also required in multiplication, division and input/output operations. BX (Base): It can hold a memory address that points to a variable. CX (Counter): Act as a counter for repeating or looping instructions. These instructions automatically repeat and decrement CX and quit when equals to 0. DX (Data): It has a special role in multiply and divide operations. Also used in input/output operations. 14

Segment Registers Store addresses of instruction and data in memory. These values are used by the processor to access memory locations. CS (Code): Defines the starting address of the section of memory holding code. DS (Data): Defines the section of memory that holds most of the data used by programs. ES (Extra): This is an additional data segment that is used by some of the string instructions. SS (Stack): It defines the area of the memory used for stack 15

Pointers and Index Registers These can be accessed only as 16 bit registers. IP - instruction pointer: Always points to next instruction to be executed. IP register always works together with CS segment register and it points to currently executing instruction. SI - source index register: Can be used for pointer addressing of data. Offset address relative to DS DI - destination index register: Can be used for pointer addressing of data. Offset address relative to ES SI and DI used in string movement instructions. SP and BP are used to access data inside the stack segment BP - base pointer: Primarily used to access parameters passed via the stack. Offset address relative to SS SP – stack pointer: Always points to top item on the stack. Offset address relative to SS 16

80386 Extended Registers The 80386/80486 processor contain 32 -bit registers which greatly improve the efficiency of program that take advantage of them. 17 EAX, EBX, ECX, EDX, EFLAGS EIP EBP, ESI, EDI.

Flag Register 16 -bit special register Each bit position is assigned to show the status of CPU or the results of arithmetic operations. Each relevant bit position is given a name; other positions are undefined. Two Types: 18 Control Flags: Individual bits may be set to control the CPU’s Operation Status Flags: The Status bits reflect the outcome of arithmetic and logical operations performed by the CPU.

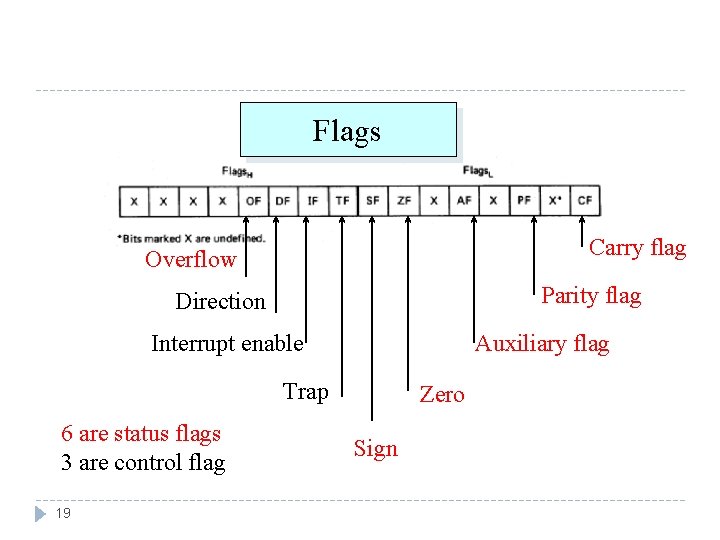

Flags Carry flag Overflow Parity flag Direction Interrupt enable Auxiliary flag Trap 6 are status flags 3 are control flag 19 Zero Sign

Status Flags Carry Flag: The Carry Flag is set to 1 if after the result of an ALU operation, there is a carry out from the MSB else it is 0 Sign Flag: The Sign Flag is set to the value of the MSB. If the MSB is 0 then the Sign flag is 0, if the MSB is 1 then the Sign Flag is 1. Zero Flag: If after an ALU operation the result of the operation is All Zeros, then the Zero Flag is set to 1 otherwise it is set to 0. Overflow Flag: It is set when the signed result of an arithmetic operation is too large to fit into destination area. Auxiliary Carry Flag: is set when an operation causes a carry from bit 3 to bit 4 or borrow from bit 4 to bit 3. Parity Flag: reflects the number of bits in the result of an operation that are set. If number is even, parity is even. If it is odd, parity is odd. This is used by Operating System to verify correct transmission of data. 20

Control Flags Direction Flag: Controls the assumed direction used by string processing instructions. 1=Up, 0=Down Interrupt Flag: Enable/Disable external interrupt. Trap Flag: determines whether or not CPU will be halted after each instruction. 21

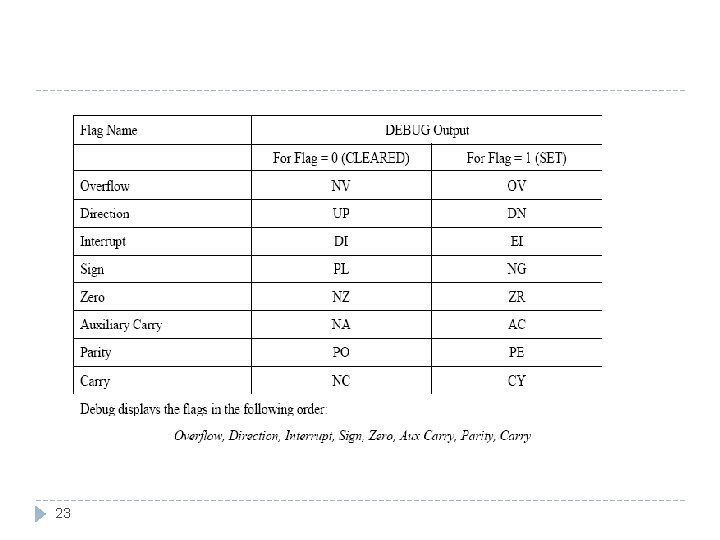

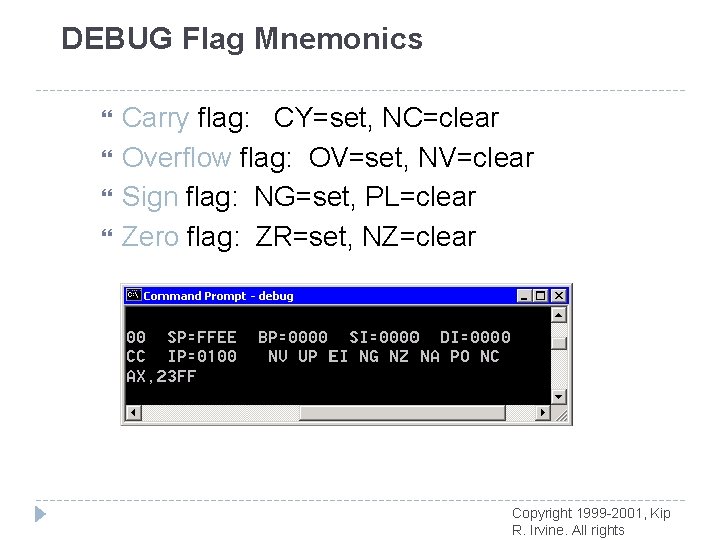

Default Values When Debug is first loaded, the following defaults are in the effect: All segment registers are set to the bottom of free memory, just above debug program. IP is set to 0100 h. Debug reserves 256 bytes of stack space at the end of current segment. All of available memory is allocated (reserved). The flags are set to the following values: NV (Overflow flag clear), UP (Direction flag= up), EI (interrupt enabled), PL (Sign flag = positive), NZ (Zero flag set), NA (Auxiliary Carry Flag clear), PO (Odd Parity), NC (Carry flag clear) 22

23

DEBUG Examples Experimenting with the Carry, Overflow, Sign, and Zero flags Copyright 1999 -2001, Kip R. Irvine. All rights reserved.

DEBUG Flag Mnemonics Carry flag: CY=set, NC=clear Overflow flag: OV=set, NV=clear Sign flag: NG=set, PL=clear Zero flag: ZR=set, NZ=clear Copyright 1999 -2001, Kip R. Irvine. All rights

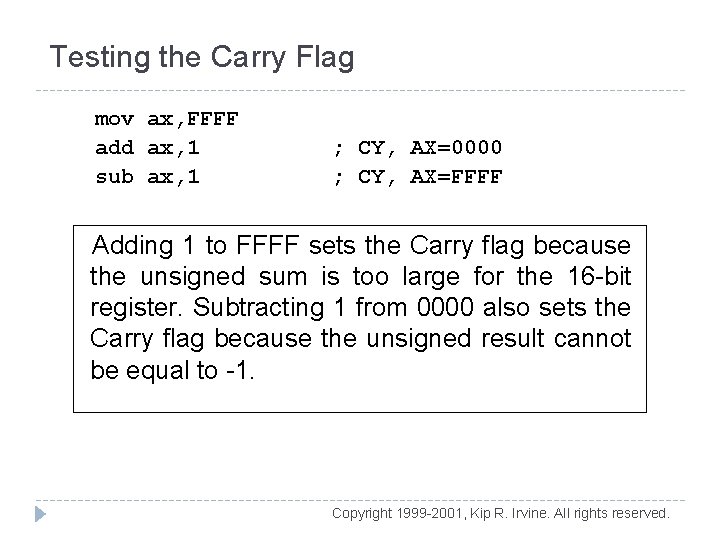

Testing the Carry Flag mov ax, FFFF add ax, 1 sub ax, 1 ; CY, AX=0000 ; CY, AX=FFFF Adding 1 to FFFF sets the Carry flag because the unsigned sum is too large for the 16 -bit register. Subtracting 1 from 0000 also sets the Carry flag because the unsigned result cannot be equal to -1. Copyright 1999 -2001, Kip R. Irvine. All rights reserved.

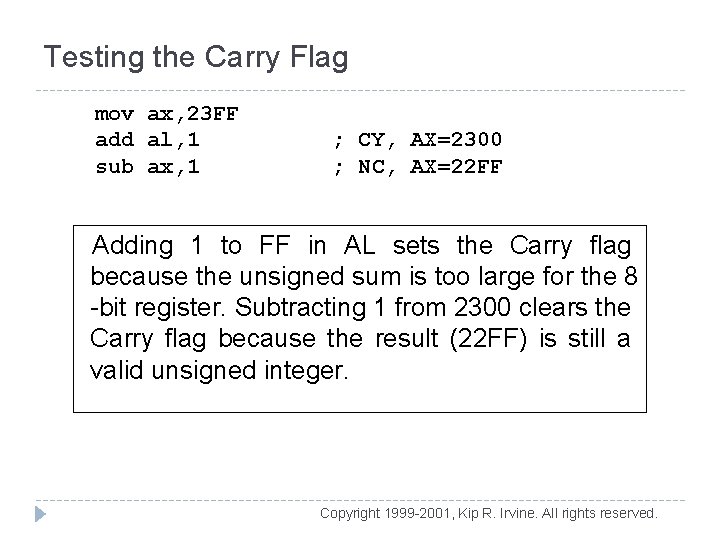

Testing the Carry Flag mov ax, 23 FF add al, 1 sub ax, 1 ; CY, AX=2300 ; NC, AX=22 FF Adding 1 to FF in AL sets the Carry flag because the unsigned sum is too large for the 8 -bit register. Subtracting 1 from 2300 clears the Carry flag because the result (22 FF) is still a valid unsigned integer. Copyright 1999 -2001, Kip R. Irvine. All rights reserved.

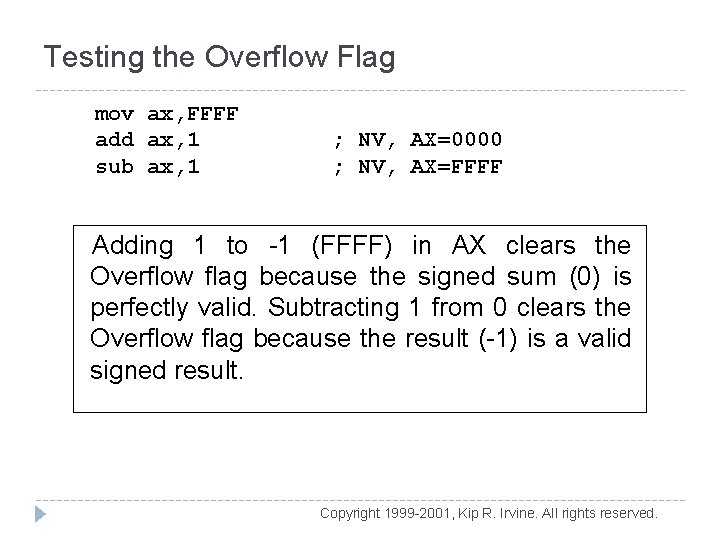

Testing the Overflow Flag mov ax, FFFF add ax, 1 sub ax, 1 ; NV, AX=0000 ; NV, AX=FFFF Adding 1 to -1 (FFFF) in AX clears the Overflow flag because the signed sum (0) is perfectly valid. Subtracting 1 from 0 clears the Overflow flag because the result (-1) is a valid signed result. Copyright 1999 -2001, Kip R. Irvine. All rights reserved.

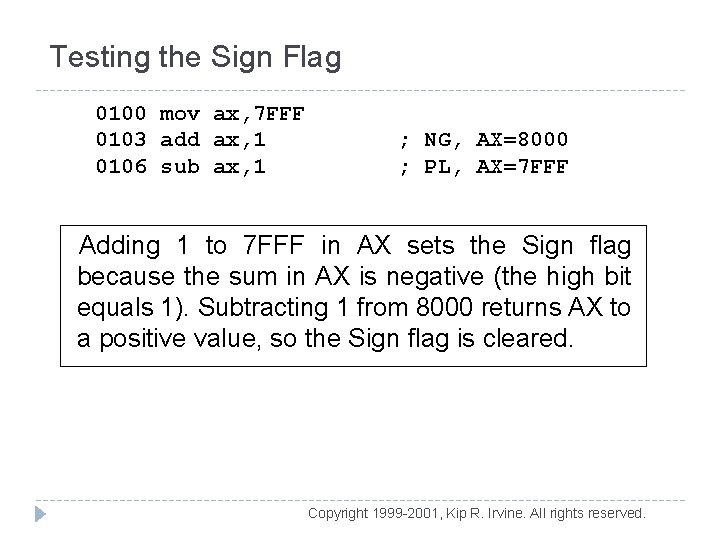

Testing the Sign Flag 0100 mov ax, 7 FFF 0103 add ax, 1 0106 sub ax, 1 ; NG, AX=8000 ; PL, AX=7 FFF Adding 1 to 7 FFF in AX sets the Sign flag because the sum in AX is negative (the high bit equals 1). Subtracting 1 from 8000 returns AX to a positive value, so the Sign flag is cleared. Copyright 1999 -2001, Kip R. Irvine. All rights reserved.

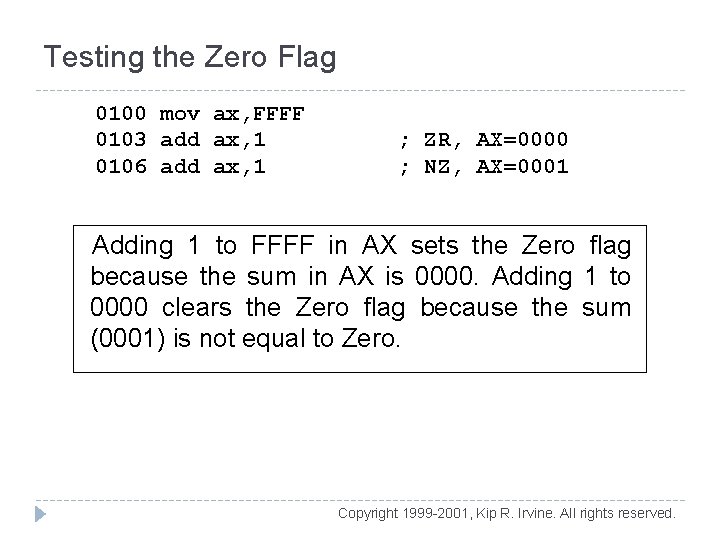

Testing the Zero Flag 0100 mov ax, FFFF 0103 add ax, 1 0106 add ax, 1 ; ZR, AX=0000 ; NZ, AX=0001 Adding 1 to FFFF in AX sets the Zero flag because the sum in AX is 0000. Adding 1 to 0000 clears the Zero flag because the sum (0001) is not equal to Zero. Copyright 1999 -2001, Kip R. Irvine. All rights reserved.

References Chapter 3, Ytha Yu and Charles Marut, “Assembly Language Programming and Organization of IBM PC” 31

- Slides: 31