Computer Organization and Logic design COS 3602 Architecture

- Slides: 44

Computer Organization and Logic design COS 3602

Architecture & Organization 1 z Architecture is those attributes visible to the programmer y. Instruction set, number of bits used for data representation, I/O mechanisms, addressing techniques. ye. g. Is there a multiply instruction? z Organization is how features are implemented y. Control signals, interfaces, memory technology. ye. g. Is there a hardware multiply unit or is it done by repeated addition?

Structure & Function z Structure is the way in which components relate to each other z Function is the operation of individual components as part of the structure

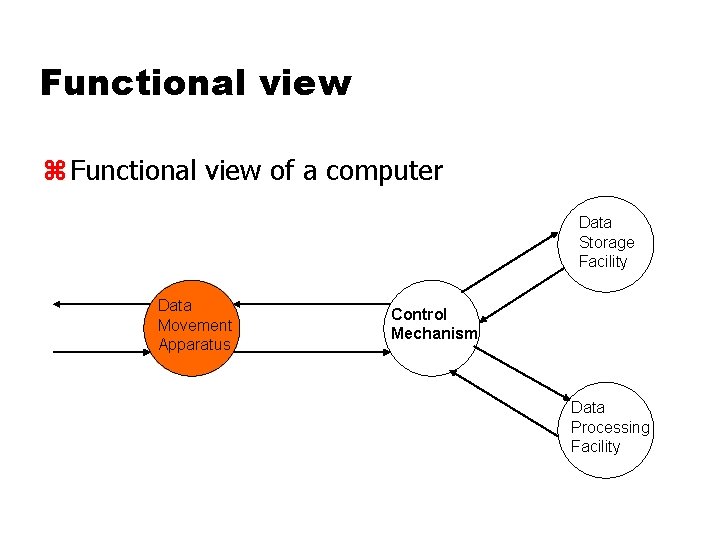

Function z All computer functions are: y. Data processing y. Data storage y. Data movement y. Control

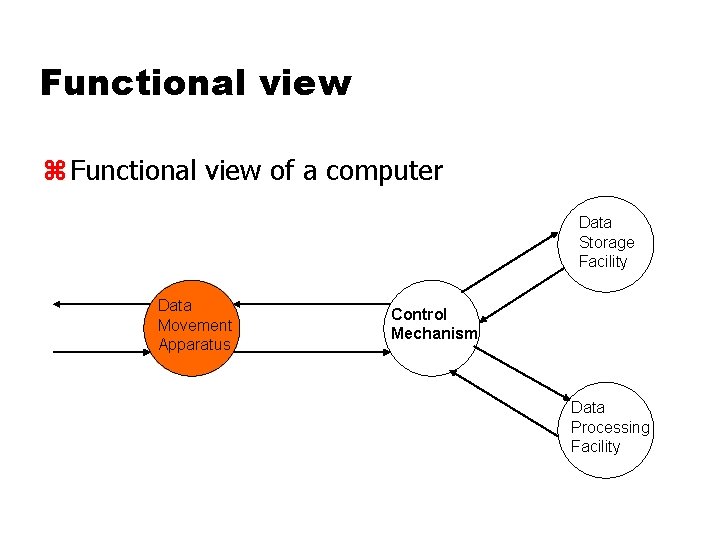

Functional view z Functional view of a computer Data Storage Facility Data Movement Apparatus Control Mechanism Data Processing Facility

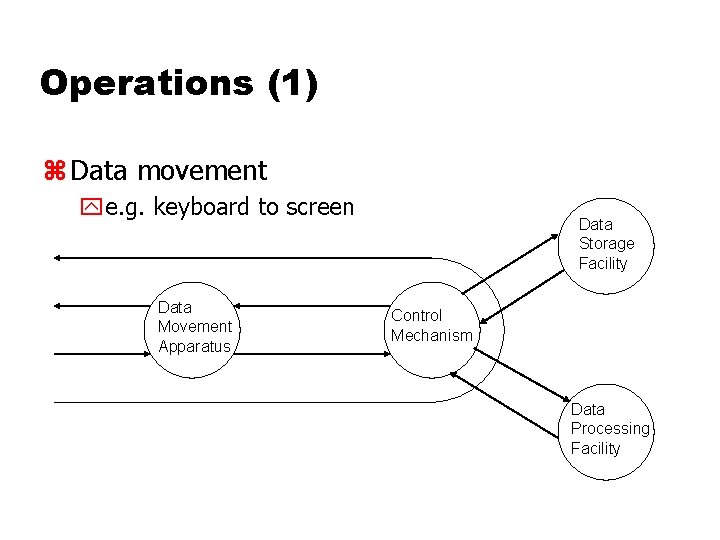

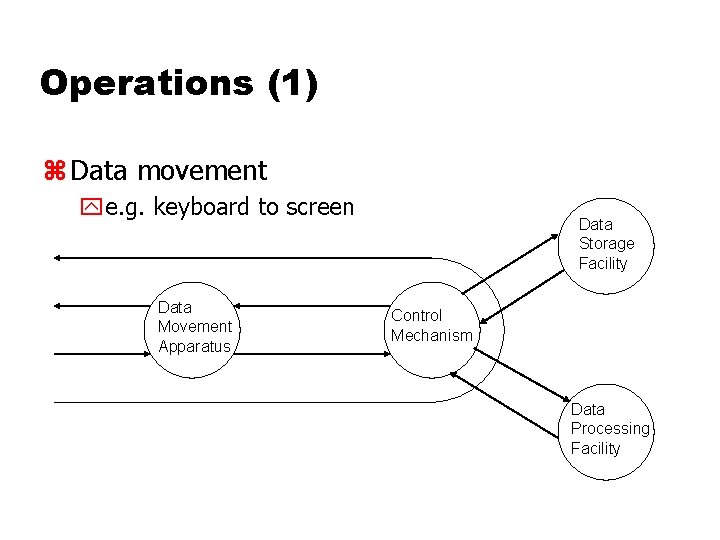

Operations (1) z Data movement ye. g. keyboard to screen Data Movement Apparatus Data Storage Facility Control Mechanism Data Processing Facility

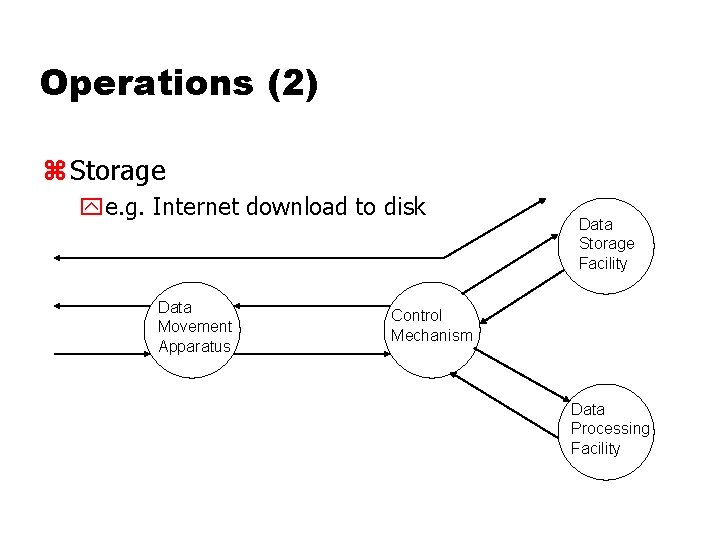

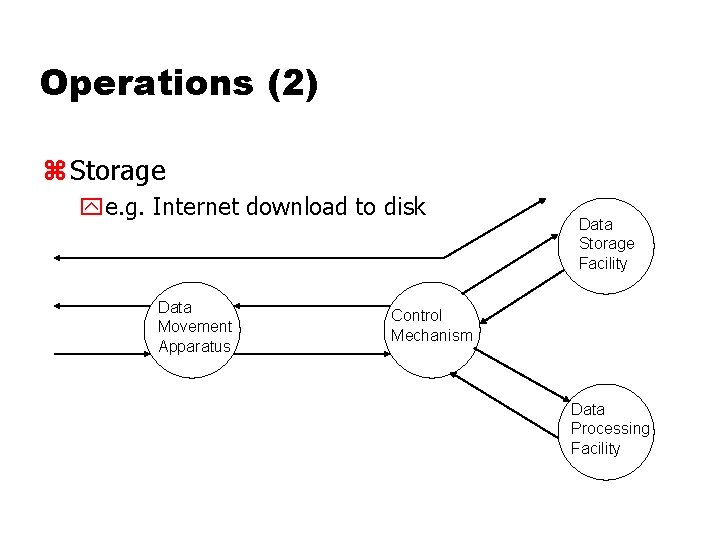

Operations (2) z Storage ye. g. Internet download to disk Data Movement Apparatus Data Storage Facility Control Mechanism Data Processing Facility

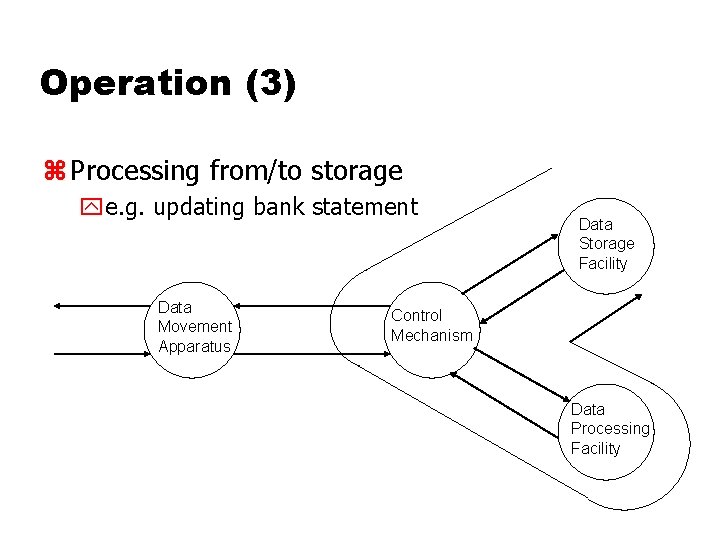

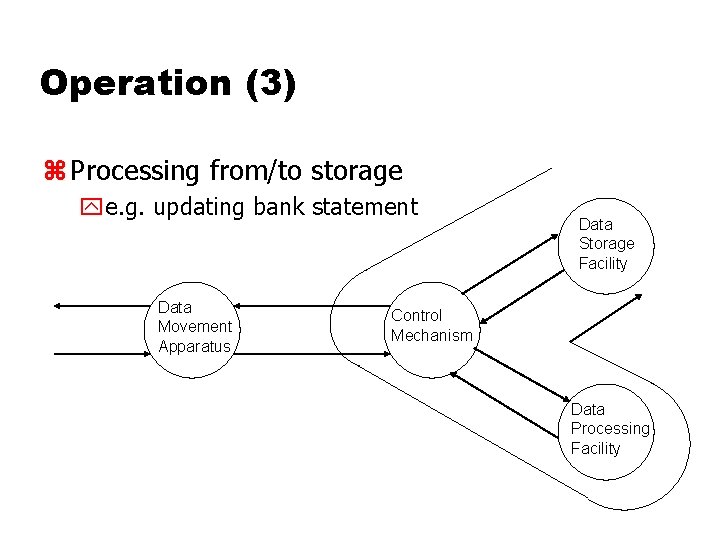

Operation (3) z Processing from/to storage ye. g. updating bank statement Data Movement Apparatus Data Storage Facility Control Mechanism Data Processing Facility

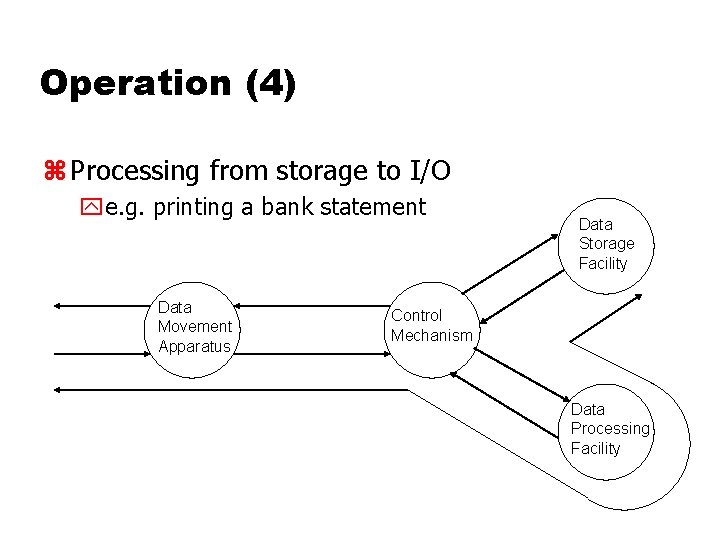

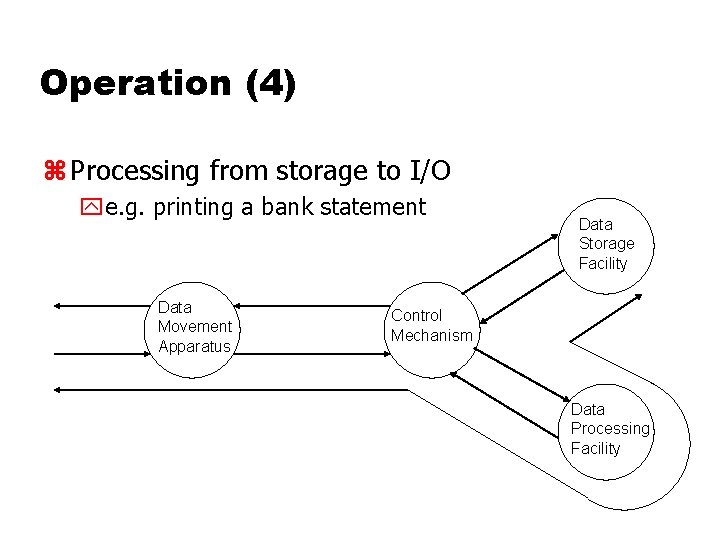

Operation (4) z Processing from storage to I/O ye. g. printing a bank statement Data Movement Apparatus Data Storage Facility Control Mechanism Data Processing Facility

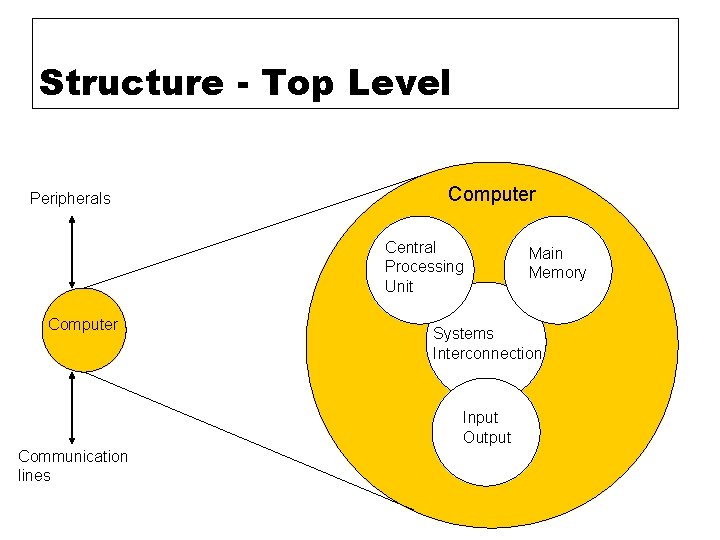

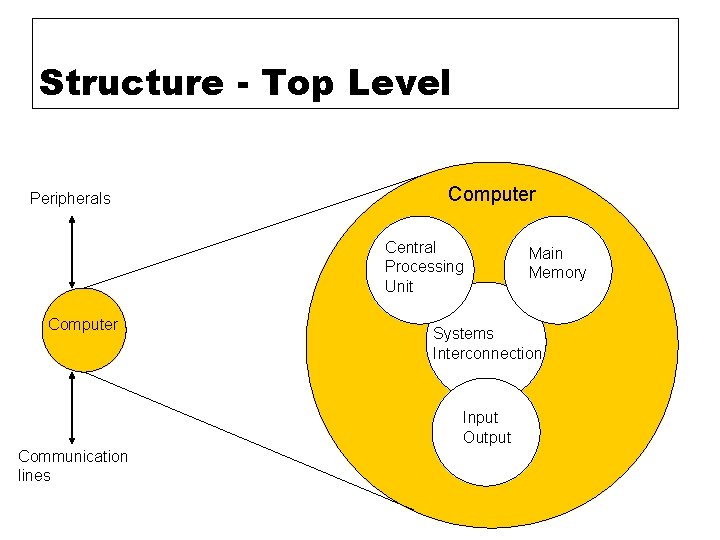

Structure - Top Level Peripherals Computer Central Processing Unit Computer Systems Interconnection Input Output Communication lines Main Memory

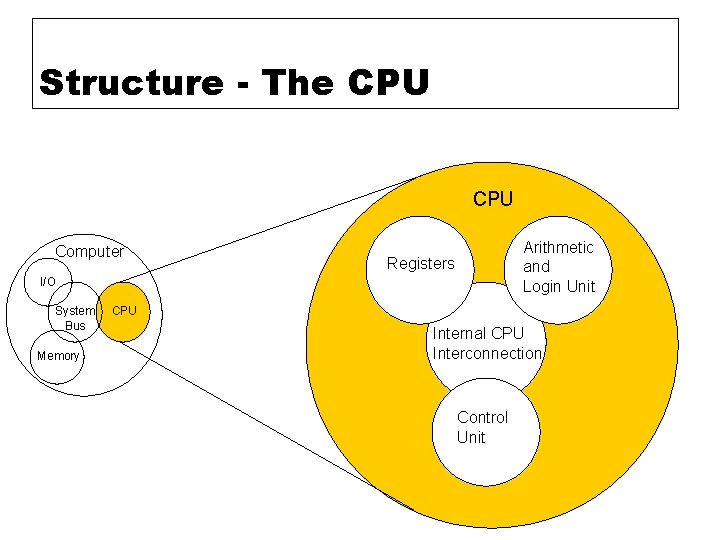

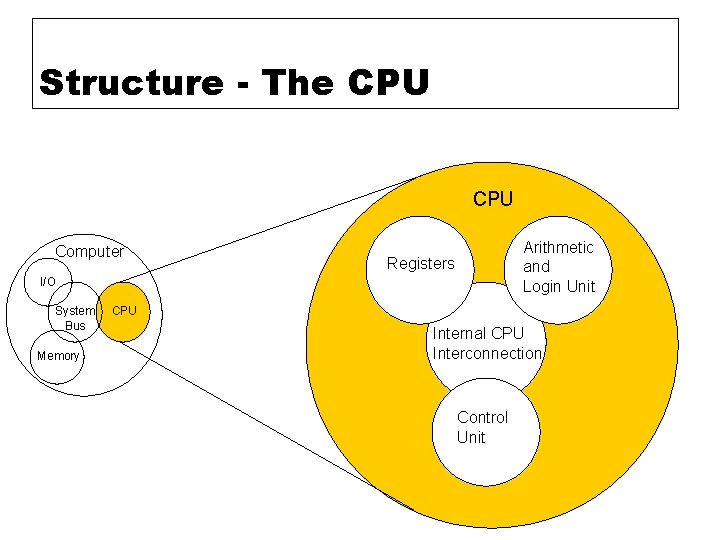

Structure - The CPU Computer Arithmetic and Login Unit Registers I/O System Bus Memory CPU Internal CPU Interconnection Control Unit

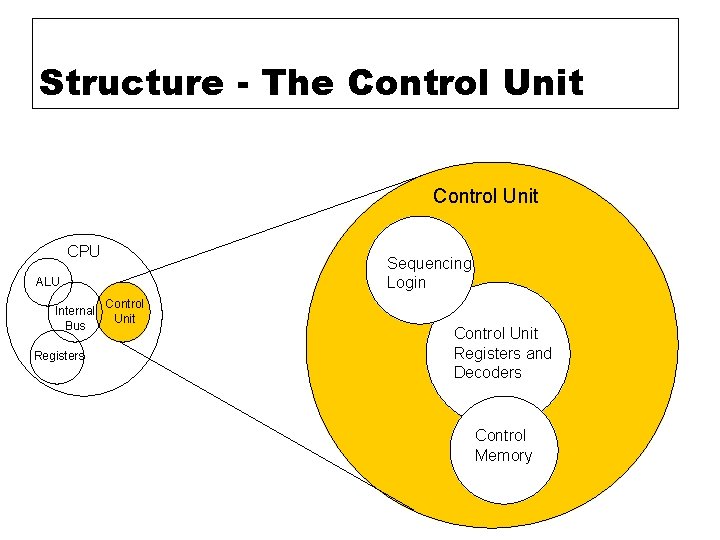

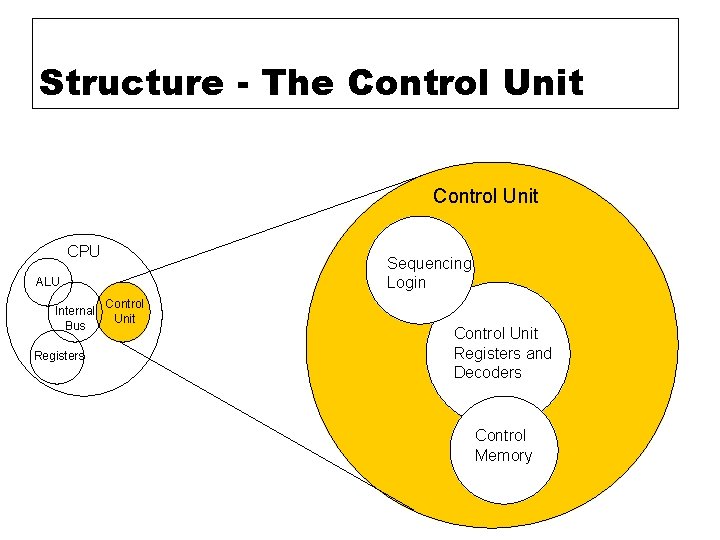

Structure - The Control Unit CPU Sequencing Login ALU Internal Bus Registers Control Unit Registers and Decoders Control Memory

Computer Architecture is the design of computer , including their instruction sets, hardware components, and system organization. The computer architecture consists of two parts ; • Instruction set architecture (ISA( • Hardware system architecture (HAS (

• The instruction set architecture : เปนการแสดงรายละเอยด Software/Hardware ทใชในการเชอมตอทอยในระดบ ภาษาเครองทโปรแกรมเมอรมองเหนได รวมถง • The instruction set • The instruction formats • The available addressing techniques • The format of the available data types

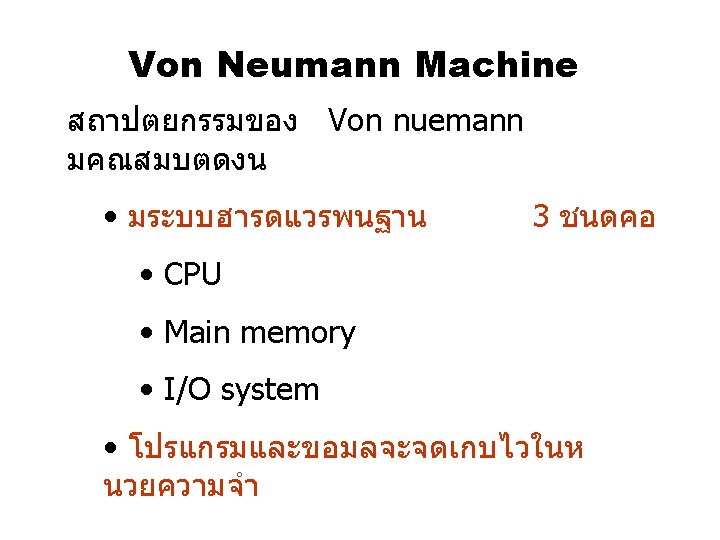

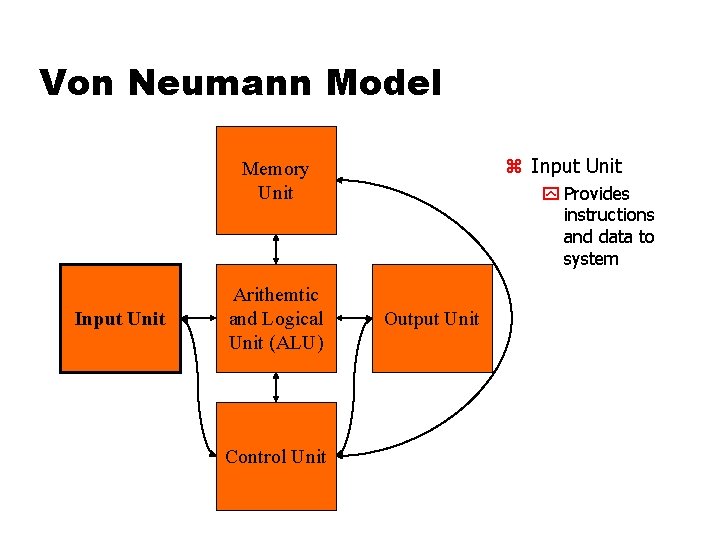

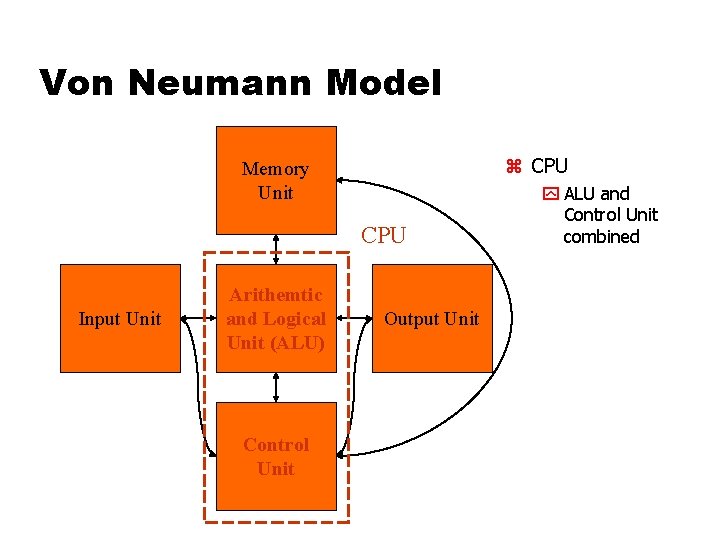

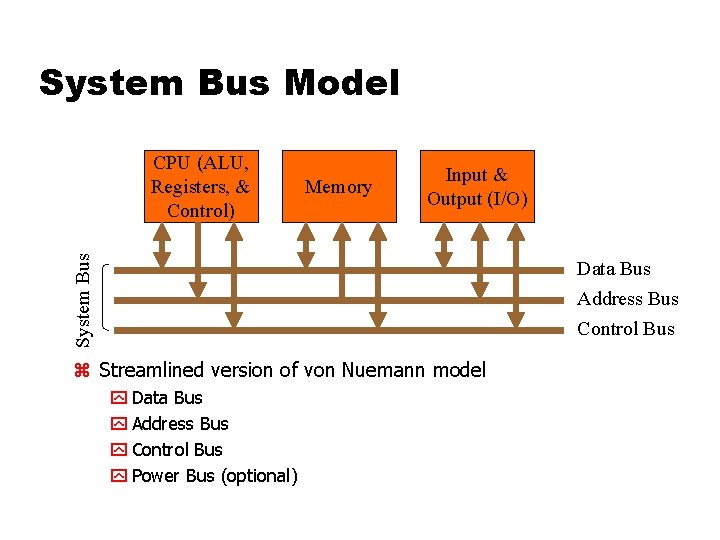

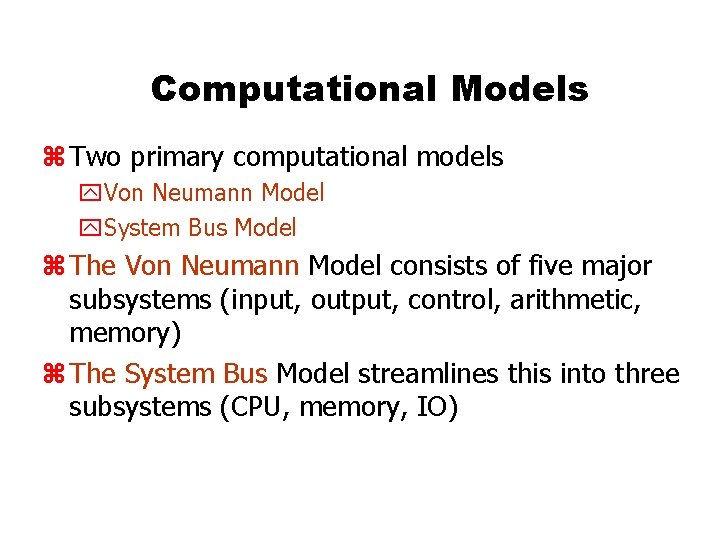

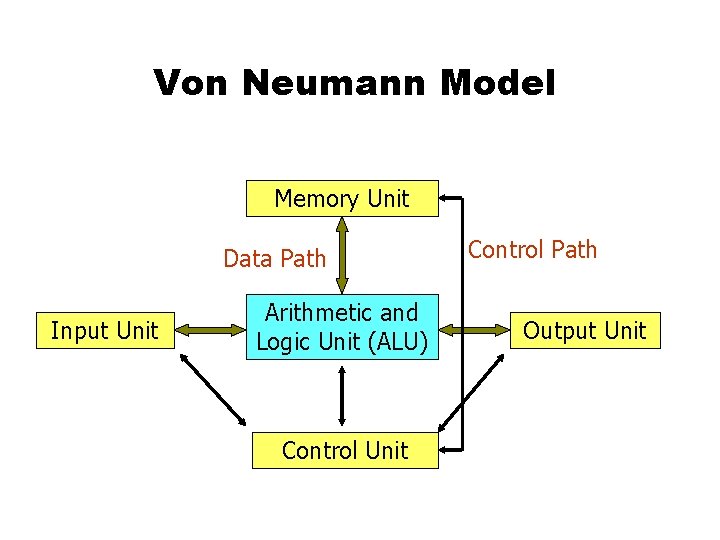

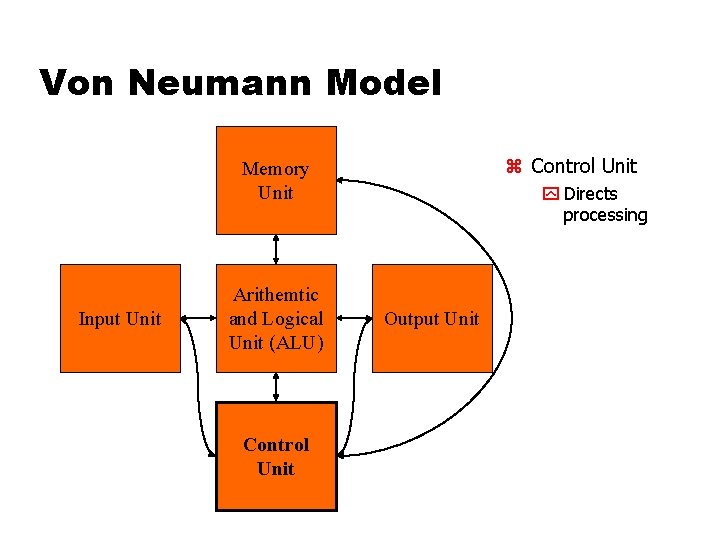

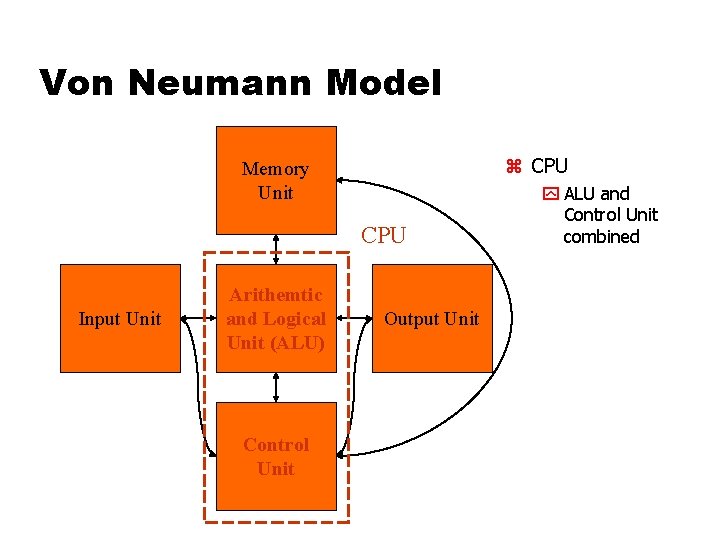

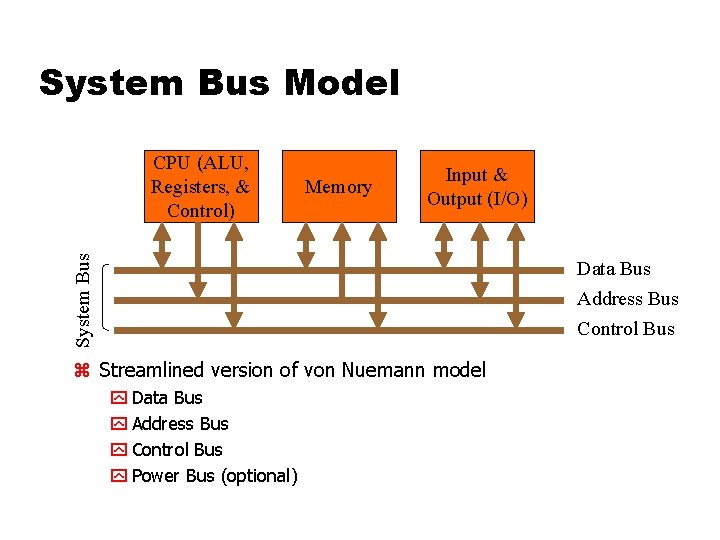

Computational Models z Two primary computational models y. Von Neumann Model y. System Bus Model z The Von Neumann Model consists of five major subsystems (input, output, control, arithmetic, memory) z The System Bus Model streamlines this into three subsystems (CPU, memory, IO)

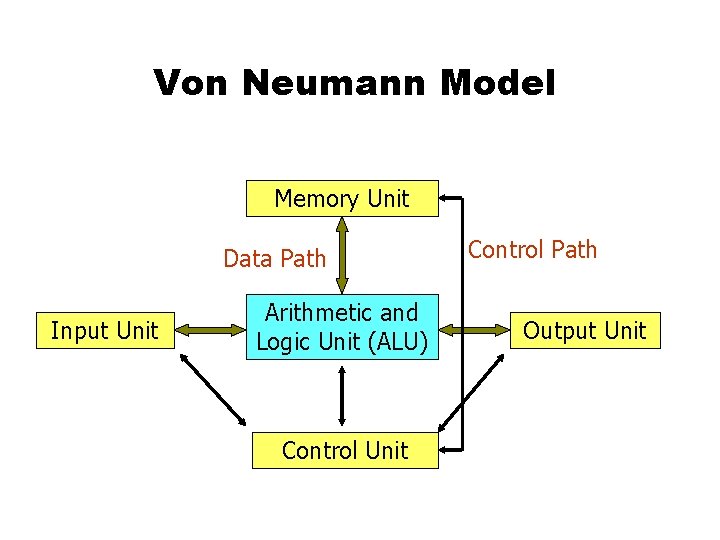

Von Neumann Model Memory Unit Data Path Input Unit Arithmetic and Logic Unit (ALU) Control Unit Control Path Output Unit

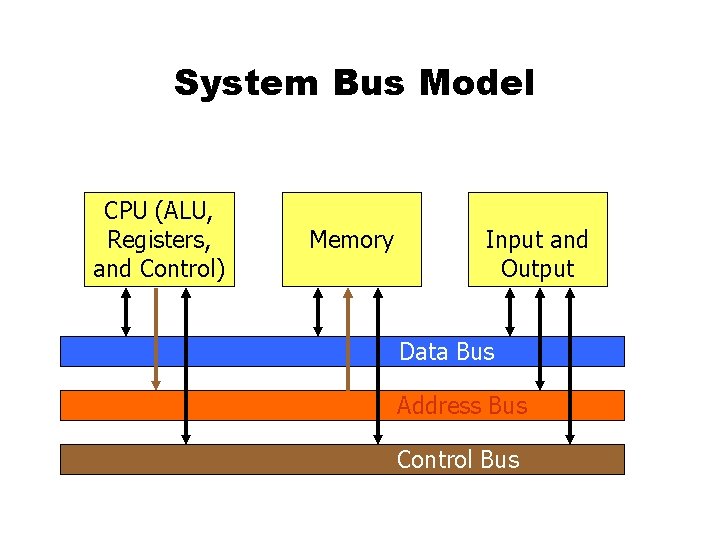

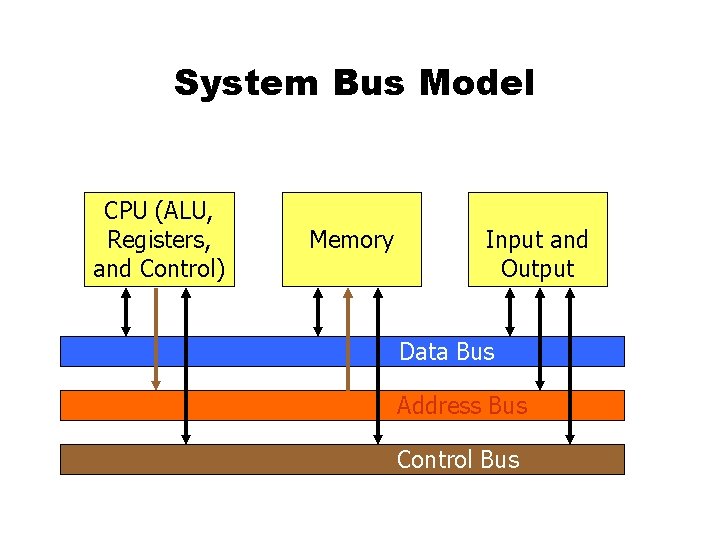

System Bus Model CPU (ALU, Registers, and Control) Memory Input and Output Data Bus Address Bus Control Bus

Computational Models z Consider the implications of these alternative designs y. Design 1: Central processor with special cabling to specialized devices y. Design 2: Multi-bus with common parsing of data and control packets for device-ids

Introduction to Computer Architecture z History z Computational Models z >> Levels of the Machine z Computer System Metaphor

Levels of the Machine z 1. Individual electrical components y. Transistors y. Resisters y. Capacitors z 2. Circuit boards z 3. Specialized devices y. Power supply y. Cooling fan

Levels of the Machine z 4. Specialized components y. Graphics accelerator y. Memory banks z 5. Mother board y. CPU y. Battery y. Plug-in expansion card slots y. Specialized components y. Connector for power supply

Levels of the Machine z 6. z 7. z 8. z 9. Operating system and device drivers Machine language Compilers and interpreters High-level languages y. Java y. C++ y. Visual Basic y. Microsoft Excel (? )

Levels of the Machine z 10. z 11. z 12. z 13. z 14. z 15. z 16. Single-user applications Network components and software Multi-user centralized applications Internet connection devices and s/w Internet utilities (global / specific) Web connection devices and s/w Web utilities (global / general)

Introduction to Computer Architecture z History z Computational Models z Levels of the Machine z >> Computer System

Typical Computer System z Hard Disk z Floppy Disk z Tape Backup z Random Access Memory z Central Processing Unit z Graphics Accelerator Card z Keyboard z Monitor z Printer

Computer System The intent of the following slides is to remind us to ask, when studying any computer component, “What problem is this intended to solve? ”

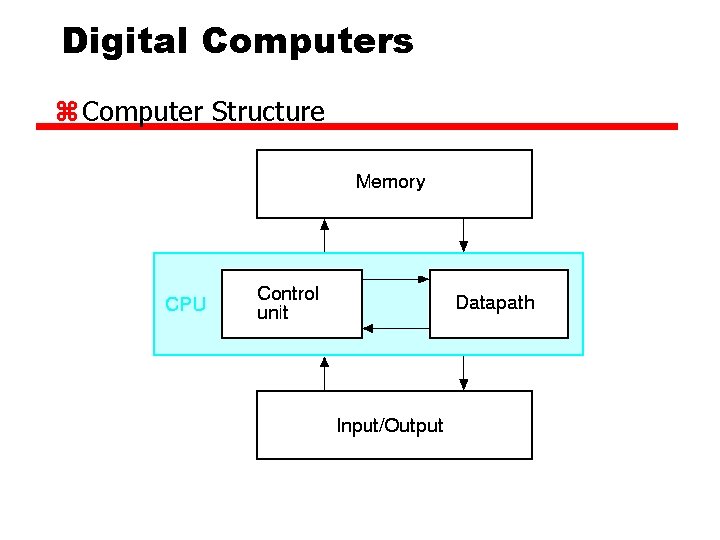

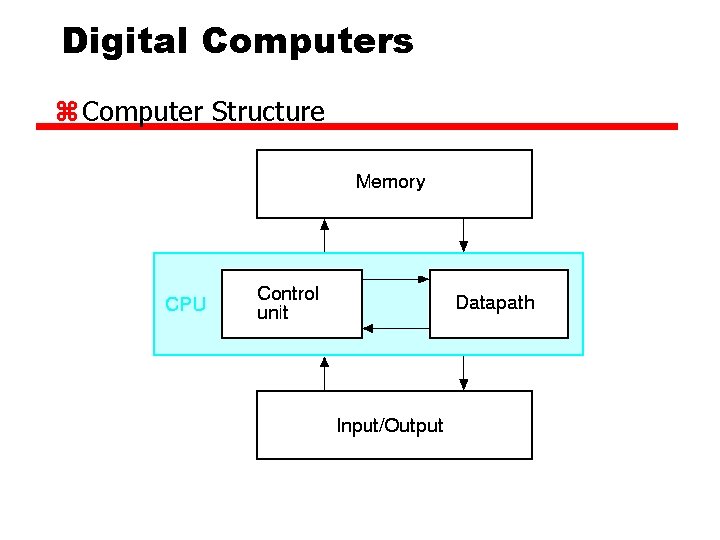

Digital Computers z Computer Structure

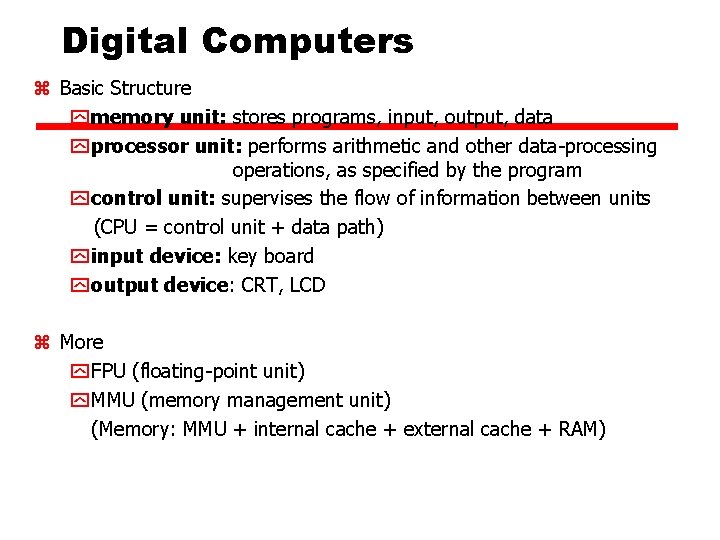

Digital Computers z Basic Structure y memory unit: stores programs, input, output, data y processor unit: performs arithmetic and other data-processing operations, as specified by the program y control unit: supervises the flow of information between units (CPU = control unit + data path) y input device: key board y output device: CRT, LCD z More y FPU (floating-point unit) y MMU (memory management unit) (Memory: MMU + internal cache + external cache + RAM)

Classification of Computer Architectures

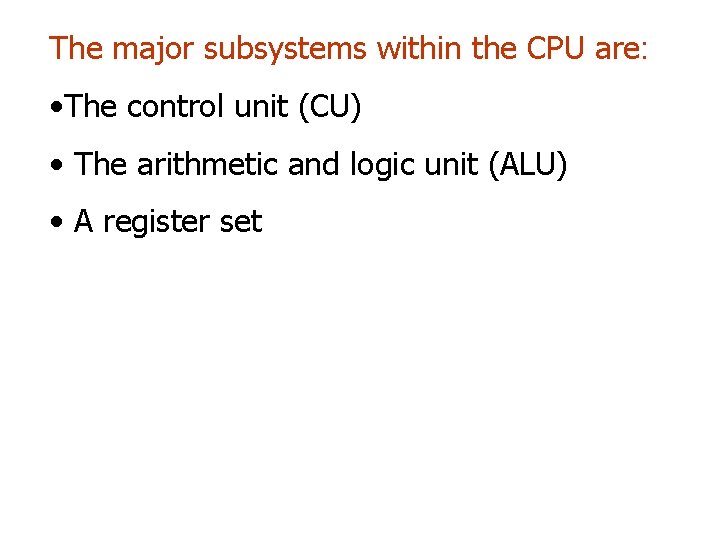

The major subsystems within the CPU are: • The control unit (CU) • The arithmetic and logic unit (ALU) • A register set

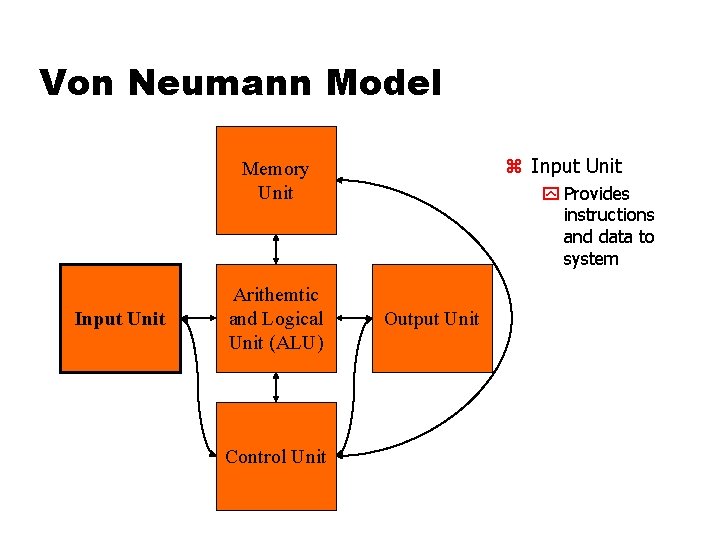

Von Neumann Model z Input Unit Memory Unit Input Unit Arithemtic and Logical Unit (ALU) Control Unit y Provides instructions and data to system Output Unit

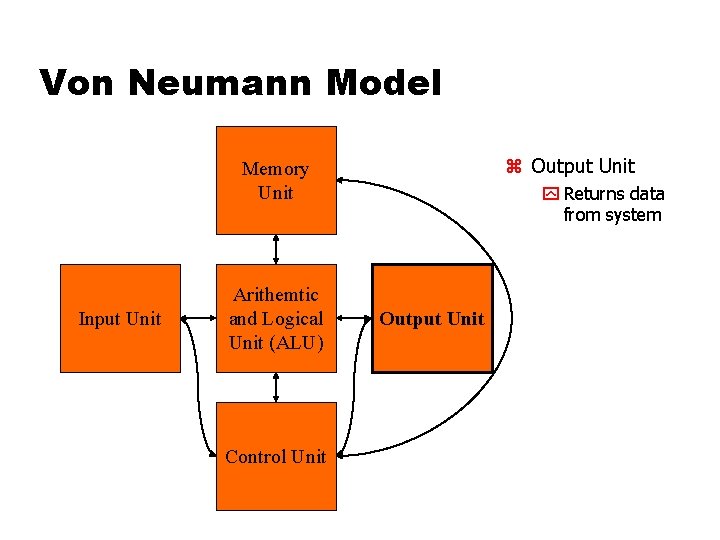

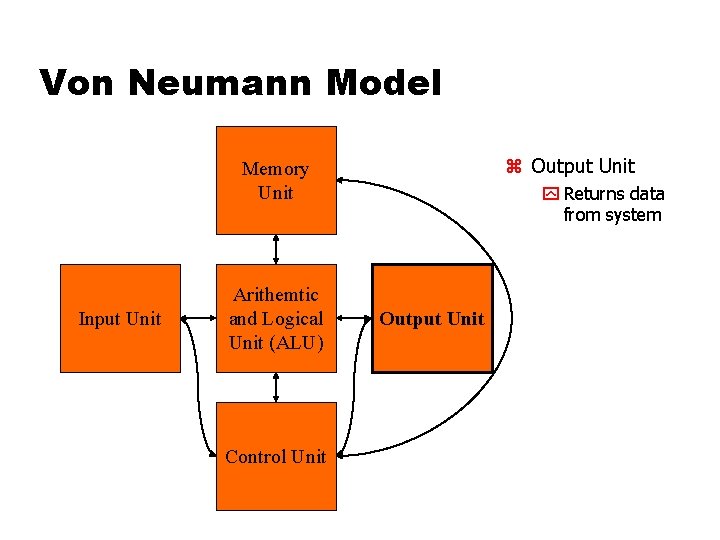

Von Neumann Model z Output Unit Memory Unit Input Unit Arithemtic and Logical Unit (ALU) Control Unit y Returns data from system Output Unit

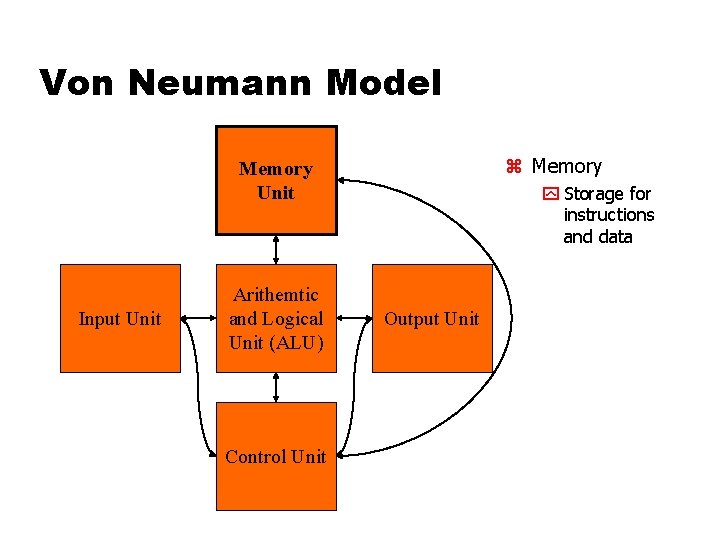

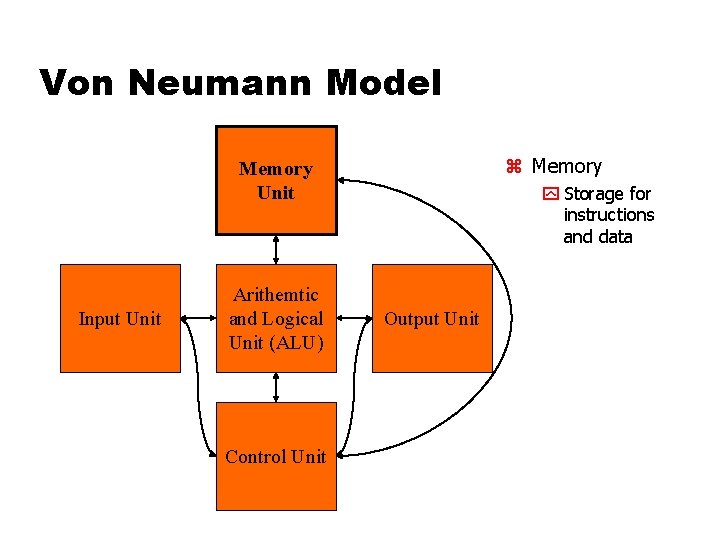

Von Neumann Model z Memory Unit Input Unit Arithemtic and Logical Unit (ALU) Control Unit y Storage for instructions and data Output Unit

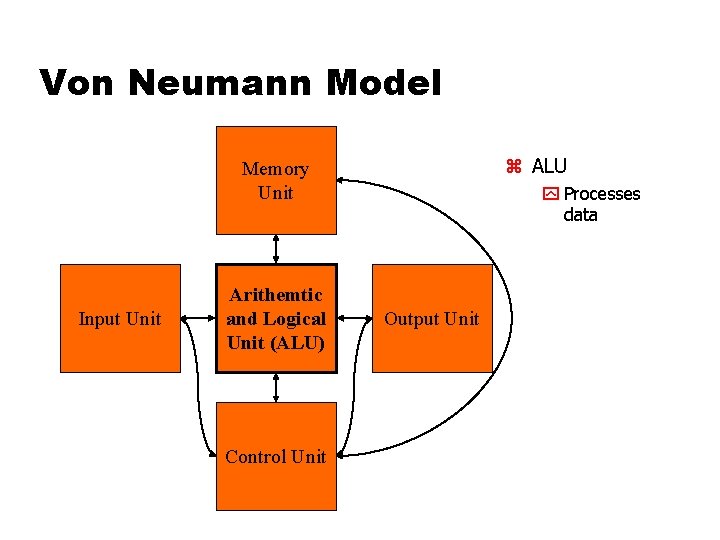

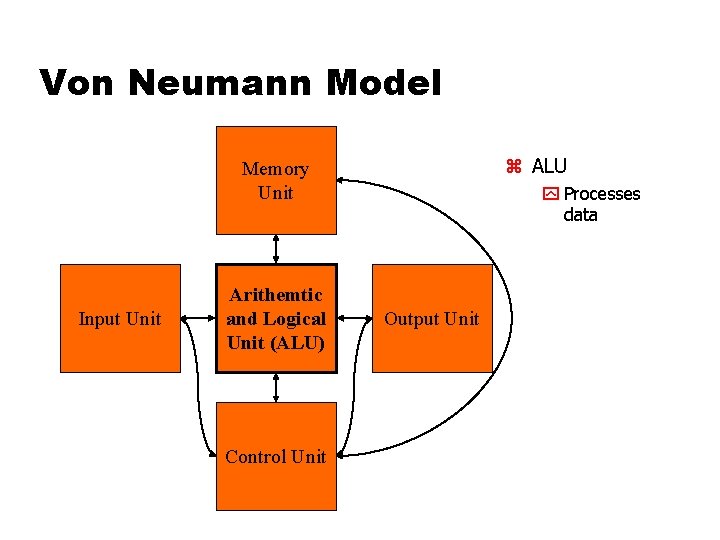

Von Neumann Model z ALU Memory Unit Input Unit Arithemtic and Logical Unit (ALU) Control Unit y Processes data Output Unit

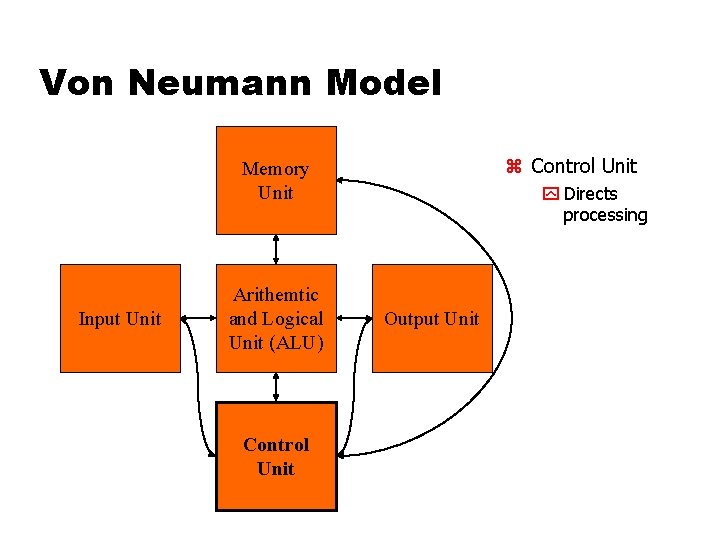

Von Neumann Model z Control Unit Memory Unit Input Unit Arithemtic and Logical Unit (ALU) Control Unit y Directs processing Output Unit

Von Neumann Model z CPU Memory Unit CPU Input Unit Arithemtic and Logical Unit (ALU) Control Unit Output Unit y ALU and Control Unit combined

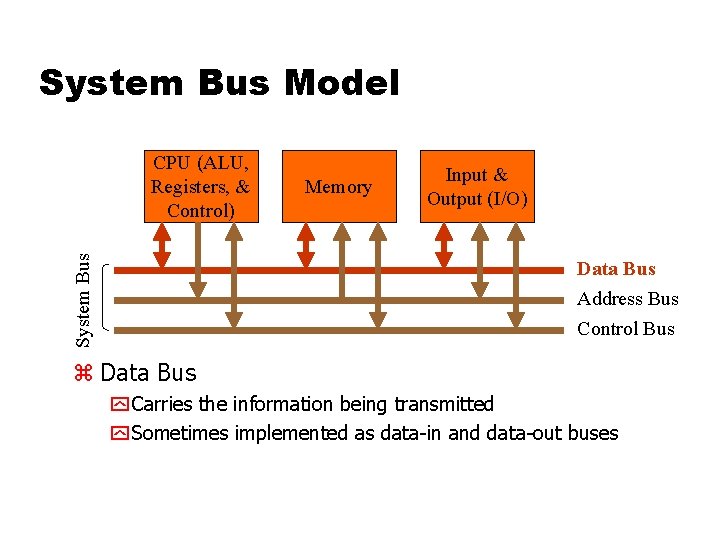

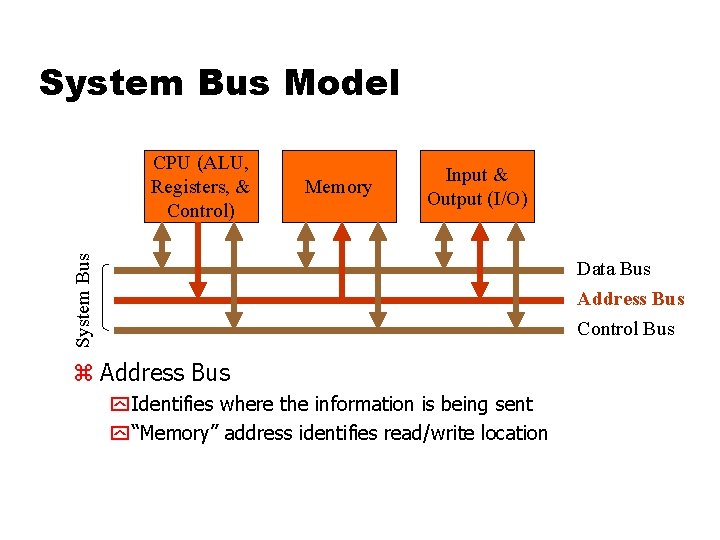

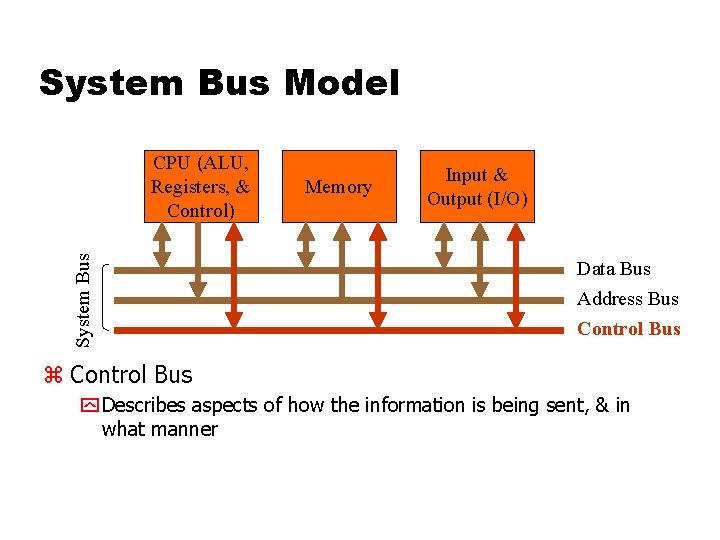

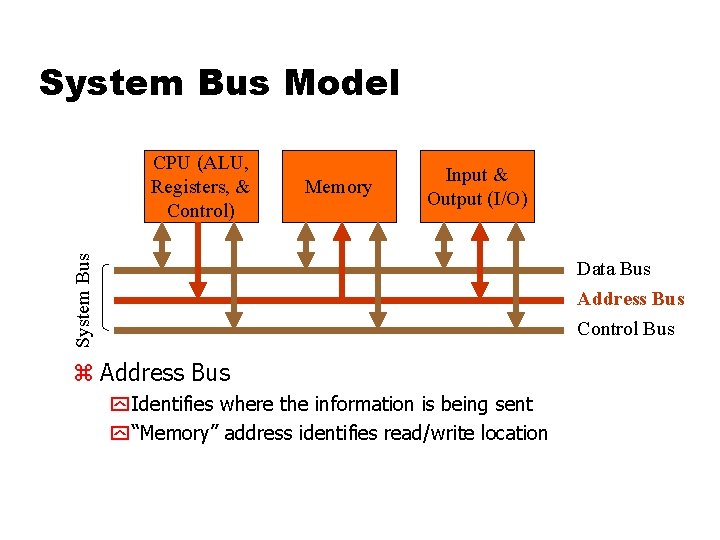

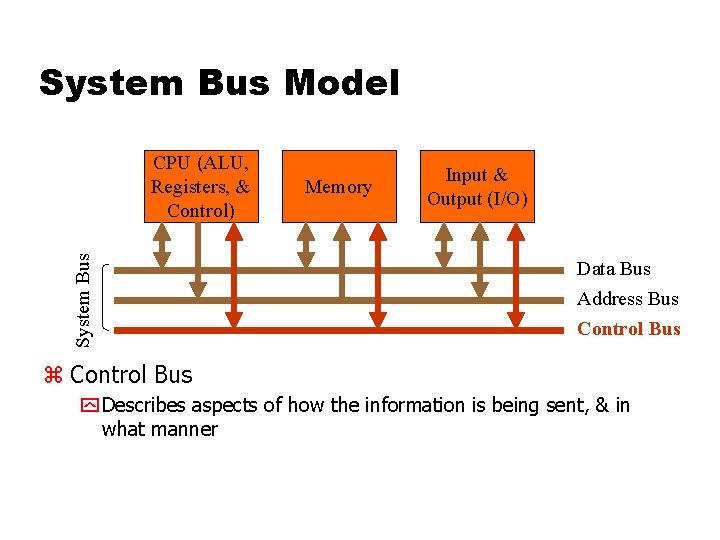

System Bus Model Memory Input & Output (I/O) System Bus CPU (ALU, Registers, & Control) Data Bus Address Bus Control Bus z Streamlined version of von Nuemann model y Data Bus y Address Bus y Control Bus y Power Bus (optional)

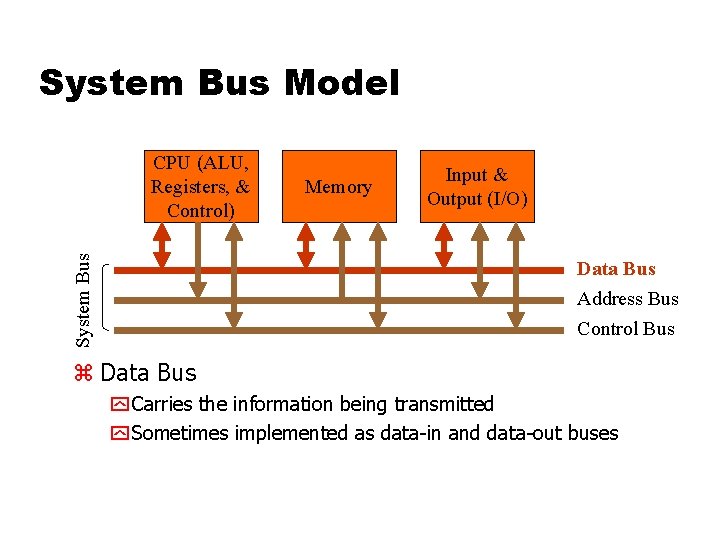

System Bus Model System Bus CPU (ALU, Registers, & Control) Memory Input & Output (I/O) Data Bus Address Bus Control Bus z Data Bus y Carries the information being transmitted y Sometimes implemented as data-in and data-out buses

System Bus Model Memory Input & Output (I/O) System Bus CPU (ALU, Registers, & Control) Data Bus Address Bus Control Bus z Address Bus y Identifies where the information is being sent y “Memory” address identifies read/write location

System Bus Model System Bus CPU (ALU, Registers, & Control) Memory Input & Output (I/O) Data Bus Address Bus Control Bus z Control Bus y Describes aspects of how the information is being sent, & in what manner