COMPUTER ORGANIZATION AND DESIGN The HardwareSoftware Interface Chapter

![Memory Operand Example n Compiling Using Load and Store: A[12] = h + A[8]; Memory Operand Example n Compiling Using Load and Store: A[12] = h + A[8];](https://slidetodoc.com/presentation_image_h/341369de0956c11abc804435a5788ebe/image-7.jpg)

![Example n Translating LEGv 8 Assembly Language into Machine Language A[30] = h + Example n Translating LEGv 8 Assembly Language into Machine Language A[30] = h +](https://slidetodoc.com/presentation_image_h/341369de0956c11abc804435a5788ebe/image-21.jpg)

- Slides: 24

COMPUTER ORGANIZATION AND DESIGN The Hardware/Software Interface Chapter 2 Instructions: Language of the Computer

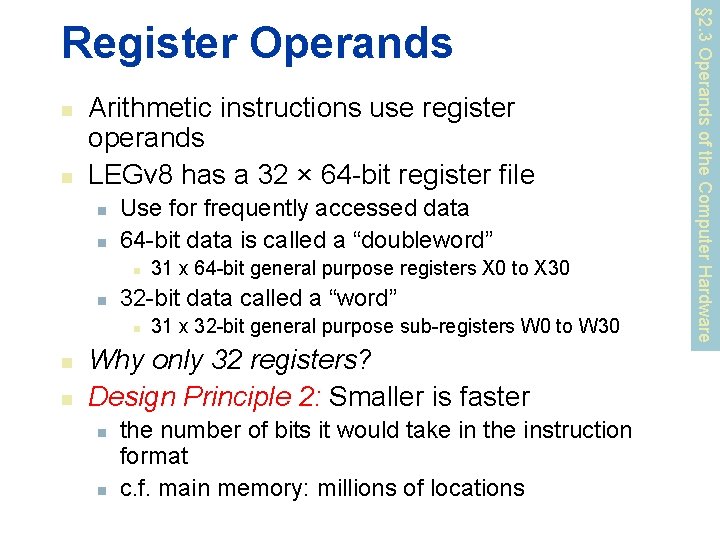

n n Arithmetic instructions use register operands LEGv 8 has a 32 × 64 -bit register file n n Use for frequently accessed data 64 -bit data is called a “doubleword” n n 32 -bit data called a “word” n n n 31 x 64 -bit general purpose registers X 0 to X 30 31 x 32 -bit general purpose sub-registers W 0 to W 30 Why only 32 registers? Design Principle 2: Smaller is faster n n the number of bits it would take in the instruction format c. f. main memory: millions of locations § 2. 3 Operands of the Computer Hardware Register Operands

LEGv 8 Registers n n n n n X 0 – X 7: procedure arguments/results X 8: indirect result location register X 9 – X 15: temporaries X 16 – X 17 (IP 0 – IP 1): may be used by linker as a scratch register, other times as temporary register X 18: platform register for platform independent code; otherwise a temporary register X 19 – X 27: saved X 28 (SP): stack pointer X 29 (FP): frame pointer X 30 (LR): link register (return address) XZR (register 31): the constant value 0

Register Operand Example n Compiling a C Assignment Using Registers: f = (g + h) - (i + j); n f, g, h, i, j in X 19, X 20, X 21, X 22, X 23 n Compiled LEGv 8 code: ADD X 9, X 20, X 21 // register X 9 contains g + h ADD X 10, X 22, X 23 // register X 10 contains i + j SUB X 19, X 10 // f gets X 9−X 10, which is (g + h)−(i + j)

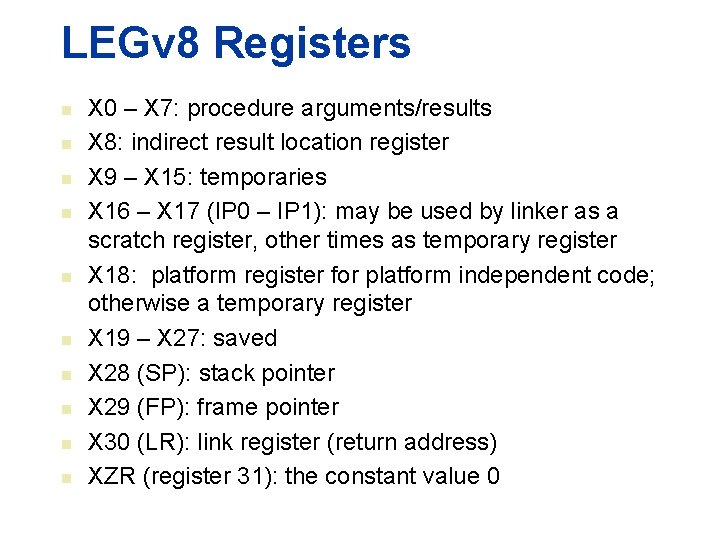

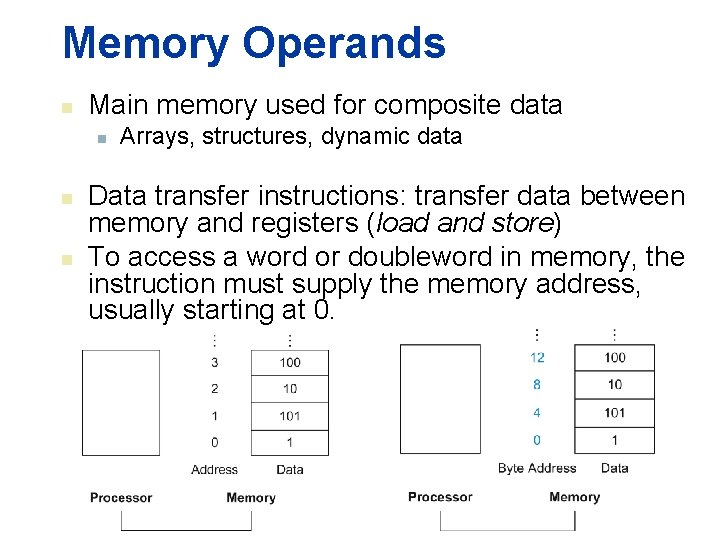

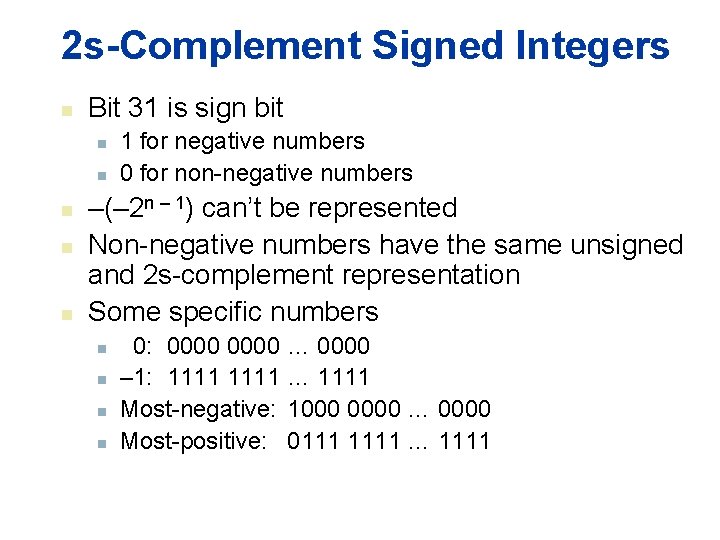

Memory Operands n Main memory used for composite data n n n Arrays, structures, dynamic data Data transfer instructions: transfer data between memory and registers (load and store) To access a word or doubleword in memory, the instruction must supply the memory address, usually starting at 0.

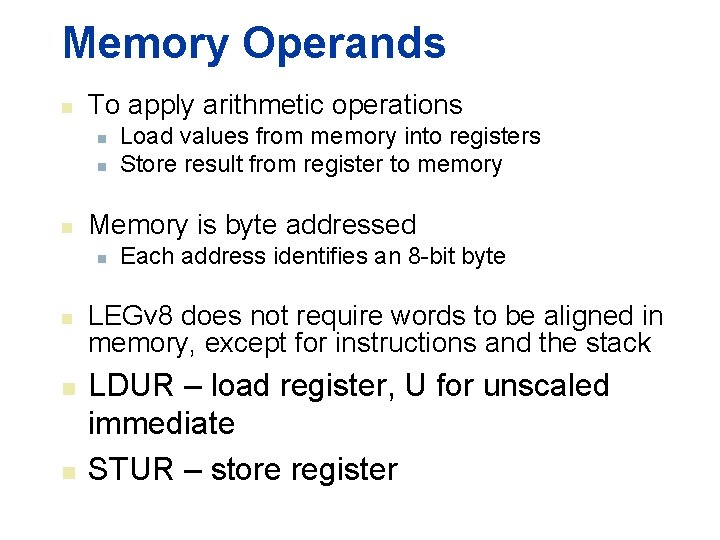

Memory Operands n To apply arithmetic operations n n n Memory is byte addressed n n Load values from memory into registers Store result from register to memory Each address identifies an 8 -bit byte LEGv 8 does not require words to be aligned in memory, except for instructions and the stack LDUR – load register, U for unscaled immediate STUR – store register

![Memory Operand Example n Compiling Using Load and Store A12 h A8 Memory Operand Example n Compiling Using Load and Store: A[12] = h + A[8];](https://slidetodoc.com/presentation_image_h/341369de0956c11abc804435a5788ebe/image-7.jpg)

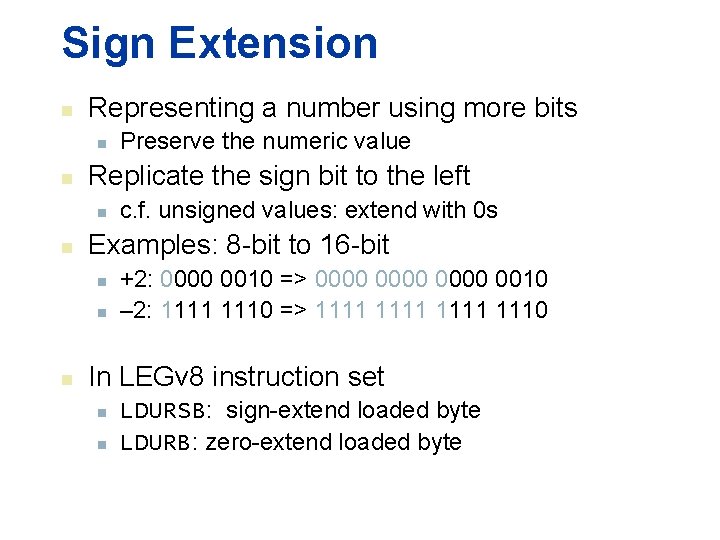

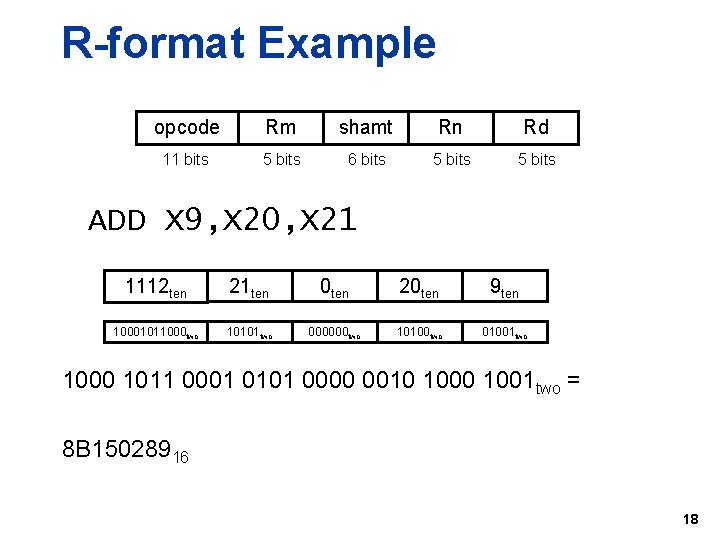

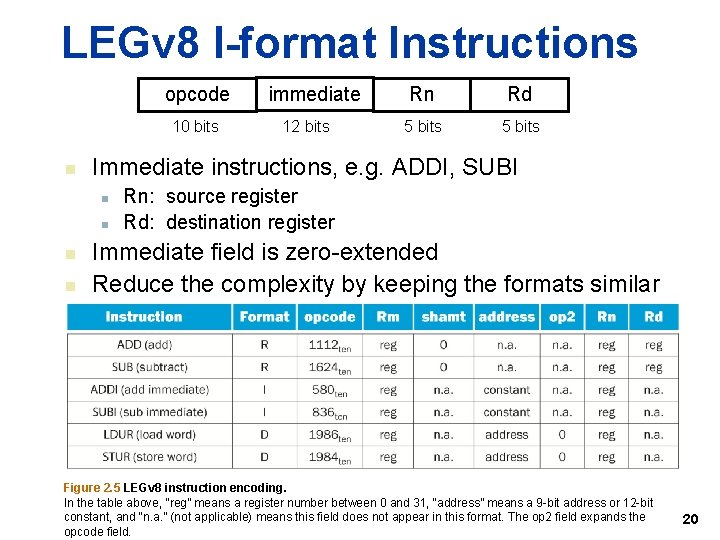

Memory Operand Example n Compiling Using Load and Store: A[12] = h + A[8]; n h in X 21, base address of A in X 22 n Compiled LEGv 8 code: n n Index 8 requires offset of 64 (8 x 8) Index 12 requires offset of 96 (8 x 12) LDUR ADD STUR X 9, [X 22, #64] // Temporary reg X 9 gets X 9, X 21, X 9 // Temporary reg X 9 gets h + X 9, [X 22, #96] //Stores h + A[8] back into A[8] A[12]

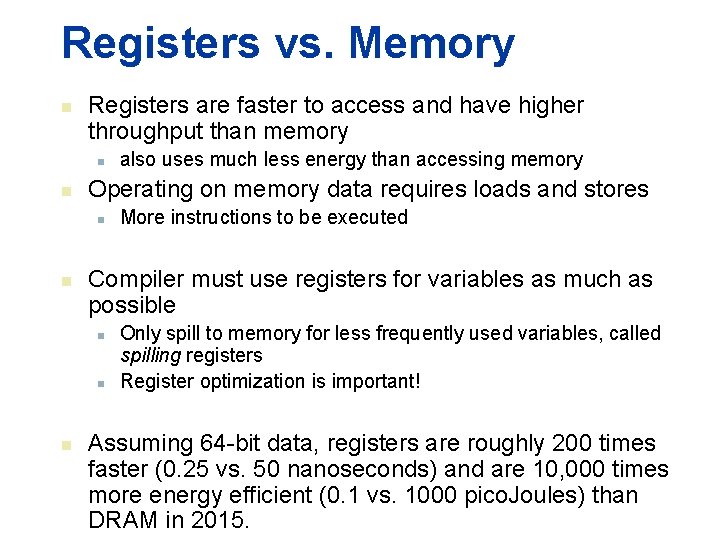

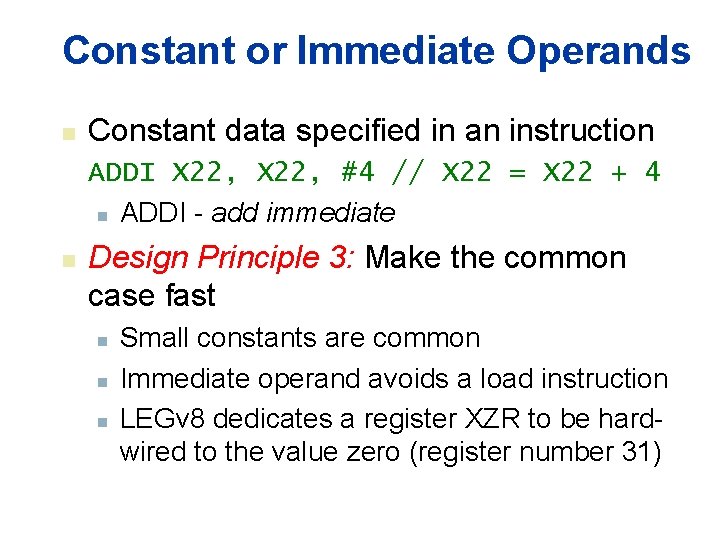

Registers vs. Memory n Registers are faster to access and have higher throughput than memory n n Operating on memory data requires loads and stores n n More instructions to be executed Compiler must use registers for variables as much as possible n n n also uses much less energy than accessing memory Only spill to memory for less frequently used variables, called spilling registers Register optimization is important! Assuming 64 -bit data, registers are roughly 200 times faster (0. 25 vs. 50 nanoseconds) and are 10, 000 times more energy efficient (0. 1 vs. 1000 pico. Joules) than DRAM in 2015.

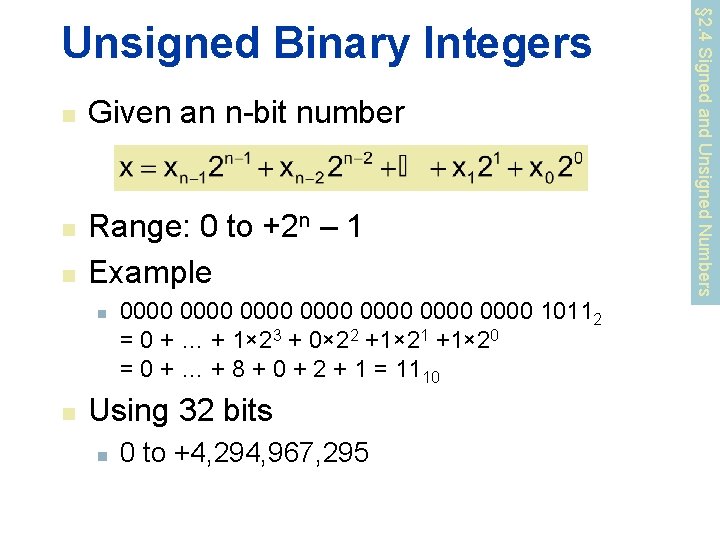

Constant or Immediate Operands n Constant data specified in an instruction ADDI X 22, #4 // X 22 = X 22 + 4 n ADDI - add immediate n Design Principle 3: Make the common case fast n n n Small constants are common Immediate operand avoids a load instruction LEGv 8 dedicates a register XZR to be hardwired to the value zero (register number 31)

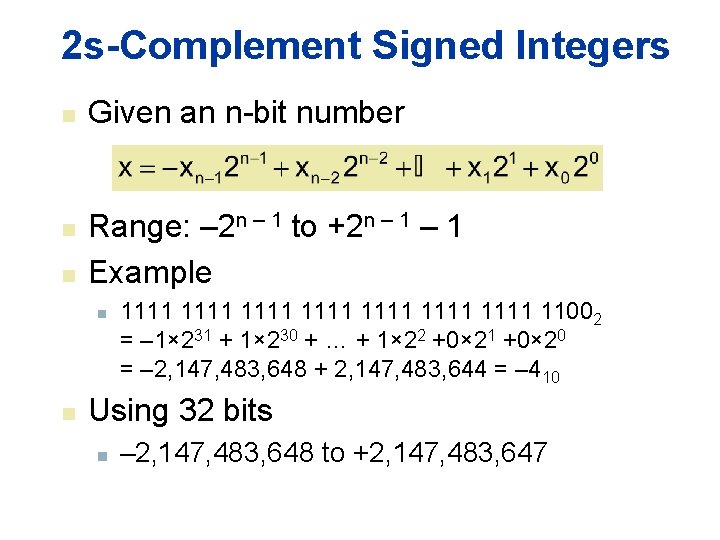

n n n Given an n-bit number Range: 0 to +2 n – 1 Example n n 0000 0000 10112 = 0 + … + 1× 23 + 0× 22 +1× 21 +1× 20 = 0 + … + 8 + 0 + 2 + 1 = 1110 Using 32 bits n 0 to +4, 294, 967, 295 § 2. 4 Signed and Unsigned Numbers Unsigned Binary Integers

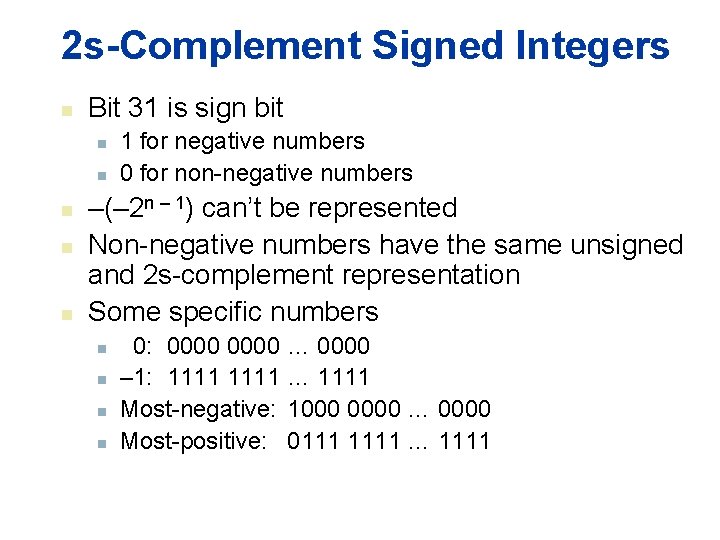

2 s-Complement Signed Integers n n n Given an n-bit number Range: – 2 n – 1 to +2 n – 1 Example n n 1111 1111 11002 = – 1× 231 + 1× 230 + … + 1× 22 +0× 21 +0× 20 = – 2, 147, 483, 648 + 2, 147, 483, 644 = – 410 Using 32 bits n – 2, 147, 483, 648 to +2, 147, 483, 647

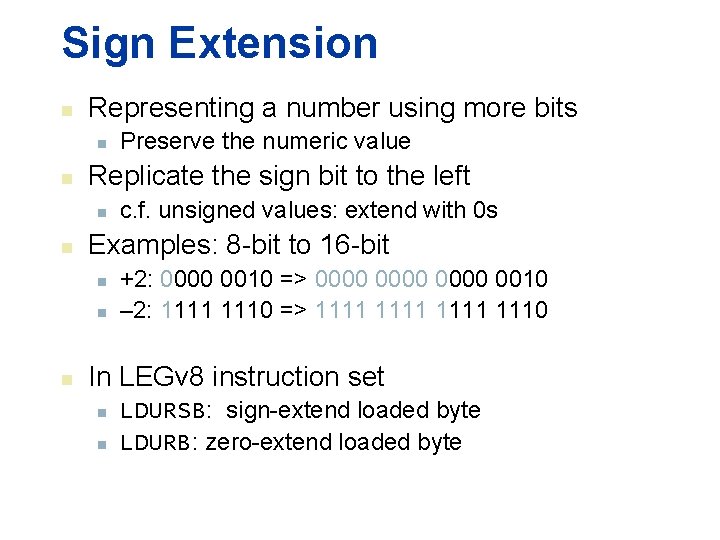

2 s-Complement Signed Integers n Bit 31 is sign bit n n n 1 for negative numbers 0 for non-negative numbers –(– 2 n – 1) can’t be represented Non-negative numbers have the same unsigned and 2 s-complement representation Some specific numbers n n 0: 0000 … 0000 – 1: 1111 … 1111 Most-negative: 1000 0000 … 0000 Most-positive: 0111 1111 … 1111

Signed Negation n Complement and add 1 n n Complement means 1 → 0, 0 → 1 Example: negate +2 n n +2 = 0000 … 0010 two – 2 = 1111 … 1101 two + 1 = 1111 … 1110 two

Sign Extension n Representing a number using more bits n n Replicate the sign bit to the left n n c. f. unsigned values: extend with 0 s Examples: 8 -bit to 16 -bit n n n Preserve the numeric value +2: 0000 0010 => 0000 0010 – 2: 1111 1110 => 1111 1110 In LEGv 8 instruction set n n LDURSB: sign-extend loaded byte LDURB: zero-extend loaded byte

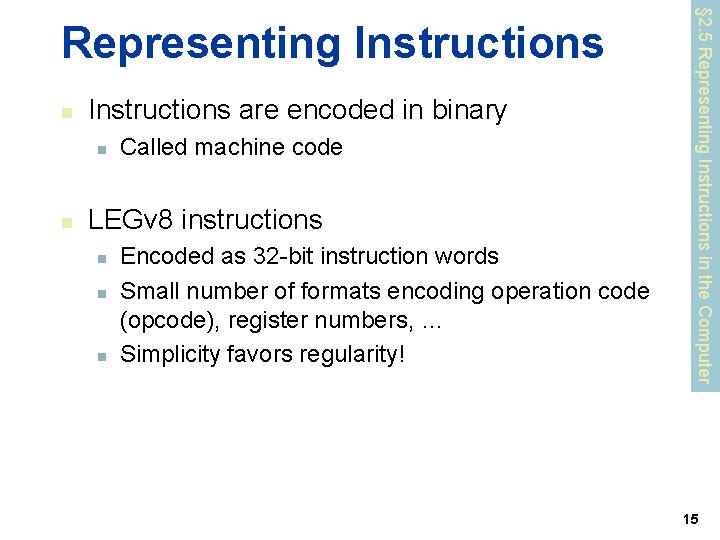

n Instructions are encoded in binary n n Called machine code LEGv 8 instructions n n n Encoded as 32 -bit instruction words Small number of formats encoding operation code (opcode), register numbers, … Simplicity favors regularity! § 2. 5 Representing Instructions in the Computer Representing Instructions 15

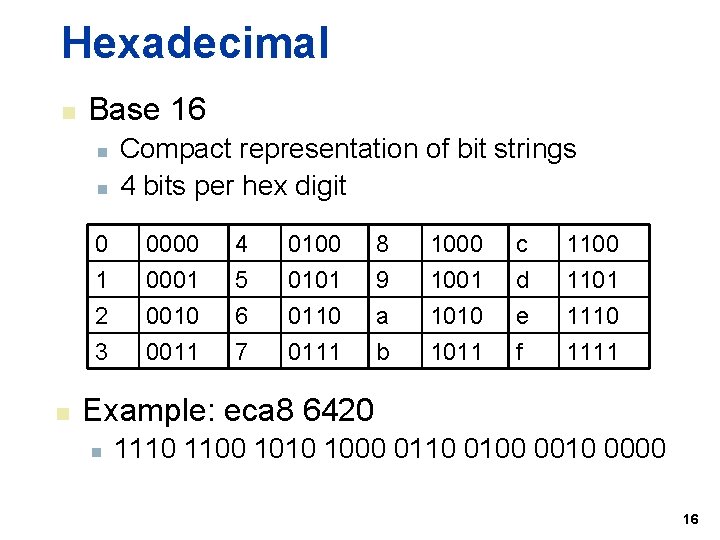

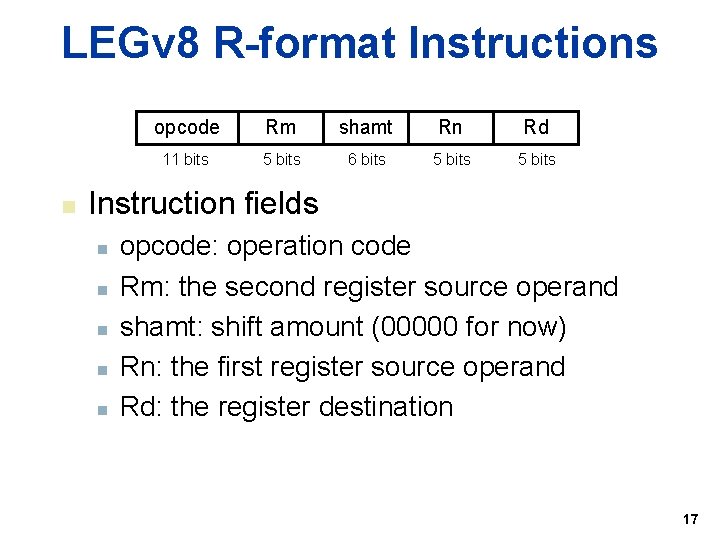

Hexadecimal n Base 16 n n 0 1 2 3 n Compact representation of bit strings 4 bits per hex digit 0000 0001 0010 0011 4 5 6 7 0100 0101 0110 0111 8 9 a b 1000 1001 1010 1011 c d e f 1100 1101 1110 1111 Example: eca 8 6420 n 1110 1100 1010 1000 0110 0100 0010 0000 16

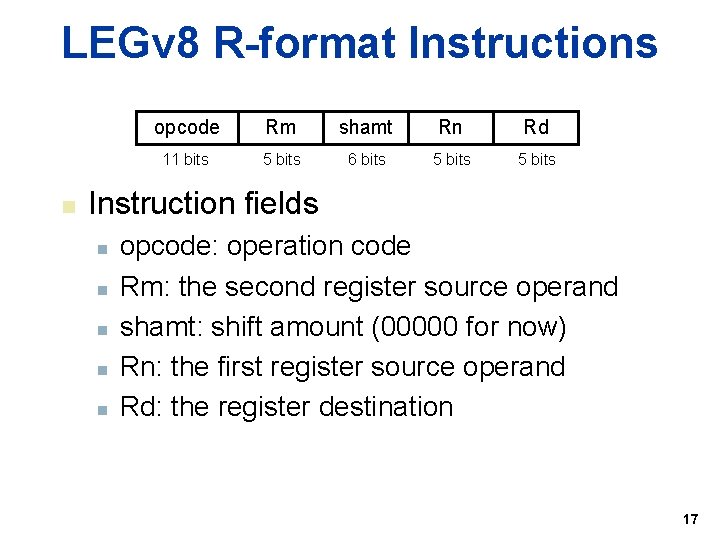

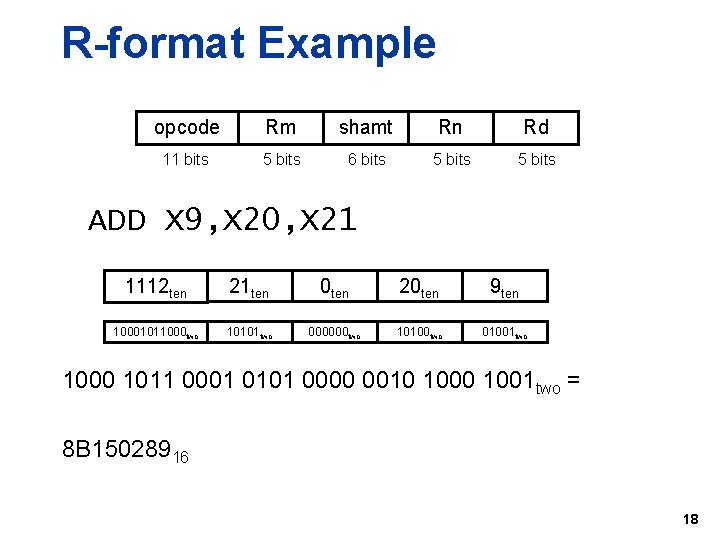

LEGv 8 R-format Instructions n opcode Rm shamt Rn Rd 11 bits 5 bits 6 bits 5 bits Instruction fields n n n opcode: operation code Rm: the second register source operand shamt: shift amount (00000 for now) Rn: the first register source operand Rd: the register destination 17

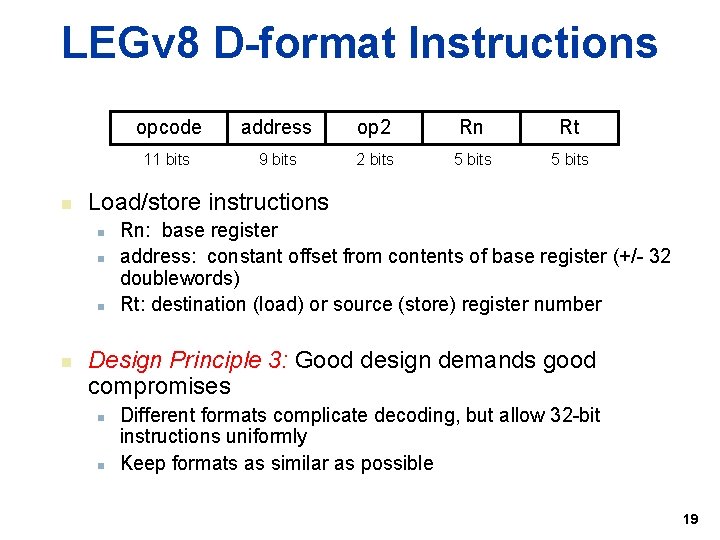

R-format Example opcode Rm shamt Rn Rd 11 bits 5 bits 6 bits 5 bits ADD X 9, X 20, X 21 1112 ten 21 ten 0 ten 20 ten 9 ten 10001011000 two 10101 two 000000 two 10100 two 01001 two 1000 1011 0001 0101 0000 0010 1001 two = 8 B 15028916 18

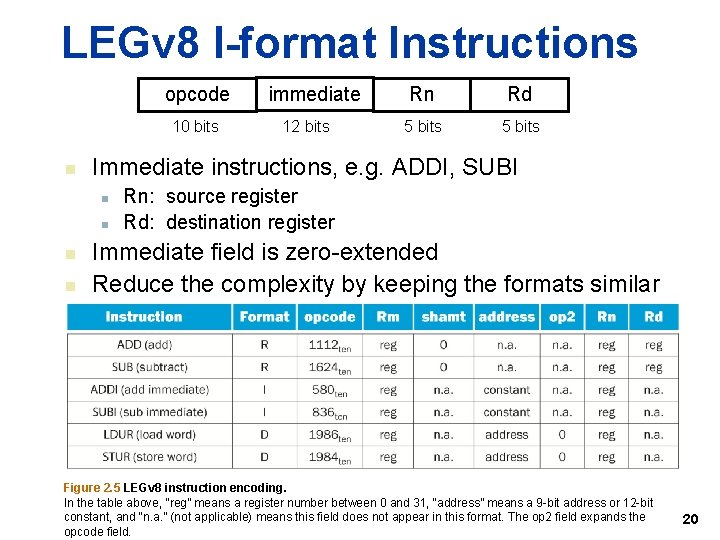

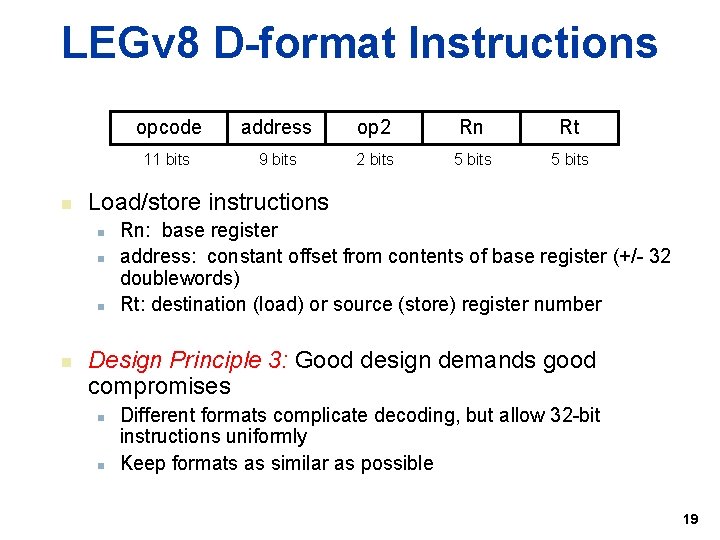

LEGv 8 D-format Instructions n address op 2 Rn Rt 11 bits 9 bits 2 bits 5 bits Load/store instructions n n opcode Rn: base register address: constant offset from contents of base register (+/- 32 doublewords) Rt: destination (load) or source (store) register number Design Principle 3: Good design demands good compromises n n Different formats complicate decoding, but allow 32 -bit instructions uniformly Keep formats as similar as possible 19

LEGv 8 I-format Instructions opcode 10 bits n n n 12 bits Rn Rd 5 bits Immediate instructions, e. g. ADDI, SUBI n n immediate Rn: source register Rd: destination register Immediate field is zero-extended Reduce the complexity by keeping the formats similar Figure 2. 5 LEGv 8 instruction encoding. In the table above, “reg” means a register number between 0 and 31, “address” means a 9 -bit address or 12 -bit constant, and “n. a. ” (not applicable) means this field does not appear in this format. The op 2 field expands the opcode field. 20

![Example n Translating LEGv 8 Assembly Language into Machine Language A30 h Example n Translating LEGv 8 Assembly Language into Machine Language A[30] = h +](https://slidetodoc.com/presentation_image_h/341369de0956c11abc804435a5788ebe/image-21.jpg)

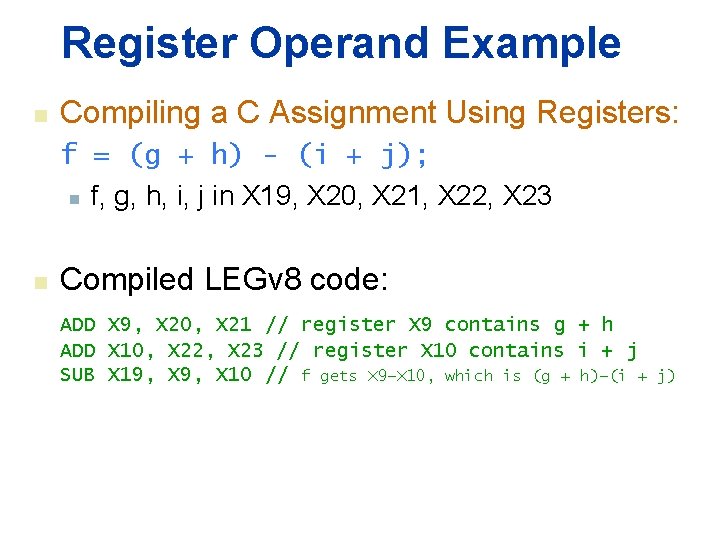

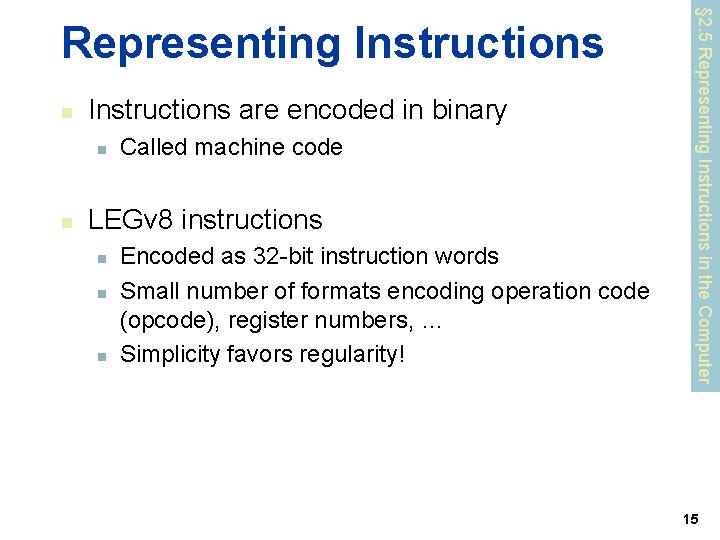

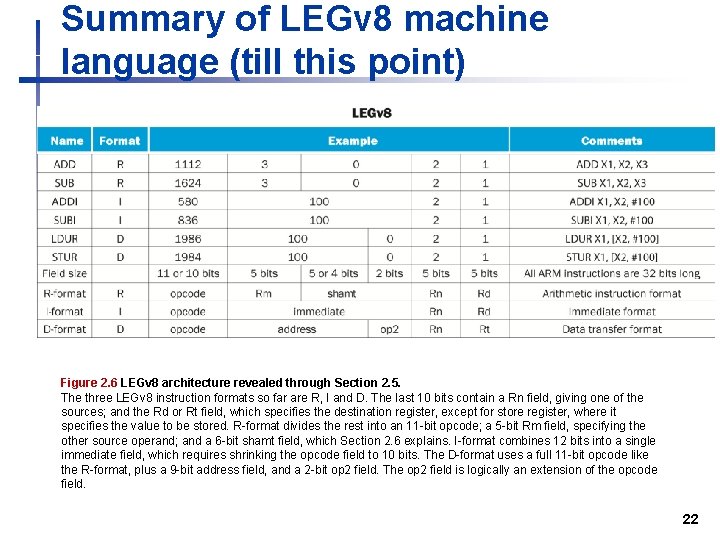

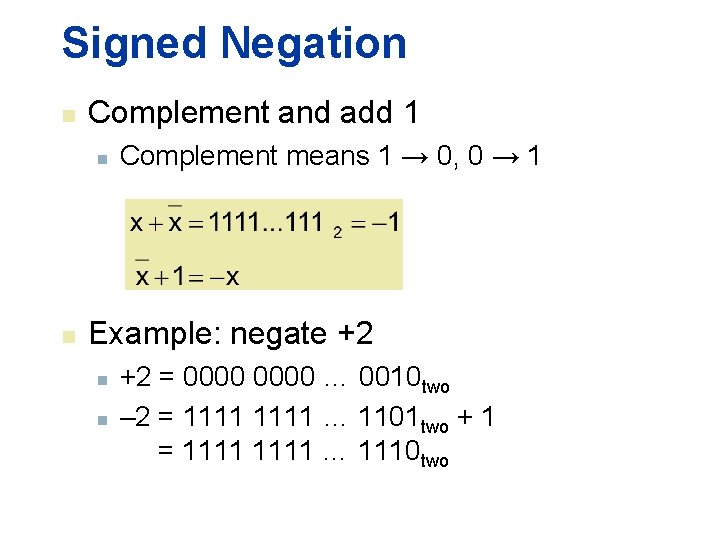

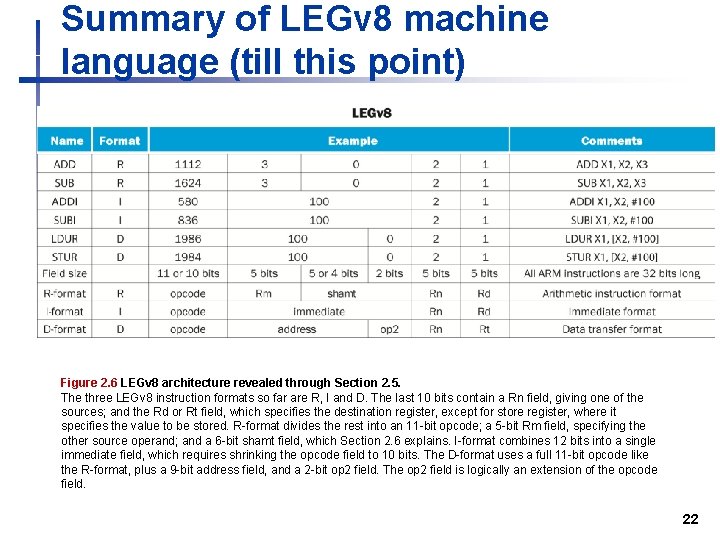

Example n Translating LEGv 8 Assembly Language into Machine Language A[30] = h + A[30] + 1; n n X 10 has the base of the array A and X 21 corresponds to h Compiled LEGv 8 code: n LDUR X 9, [X 10, #240] // Temporary reg X 9 gets A[30] ADD X 9, X 21, X 9 // Temporary reg X 9 gets h+A[30] ADDI X 9, #1 // Temporary reg X 9 gets h+A[30]+1 STUR X 9, [X 10, #240] // Stores h+A[30]+1 back into A[30] n Machine language instructions using decimal numbers: n n n opcode Rm/ address shamt /op 2 Rn Rd/Rt 1986 240 0 10 9 11111000010 01111000 01010 01001 1112 9 0 21 9 10001011000 01001 000000 10101 01001 580 1 9 9 100100 0000001 01001 21

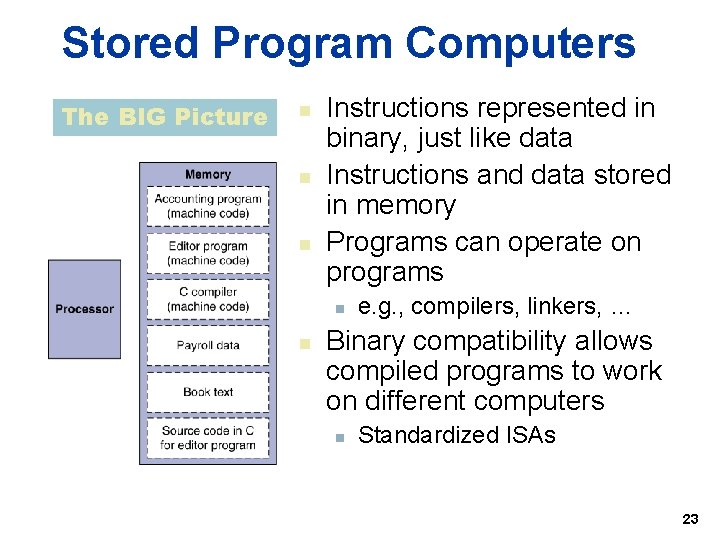

Summary of LEGv 8 machine language (till this point) Figure 2. 6 LEGv 8 architecture revealed through Section 2. 5. The three LEGv 8 instruction formats so far are R, I and D. The last 10 bits contain a Rn field, giving one of the sources; and the Rd or Rt field, which specifies the destination register, except for store register, where it specifies the value to be stored. R-format divides the rest into an 11 -bit opcode; a 5 -bit Rm field, specifying the other source operand; and a 6 -bit shamt field, which Section 2. 6 explains. I-format combines 12 bits into a single immediate field, which requires shrinking the opcode field to 10 bits. The D-format uses a full 11 -bit opcode like the R-format, plus a 9 -bit address field, and a 2 -bit op 2 field. The op 2 field is logically an extension of the opcode field. 22

Stored Program Computers The BIG Picture n n n Instructions represented in binary, just like data Instructions and data stored in memory Programs can operate on programs n n e. g. , compilers, linkers, … Binary compatibility allows compiled programs to work on different computers n Standardized ISAs 23

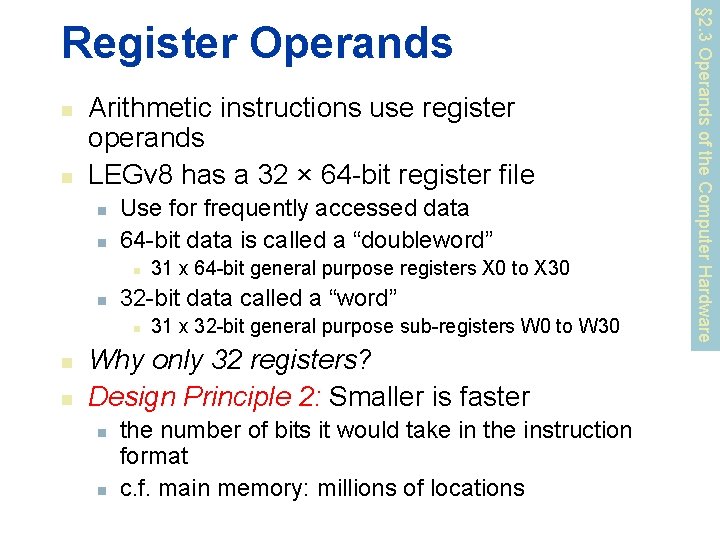

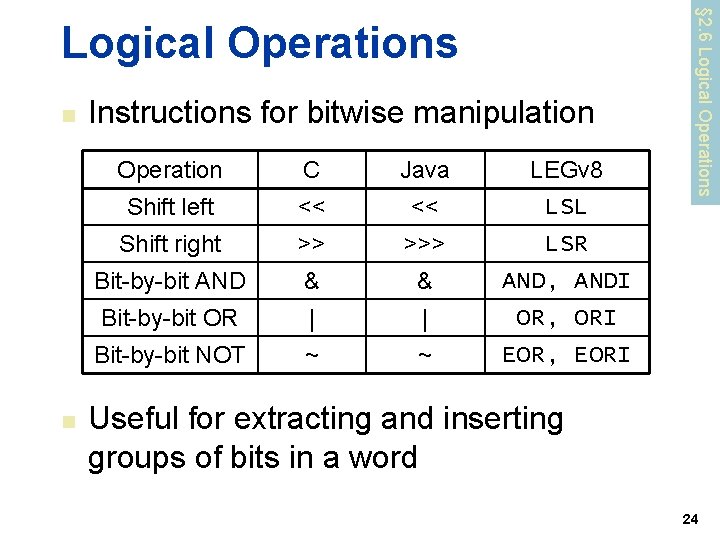

n n Instructions for bitwise manipulation Operation C Java LEGv 8 Shift left << << LSL Shift right >> >>> LSR Bit-by-bit AND & & AND, ANDI Bit-by-bit OR | | OR, ORI Bit-by-bit NOT ~ ~ EOR, EORI § 2. 6 Logical Operations Useful for extracting and inserting groups of bits in a word 24