Computer Organization and Architecture Networks Lecture 6 InputOutput

- Slides: 33

Computer Organization and Architecture + Networks Lecture 6 • Input/Output

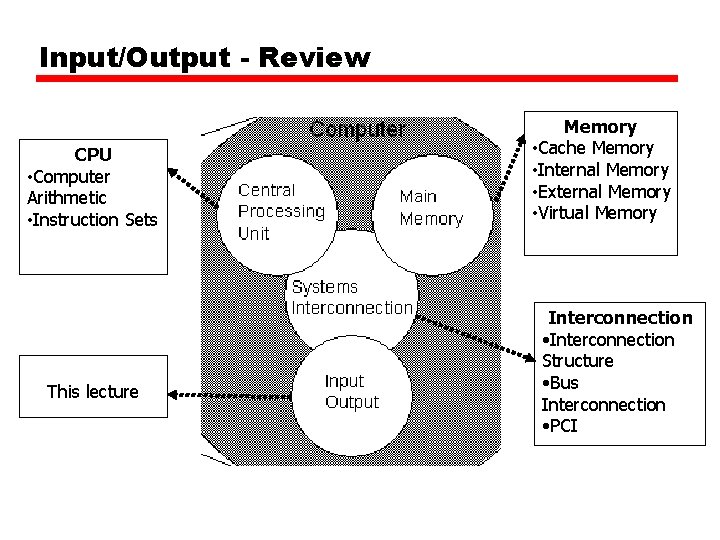

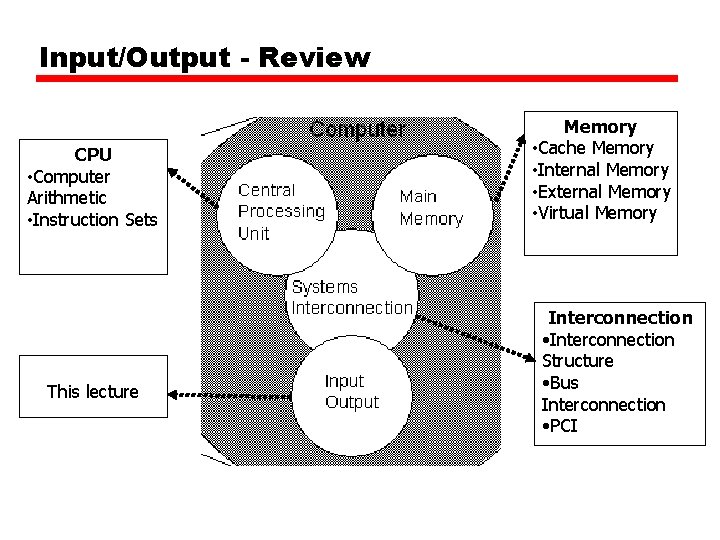

Input/Output - Review CPU • Computer Arithmetic • Instruction Sets This lecture Memory • Cache Memory • Internal Memory • External Memory • Virtual Memory Interconnection • Interconnection Structure • Bus Interconnection • PCI

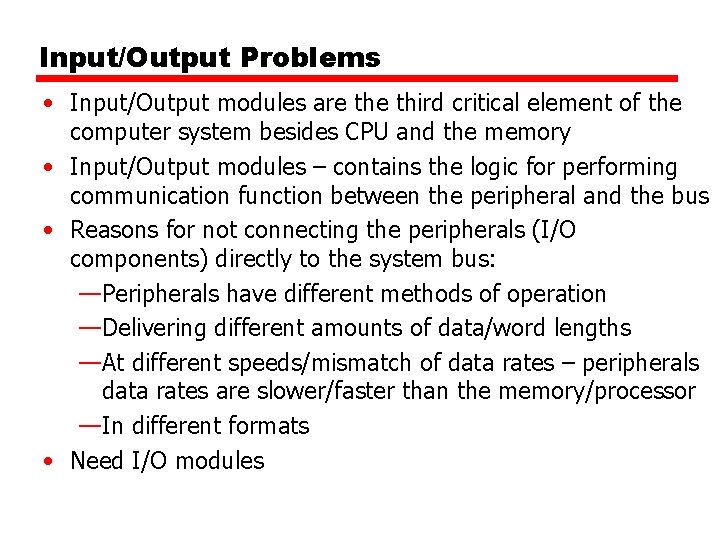

Input/Output Problems • Input/Output modules are third critical element of the computer system besides CPU and the memory • Input/Output modules – contains the logic for performing communication function between the peripheral and the bus • Reasons for not connecting the peripherals (I/O components) directly to the system bus: —Peripherals have different methods of operation —Delivering different amounts of data/word lengths —At different speeds/mismatch of data rates – peripherals data rates are slower/faster than the memory/processor —In different formats • Need I/O modules

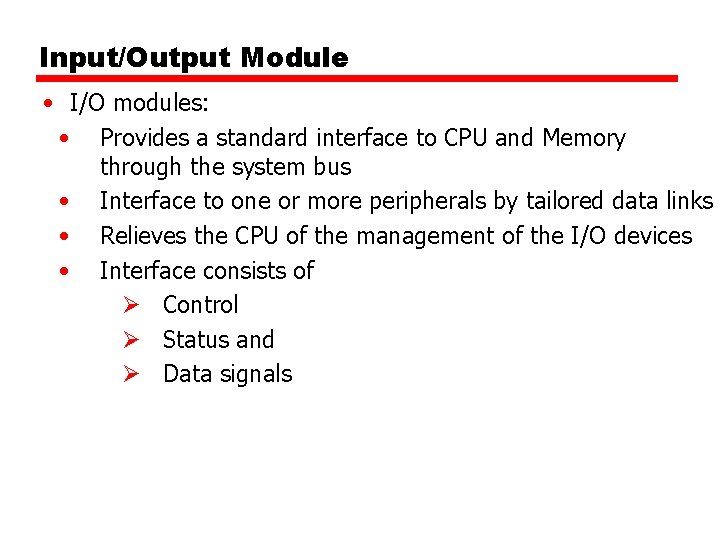

Input/Output Module • I/O modules: • Provides a standard interface to CPU and Memory through the system bus • Interface to one or more peripherals by tailored data links • Relieves the CPU of the management of the I/O devices • Interface consists of Ø Control Ø Status and Ø Data signals

Generic Model of I/O Module To peripheral device I/O Module External device block diagram

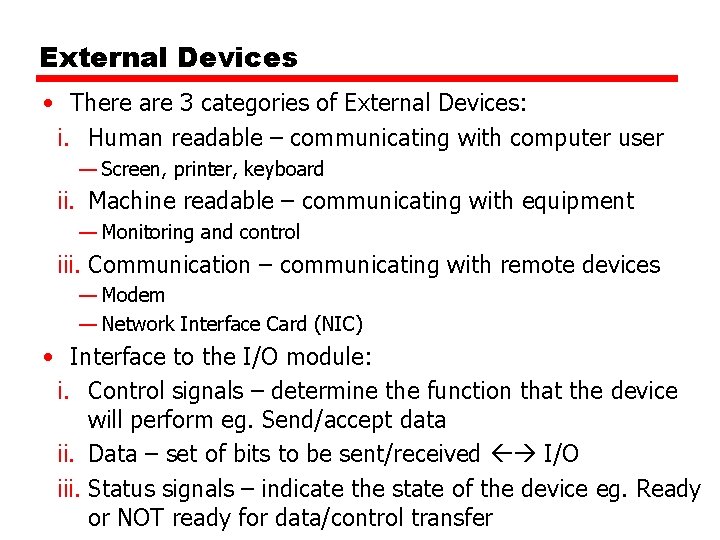

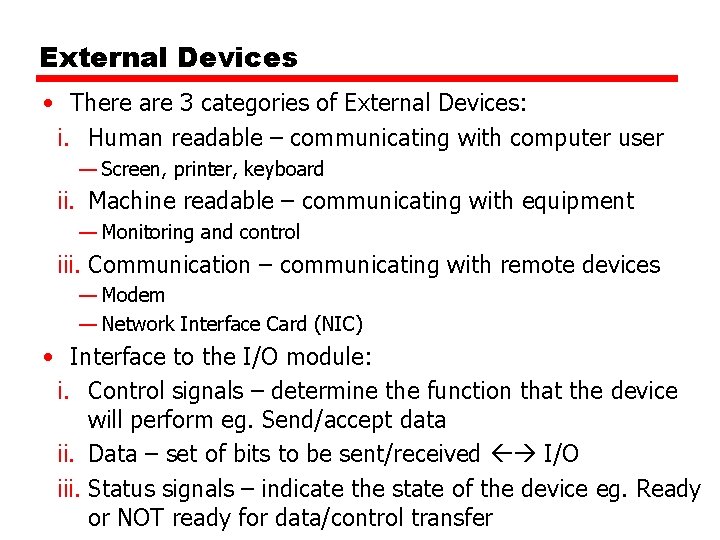

External Devices • There are 3 categories of External Devices: i. Human readable – communicating with computer user — Screen, printer, keyboard ii. Machine readable – communicating with equipment — Monitoring and control iii. Communication – communicating with remote devices — Modem — Network Interface Card (NIC) • Interface to the I/O module: i. Control signals – determine the function that the device will perform eg. Send/accept data ii. Data – set of bits to be sent/received I/O iii. Status signals – indicate the state of the device eg. Ready or NOT ready for data/control transfer

External Devices • Other components of the I/O module: i. Control logic – control the device’s operation ii. Transducer – converts electrical other forms iii. Buffer – to temporarily hold data

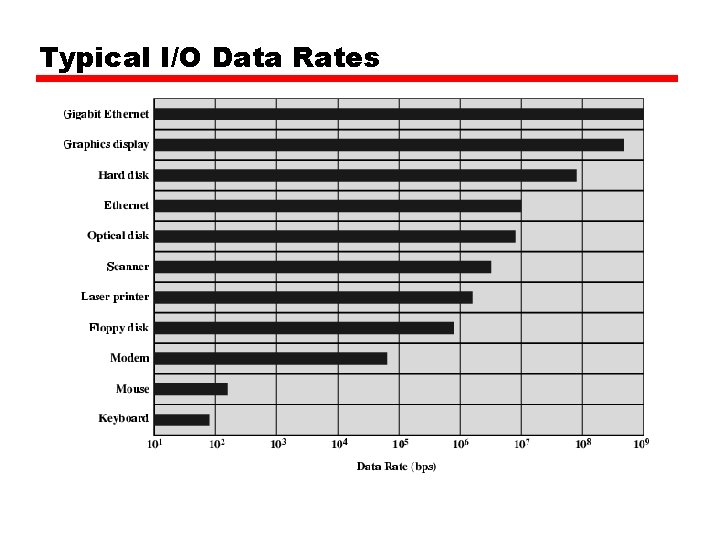

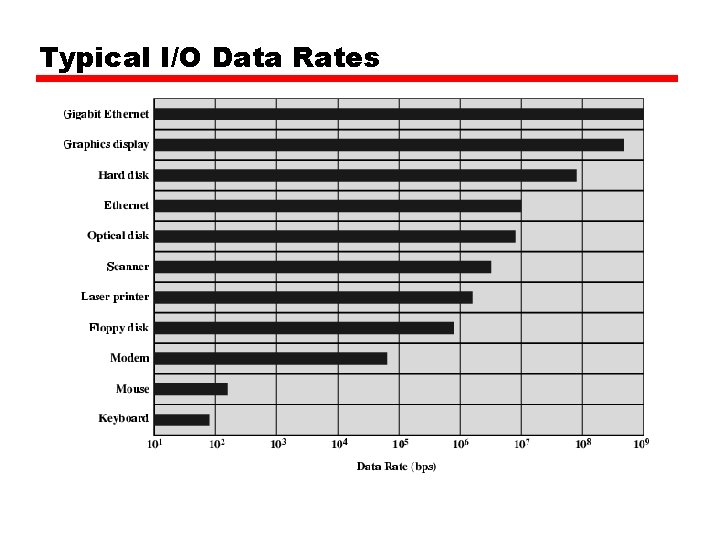

Typical I/O Data Rates

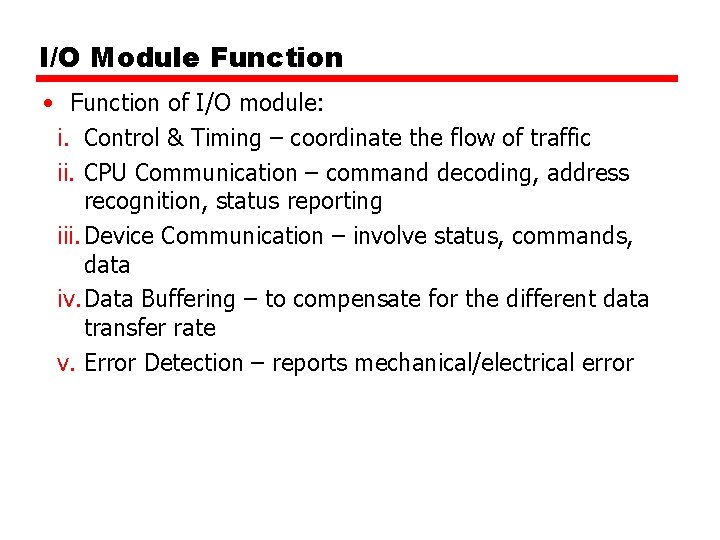

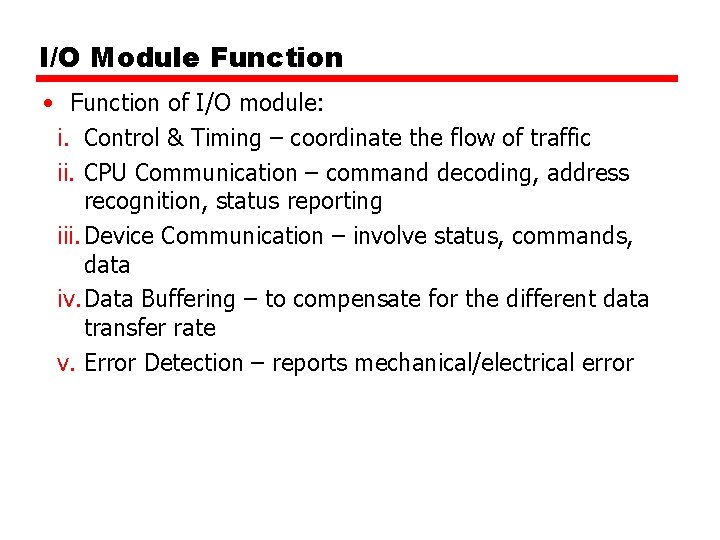

I/O Module Function • Function of I/O module: i. Control & Timing – coordinate the flow of traffic ii. CPU Communication – command decoding, address recognition, status reporting iii. Device Communication – involve status, commands, data iv. Data Buffering – to compensate for the different data transfer rate v. Error Detection – reports mechanical/electrical error

I/O Steps • I/O sequence of steps in the transfer of data from an external devices to the processor: 1. CPU checks I/O module device status 2. I/O module returns status 3. If ready, CPU requests data transfer 4. I/O module gets data from device 5. I/O module transfers data to CPU 6. Variations for output, DMA, etc.

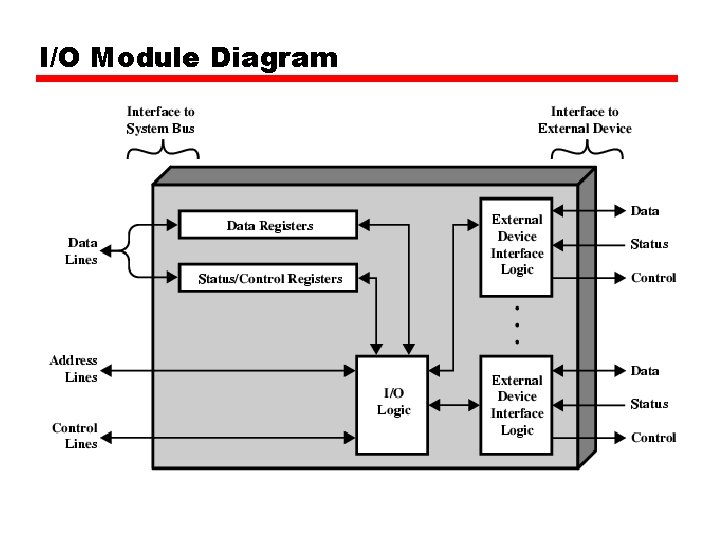

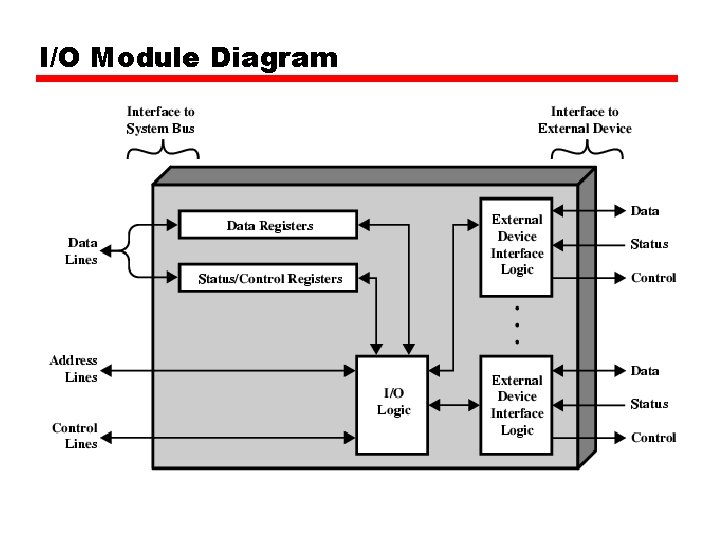

I/O Module Diagram

I/O Module Decisions • Decisions made by the I/O module: ①Hide or reveal device properties to CPU ②Support multiple or single device ③Control device functions or leave for CPU ④Also O/S decisions —e. g. Unix treats everything it can as a file

Input Output Techniques • Three Principal Input Output Techniques: Ø Programmed Ø Interrupt driven Ø Direct Memory Access (DMA)

Programmed I/O • I/O operation in which CPU issues the I/O command to the I/O module • CPU has direct control over I/O operation eg. Sensing status, read/write commands, transferring data — CPU waits until the I/O operation is completed before it can perform other tasks — Completion indicated by a change in the module status bits — CPU must periodically poll the module to check its status • As a result of the speed difference between a CPU and the peripheral devices (orders of magnitude), programmed I/O wastes an enormous amount of CPU processing power — Very inefficient — CPU slowed to the speed of the peripheral

Programmed I/O • Advantages — Simple to implement — Requires very little special software or hardware

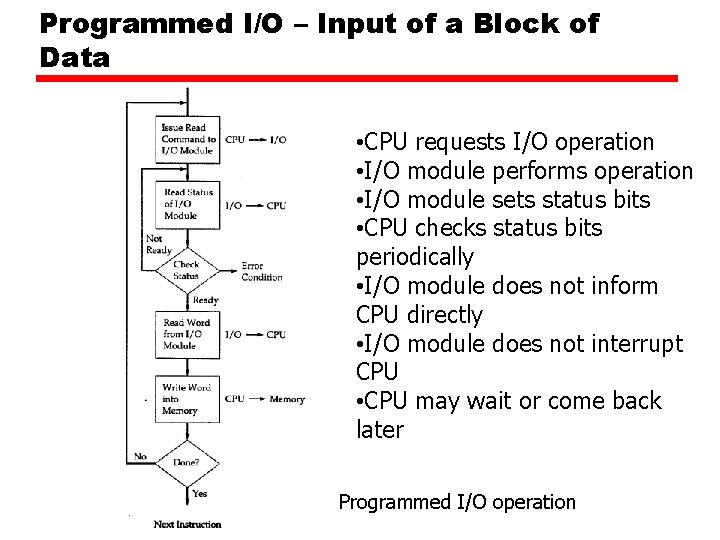

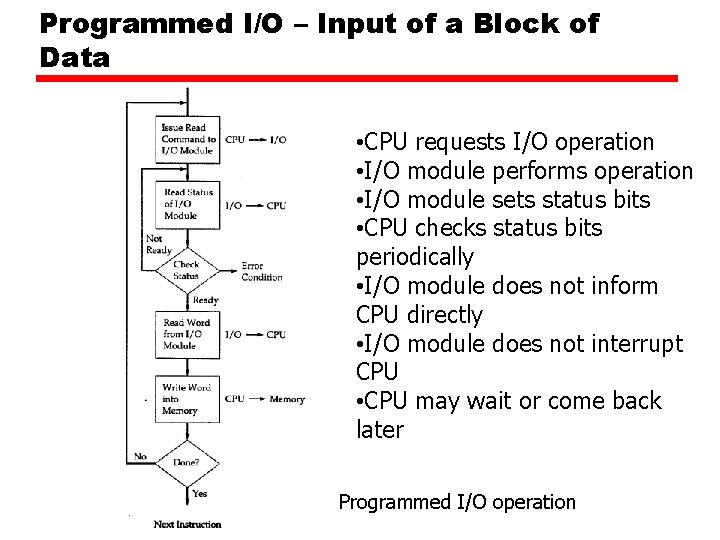

Programmed I/O – Input of a Block of Data • CPU requests I/O operation • I/O module performs operation • I/O module sets status bits • CPU checks status bits periodically • I/O module does not inform CPU directly • I/O module does not interrupt CPU • CPU may wait or come back later Programmed I/O operation

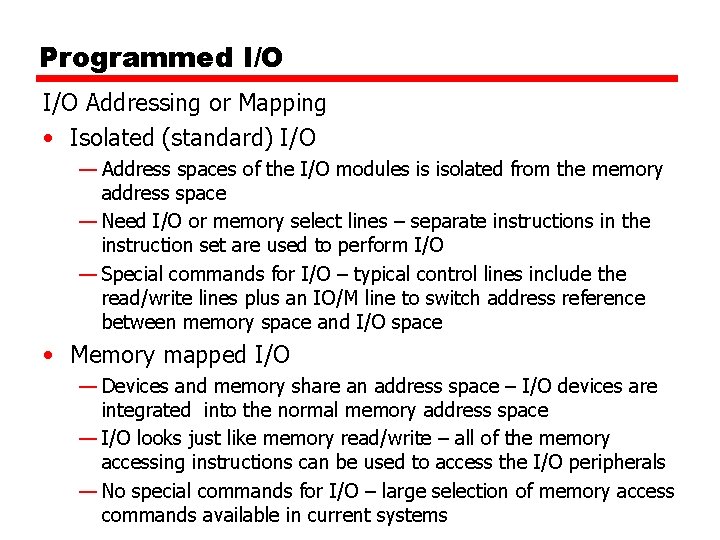

Programmed I/O Addressing or Mapping • Isolated (standard) I/O — Address spaces of the I/O modules is isolated from the memory address space — Need I/O or memory select lines – separate instructions in the instruction set are used to perform I/O — Special commands for I/O – typical control lines include the read/write lines plus an IO/M line to switch address reference between memory space and I/O space • Memory mapped I/O — Devices and memory share an address space – I/O devices are integrated into the normal memory address space — I/O looks just like memory read/write – all of the memory accessing instructions can be used to access the I/O peripherals — No special commands for I/O – large selection of memory access commands available in current systems

Interrupt Driven I/O • To reduce the time spent on I/O operations, the CPU can use an interrupt-driven approach — CPU issues I/O command to the module — CPU continues with its other tasks while the module performs its task — Module signals the CPU when the I/O operation is finished (the interrupt) — CPU responds to the interrupt by executing an interrupt service routine and then continues on with its primary task • CPU recognizes and responds to interrupts at the end of an instruction execution cycle • Interrupt technique is used to support a wide variety of devices

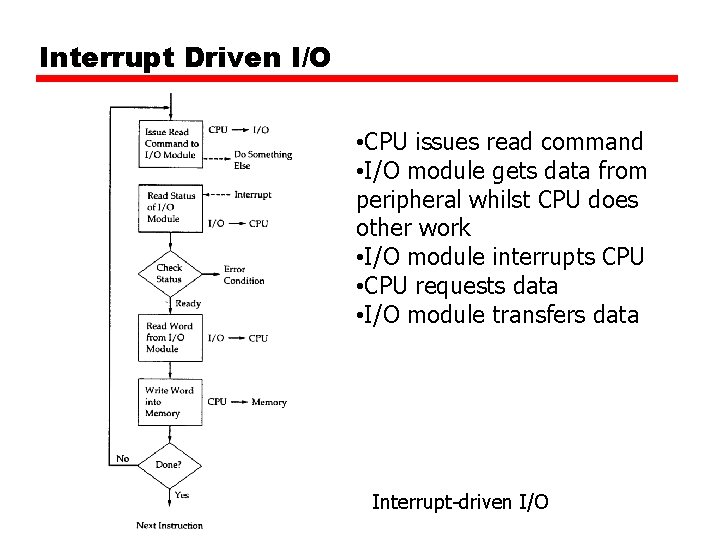

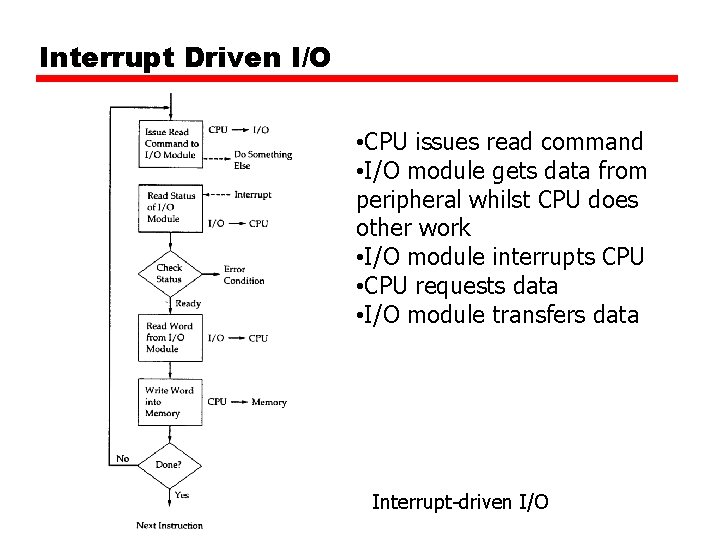

Interrupt Driven I/O • CPU issues read command • I/O module gets data from peripheral whilst CPU does other work • I/O module interrupts CPU • CPU requests data • I/O module transfers data Interrupt-driven I/O

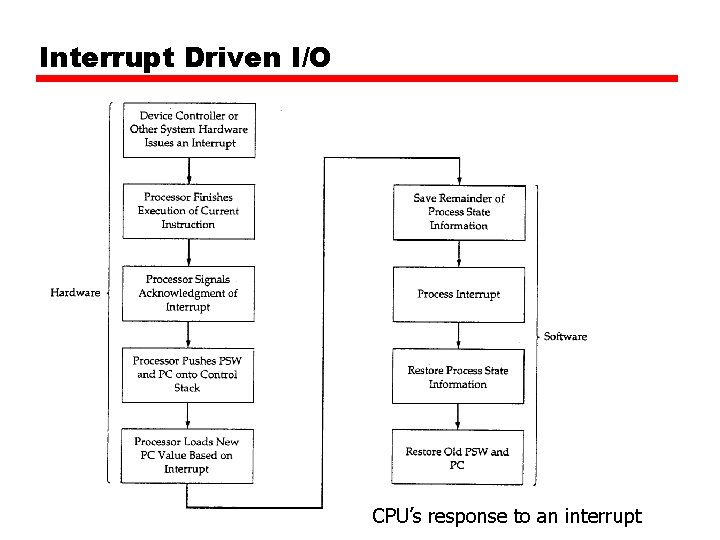

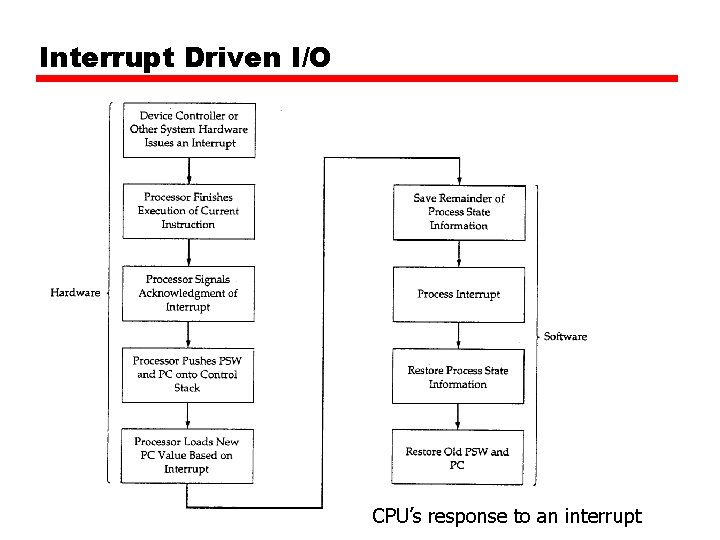

Interrupt Driven I/O CPU’s response to an interrupt

Interrupt Driven I/O • Design issues with multiple modules and thus multiple interrupts — How does the CPU identify the module issuing the interrupt? — How does the CPU deal with multiple interrupts? If multiple interrupts occur at the same time, which is processed first? – i. e. an interrupt handler being interrupted • Interrupt determination — Provide multiple interrupt signal lines for a system – Practically only for small numbers of interrupts — Use 1 interrupt for more than 1 device – Must perform some sort of device polling to determine which requested service – Requesting device can place an ID on the bus vectored interrupts • Determination scheme prioritizes multiple interrupts

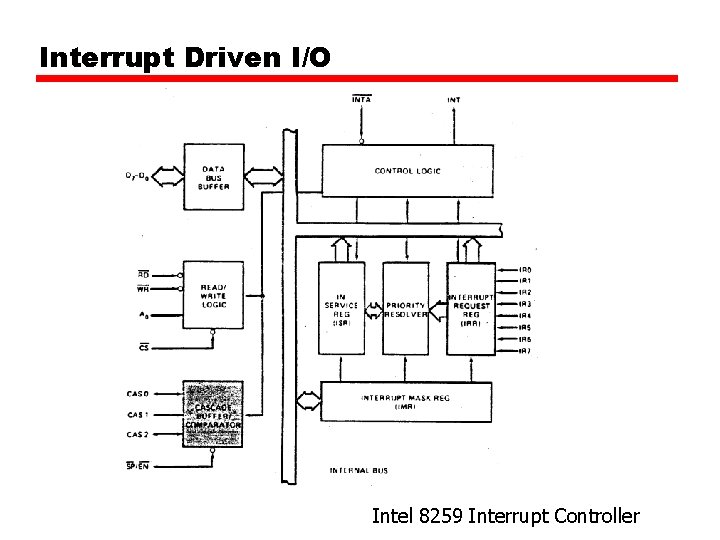

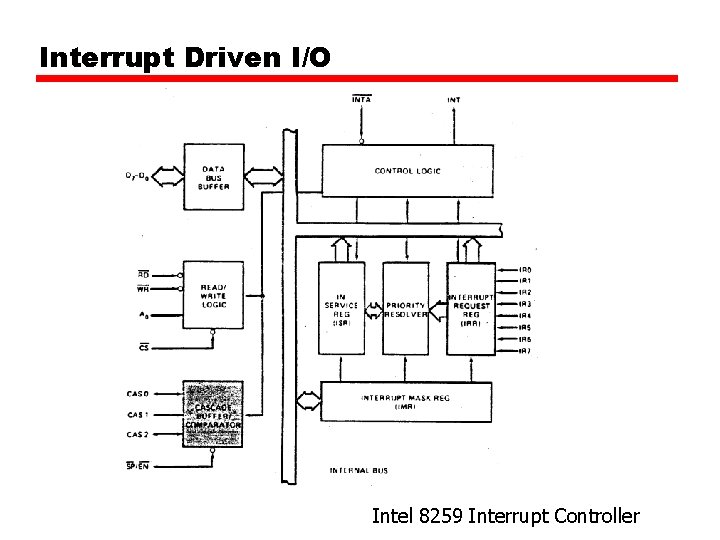

Interrupt Driven I/O Intel 8259 Interrupt Controller

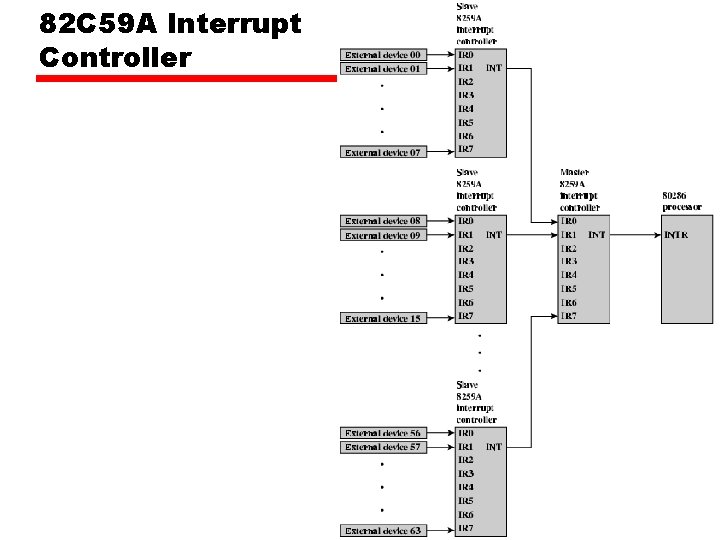

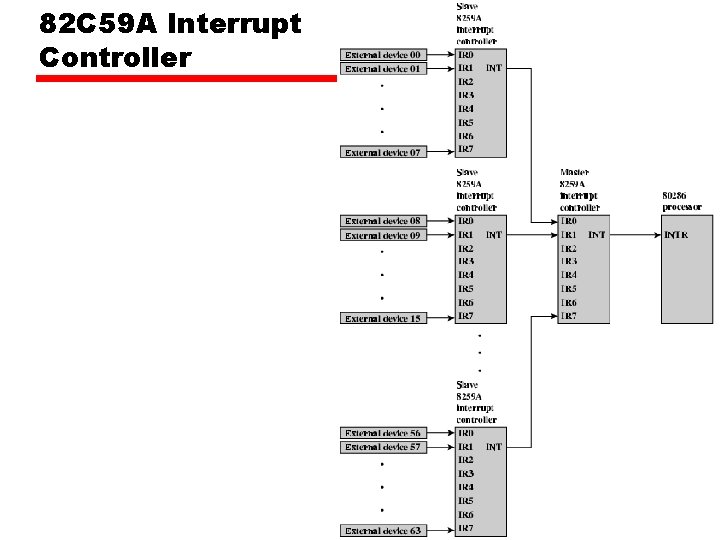

82 C 59 A Interrupt Controller

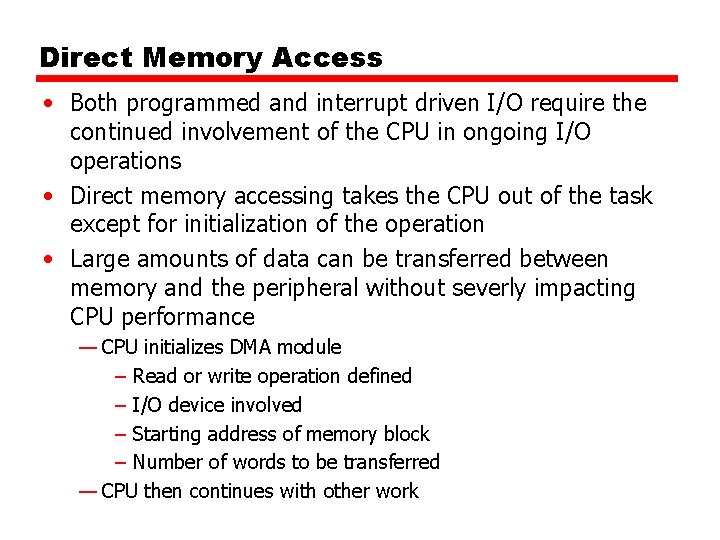

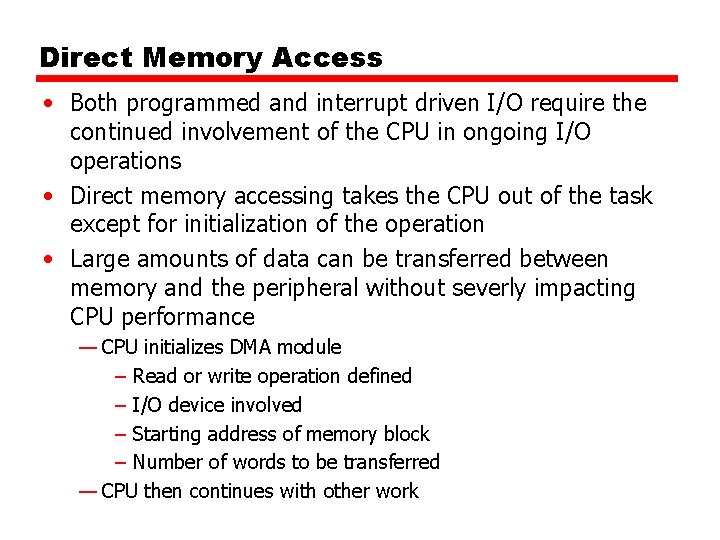

Direct Memory Access • Both programmed and interrupt driven I/O require the continued involvement of the CPU in ongoing I/O operations • Direct memory accessing takes the CPU out of the task except for initialization of the operation • Large amounts of data can be transferred between memory and the peripheral without severly impacting CPU performance — CPU initializes DMA module – Read or write operation defined – I/O device involved – Starting address of memory block – Number of words to be transferred — CPU then continues with other work

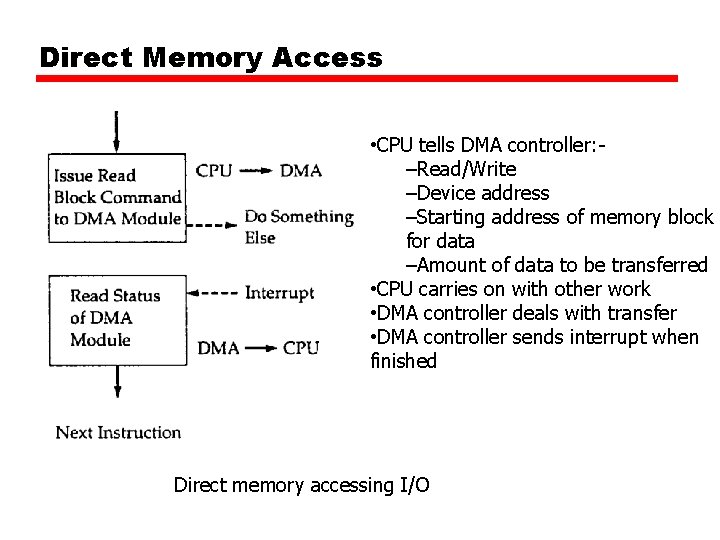

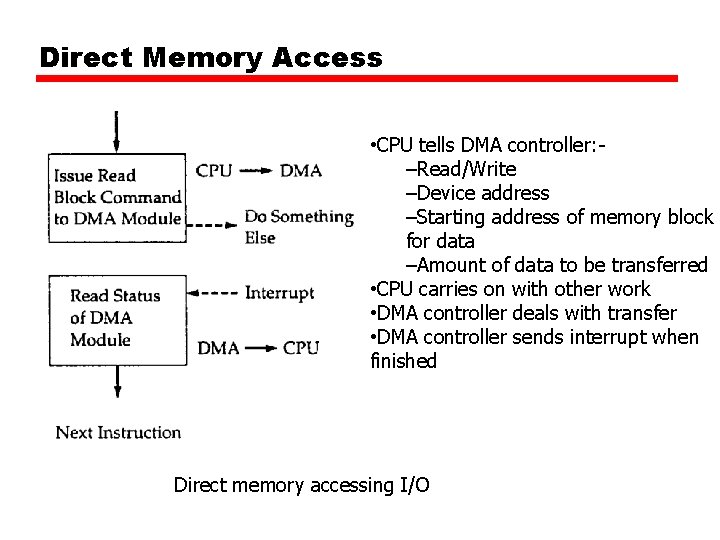

Direct Memory Access • CPU tells DMA controller: –Read/Write –Device address –Starting address of memory block for data –Amount of data to be transferred • CPU carries on with other work • DMA controller deals with transfer • DMA controller sends interrupt when finished Direct memory accessing I/O

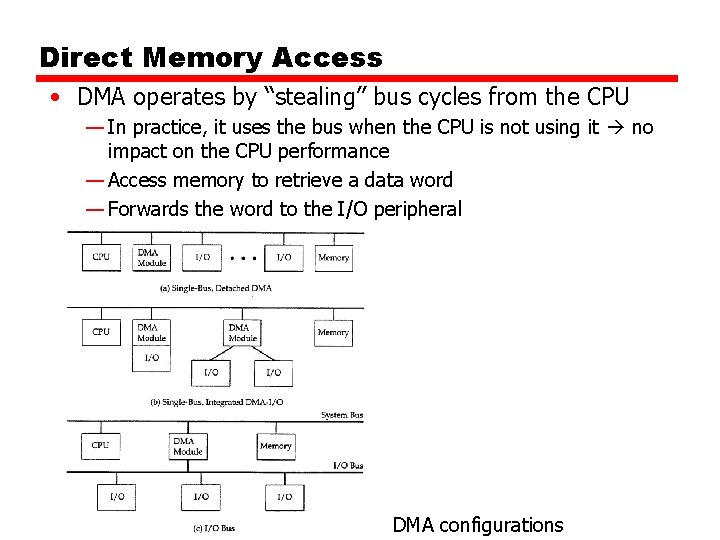

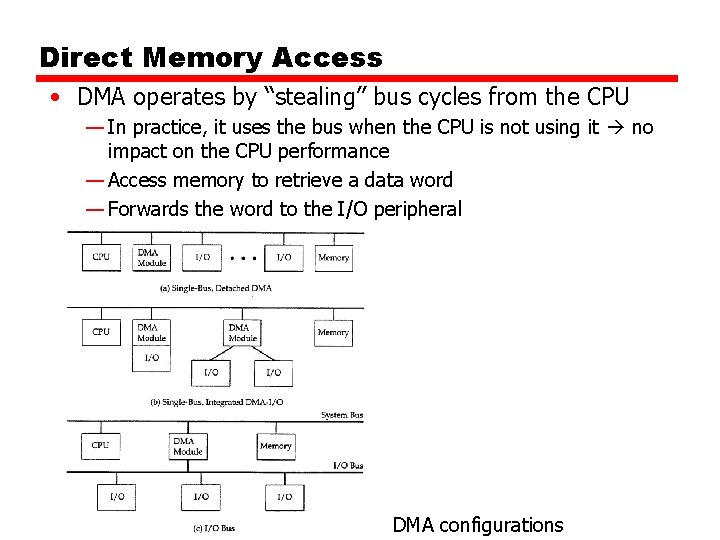

Direct Memory Access • DMA operates by “stealing” bus cycles from the CPU — In practice, it uses the bus when the CPU is not using it no impact on the CPU performance — Access memory to retrieve a data word — Forwards the word to the I/O peripheral DMA configurations

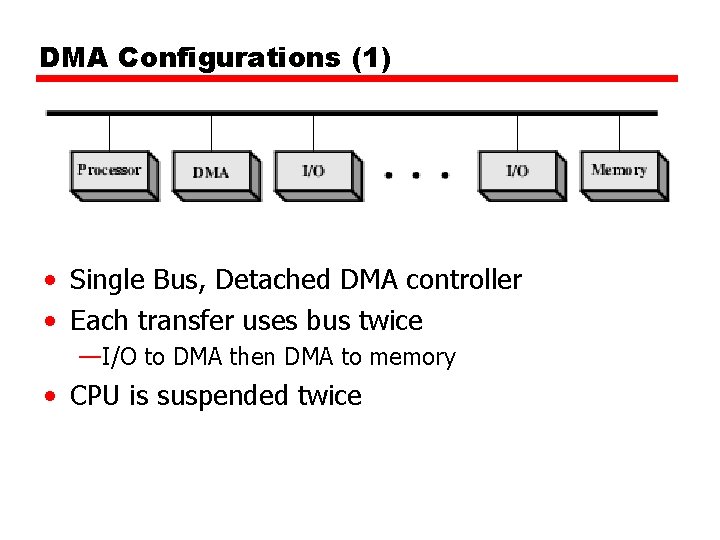

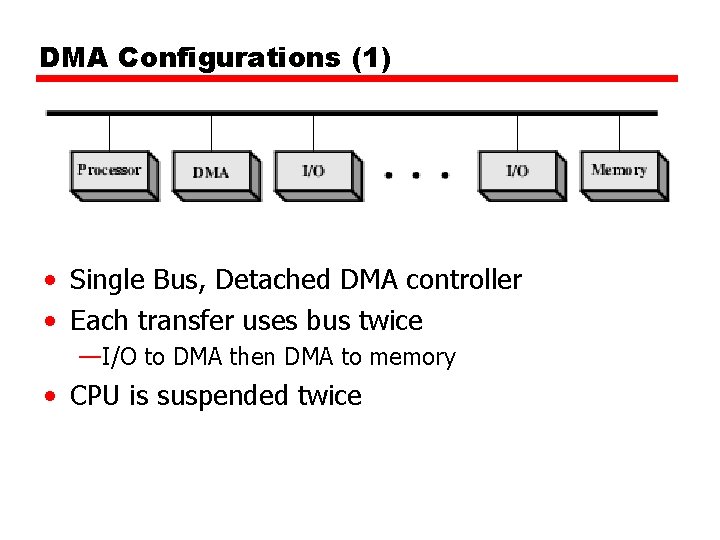

DMA Configurations (1) • Single Bus, Detached DMA controller • Each transfer uses bus twice —I/O to DMA then DMA to memory • CPU is suspended twice

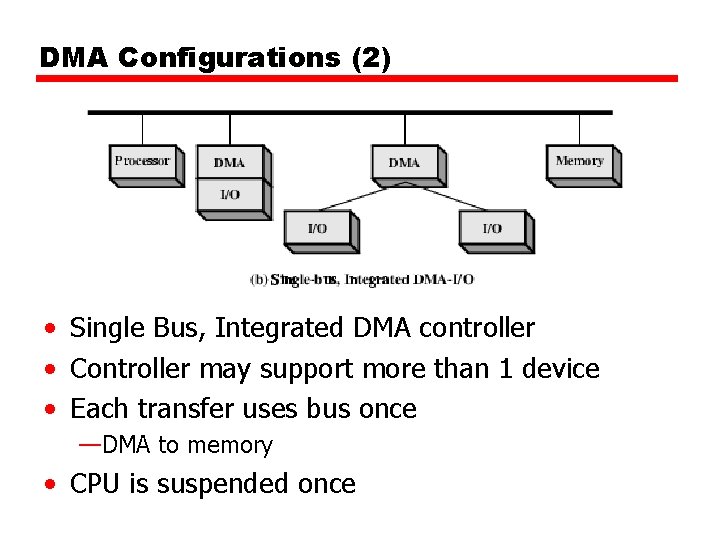

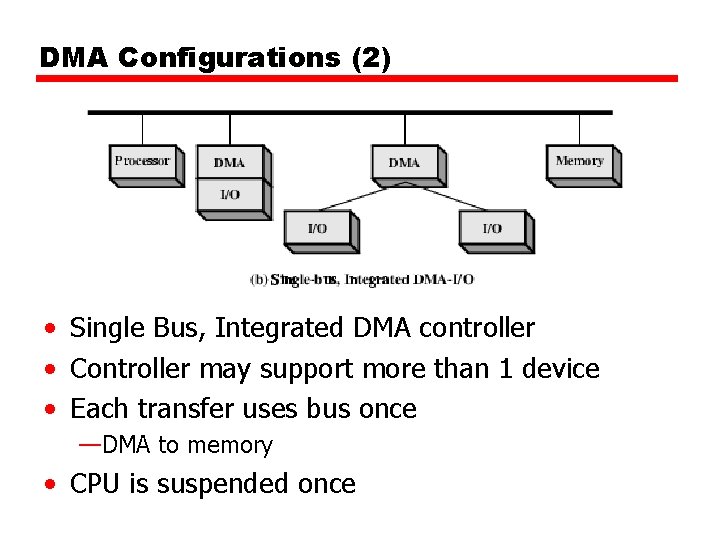

DMA Configurations (2) • Single Bus, Integrated DMA controller • Controller may support more than 1 device • Each transfer uses bus once —DMA to memory • CPU is suspended once

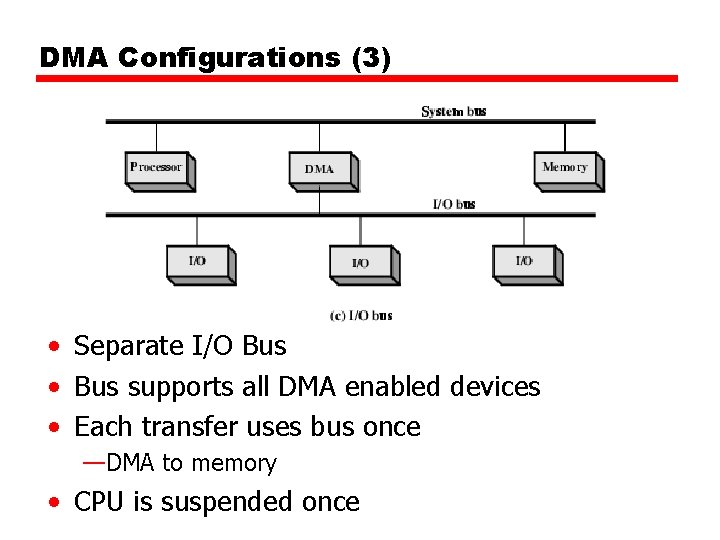

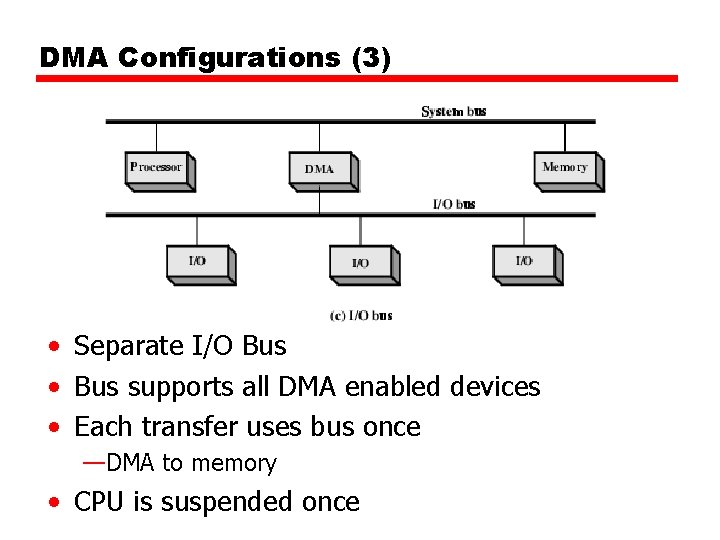

DMA Configurations (3) • Separate I/O Bus • Bus supports all DMA enabled devices • Each transfer uses bus once —DMA to memory • CPU is suspended once

I/O Channels • • • I/O devices getting more sophisticated e. g. 3 D graphics cards CPU instructs I/O controller to do transfer I/O controller does entire transfer Improves speed —Takes load off CPU —Dedicated processor is faster

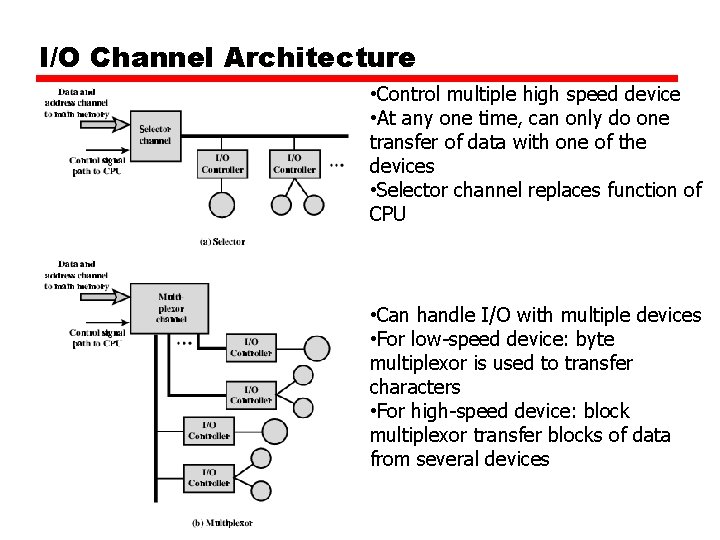

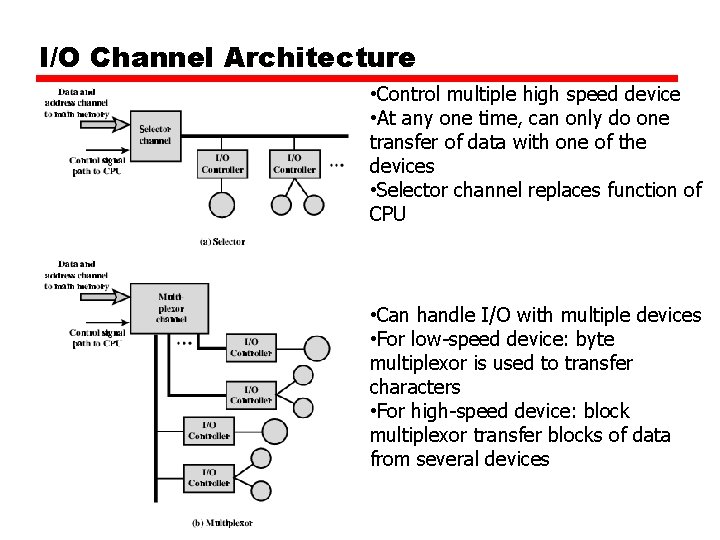

I/O Channel Architecture • Control multiple high speed device • At any one time, can only do one transfer of data with one of the devices • Selector channel replaces function of CPU • Can handle I/O with multiple devices • For low-speed device: byte multiplexor is used to transfer characters • For high-speed device: block multiplexor transfer blocks of data from several devices

External Interface • The external interface, made with the I/O module, must be tailored to the nature and operation of the peripheral — Parallel vs. Serial data transfers — Data format conversions — Transfer rates — Number of devices supported • Example: — Fire. Wire (IEEE 1394) high performance serial bus; data rates from 25 to 400 Mbps — Infini. Band data transfer is up to 30 Gbps; intended to replace PCI in servers

Foreground Reading • Check out Universal Serial Bus (USB) • Compare with other communication standards e. g. Ethernet