Computer Organization and Architecture Chapter 3 System Buses

Computer Organization and Architecture Chapter 3 System Buses

Topics • • • Computer Components Computer Function Interconnection Structures Bus Interconnection PC Buses

ORGANIZATION AND ARCHITECTURE • Computer architecture refers to those attributes of a system visible to a programmer or, put another way, those attributes that have a direct impact on the logical execution of a program. • Computer organization refers to the operational units and their interconnections that realize the architectural specifications. • Examples of architectural attributes include the instruction set, the number of bits used to represent various data types (e. g. , numbers, characters), I/O mechanisms, and techniques for addressing memory. • Organizational attributes include those hardware details transparent to the programmer, such as control signals; interfaces between the computer and peripherals; and the memory technology used.

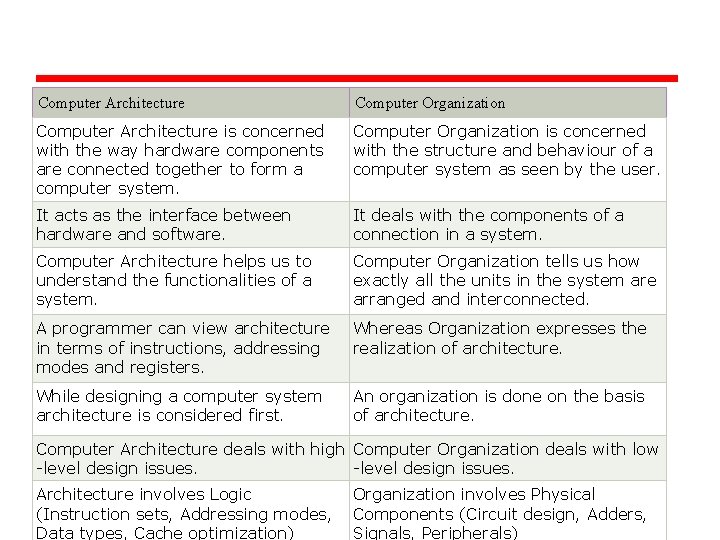

Computer Architecture Computer Organization Computer Architecture is concerned with the way hardware components are connected together to form a computer system. Computer Organization is concerned with the structure and behaviour of a computer system as seen by the user. It acts as the interface between hardware and software. It deals with the components of a connection in a system. Computer Architecture helps us to understand the functionalities of a system. Computer Organization tells us how exactly all the units in the system are arranged and interconnected. A programmer can view architecture in terms of instructions, addressing modes and registers. Whereas Organization expresses the realization of architecture. While designing a computer system architecture is considered first. An organization is done on the basis of architecture. Computer Architecture deals with high Computer Organization deals with low -level design issues. Architecture involves Logic (Instruction sets, Addressing modes, Data types, Cache optimization) Organization involves Physical Components (Circuit design, Adders, Signals, Peripherals)

Computer Components • Three key concepts of von Neumann architecture —Data and instructions are stored in a single R/W memory —Contents of memory are addressable by location, w/o regard to the type of data contained there —Execution occurs in a sequential fashion (unless explicitly modified), from one execution to the next.

Program Concept (1) • Hardware programming • • • If there is a particular computation to be performed, a configuration of logic components designed specifically for that computation could be constructed process of connecting the various components in the desired configuration as a form of programming. The resulting “program” is in the form of hardware and is termed a hardwired program. • Rewiring hardware for new program —Hardwired systems are inflexible • General purpose hardware can do different tasks, given correct control signals —Instead of re-wiring, supply a new set of control signals

Software programming • For each step, a new set of control signals is needed. • Let us provide a unique code for each possible set of control signals, and let us add to the general-purpose hardware a segment that can accept a code and generate control signals • Programming is now much easier. • Instead of rewiring the hardware for each new program, all we need to do is provide a new sequence of codes. • Each code is, in effect, an instruction, and part of the hardware interprets each instruction and generates control signals. • To distinguish this new method of programming, a sequence • of codes or instructions is called software.

Program Concept (2) • Software programming —General-purpose configuration of arithmetic and logic function —What is a program? – A sequence of steps – For each step, an arithmetic or logical operation is done – For each operation, a different set of control signals is needed and applied to the hardware —Instruction codes control signals —New program New instruction codes New control signals

System Components (1) • CPU —Instruction interpreter —General-purpose arithmetic and logic functions module • Memory —Temporary storage of code and results • I/O modules —Data and instructions need to get into the system and results out

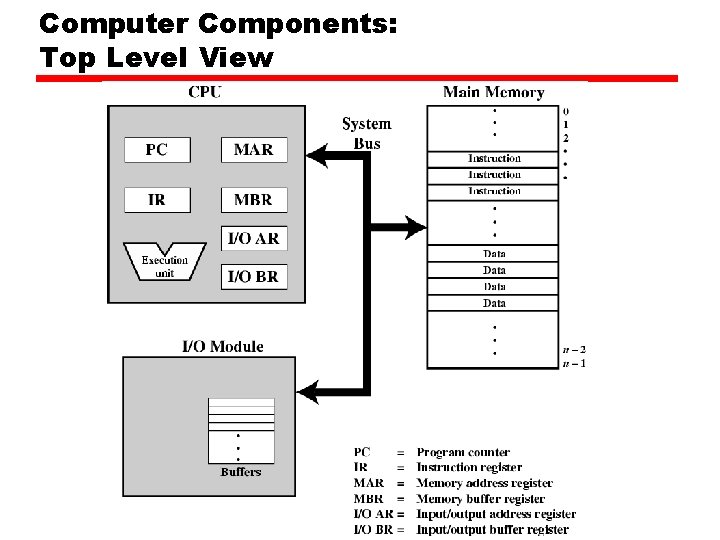

System Components (2) • CPU —Control Unit: hardware segment accepts codes and issues control signals —Arithmetic and Logic Unit —CPU registers – PC (program counter): address of next instruction to execute – IR (instruction register): current instruction being executed – MAR (memory address register): address in memory for next R/W – MBR(memory buffer register): data to be written/read to/from memory – I/O AR: particular I/O device – I/O BR: data exchanged between CPU and I/O module

System Components (3) • Memory —A set of locations defined by sequentially numbered addresses • I/O Module —Contains buffers for temporarily holding data to be exchanged with memory and CPU

Computer Components: Top Level View

Computer Function • Basic function? Program execution • Program? A set of instructions

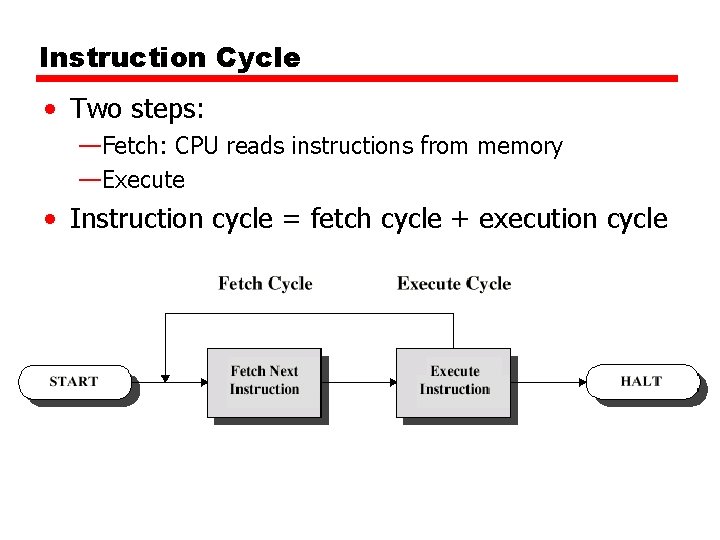

Instruction Cycle • Two steps: —Fetch: CPU reads instructions from memory —Execute • Instruction cycle = fetch cycle + execution cycle

Fetch Cycle • How do we know which instruction is next to fetch (i. e. where can we find it)? —Program Counter (PC) holds address of next instruction to fetch —Processor fetches instruction from memory location pointed to by PC —Increment PC, unless told otherwise • Where is the fetched instruction stored? —Instruction Register (IR) • Processor interprets instruction and performs required actions • In general, these actions fall into four categories

Execute Cycle • Processor-memory — Data may be transferred from processor to memory or from memory to processor. • Processor I/O — Data may be transferred to or from a peripheral device by transferring between the processor and an I/O module • Data processing — The processor may perform some arithmetic or logic operation on data. • Control —Alteration of sequence of operations —e. g. jump • For example, the processor may fetch an instruction from location 149, which specifies that the next instruction be from location 182. The processor will remember this fact by setting the program counter to 182. Thus, on the next fetchcycle, the instruction will be fetched from location 182 rather than 150. • Combination of above

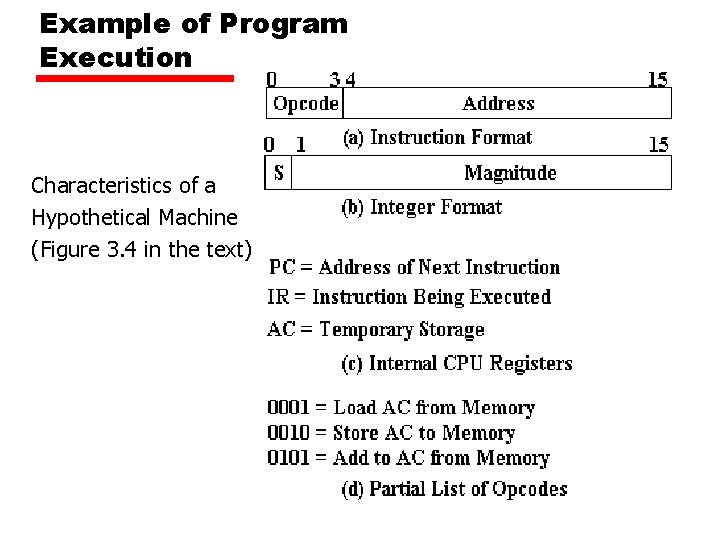

Example of Program Execution Characteristics of a Hypothetical Machine (Figure 3. 4 in the text)

Example of Program Execution • Want: Loc 941 Loc 940 + Loc 941 • One address format LOAD 940; AC Loc 940 ADD 941; AC + Loc 941 STORE 941; Loc 941 AC • Hex representation of instruction 1940 = 0001 1001 0100 0000 OP-code of LOAD

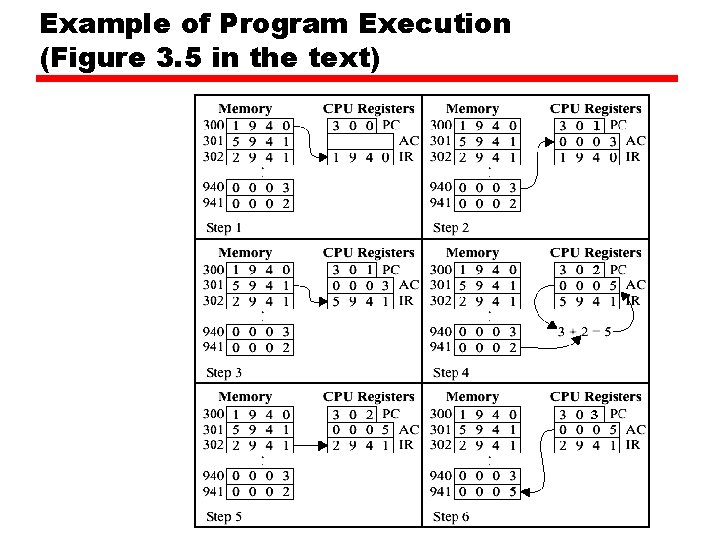

Example of Program Execution (Figure 3. 5 in the text)

• • • • The PC contains 300, the address of the first instruction. This instruction (the value 1940 in hexadecimal) is loaded into the instruction register IR and the PC is incremented. Note that this process involves the use of a memory address register (MAR) and a memory buffer register (MBR). For simplicity, these intermediate registers are ignored. 2. The first 4 bits (first hexadecimal digit) in the IR indicate that the AC is to be loaded. The remaining 12 bits (three hexadecimal digits) specify the address (940) from which data are to be loaded. 3. The next instruction (5941) is fetched from location 301 and the PC is incremented. 4. The old contents of the AC and the contents of location 941 are added and the result is stored in the AC. 5. The next instruction (2941) is fetched from location 302 and the PC is incremented. 6. The contents of the AC are stored in location 941.

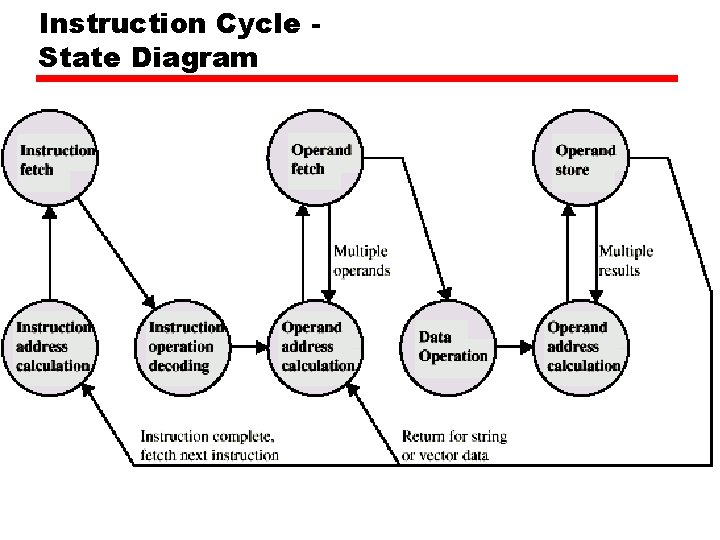

Instruction Cycle State Diagram

- Slides: 22