Computer Architecture Parhami Copyright 2005 by Oxford University

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 1

Figure 15. 1 Pipelining in the student registration process. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 2

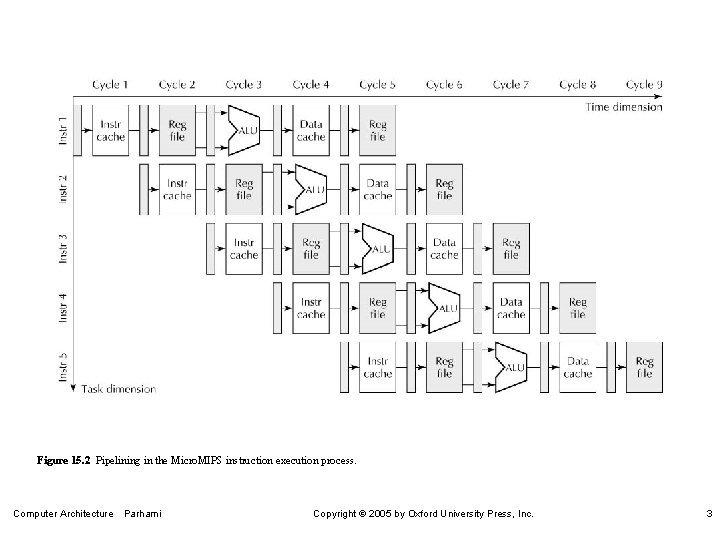

Figure 15. 2 Pipelining in the Micro. MIPS instruction execution process. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 3

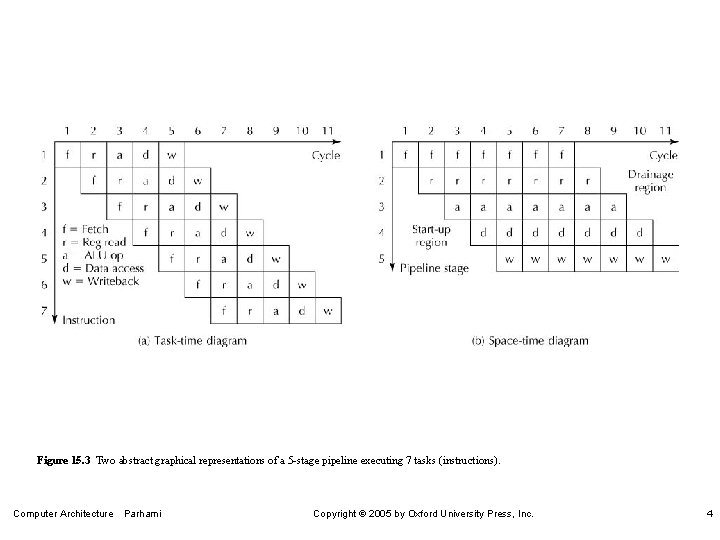

Figure 15. 3 Two abstract graphical representations of a 5 -stage pipeline executing 7 tasks (instructions). Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 4

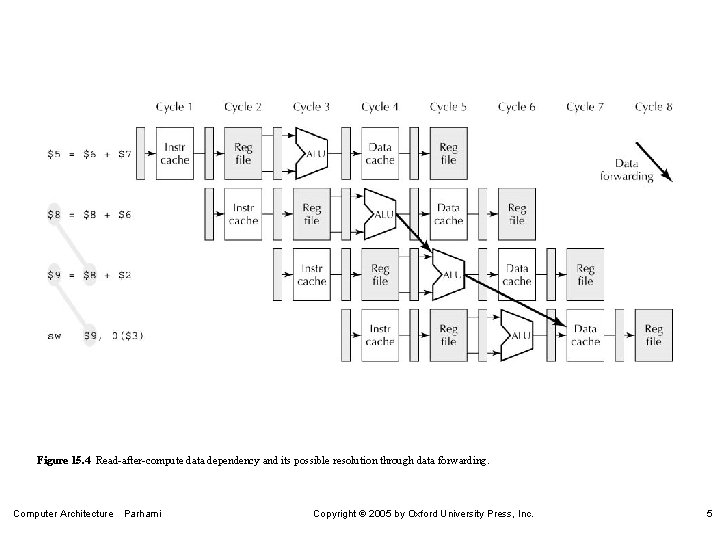

Figure 15. 4 Read-after-compute data dependency and its possible resolution through data forwarding. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 5

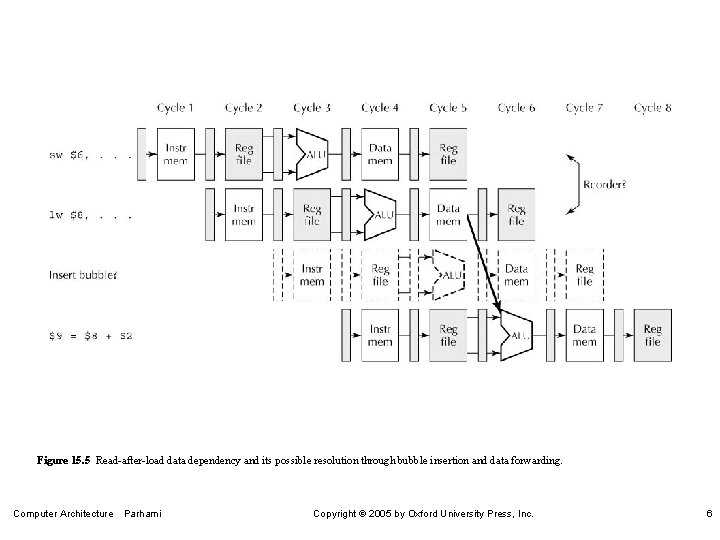

Figure 15. 5 Read-after-load data dependency and its possible resolution through bubble insertion and data forwarding. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 6

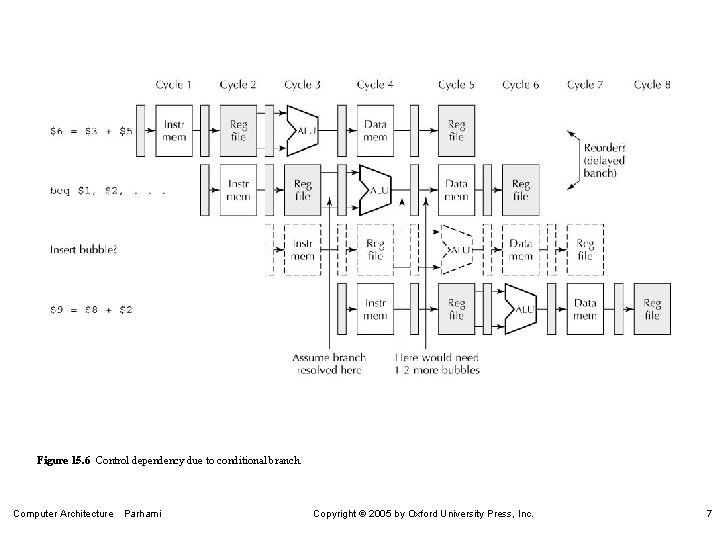

Figure 15. 6 Control dependency due to conditional branch. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 7

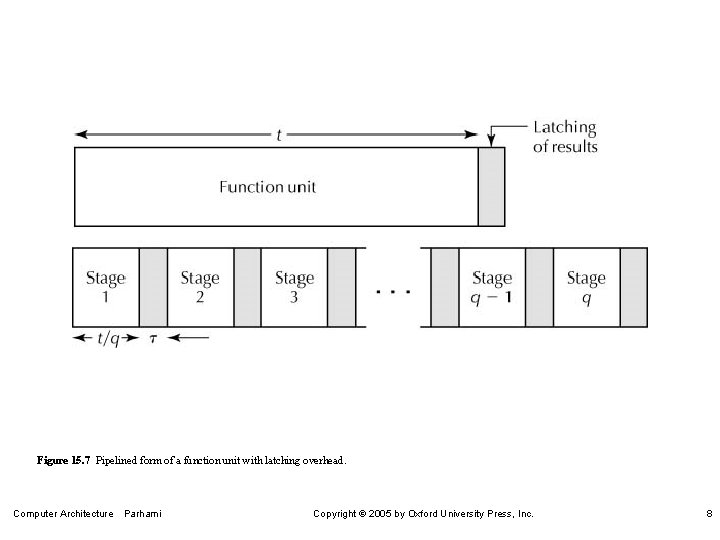

Figure 15. 7 Pipelined form of a function unit with latching overhead. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 8

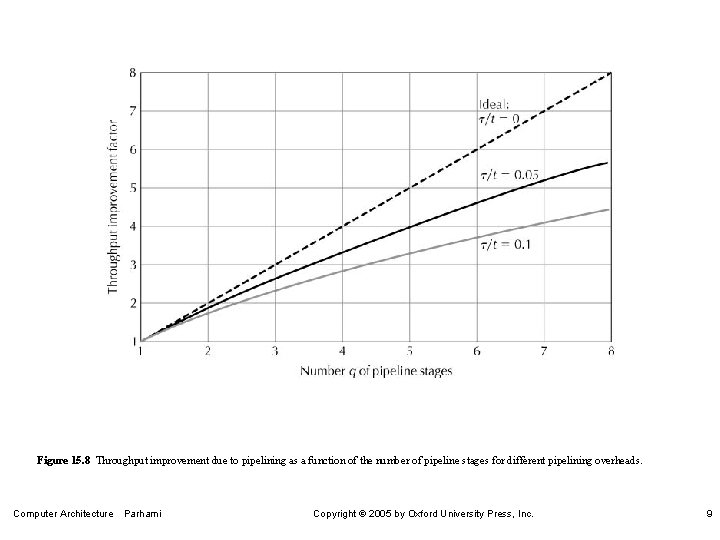

Figure 15. 8 Throughput improvement due to pipelining as a function of the number of pipeline stages for different pipelining overheads. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 9

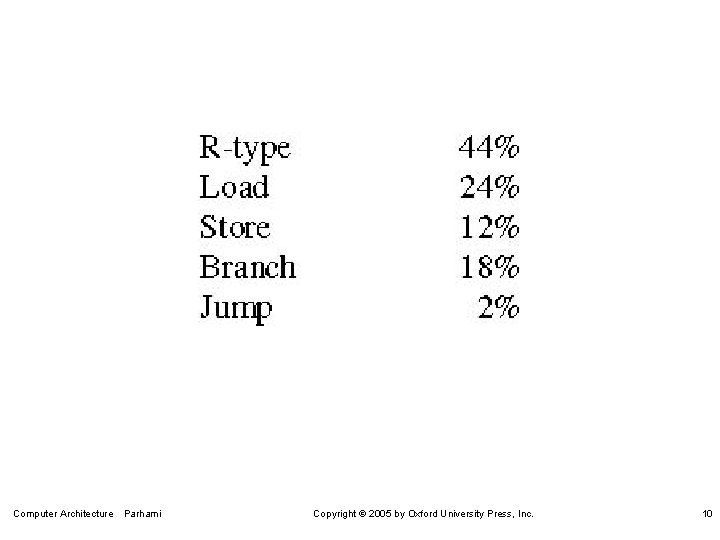

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 10

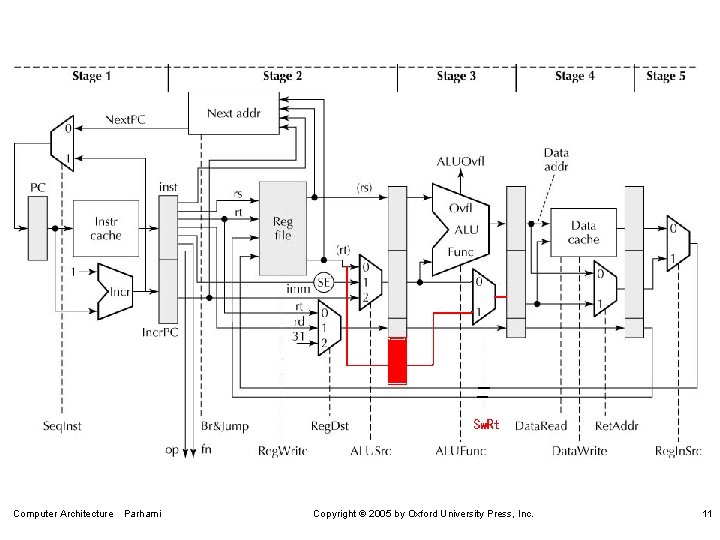

Figure 15. 9 Key elements of the pipelined Micro. MIPS data path. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 11

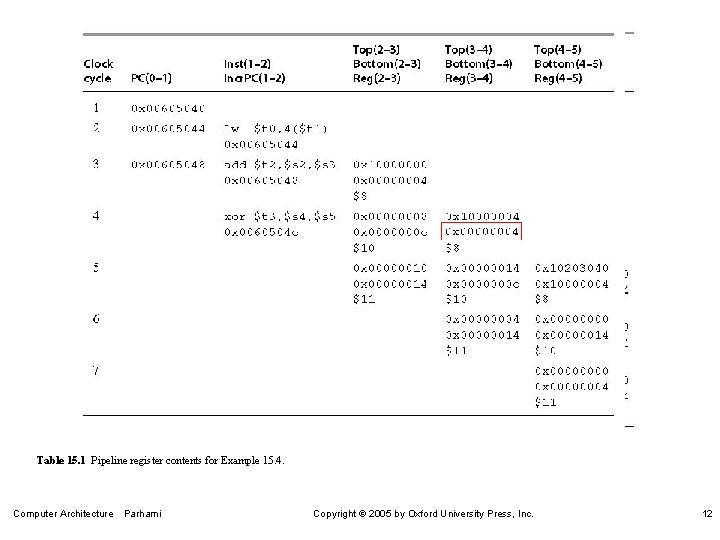

Table 15. 1 Pipeline register contents for Example 15. 4. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 12

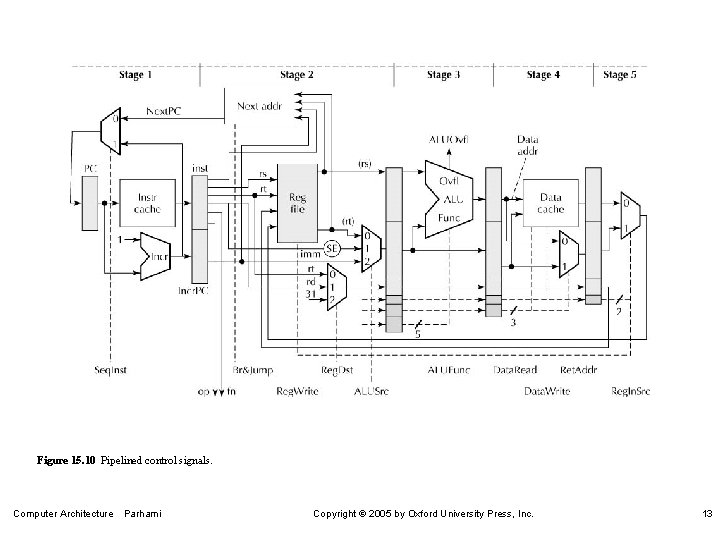

Figure 15. 10 Pipelined control signals. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 13

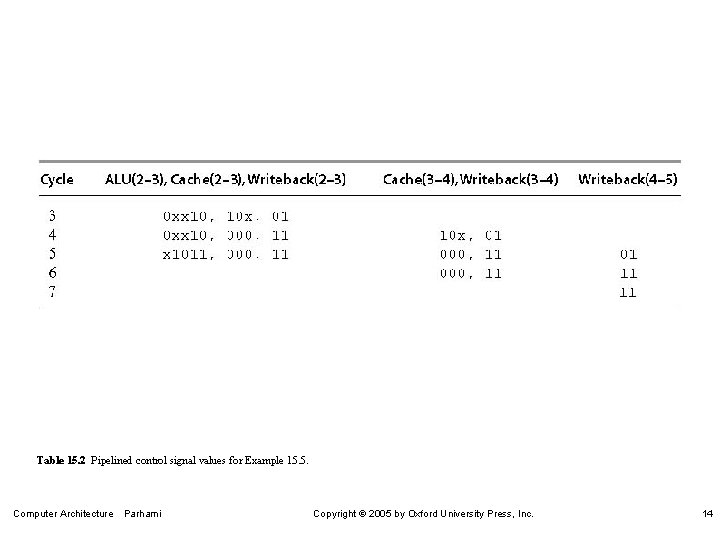

Table 15. 2 Pipelined control signal values for Example 15. 5. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 14

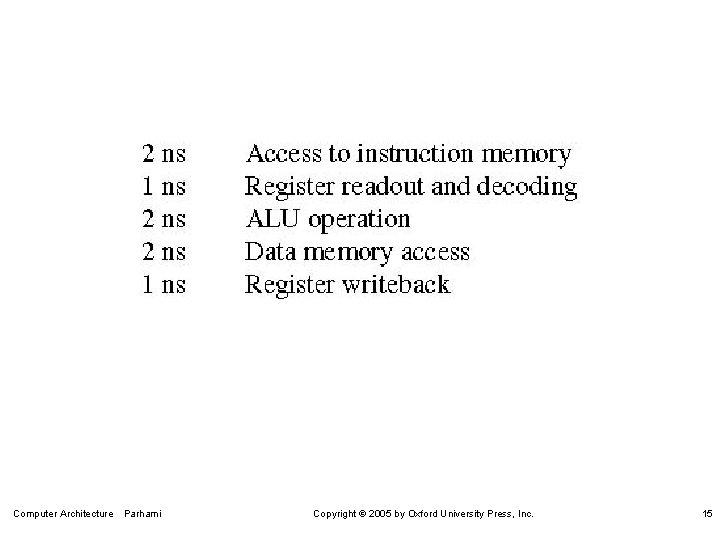

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 15

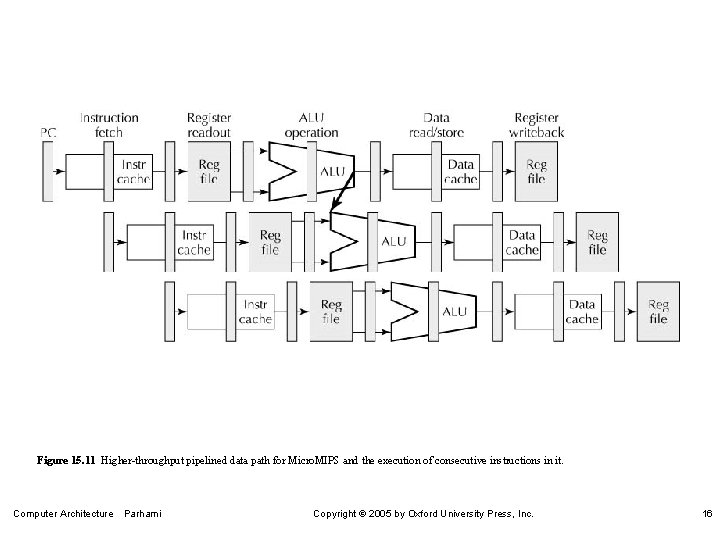

Figure 15. 11 Higher-throughput pipelined data path for Micro. MIPS and the execution of consecutive instructions in it. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 16

- Slides: 16