Computer Architecture Parhami Copyright 2005 by Oxford University

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 1

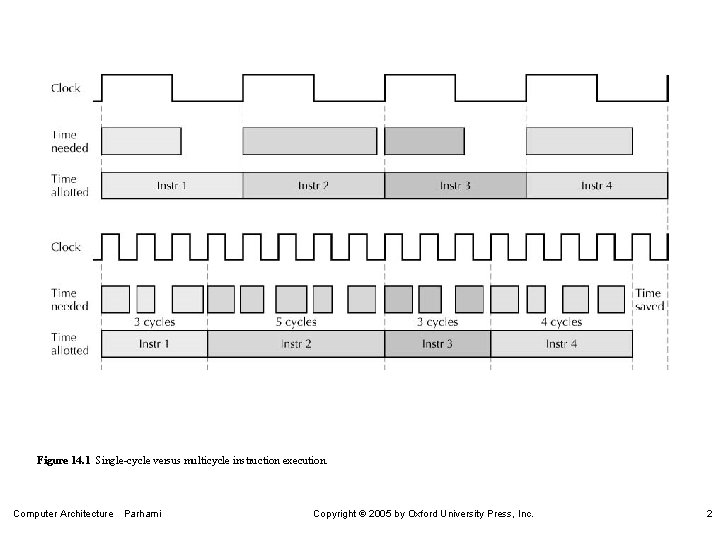

Figure 14. 1 Single-cycle versus multicycle instruction execution. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 2

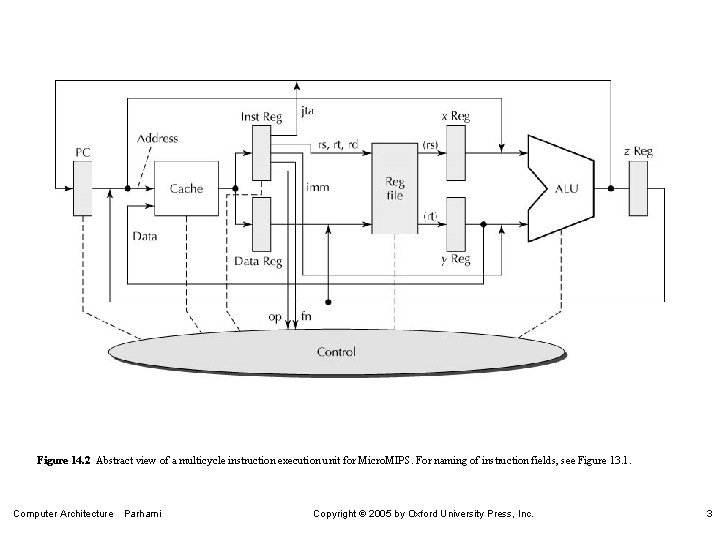

Figure 14. 2 Abstract view of a multicycle instruction execution unit for Micro. MIPS. For naming of instruction fields, see Figure 13. 1. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 3

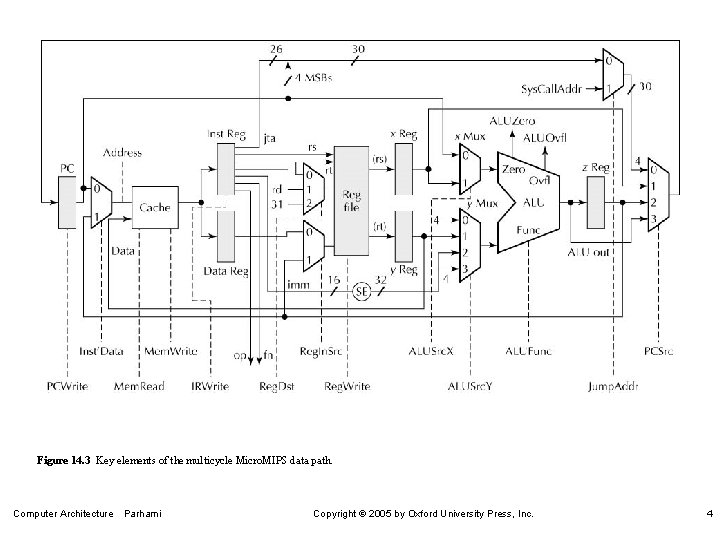

Figure 14. 3 Key elements of the multicycle Micro. MIPS data path. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 4

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 5

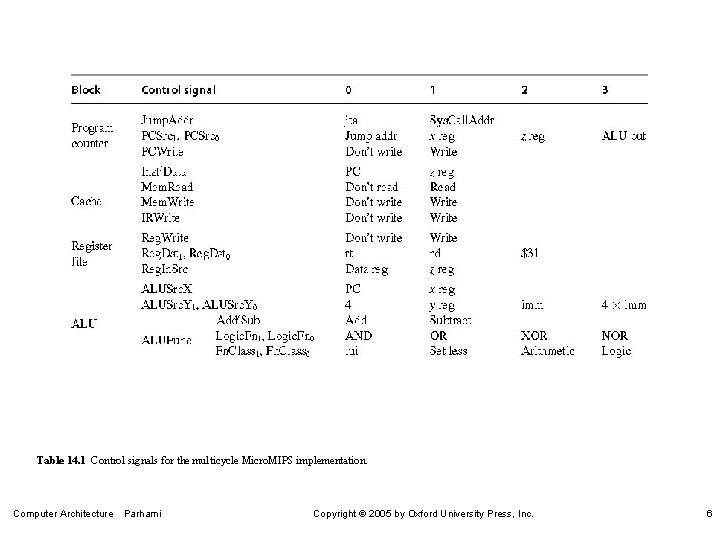

Table 14. 1 Control signals for the multicycle Micro. MIPS implementation. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 6

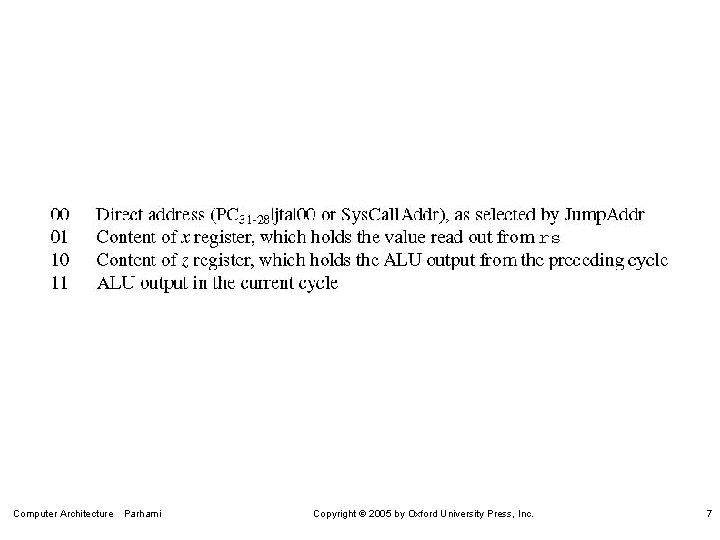

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 7

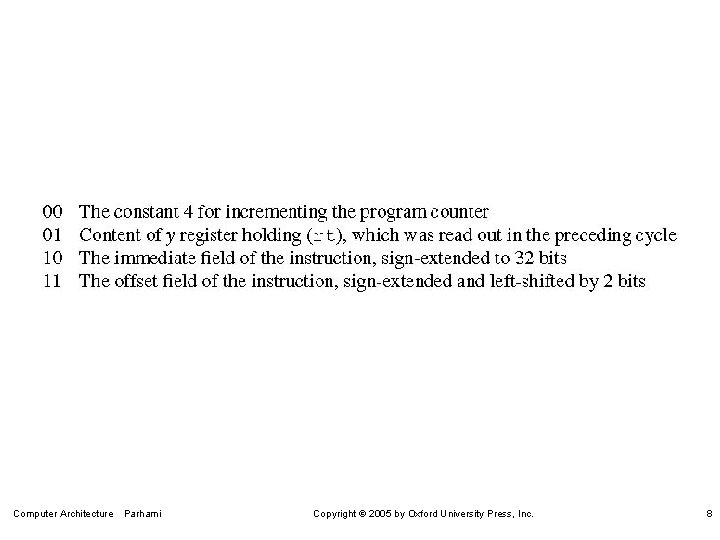

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 8

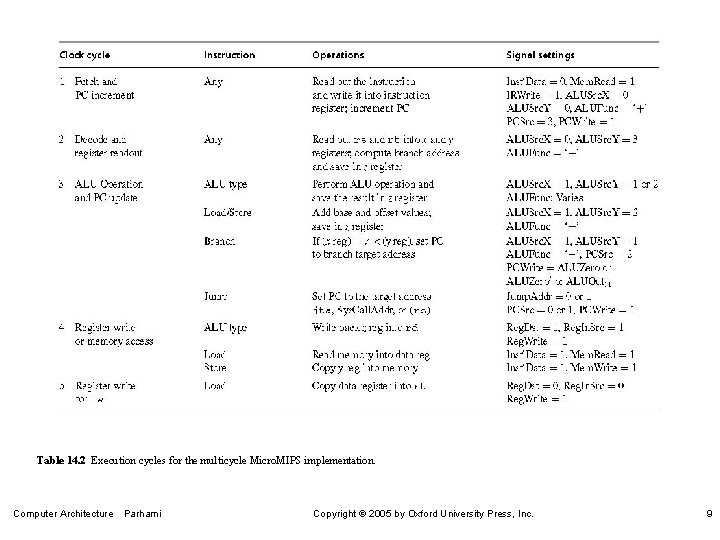

Table 14. 2 Execution cycles for the multicycle Micro. MIPS implementation. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 9

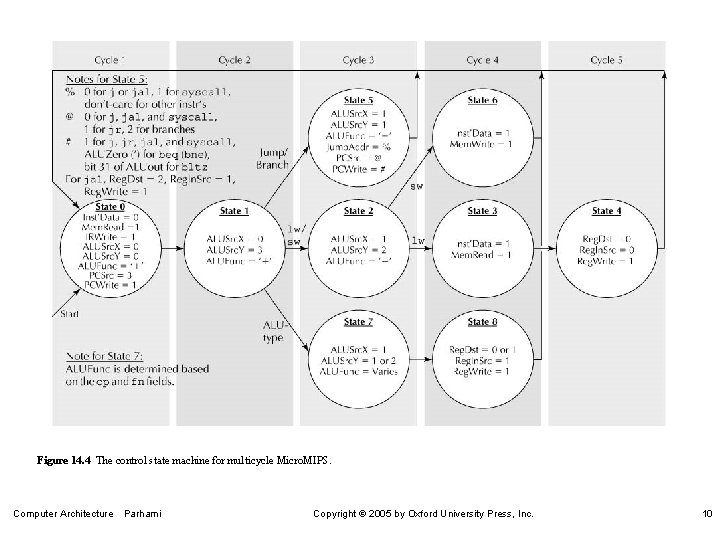

Figure 14. 4 The control state machine for multicycle Micro. MIPS. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 10

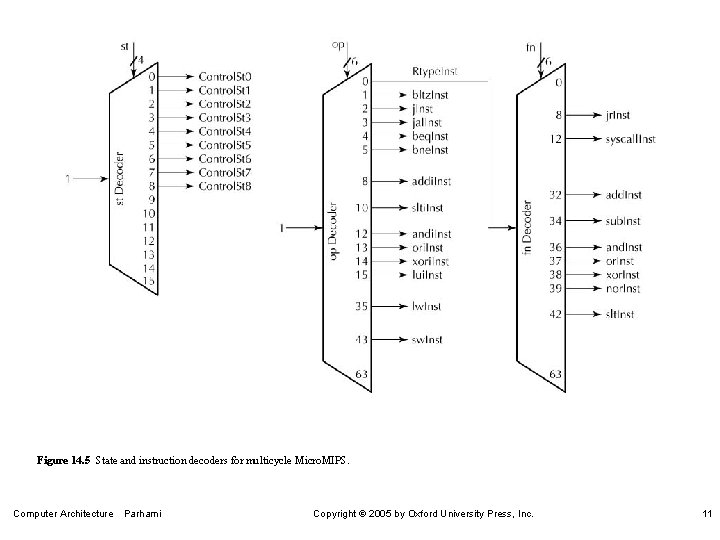

Figure 14. 5 State and instruction decoders for multicycle Micro. MIPS. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 11

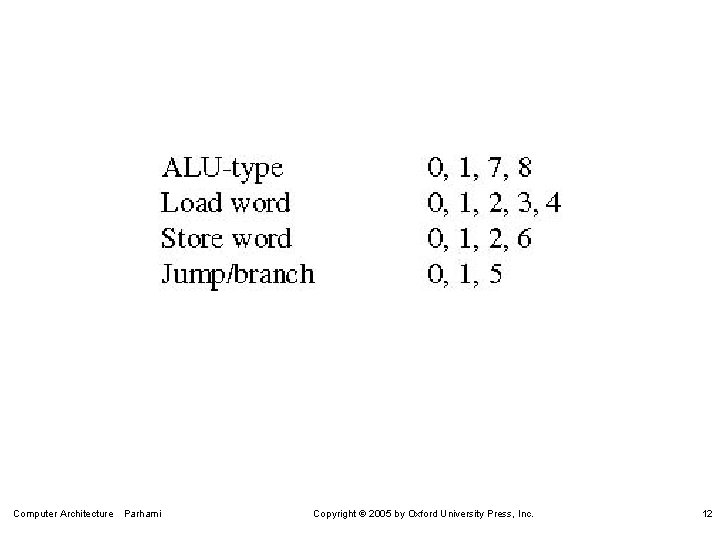

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 12

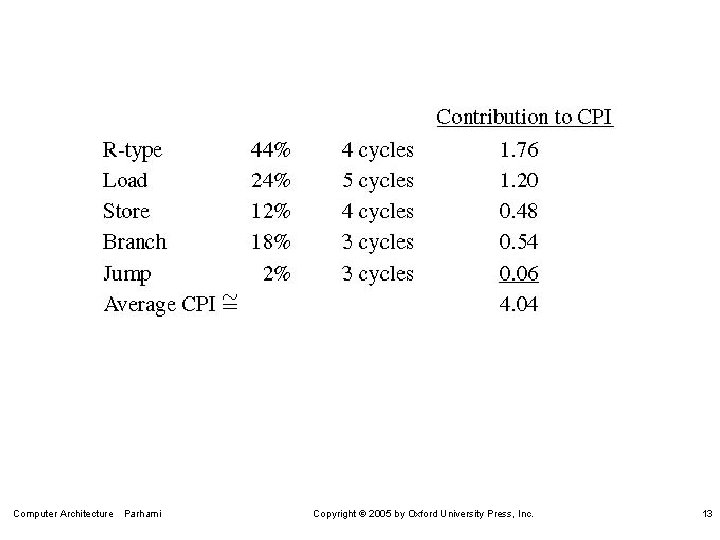

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 13

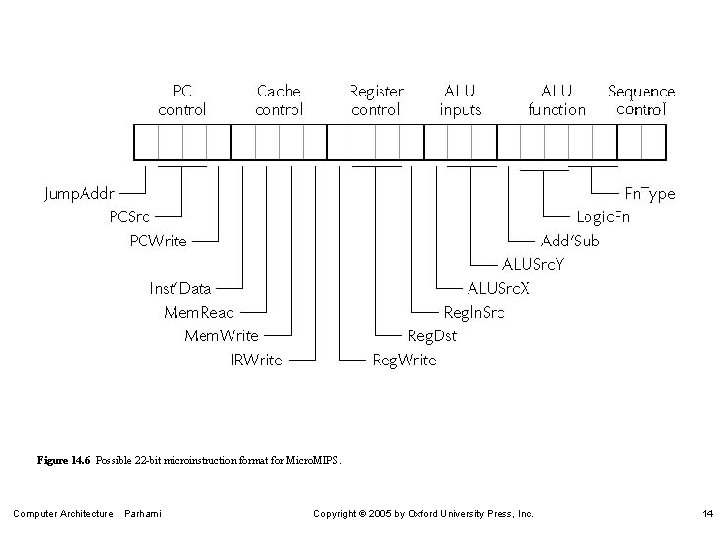

Figure 14. 6 Possible 22 -bit microinstruction format for Micro. MIPS. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 14

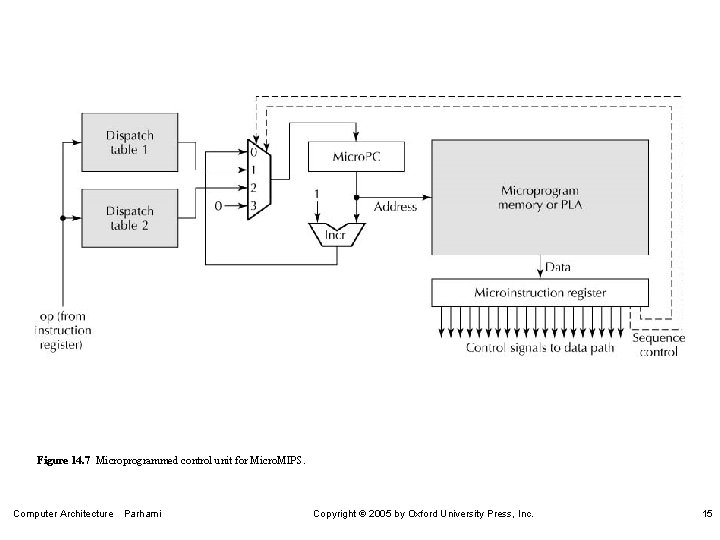

Figure 14. 7 Microprogrammed control unit for Micro. MIPS. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 15

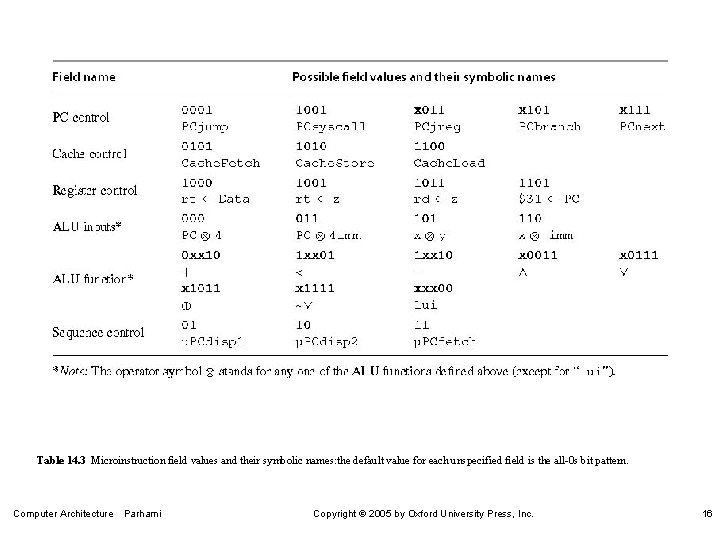

Table 14. 3 Microinstruction field values and their symbolic names: the default value for each unspecified field is the all-0 s bit pattern. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 16

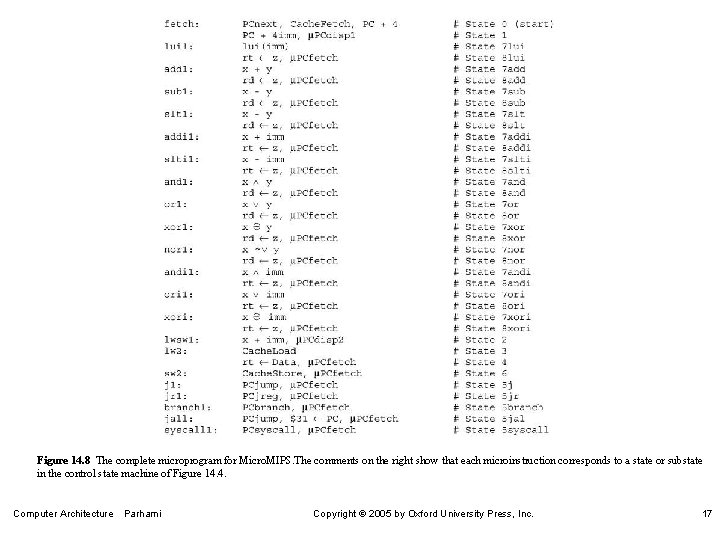

Figure 14. 8 The complete microprogram for Micro. MIPS. The comments on the right show that each microinstruction corresponds to a state or substate in the control state machine of Figure 14. 4. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 17

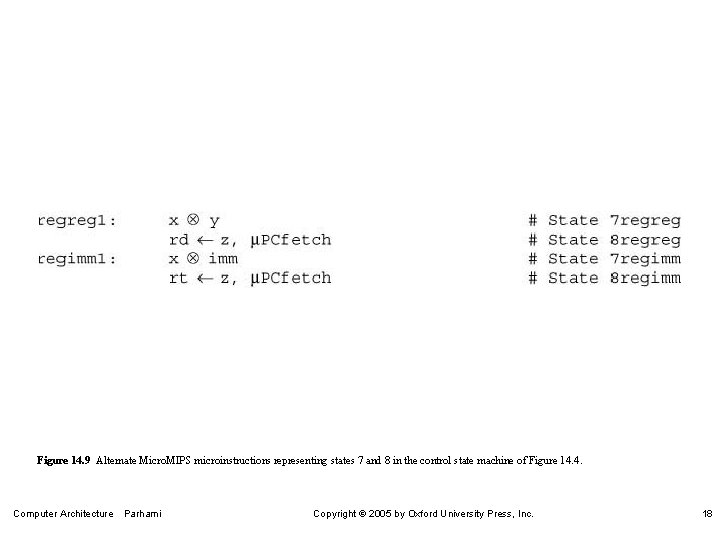

Figure 14. 9 Alternate Micro. MIPS microinstructions representing states 7 and 8 in the control state machine of Figure 14. 4. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 18

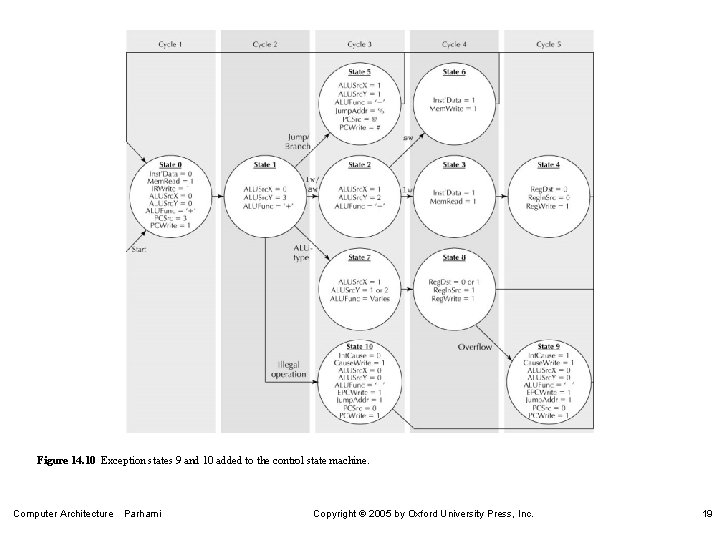

Figure 14. 10 Exception states 9 and 10 added to the control state machine. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 19

- Slides: 19