Computer Architecture Parhami 1 Figure 11 1 Multiplication

- Slides: 17

Computer Architecture Parhami 1

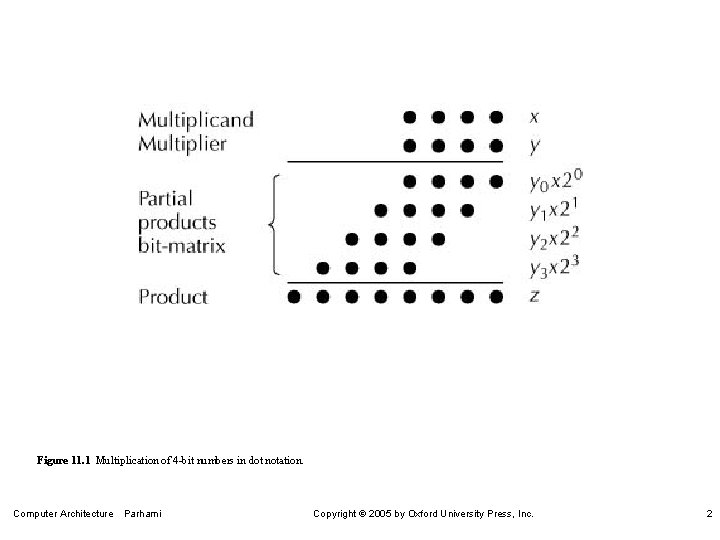

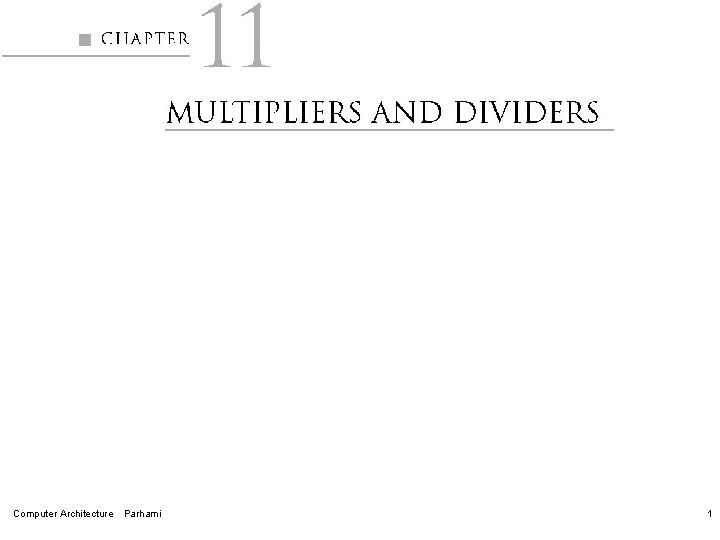

Figure 11. 1 Multiplication of 4 -bit numbers in dot notation. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 2

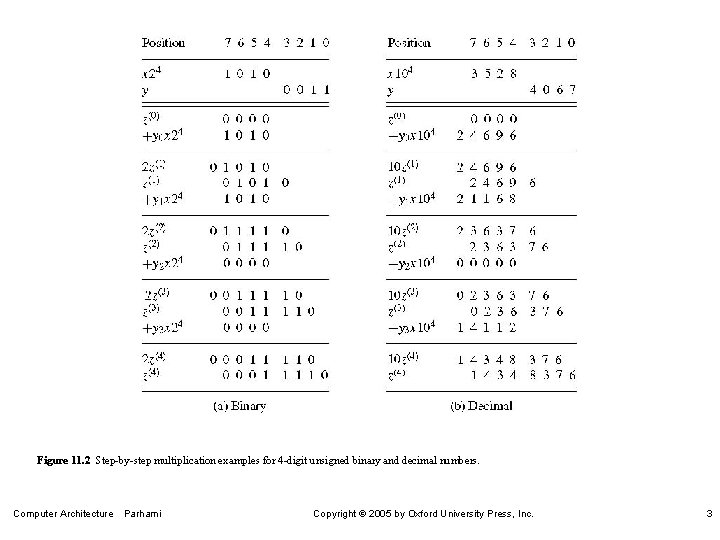

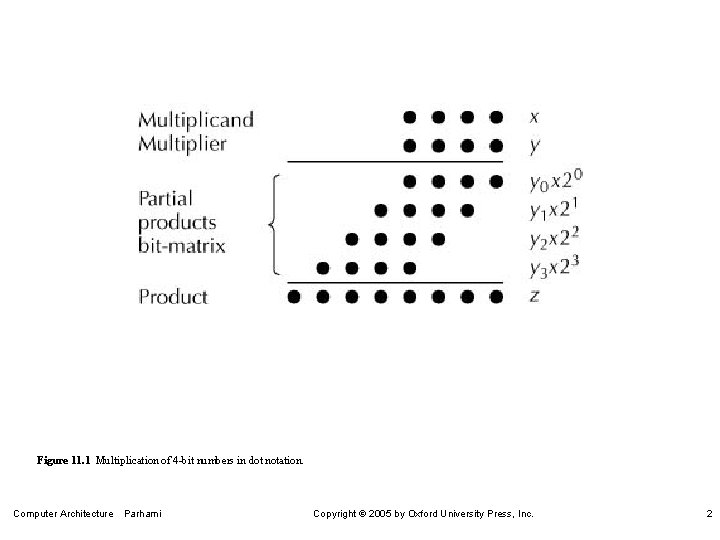

Figure 11. 2 Step-by-step multiplication examples for 4 -digit unsigned binary and decimal numbers. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 3

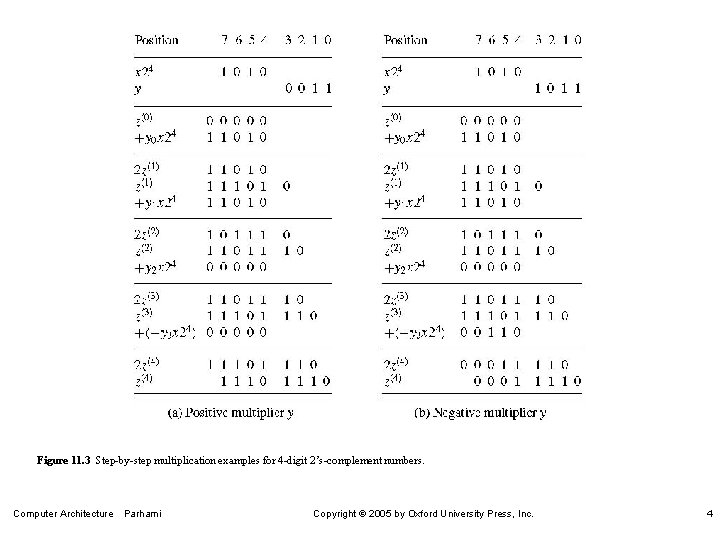

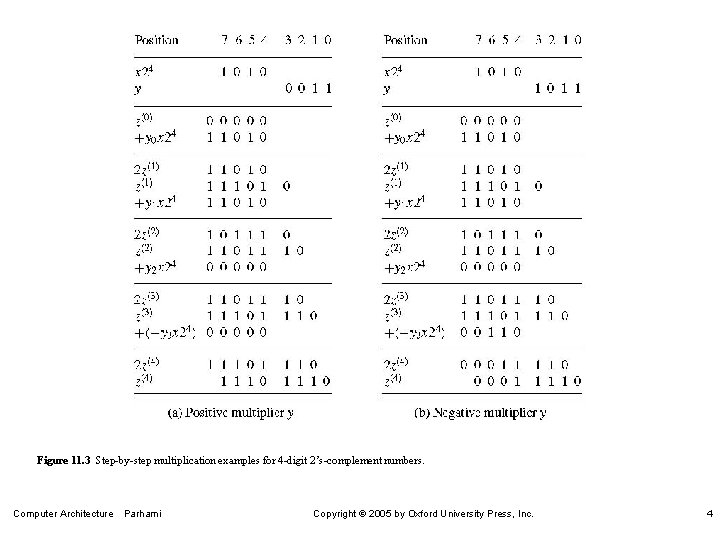

Figure 11. 3 Step-by-step multiplication examples for 4 -digit 2’s-complement numbers. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 4

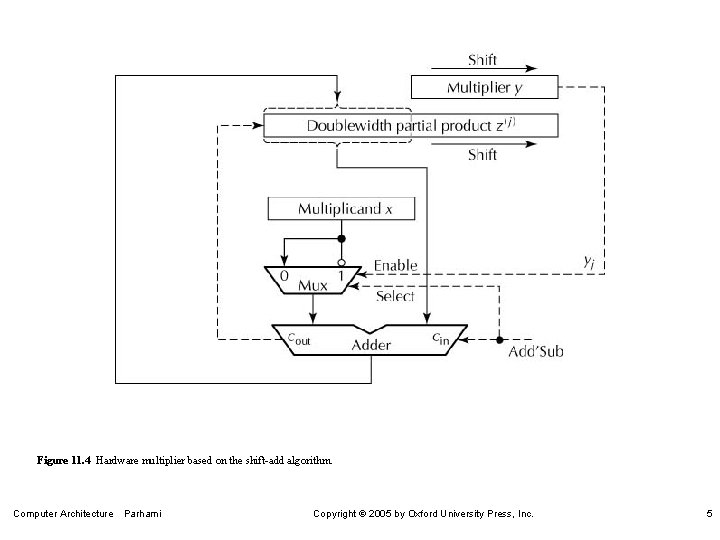

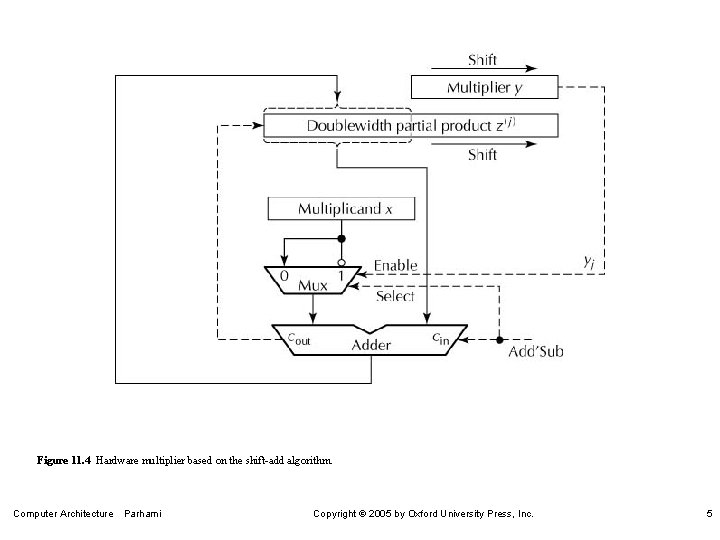

Figure 11. 4 Hardware multiplier based on the shift-add algorithm. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 5

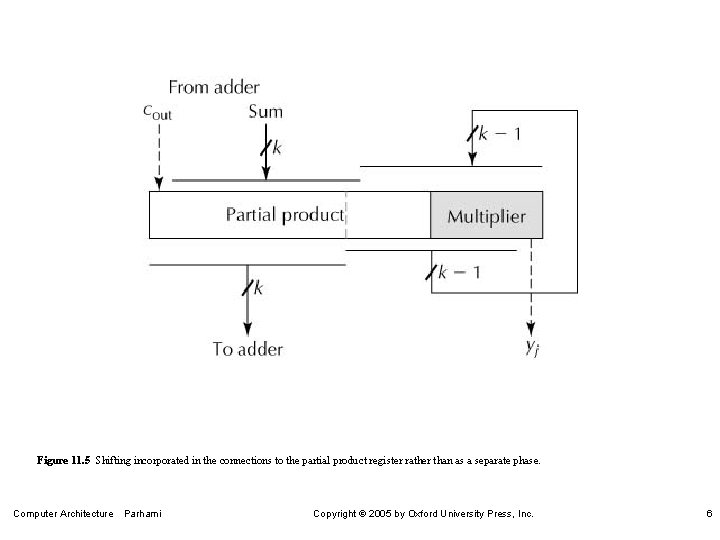

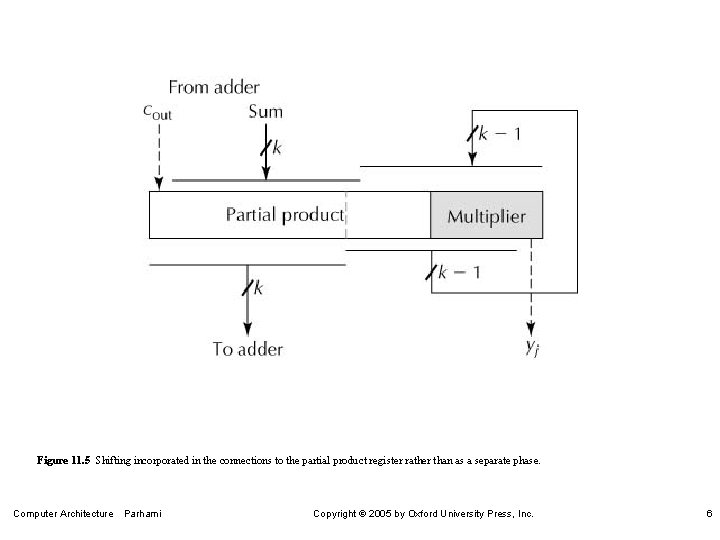

Figure 11. 5 Shifting incorporated in the connections to the partial product register rather than as a separate phase. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 6

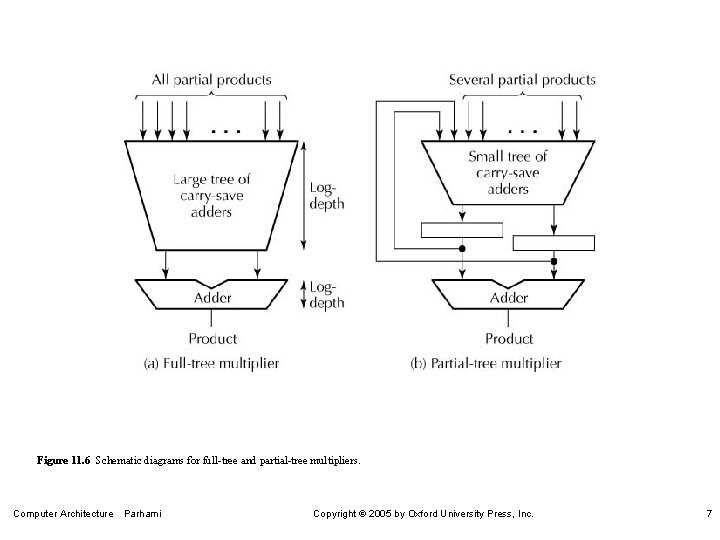

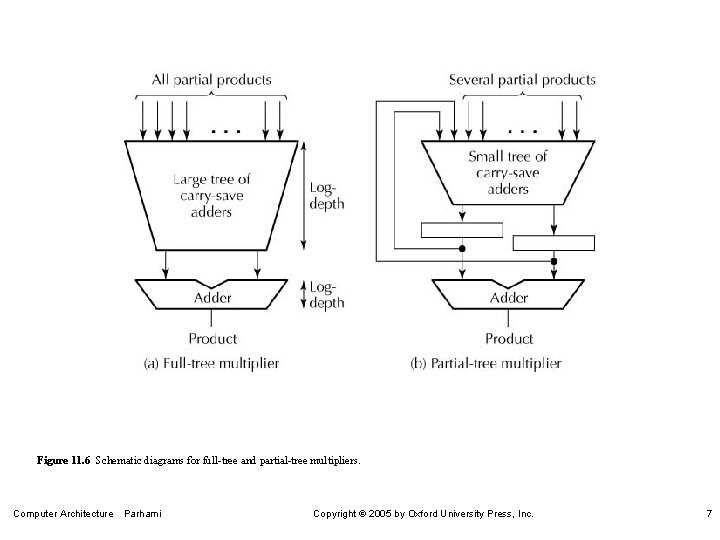

Figure 11. 6 Schematic diagrams for full-tree and partial-tree multipliers. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 7

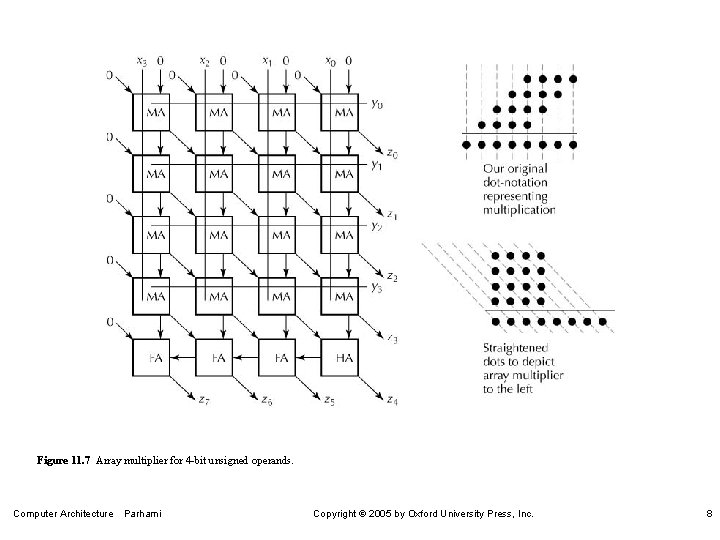

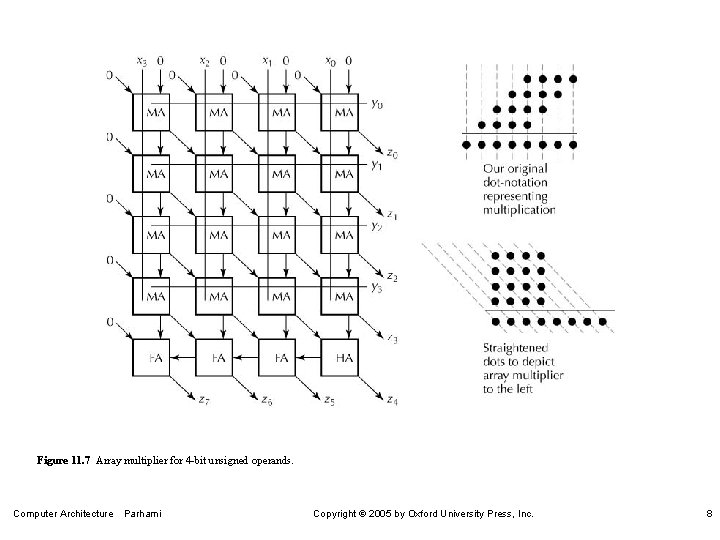

Figure 11. 7 Array multiplier for 4 -bit unsigned operands. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 8

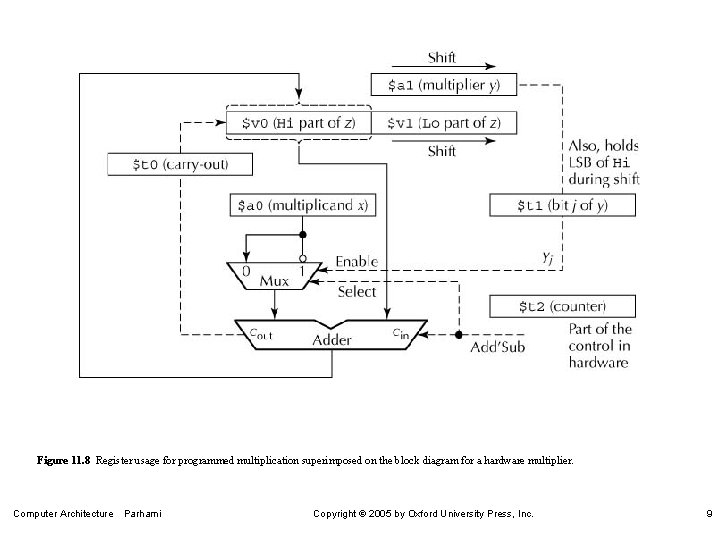

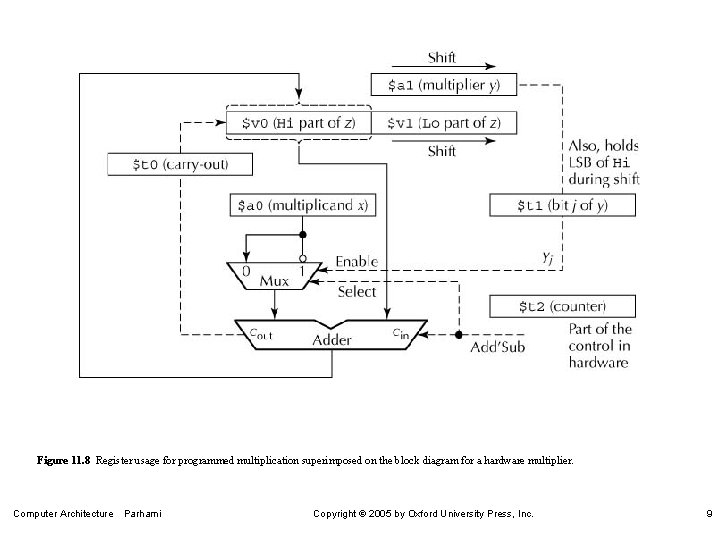

Figure 11. 8 Register usage for programmed multiplication superimposed on the block diagram for a hardware multiplier. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 9

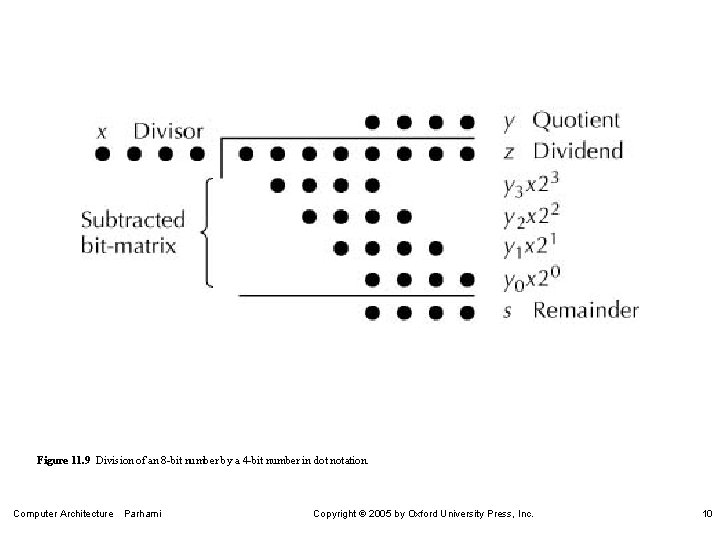

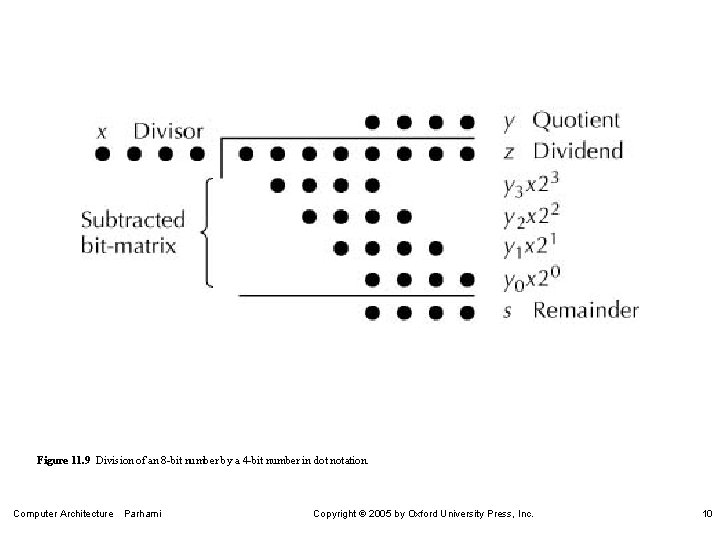

Figure 11. 9 Division of an 8 -bit number by a 4 -bit number in dot notation. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 10

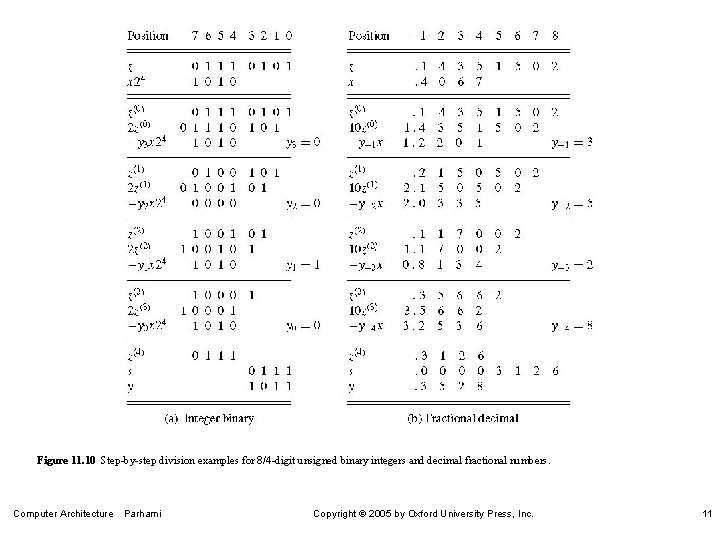

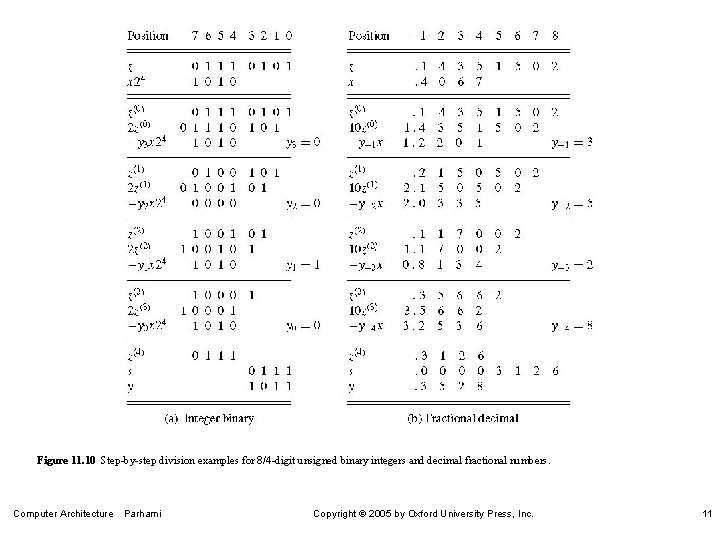

Figure 11. 10 Step-by-step division examples for 8/4 -digit unsigned binary integers and decimal fractional numbers. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 11

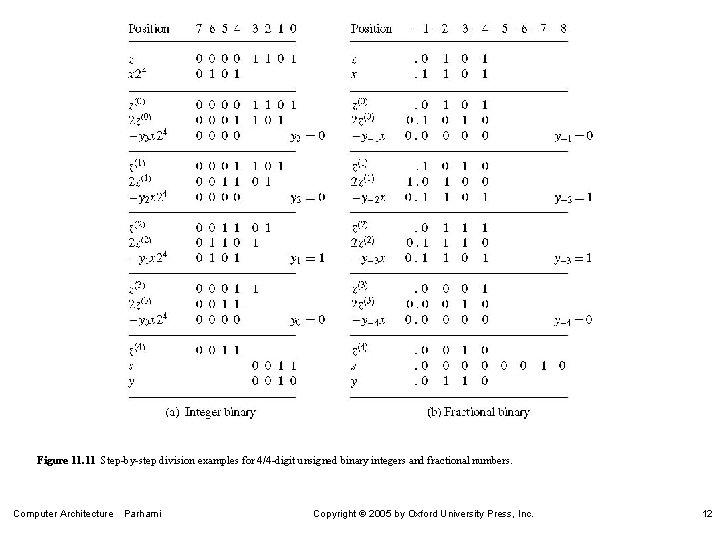

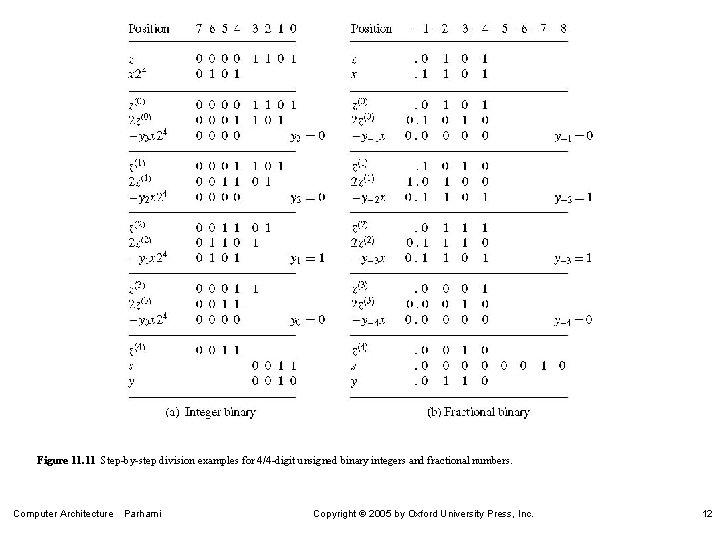

Figure 11. 11 Step-by-step division examples for 4/4 -digit unsigned binary integers and fractional numbers. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 12

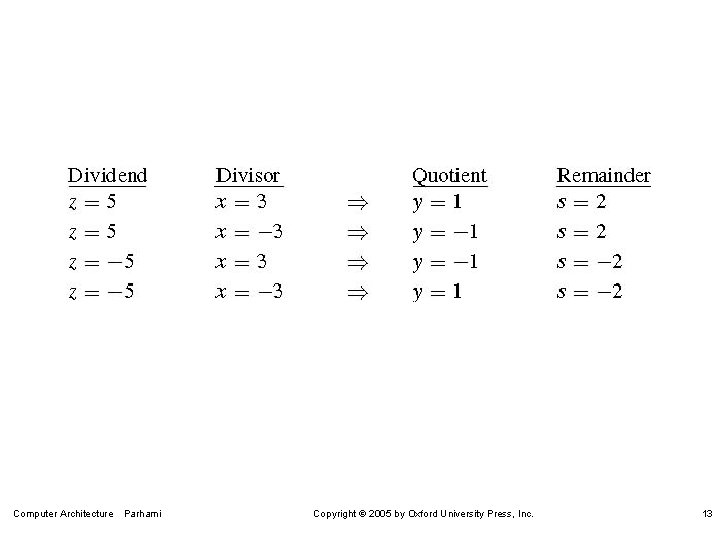

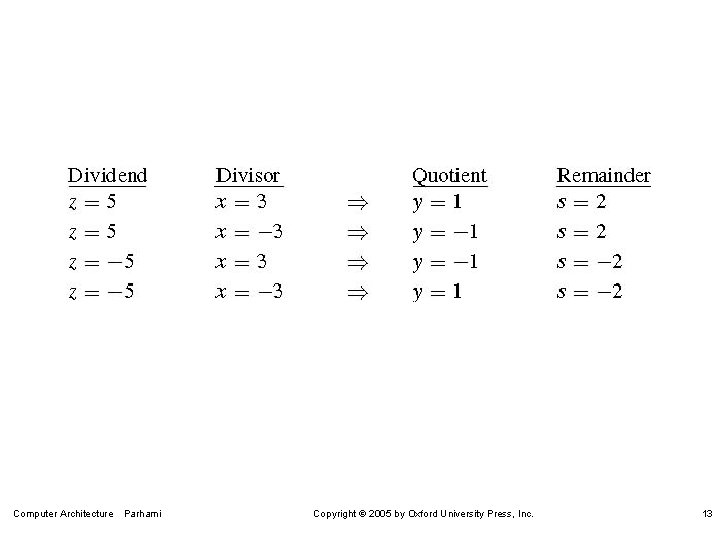

Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 13

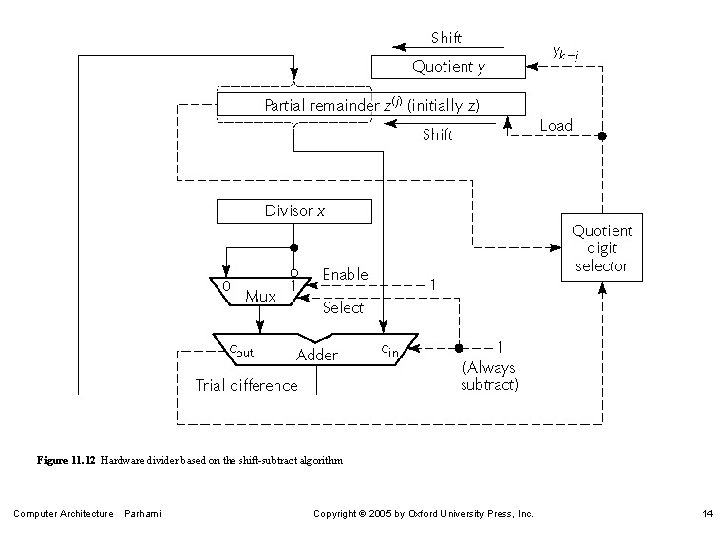

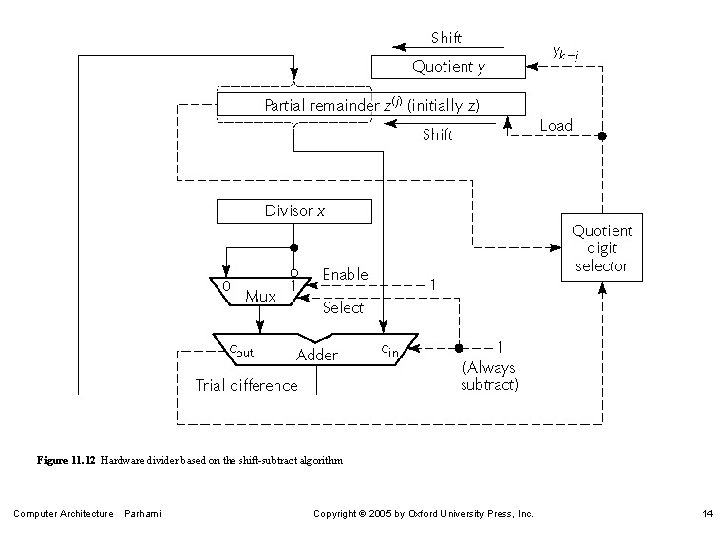

Figure 11. 12 Hardware divider based on the shift-subtract algorithm Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 14

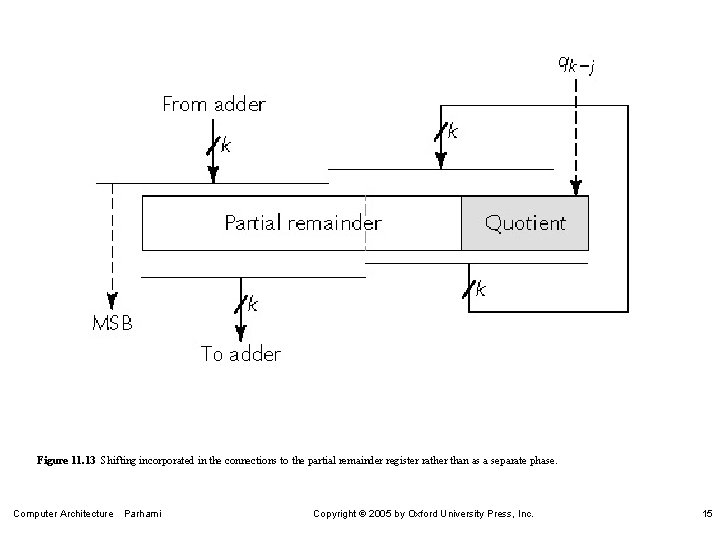

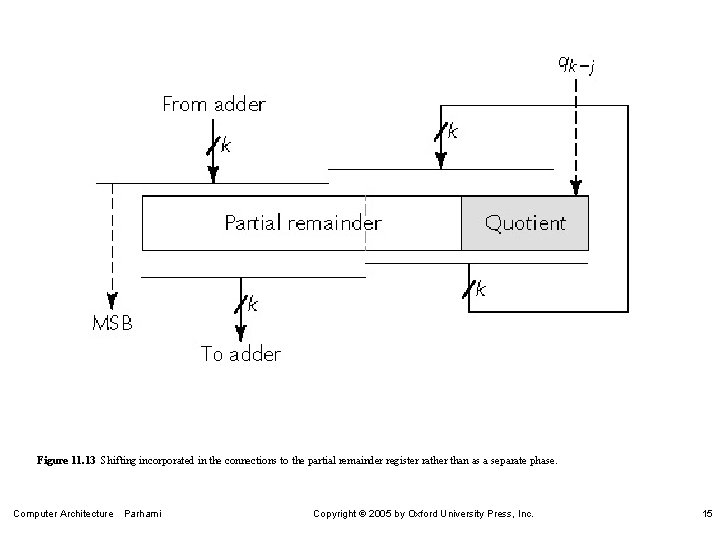

Figure 11. 13 Shifting incorporated in the connections to the partial remainder register rather than as a separate phase. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 15

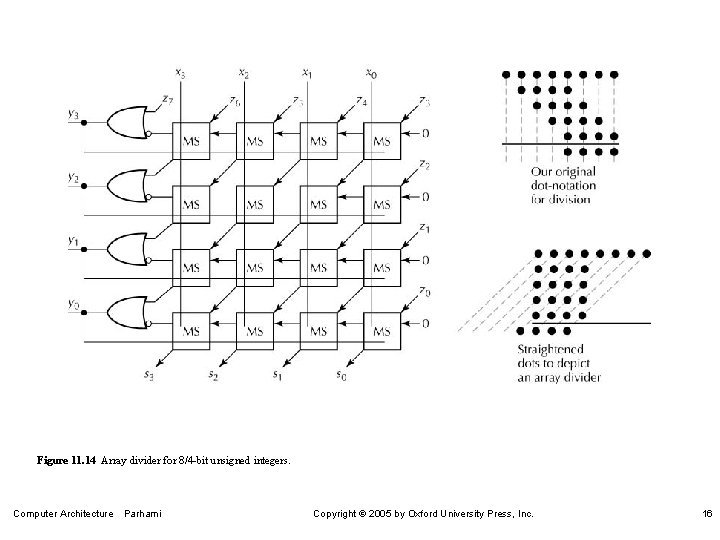

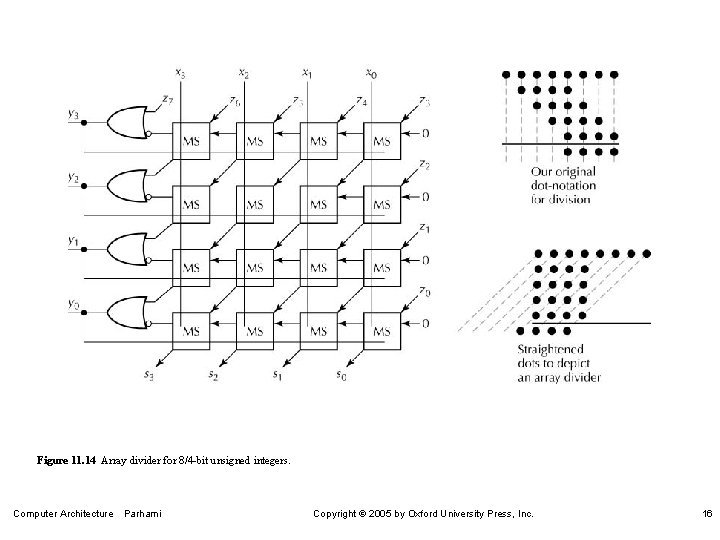

Figure 11. 14 Array divider for 8/4 -bit unsigned integers. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 16

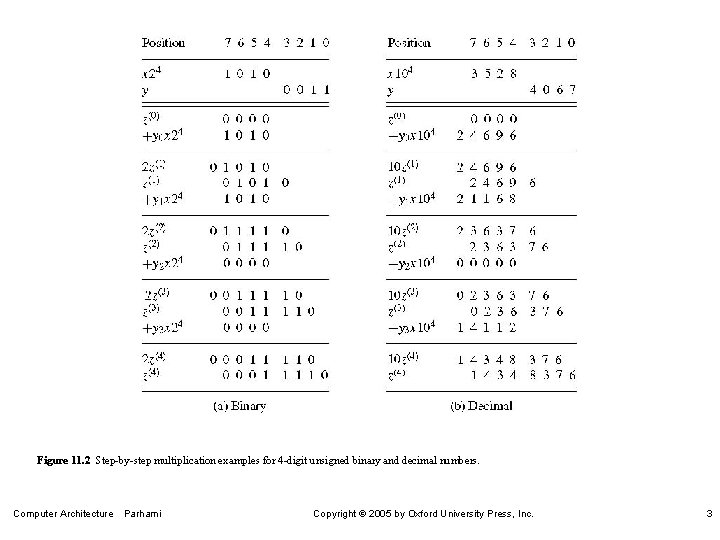

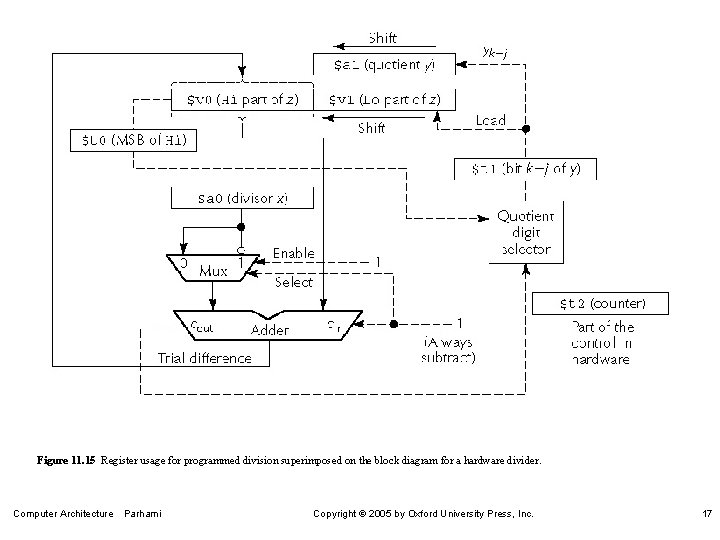

Figure 11. 15 Register usage for programmed division superimposed on the block diagram for a hardware divider. Computer Architecture Parhami Copyright 2005 by Oxford University Press, Inc. 17