Computer Architecture Exception Handling and Advanced Pipelining MemoryStorage

- Slides: 16

Computer Architecture Exception Handling and Advanced Pipelining Memory/Storage Architecture Lab

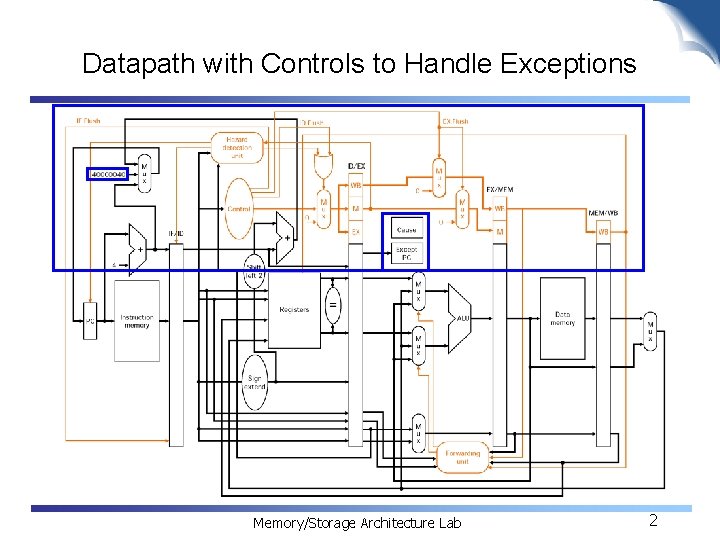

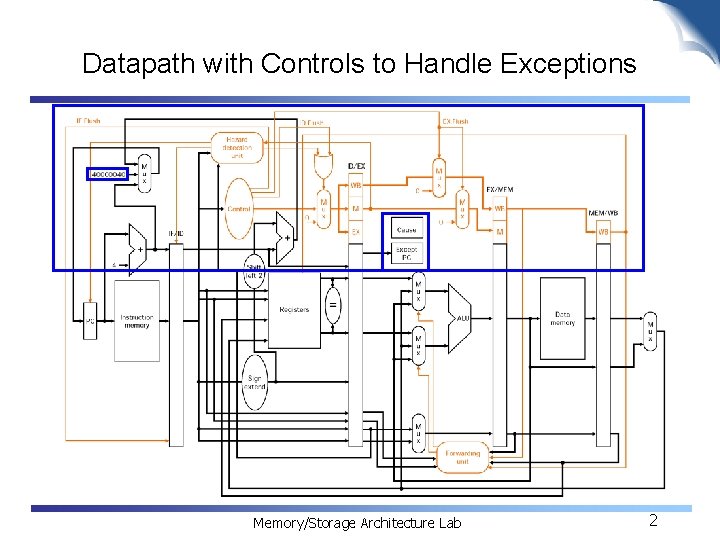

Datapath with Controls to Handle Exceptions Memory/Storage Architecture Lab 2

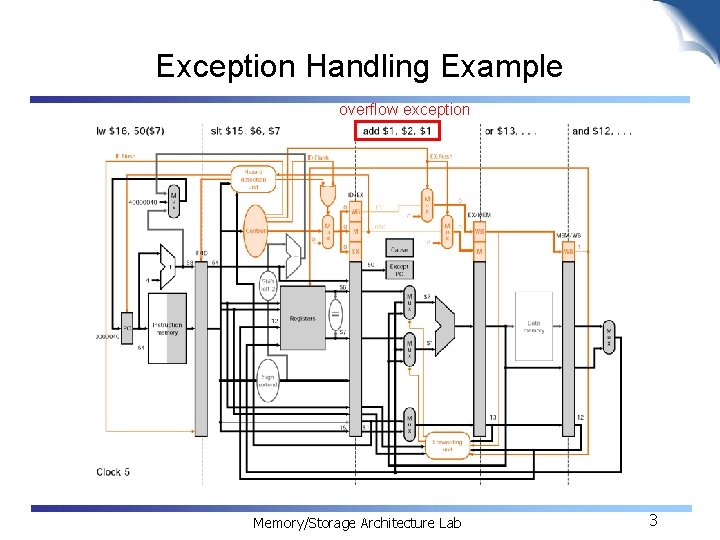

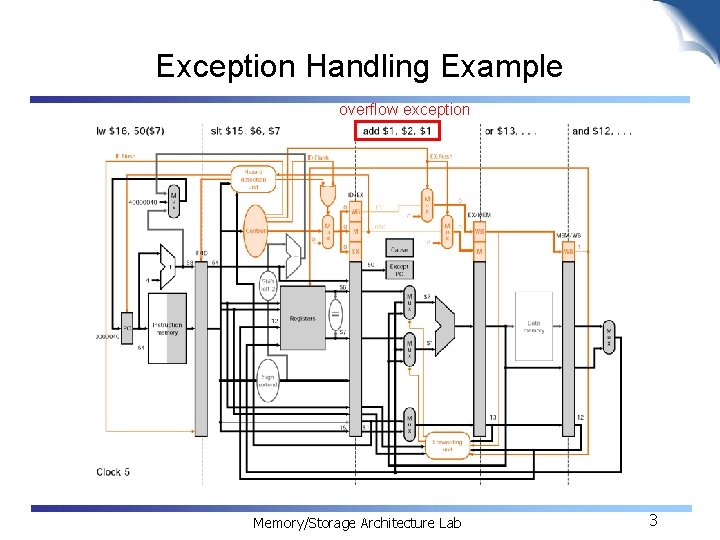

Exception Handling Example overflow exception Memory/Storage Architecture Lab 3

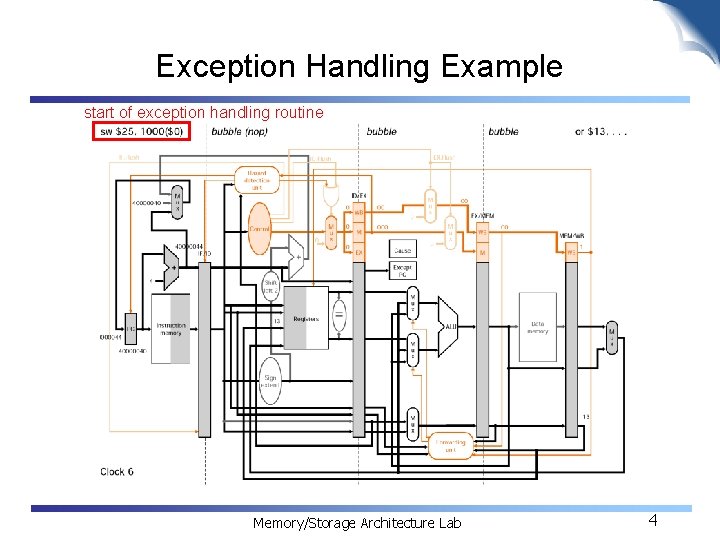

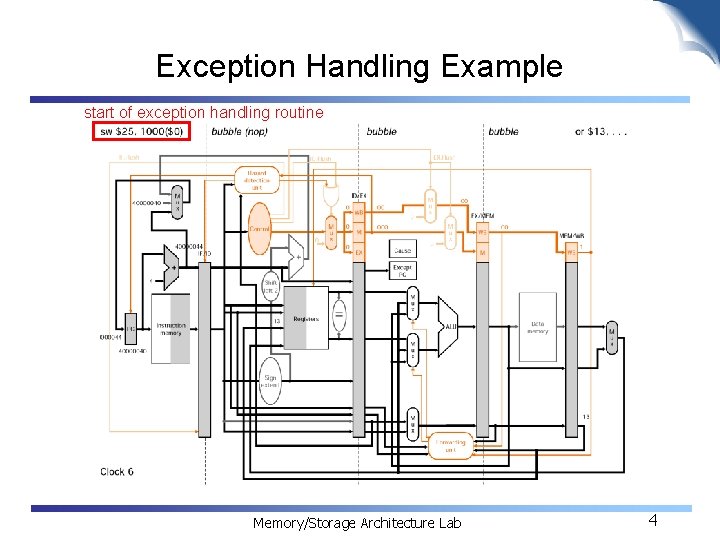

Exception Handling Example start of exception handling routine Memory/Storage Architecture Lab 4

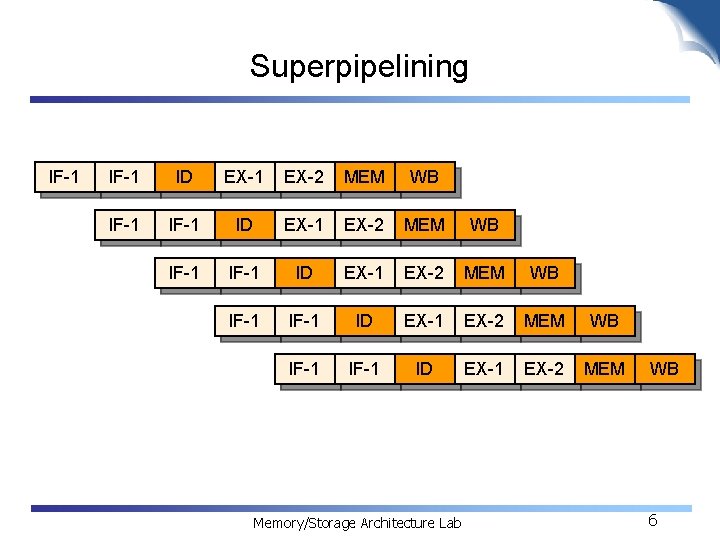

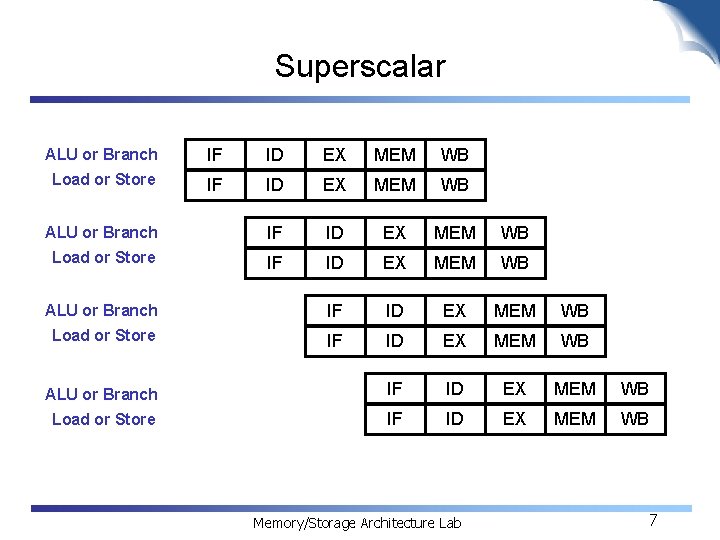

Advanced Pipelining q Superpipelining q Superscalar q Dynamic Pipeline Scheduling Memory/Storage Architecture Lab 5

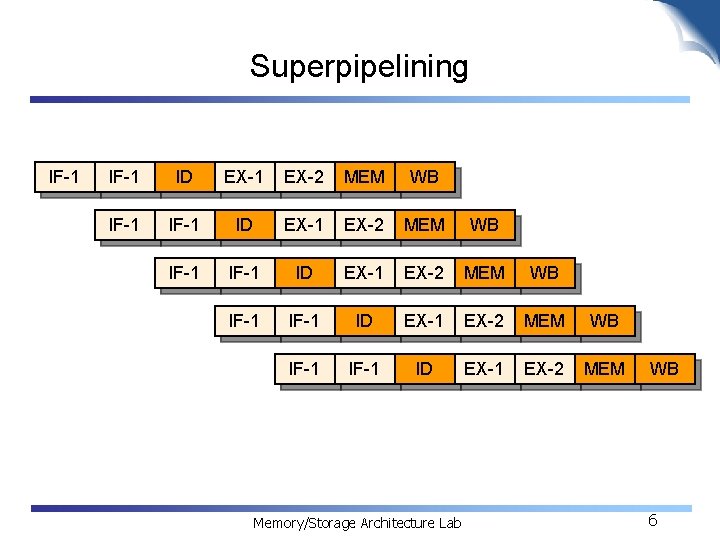

Superpipelining IF-1 IF-1 ID EX-1 EX-2 MEM WB IF-1 ID EX-1 EX-2 MEM Memory/Storage Architecture Lab WB 6

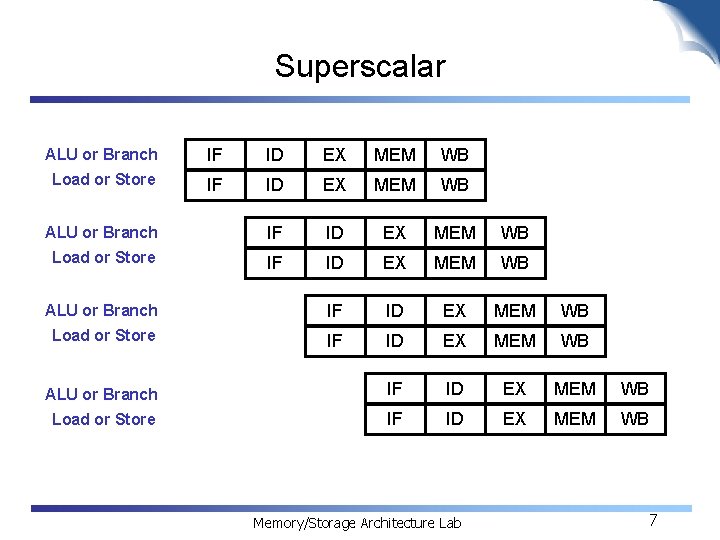

Superscalar ALU or Branch IF ID EX MEM WB Load or Store IF ID EX MEM WB Memory/Storage Architecture Lab 7

Superscalar Pipeline Memory/Storage Architecture Lab 8

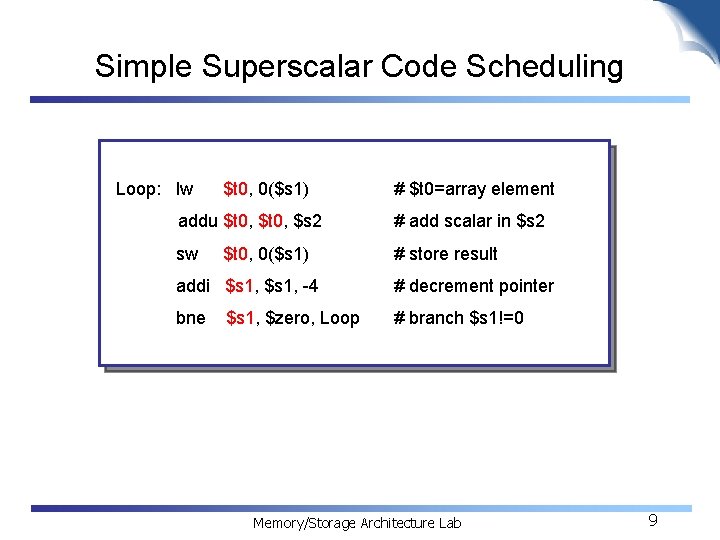

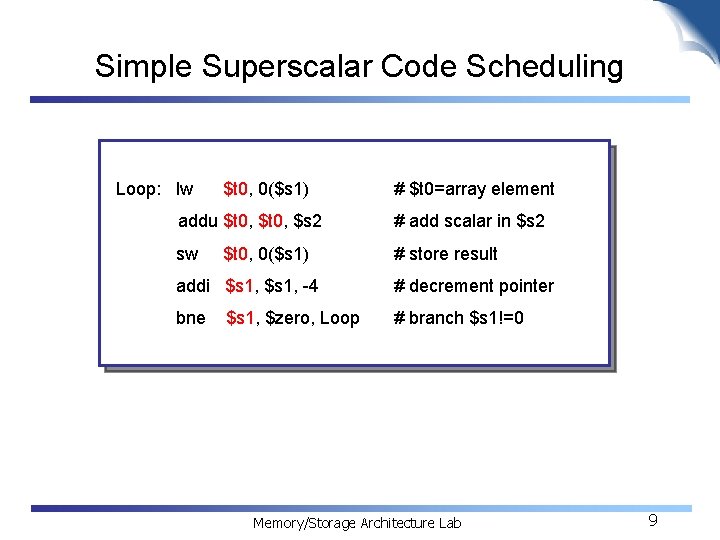

Simple Superscalar Code Scheduling Loop: lw $t 0, 0($s 1) # $t 0=array element addu $t 0, $s 2 # add scalar in $s 2 sw # store result $t 0, 0($s 1) addi $s 1, -4 # decrement pointer bne # branch $s 1!=0 $s 1, $zero, Loop Memory/Storage Architecture Lab 9

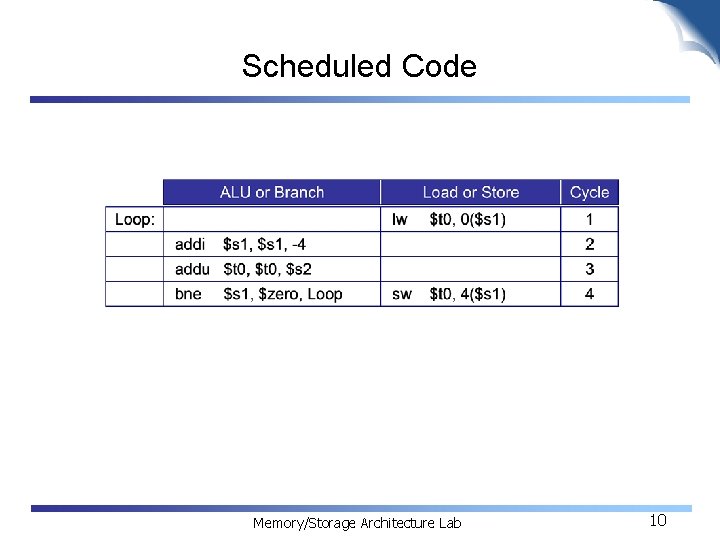

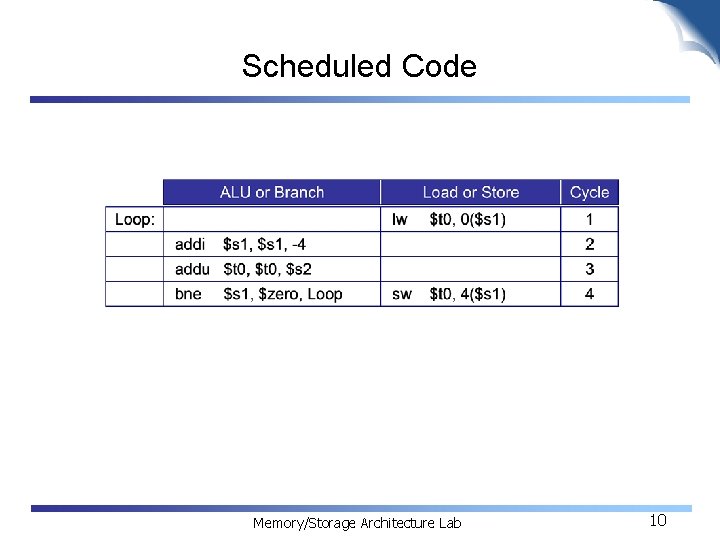

Scheduled Code Memory/Storage Architecture Lab 10

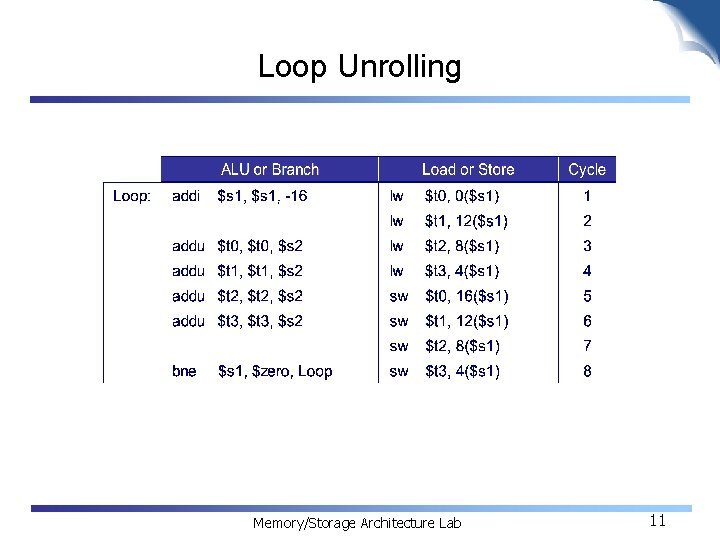

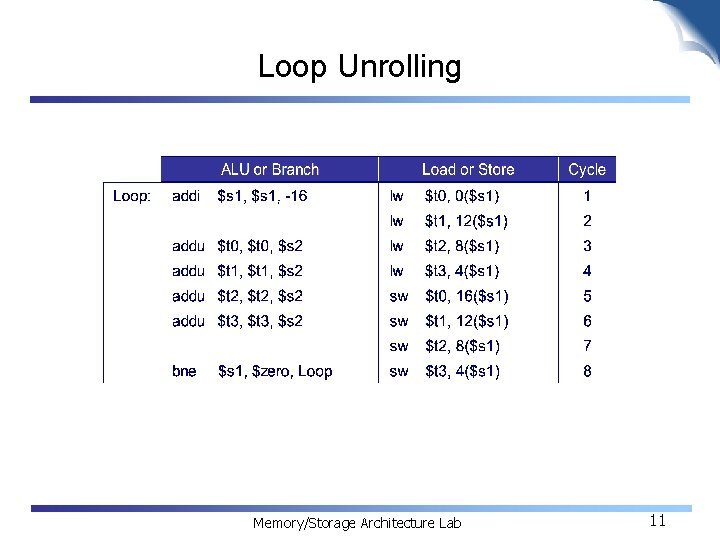

Loop Unrolling Memory/Storage Architecture Lab 11

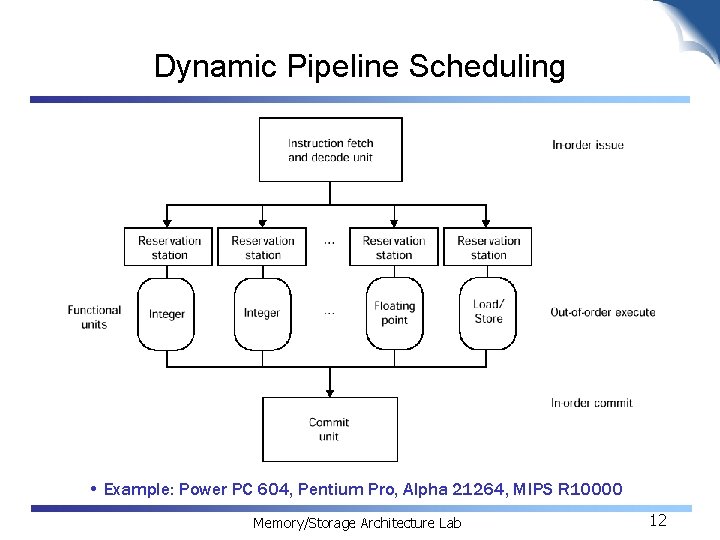

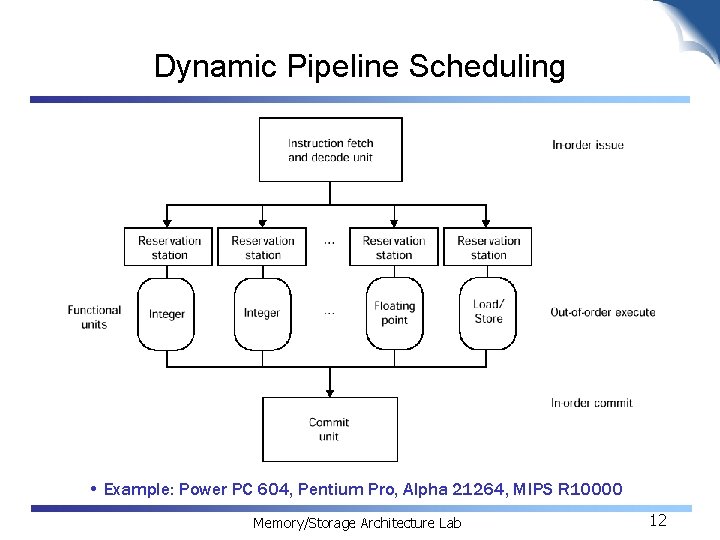

Dynamic Pipeline Scheduling • Example: Power PC 604, Pentium Pro, Alpha 21264, MIPS R 10000 Memory/Storage Architecture Lab 12

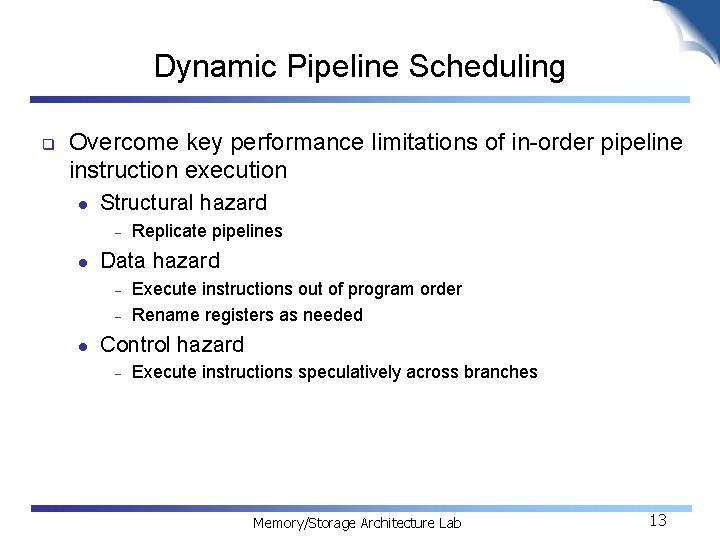

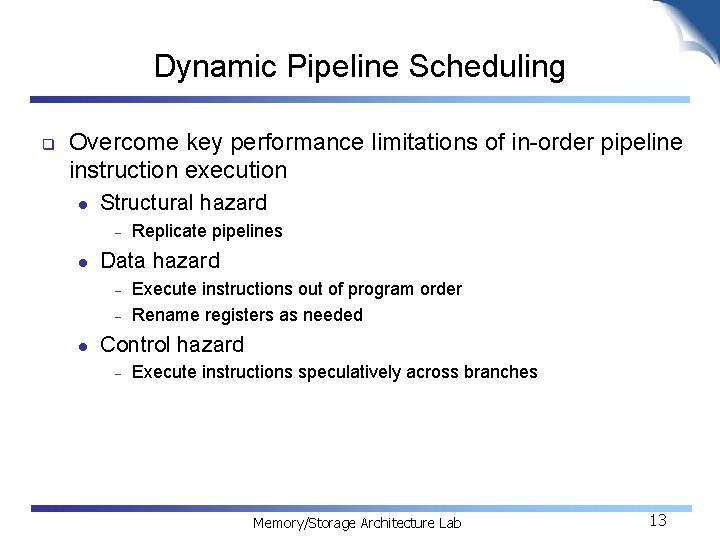

Dynamic Pipeline Scheduling q Overcome key performance limitations of in-order pipeline instruction execution l Structural hazard − l Data hazard − − l Replicate pipelines Execute instructions out of program order Rename registers as needed Control hazard − Execute instructions speculatively across branches Memory/Storage Architecture Lab 13

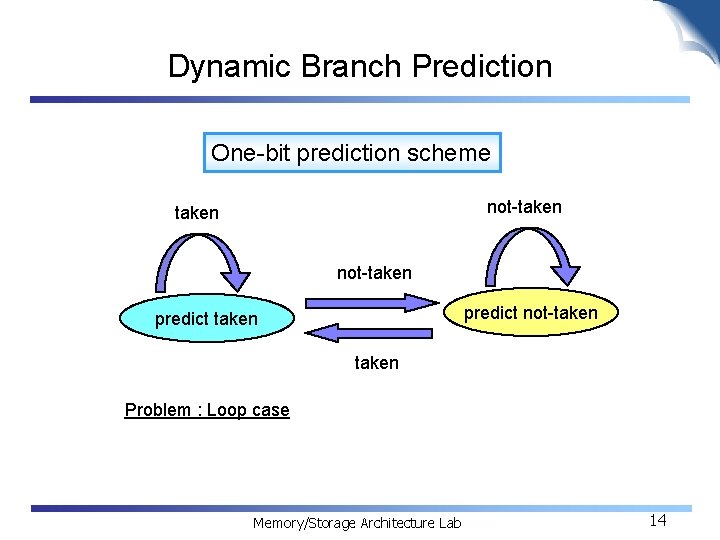

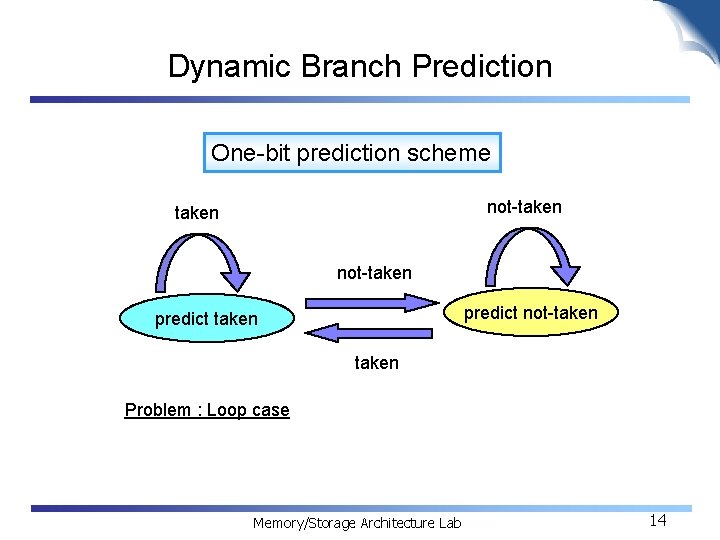

Dynamic Branch Prediction One-bit prediction scheme not-taken predict taken Problem : Loop case Memory/Storage Architecture Lab 14

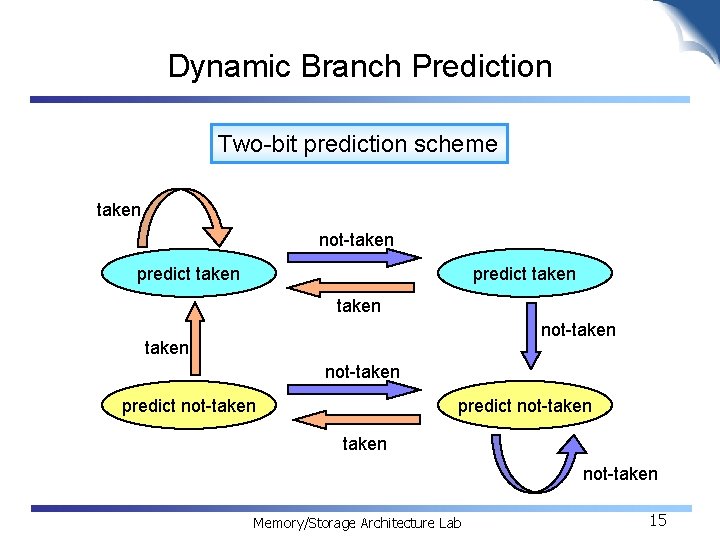

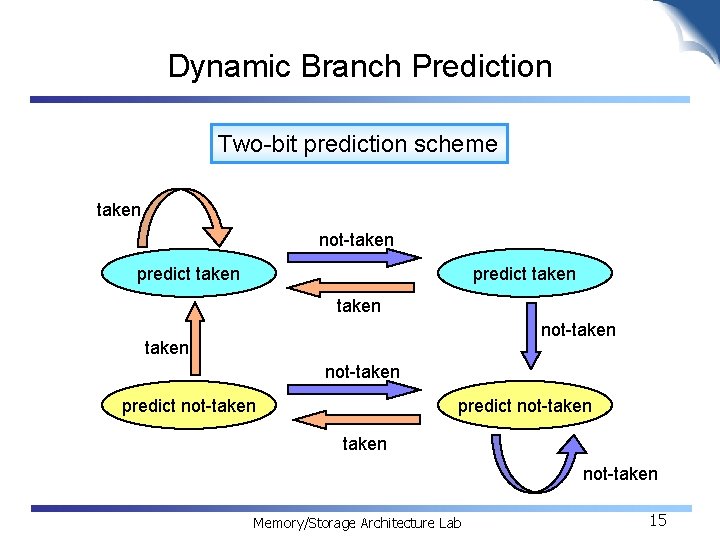

Dynamic Branch Prediction Two-bit prediction scheme taken not-taken predict taken not-taken predict not-taken Memory/Storage Architecture Lab 15

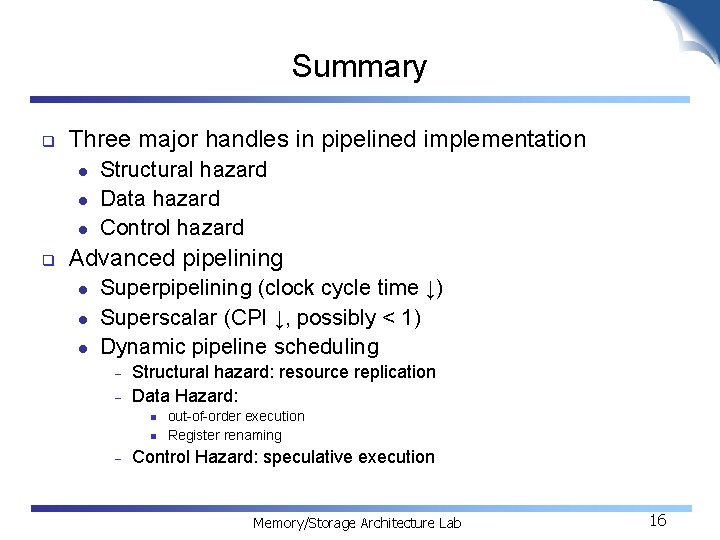

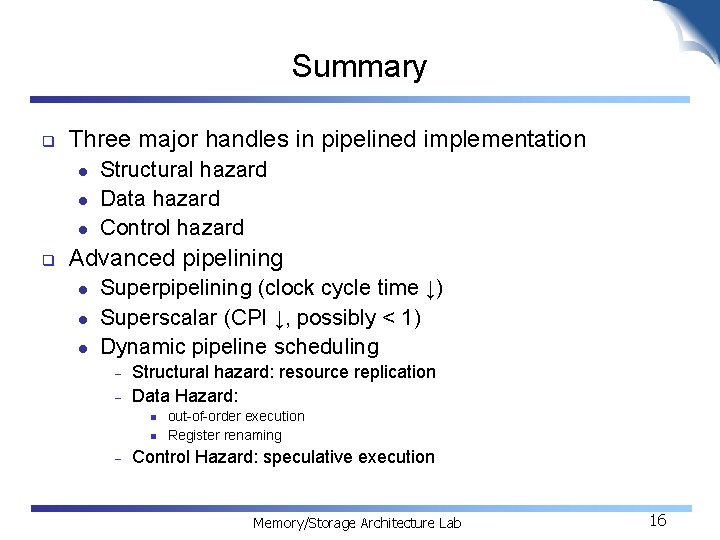

Summary q Three major handles in pipelined implementation l l l q Structural hazard Data hazard Control hazard Advanced pipelining l l l Superpipelining (clock cycle time ↓) Superscalar (CPI ↓, possibly < 1) Dynamic pipeline scheduling − − Structural hazard: resource replication Data Hazard: n n − out-of-order execution Register renaming Control Hazard: speculative execution Memory/Storage Architecture Lab 16