Computer Architecture CSE 3322 Lecture 2 Why Study

- Slides: 32

Computer Architecture CSE 3322 Lecture 2

Why Study Computer Architecture • Learn to Design Computers – Processors Designed by Few Semiconductor Companies

Why Study Computer Architecture • Learn to Design Computers – Processors Designed by Few Semiconductor Companies • Learn to Design Device Controllers

Why Study Computer Architecture • Learn to Design Computers – Processors Designed by Few Semiconductor Companies • Learn to Design Device Controllers • Learn to Design More Optimum Software!

Why Study Computer Architecture • Learn to Design Computers – Processors Designed by Few Semiconductor Companies • Learn to Design Device Controllers • Learn to Design More Optimum Software! • Learn to Design More Optimum Systems!

How to Improve Application Performance ?

How to Improve Application Performance ? • • Algorithm Language and Compiler Processor and Memory System I/O System and Devices

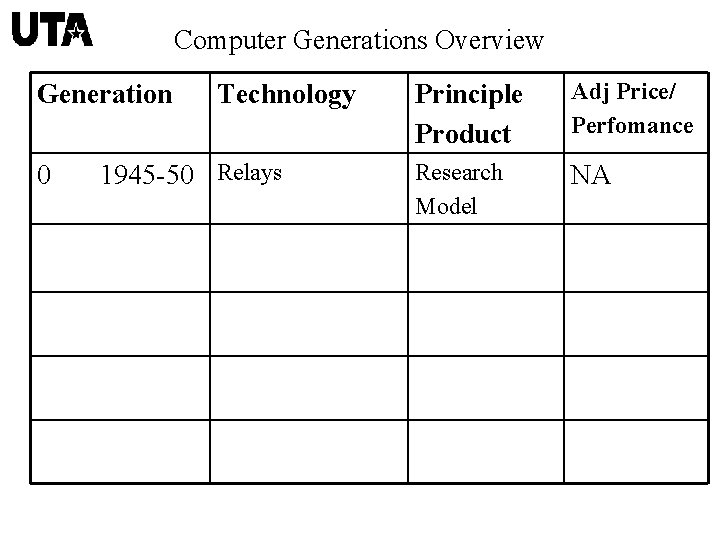

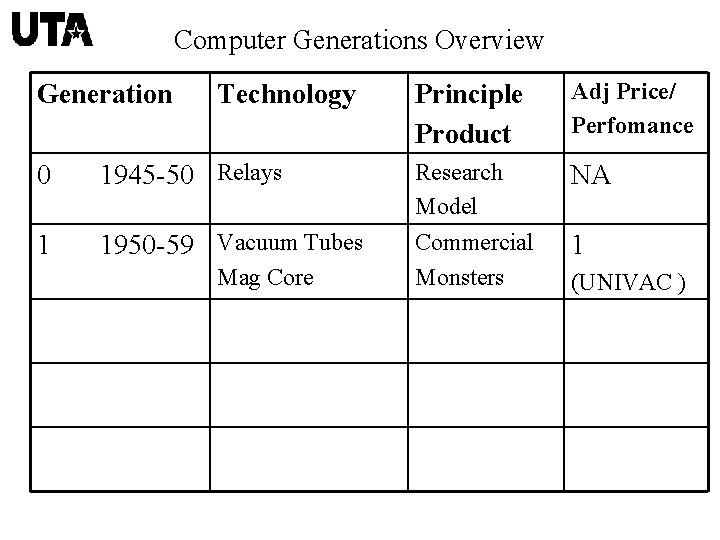

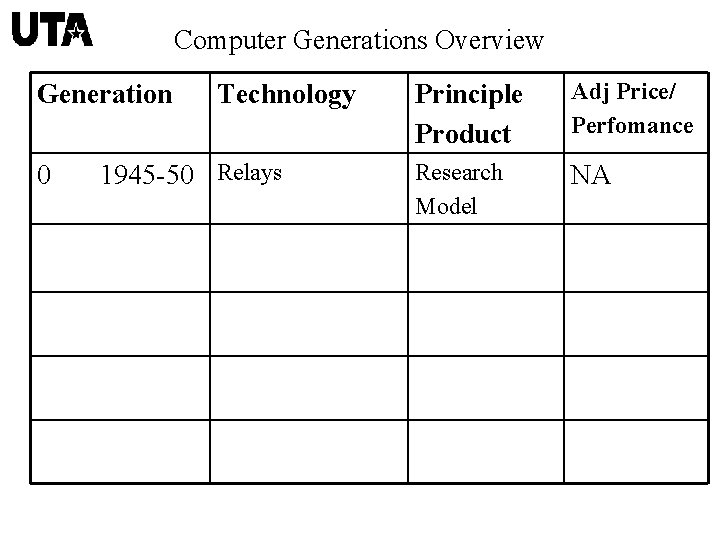

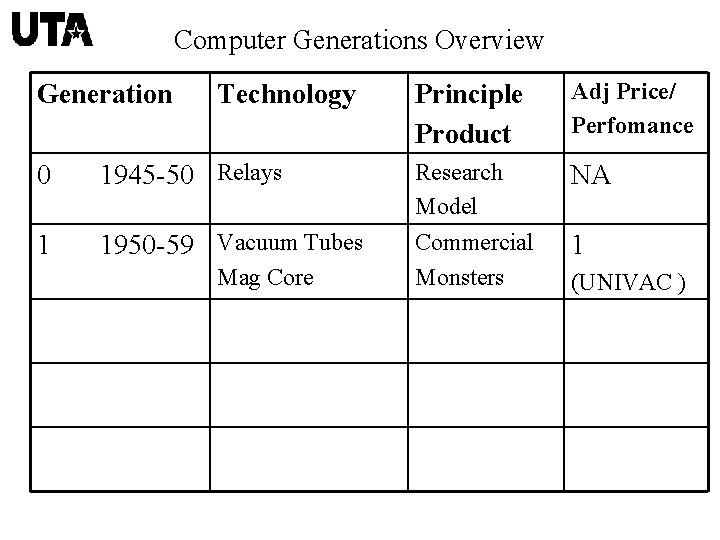

Computer Generations Overview Generation Technology 0 1945 -50 Relays Principle Product Adj Price/ Perfomance Research Model NA

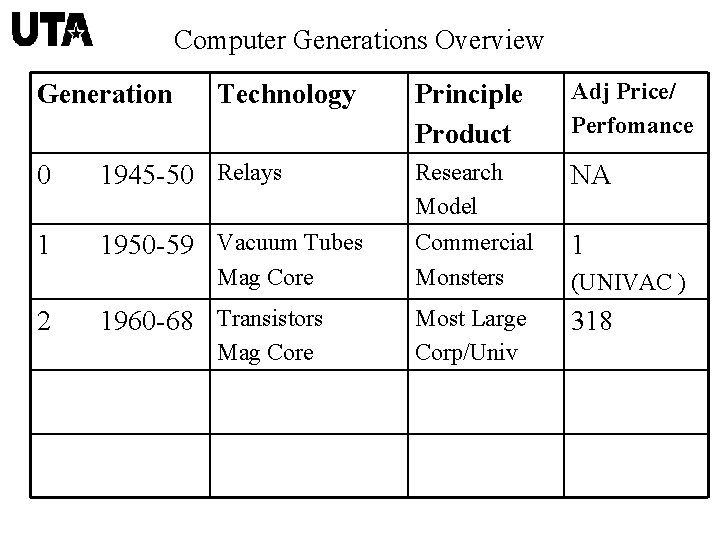

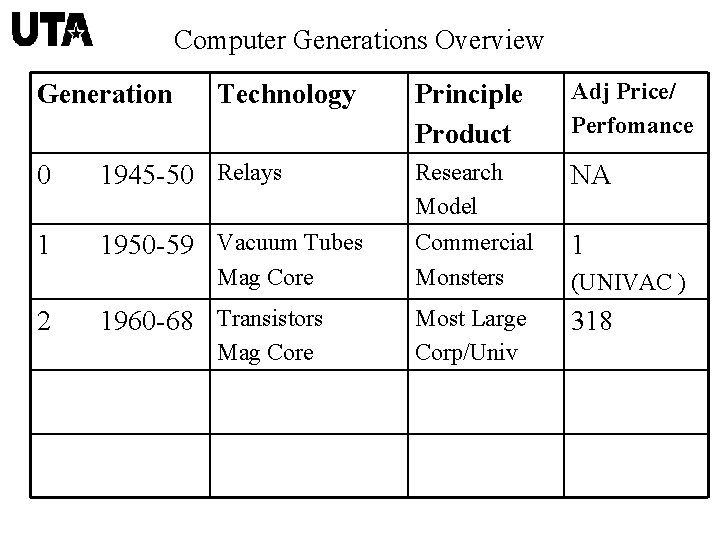

Computer Generations Overview Principle Product Adj Price/ Perfomance 0 1945 -50 Relays Research Model NA 1 1950 -59 Vacuum Tubes Commercial Monsters 1 Generation Technology Mag Core (UNIVAC )

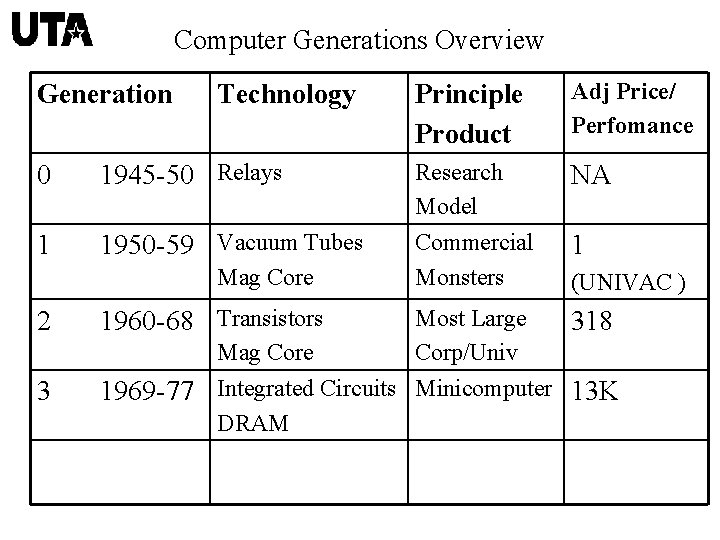

Computer Generations Overview Principle Product Adj Price/ Perfomance 0 1945 -50 Relays Research Model NA 1 1950 -59 Vacuum Tubes Commercial Monsters 1 Most Large Corp/Univ 318 Generation Technology Mag Core 2 1960 -68 Transistors Mag Core (UNIVAC )

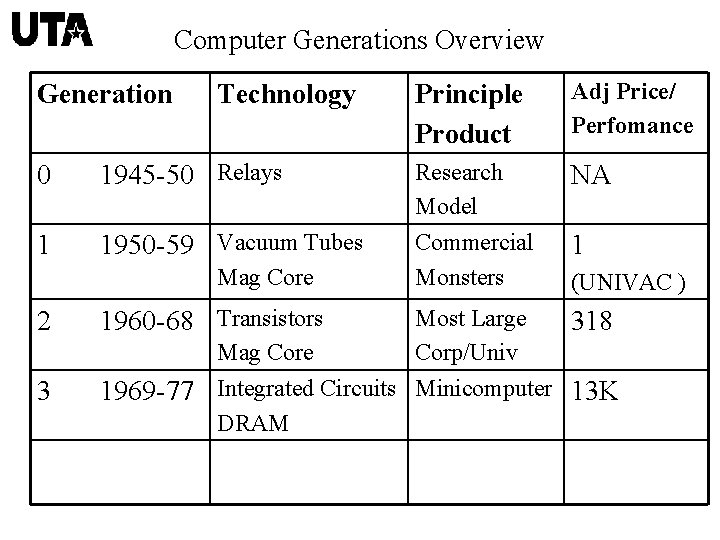

Computer Generations Overview Principle Product Adj Price/ Perfomance 0 1945 -50 Relays Research Model NA 1 1950 -59 Vacuum Tubes Commercial Monsters 1 Generation Technology Mag Core 2 1960 -68 Transistors (UNIVAC ) Most Large 318 Mag Core Corp/Univ 3 1969 -77 Integrated Circuits Minicomputer 13 K DRAM

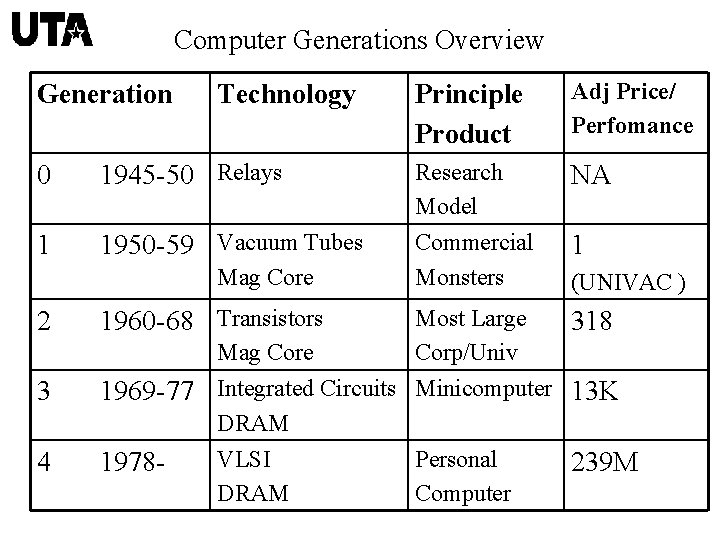

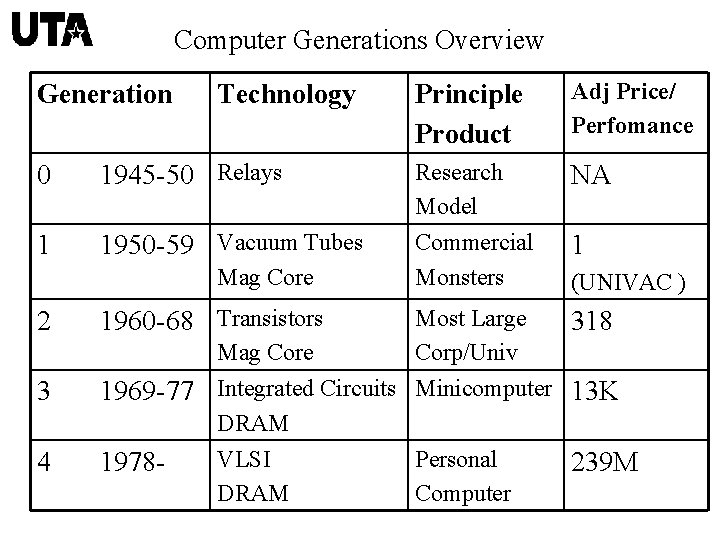

Computer Generations Overview Principle Product Adj Price/ Perfomance 0 1945 -50 Relays Research Model NA 1 1950 -59 Vacuum Tubes Commercial Monsters 1 Generation Technology Mag Core 2 1960 -68 Transistors (UNIVAC ) Most Large 318 Mag Core Corp/Univ 3 1969 -77 Integrated Circuits Minicomputer 13 K DRAM VLSI Personal 4 1978239 M DRAM Computer

Technological Growth • DRAM Growth: 4 X Capacity Every 3 Years

Technological Growth • DRAM Growth: 4 X Capacity Every 3 Years • Workstation Performance Improvement: 54% per year or 2 X every 18 months

Technological Growth • DRAM Growth: 4 X Capacity Every 3 Years • Workstation Performance Improvement: 54% per year or 2 X every 18 months • Disk Drive Growth: Capacity More than 2 x every year

Technological Growth • DRAM Growth: 4 X Capacity Every 3 Years • Workstation Performance Improvement: 54% per year or 2 X every 18 months • Disk Drive Growth: Capacity More than 2 x every year • All Continue to Drive Price /Performance Improvements

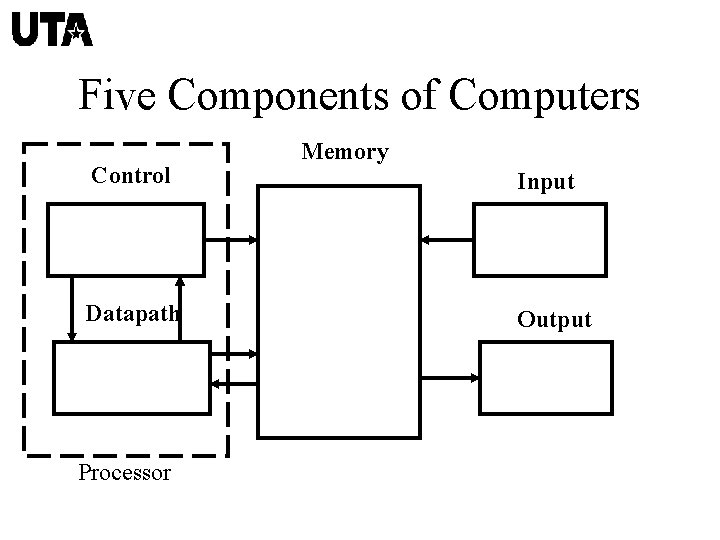

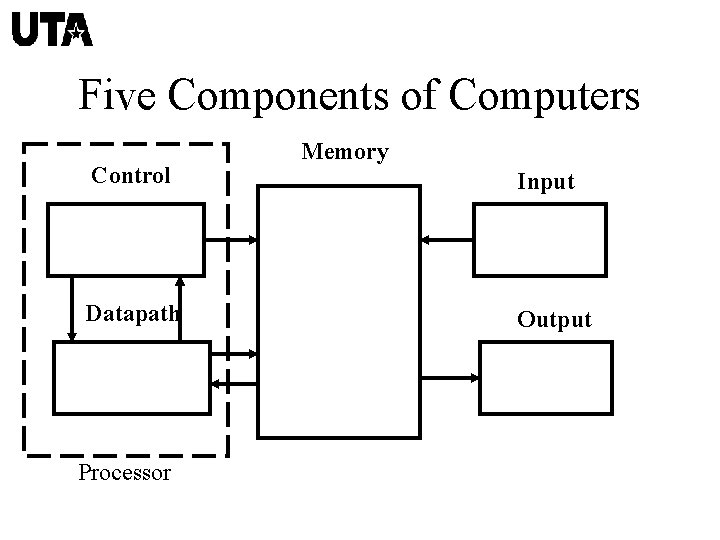

Five Components of Computers Control Datapath Processor Memory Input Output

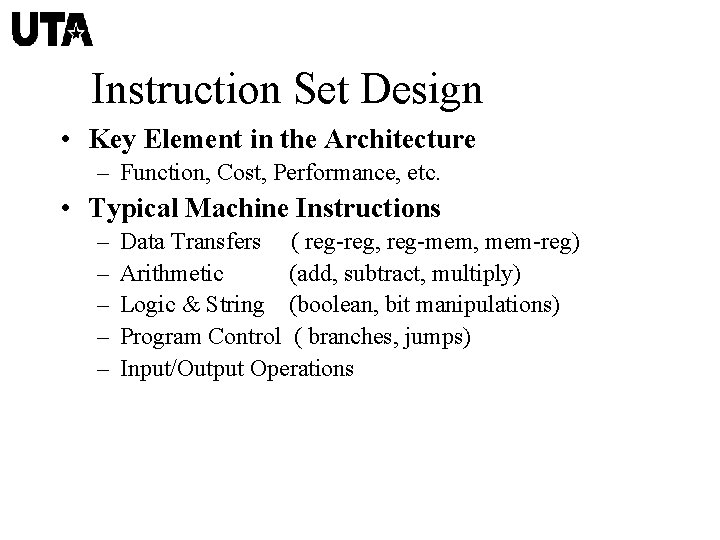

Instruction Set Design • Key Element in the Architecture – Function, Cost, Performance, etc.

Instruction Set Design • Key Element in the Architecture – Function, Cost, Performance, etc. • Typical Machine Instructions – – – Data Transfers ( reg-reg, reg-mem, mem-reg) Arithmetic (add, subtract, multiply) Logic & String (boolean, bit manipulations) Program Control ( branches, jumps) Input/Output Operations

Instruction Set Design Study the MIPS Architecture

Instruction Set Design Study the MIPS Architecture • A WORD is 32 bits or 4 bytes wide for Registers and Memory

Instruction Set Design Study the MIPS Architecture • A WORD is 32 bits or 4 bytes wide for Registers and Memory • Each byte has Memory Address starting at 0

Instruction Set Design Study the MIPS Architecture • A WORD is 32 bits or 4 bytes wide for Registers and Memory • Each byte has Memory Address starting at 0 • WORD Addresses start at 0 and are multiples of 4

Instruction Set Design Study the MIPS Architecture • A WORD is 32 bits or 4 bytes wide for Registers and Memory • Each byte has Memory Address starting at 0 • WORD Addresses start at 0 and are multiples of 4 • Big-endian Byte 0, Byte 1, Byte 2, Byte 3 • Little-endian Byte 3, Byte 2, Byte 1, Byte 0

Instruction Set Design Study the MIPS Architecture • A WORD is 32 bits or 4 bytes wide for Registers and Memory • Each byte has Memory Address starting at 0 • WORD Addresses start at 0 and are multiples of 4 • Big-endian Byte 0, Byte 1, Byte 2, Byte 3 • Little-endian Byte 3, Byte 2, Byte 1, Byte 0 • 32 Registers with Conventions on Use

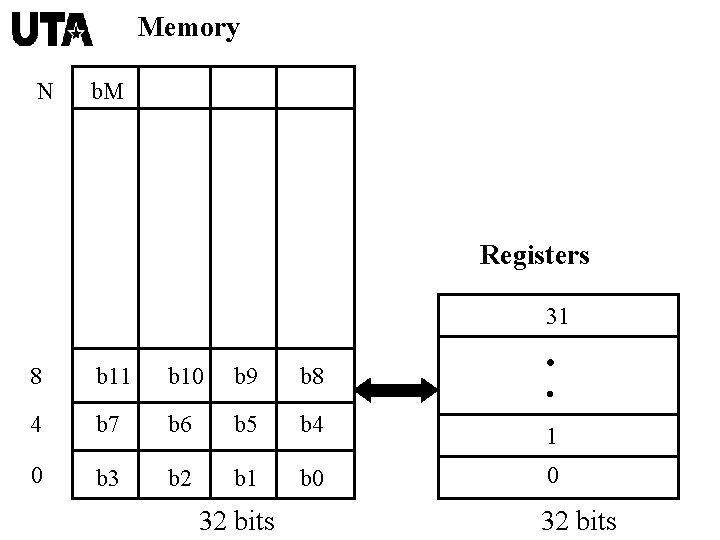

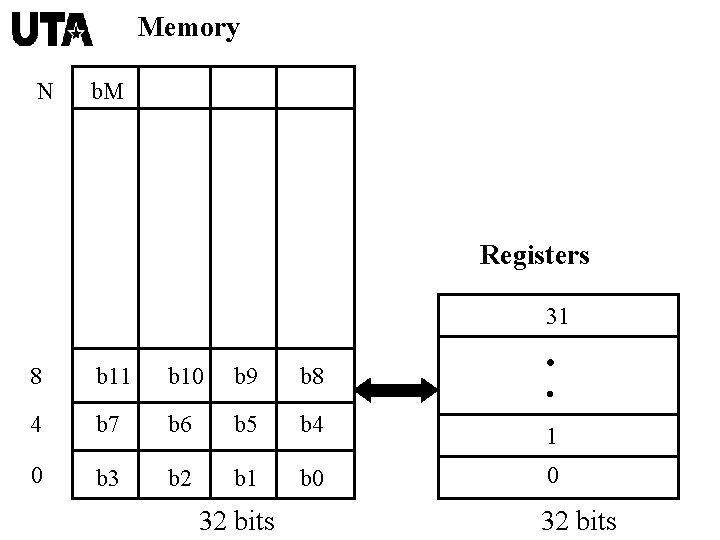

Memory N b. M Registers 31 • 8 b 11 b 10 b 9 b 8 4 b 7 b 6 b 5 b 4 1 0 b 3 b 2 b 1 b 0 0 32 bits • 32 bits

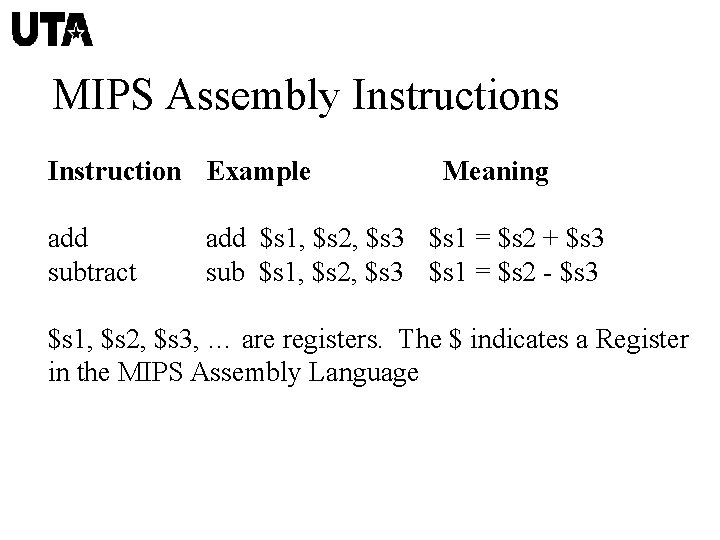

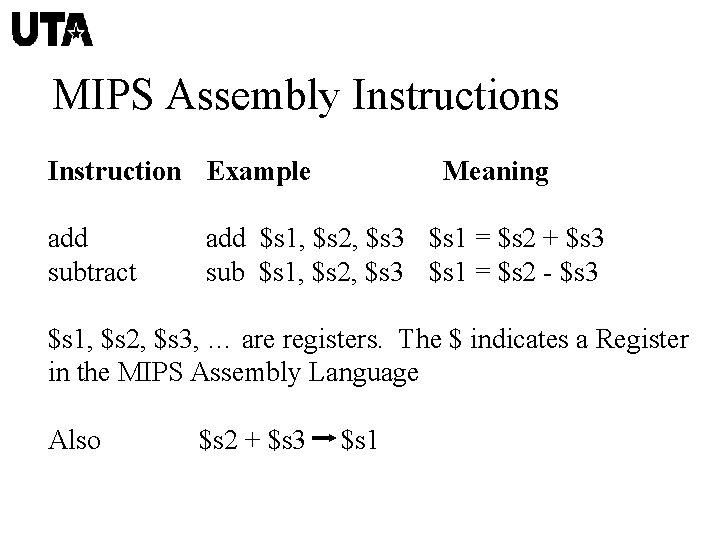

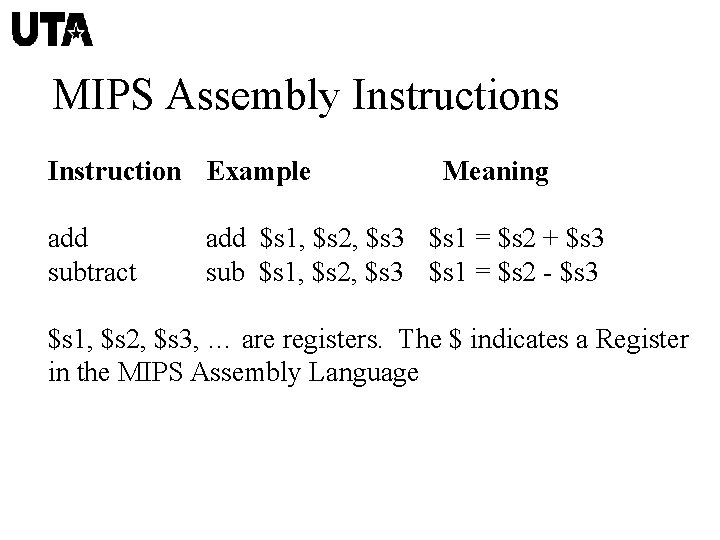

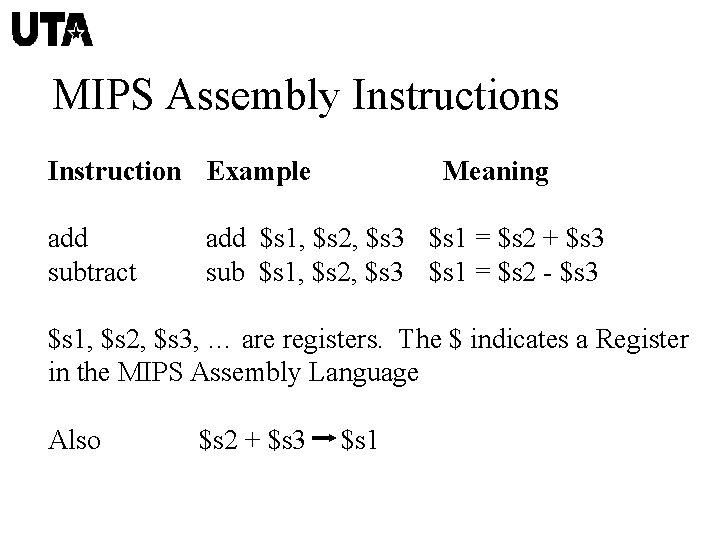

MIPS Assembly Instructions Instruction Example add subtract Meaning add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 sub $s 1, $s 2, $s 3 $s 1 = $s 2 - $s 3 $s 1, $s 2, $s 3, … are registers. The $ indicates a Register in the MIPS Assembly Language

MIPS Assembly Instructions Instruction Example add subtract Meaning add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 sub $s 1, $s 2, $s 3 $s 1 = $s 2 - $s 3 $s 1, $s 2, $s 3, … are registers. The $ indicates a Register in the MIPS Assembly Language Also $s 2 + $s 3 $s 1

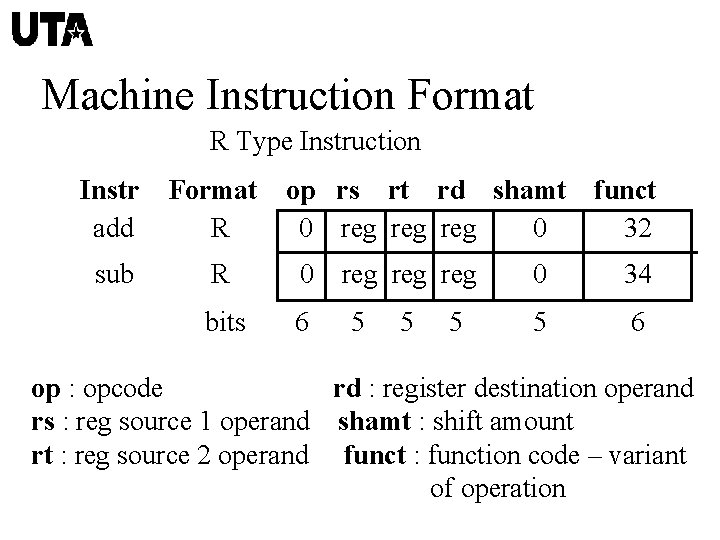

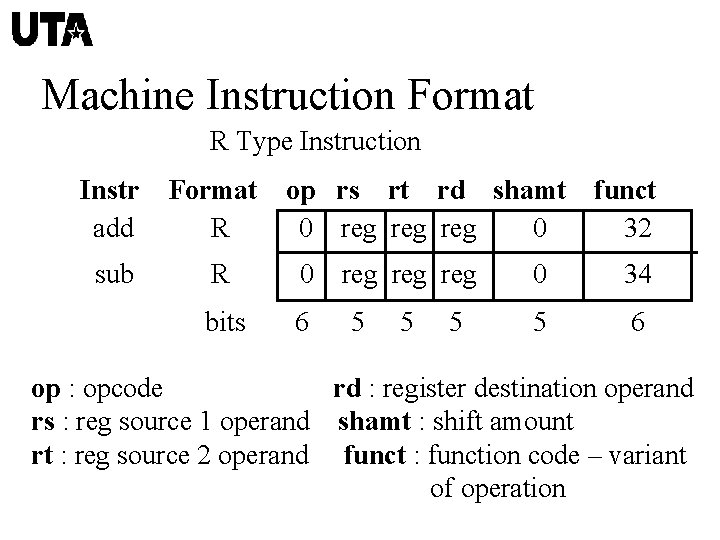

Machine Instruction Format R Type Instruction Instr Format op rs rt rd shamt funct add R 0 reg reg 0 32 sub R 0 reg reg 0 34 bits 6 5 5 5 6 op : opcode rd : register destination operand rs : reg source 1 operand shamt : shift amount rt : reg source 2 operand funct : function code – variant of operation

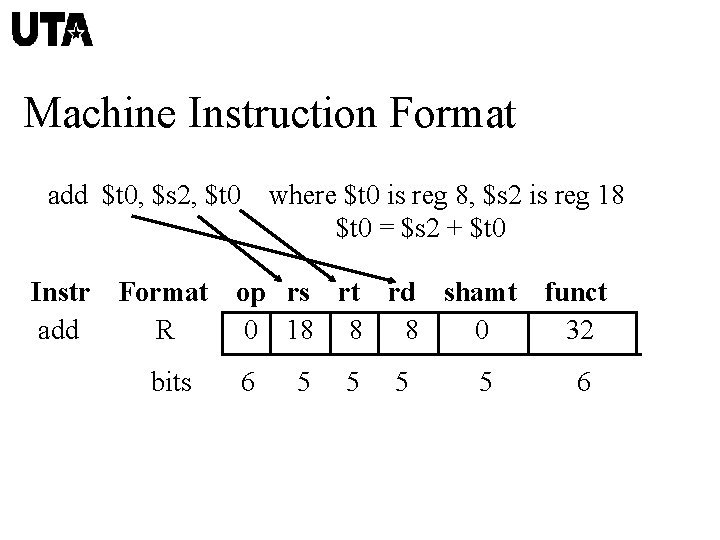

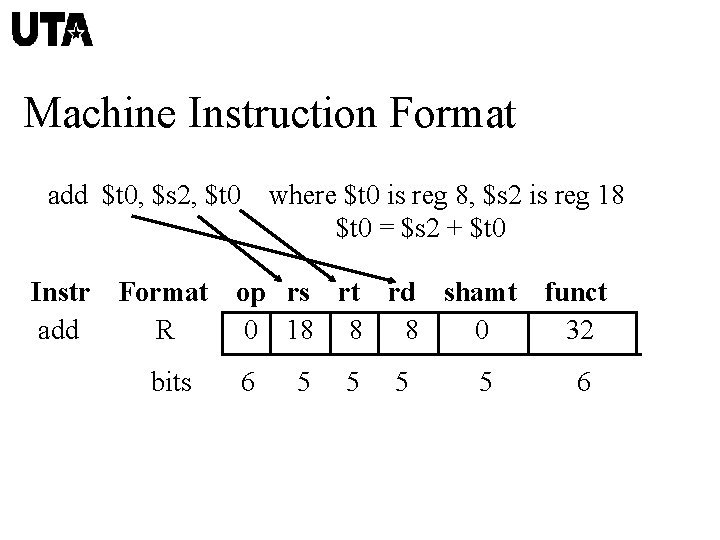

Machine Instruction Format add $t 0, $s 2, $t 0 where $t 0 is reg 8, $s 2 is reg 18 $t 0 = $s 2 + $t 0 Instr Format op rs rt rd shamt funct add R 0 18 8 8 0 32 bits 6 5 5 5 6

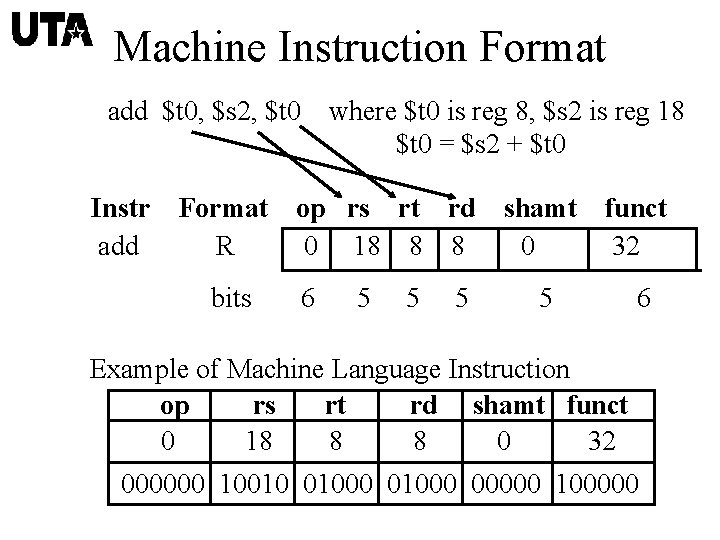

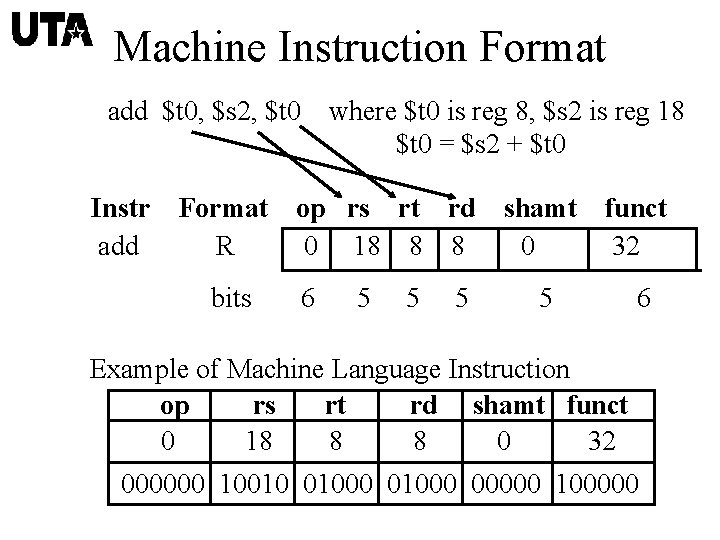

Machine Instruction Format add $t 0, $s 2, $t 0 where $t 0 is reg 8, $s 2 is reg 18 $t 0 = $s 2 + $t 0 Instr Format op rs rt rd shamt funct add R 0 18 8 8 0 32 bits 6 5 5 5 6 Example of Machine Language Instruction op rs rt rd shamt funct 0 18 8 0 32 000000 10010 01000 00000 100000