Computer Architecture and the FetchExecute Cycle Memory Addressing

- Slides: 53

Computer Architecture and the Fetch-Execute Cycle Memory Addressing Techniques

Learning Objectives Explain the concepts of direct, indexed, relative addressing and immediate addressing of memory when referring to low-level languages.

Memory Addressing Techniques 1. Direct Addressing 2. Indirect Addressing 3. Indexed Addressing 4. Relative Addressing 5. Immediate Addressing

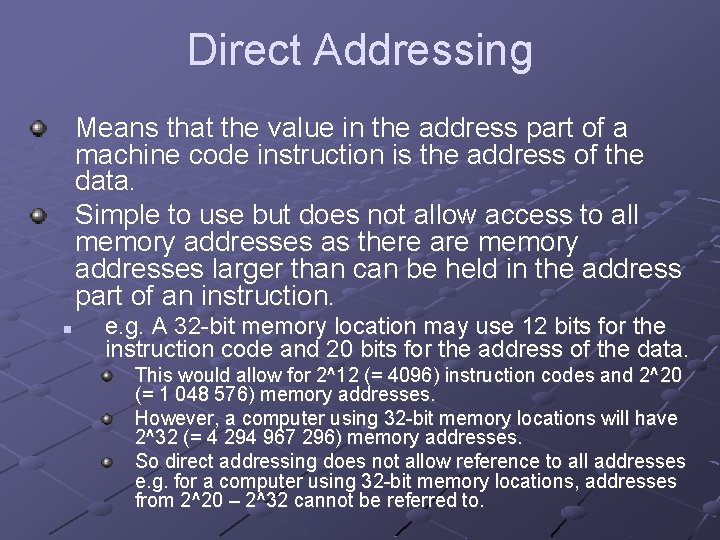

1. Direct Addressing

Direct Addressing Means that the value in the address part of a machine code instruction is the address of the data. Simple to use but does not allow access to all memory addresses as there are memory addresses larger than can be held in the address part of an instruction. n e. g. A 32 -bit memory location may use 12 bits for the instruction code and 20 bits for the address of the data. This would allow for 2^12 (= 4096) instruction codes and 2^20 (= 1 048 576) memory addresses. However, a computer using 32 -bit memory locations will have 2^32 (= 4 294 967 296) memory addresses. So direct addressing does not allow reference to all addresses e. g. for a computer using 32 -bit memory locations, addresses from 2^20 – 2^32 cannot be referred to.

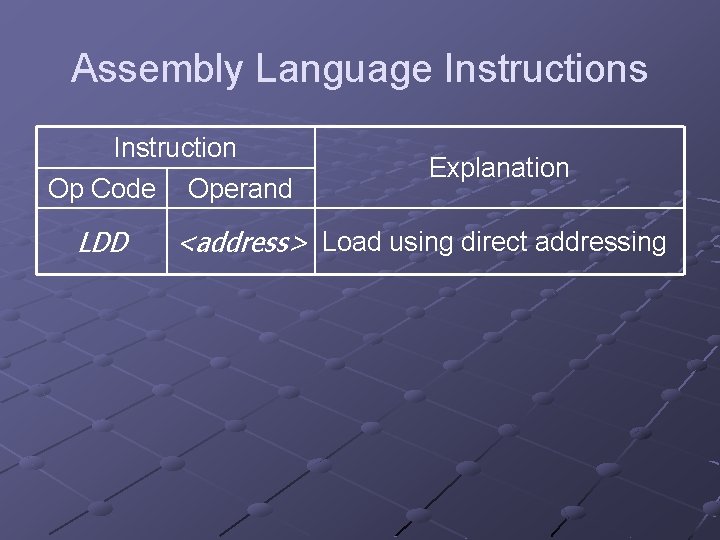

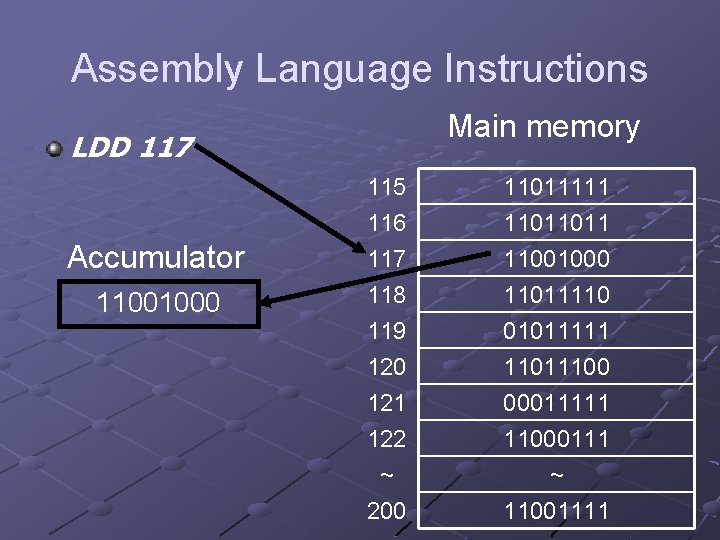

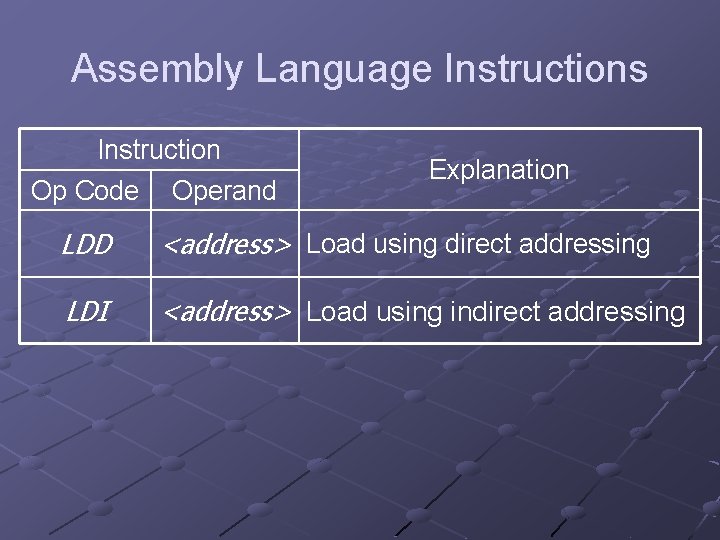

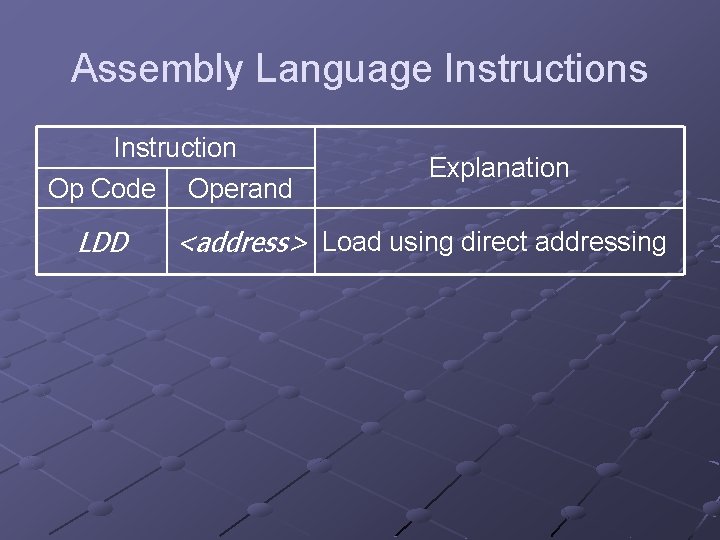

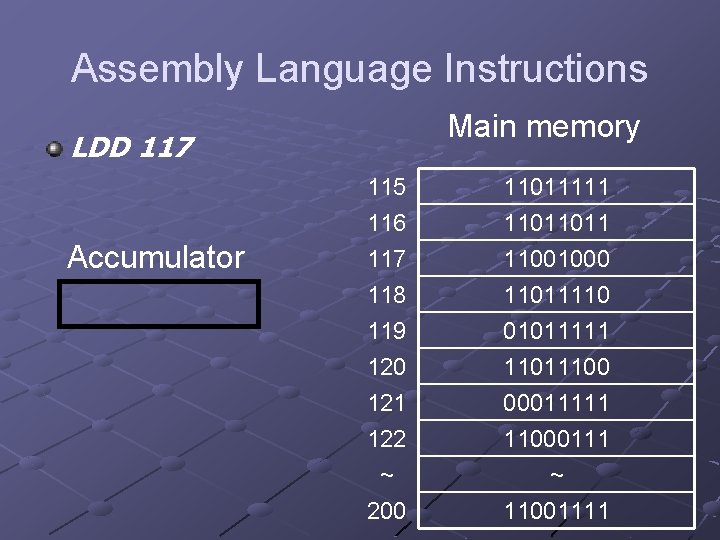

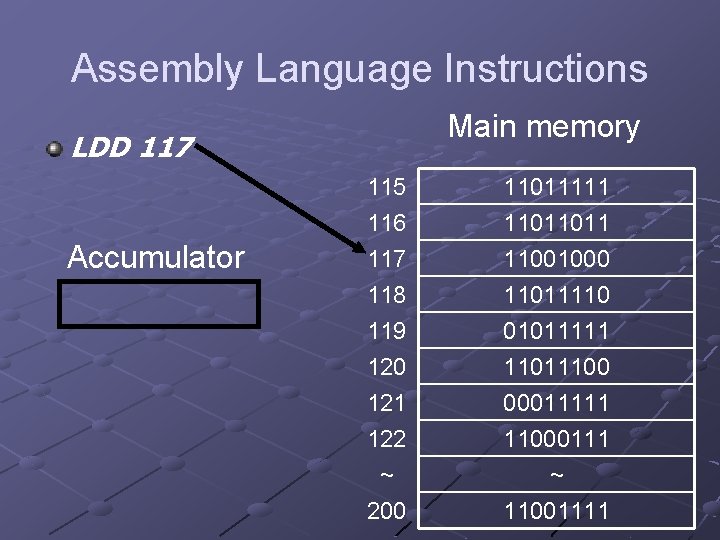

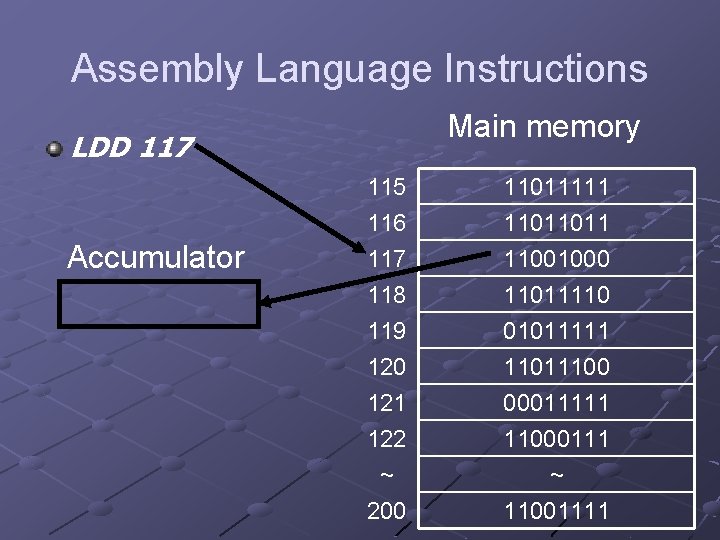

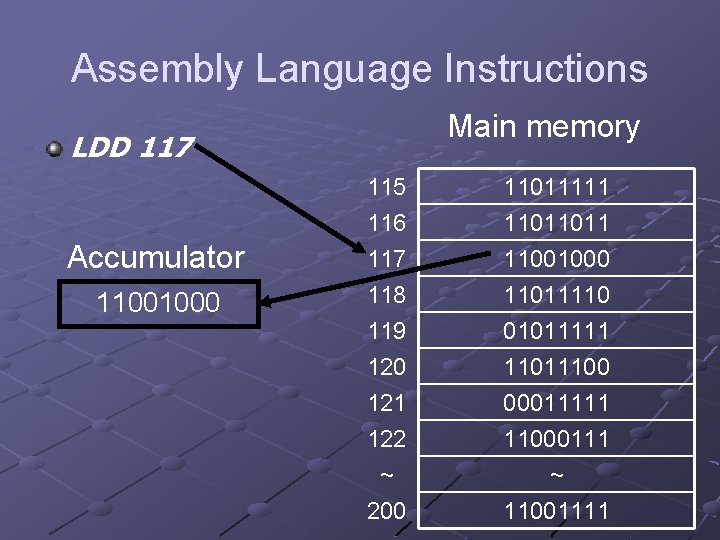

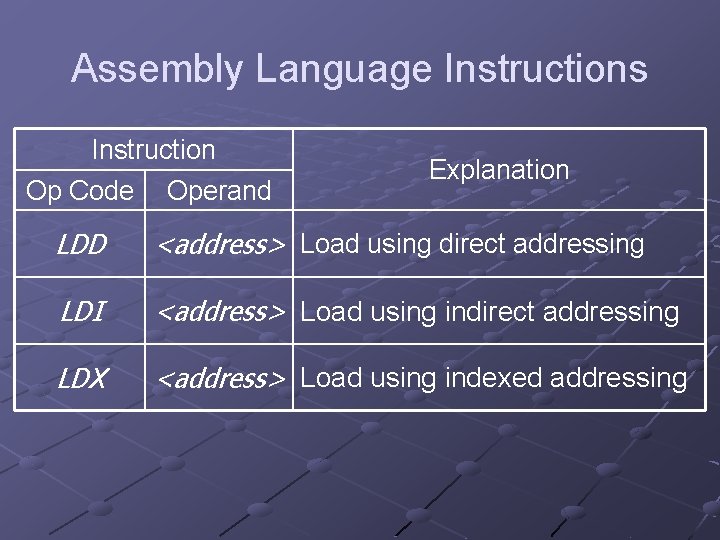

Assembly Language Instructions Instruction Op Code LDD Operand Explanation <address> Load using direct addressing

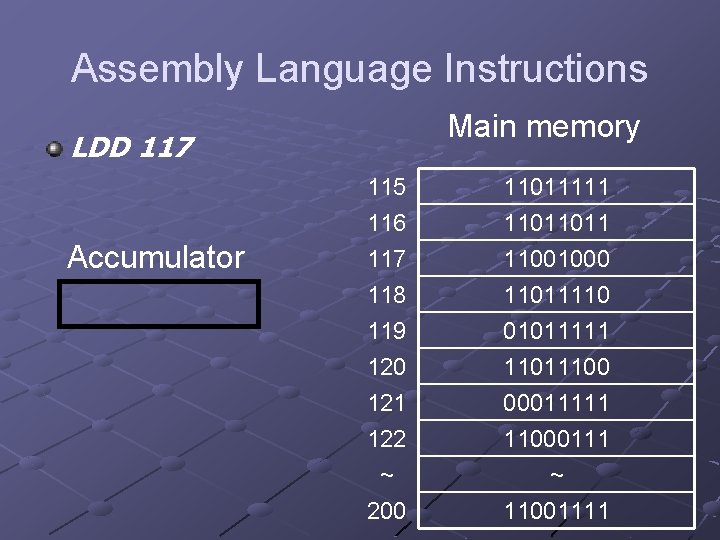

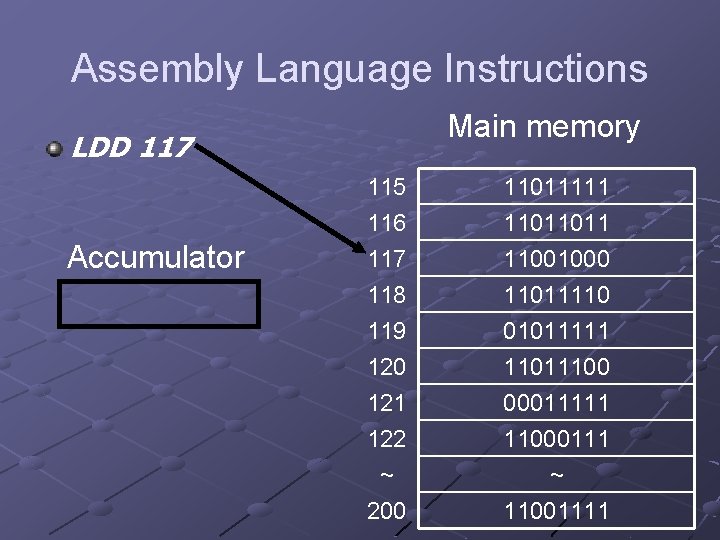

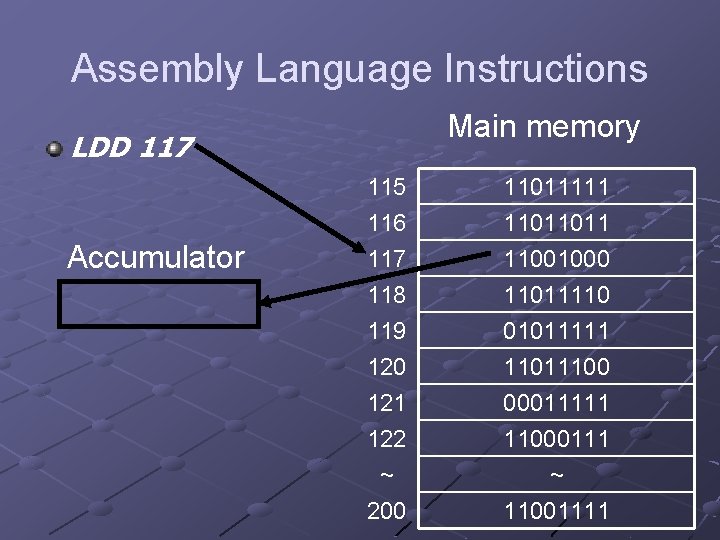

Assembly Language Instructions Main memory LDD 117 Accumulator 115 116 117 118 11011111 11011011 11001000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDD 117 Accumulator 115 116 117 118 11011111 11011011 11001000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDD 117 Accumulator 115 116 117 118 11011111 11011011 11001000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDD 117 Accumulator 11001000 115 116 117 118 11011111 11011011 11001000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

2. Indirect Addressing

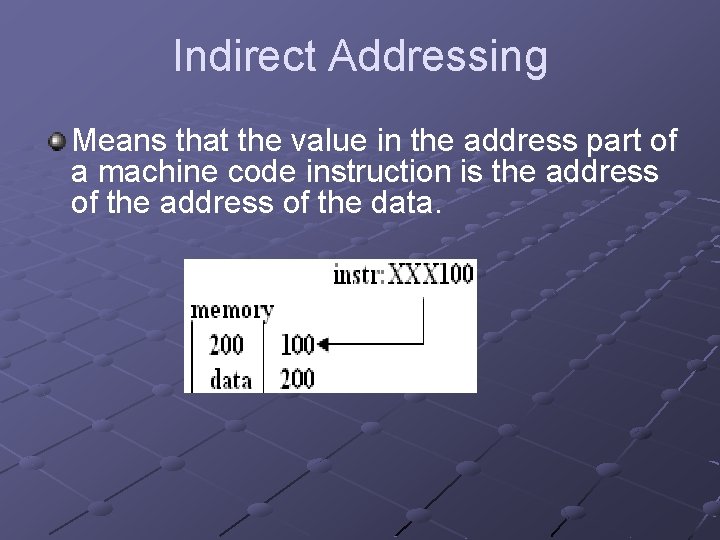

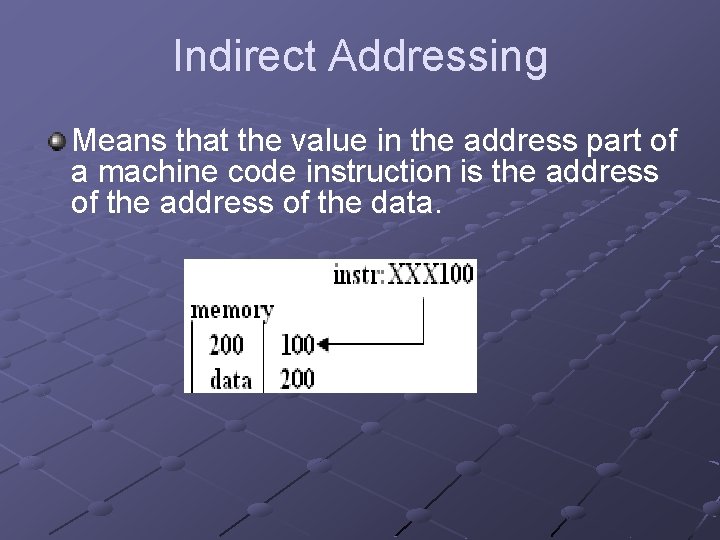

Indirect Addressing Means that the value in the address part of a machine code instruction is the address of the data.

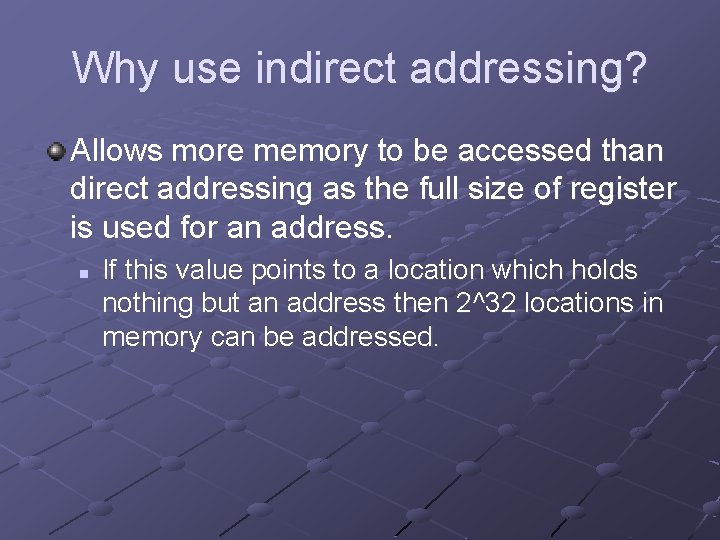

Why use indirect addressing? Allows more memory to be accessed than direct addressing as the full size of register is used for an address. n If this value points to a location which holds nothing but an address then 2^32 locations in memory can be addressed.

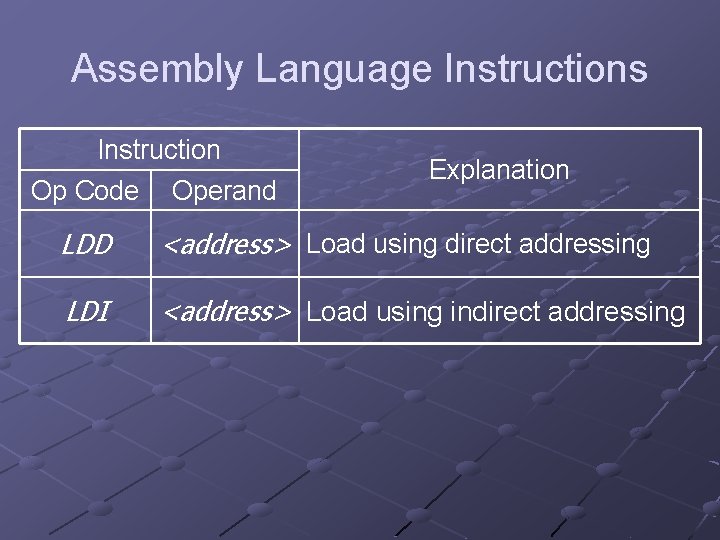

Assembly Language Instructions Instruction Op Code Operand Explanation LDD <address> Load using direct addressing LDI <address> Load using indirect addressing

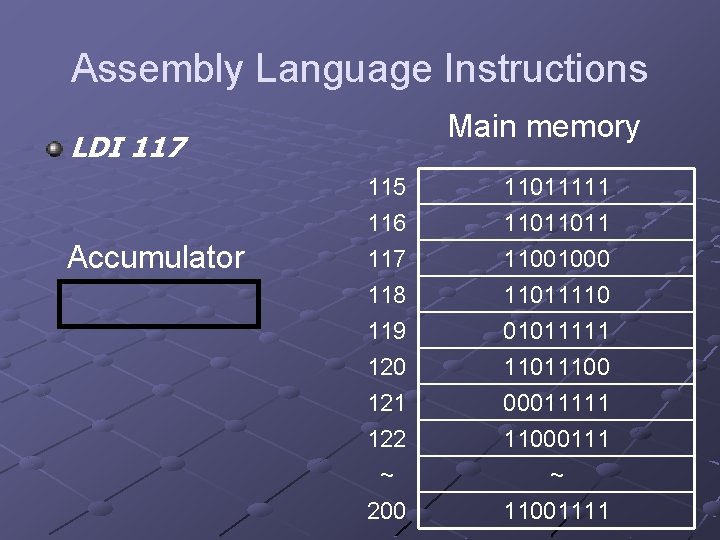

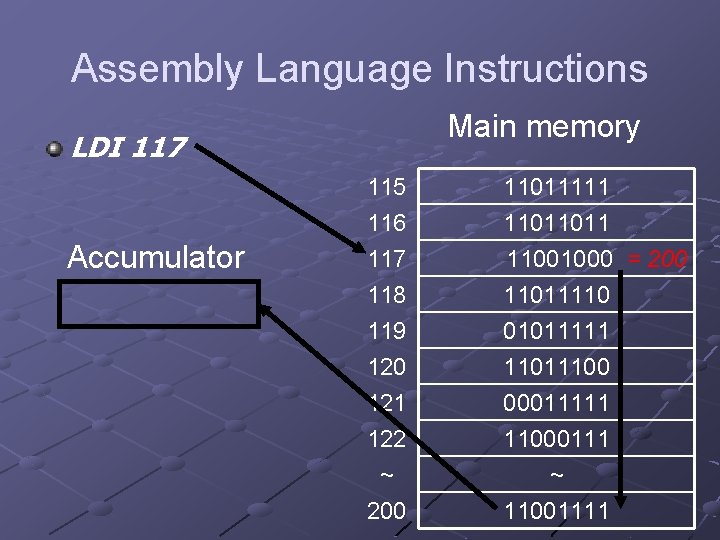

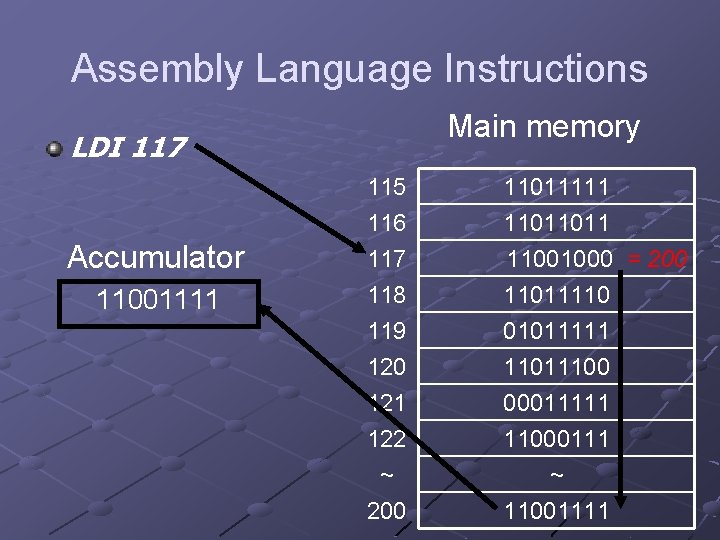

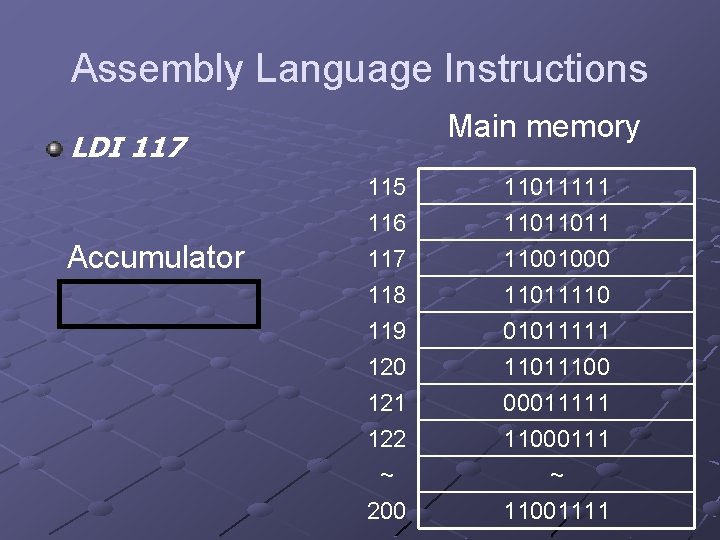

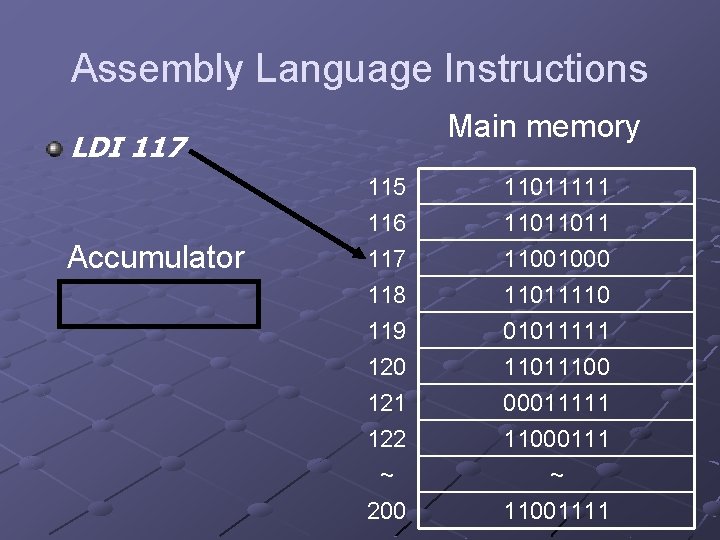

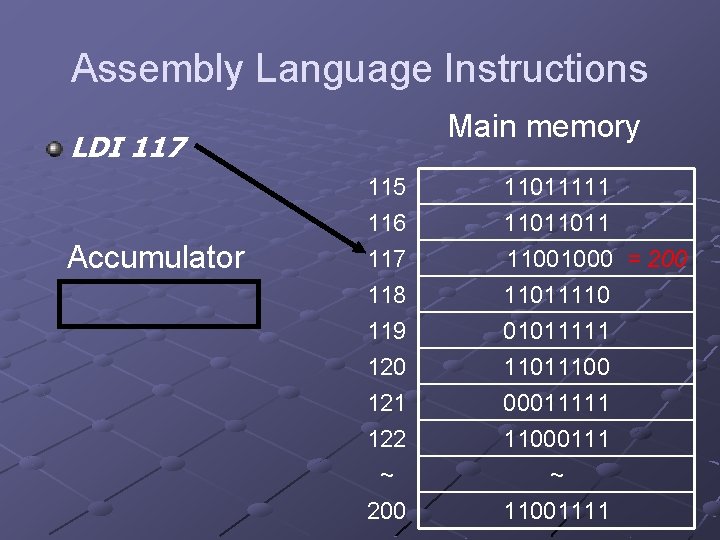

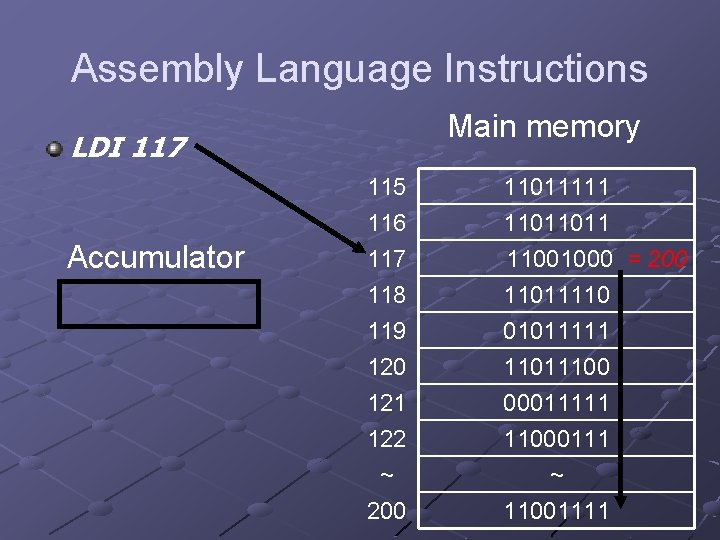

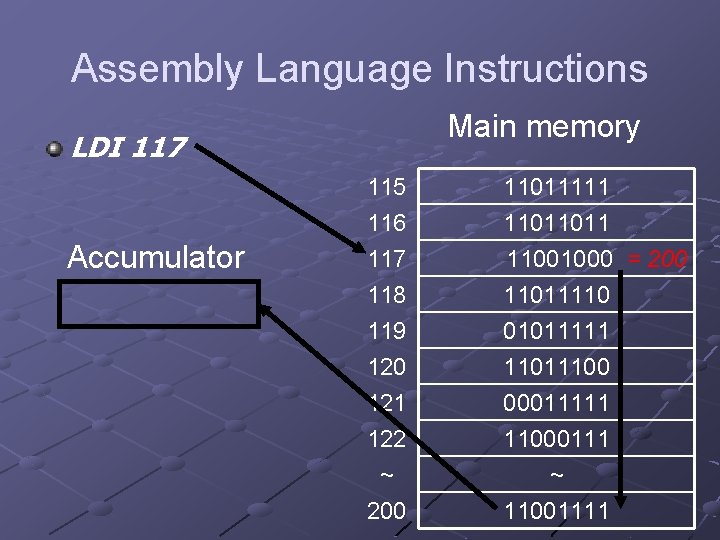

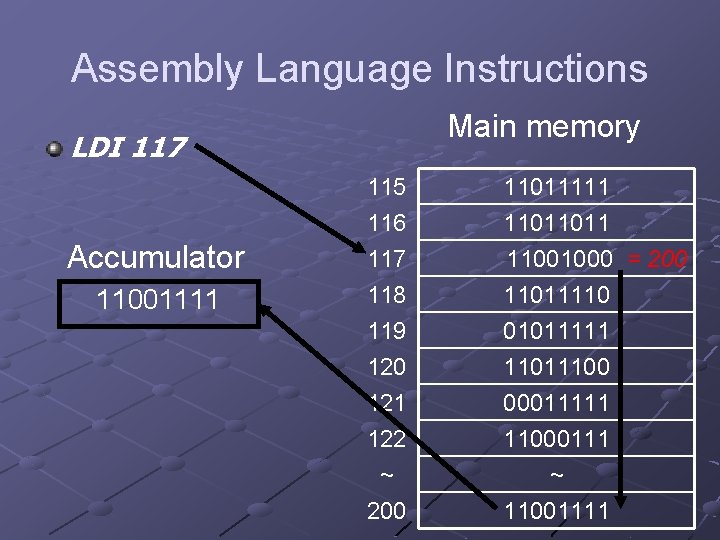

Assembly Language Instructions Main memory LDI 117 Accumulator 115 116 117 118 11011111 11011011 11001000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

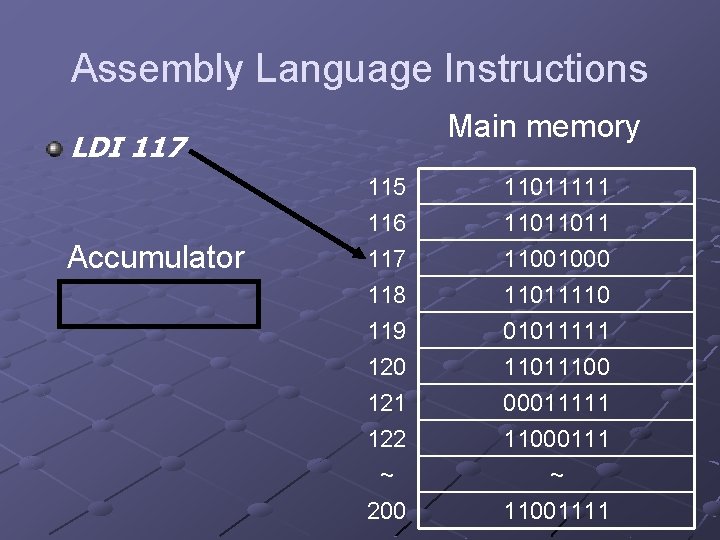

Assembly Language Instructions Main memory LDI 117 Accumulator 115 116 117 118 11011111 11011011 11001000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

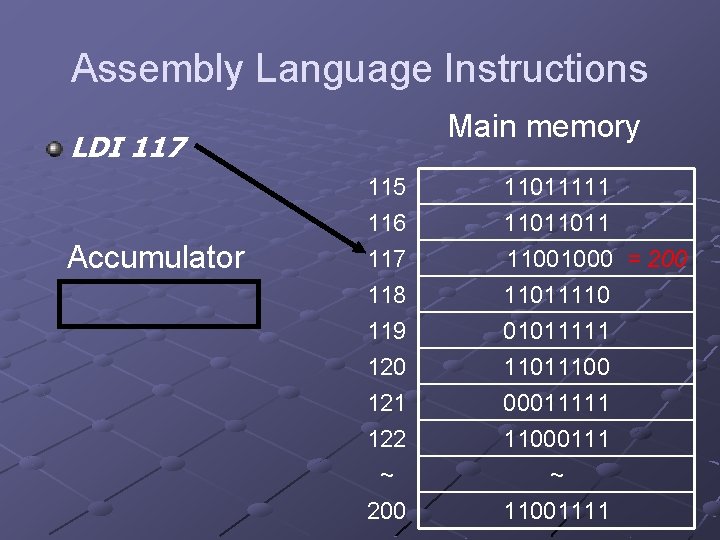

Assembly Language Instructions Main memory LDI 117 Accumulator 115 116 117 118 11011111 11011011 11001000 = 200 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

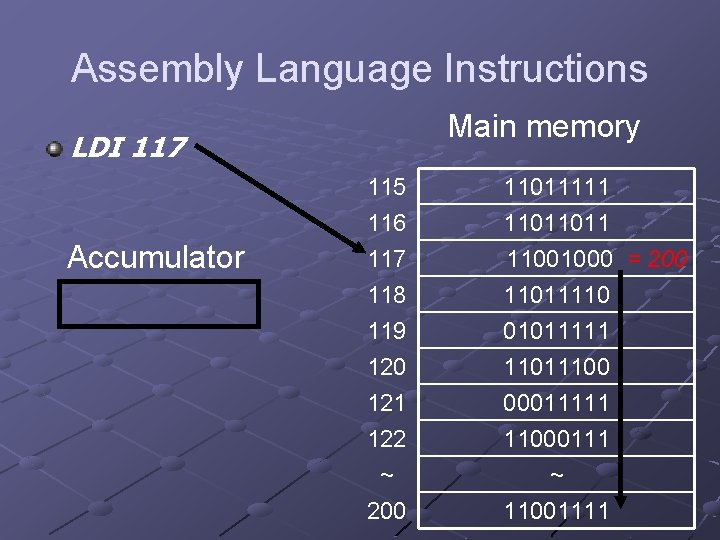

Assembly Language Instructions Main memory LDI 117 Accumulator 115 116 117 118 11011111 11011011 11001000 = 200 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDI 117 Accumulator 115 116 117 118 11011111 11011011 11001000 = 200 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDI 117 Accumulator 11001111 115 116 117 118 11011111 11011011 11001000 = 200 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

3. Indexed Addressing

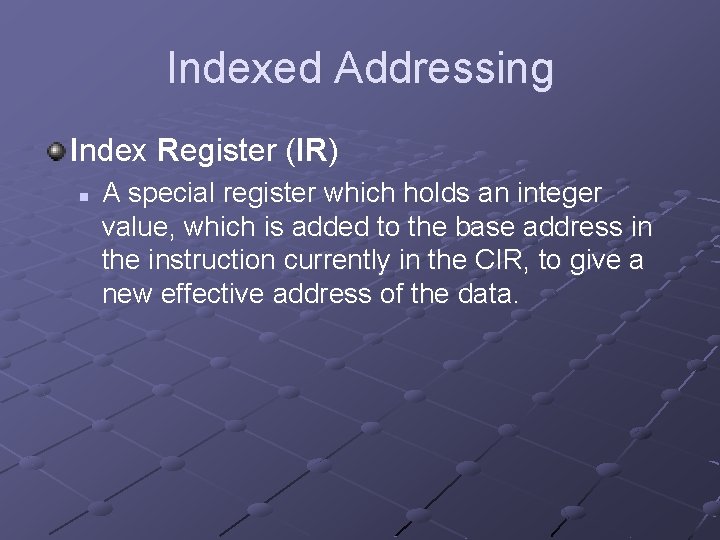

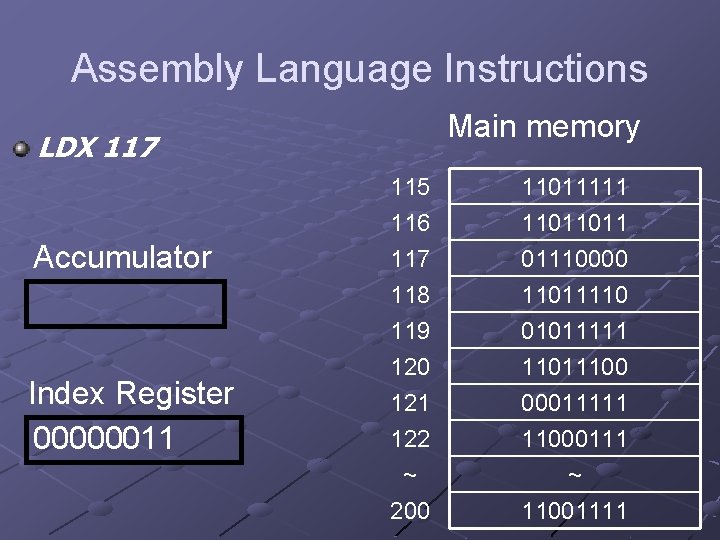

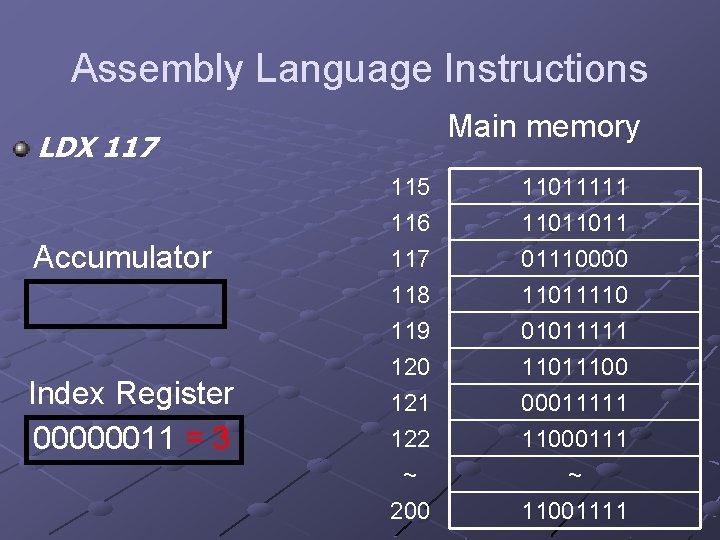

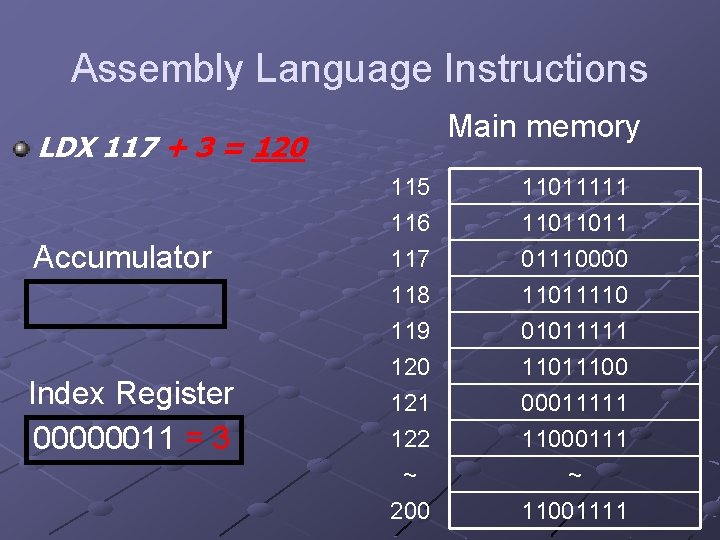

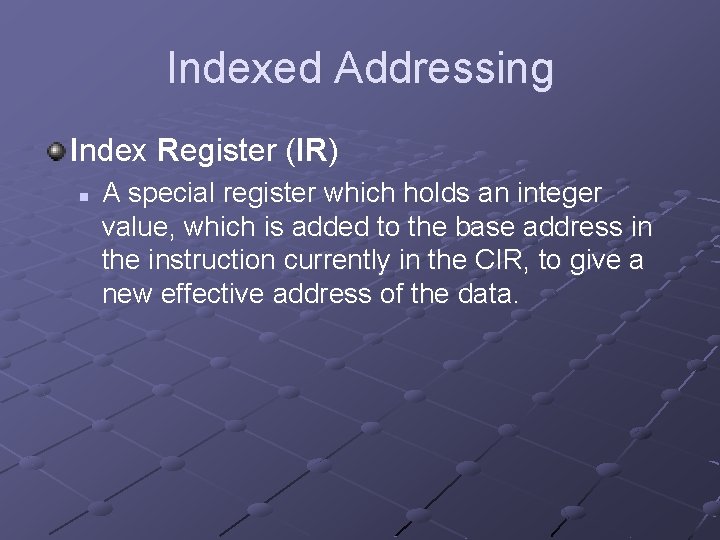

Indexed Addressing Index Register (IR) n A special register which holds an integer value, which is added to the base address in the instruction currently in the CIR, to give a new effective address of the data.

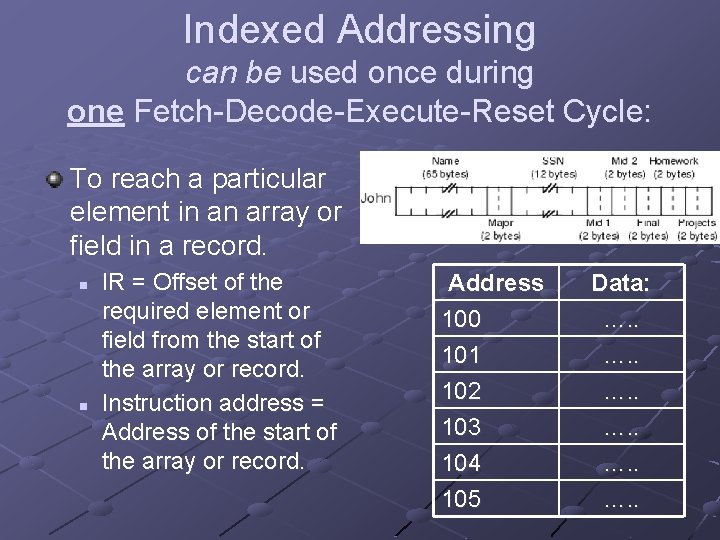

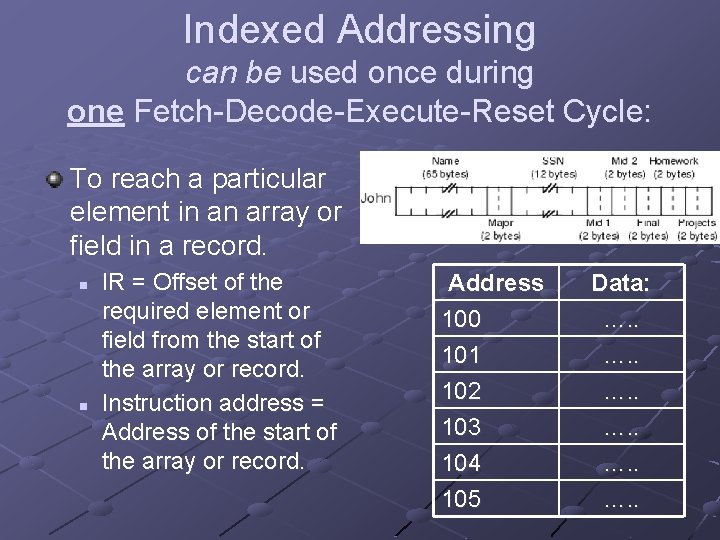

Indexed Addressing can be used once during one Fetch-Decode-Execute-Reset Cycle: To reach a particular element in an array or field in a record. n n IR = Offset of the required element or field from the start of the array or record. Instruction address = Address of the start of the array or record. Address 100 101 102 103 104 105 Data: …. .

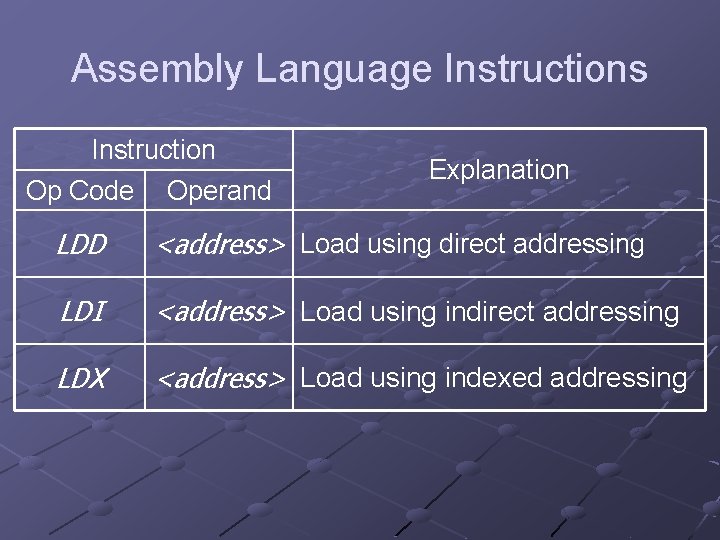

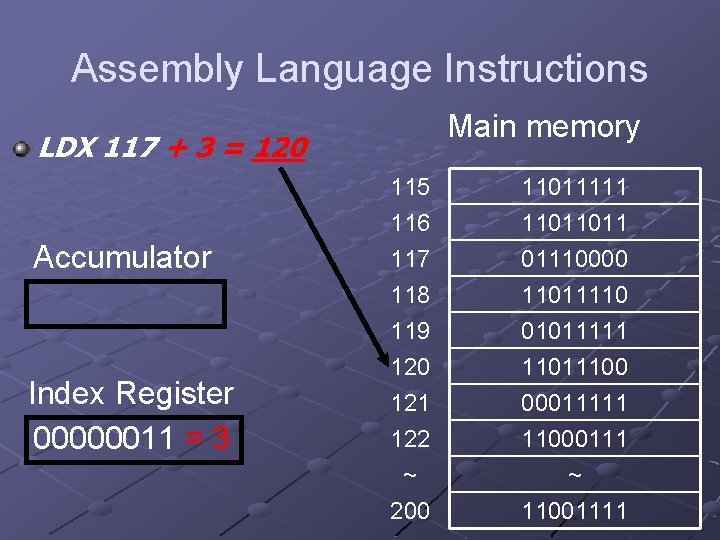

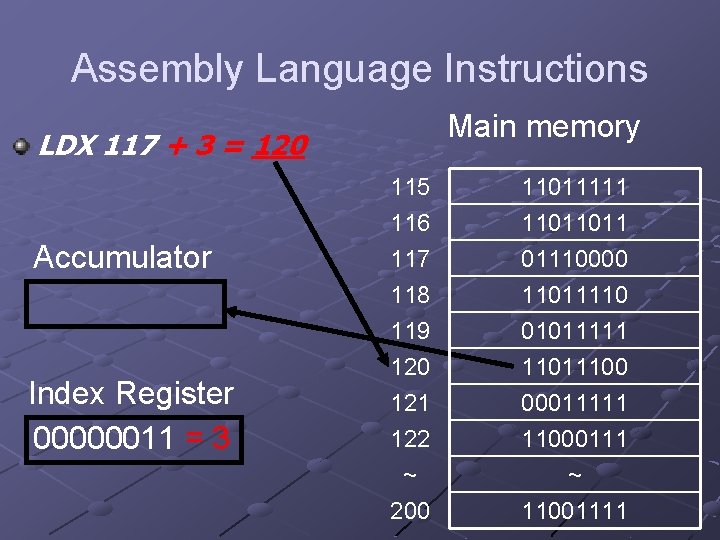

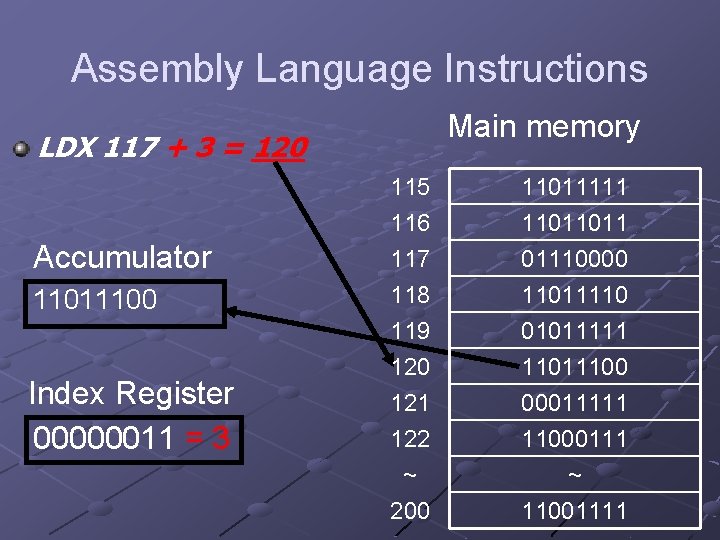

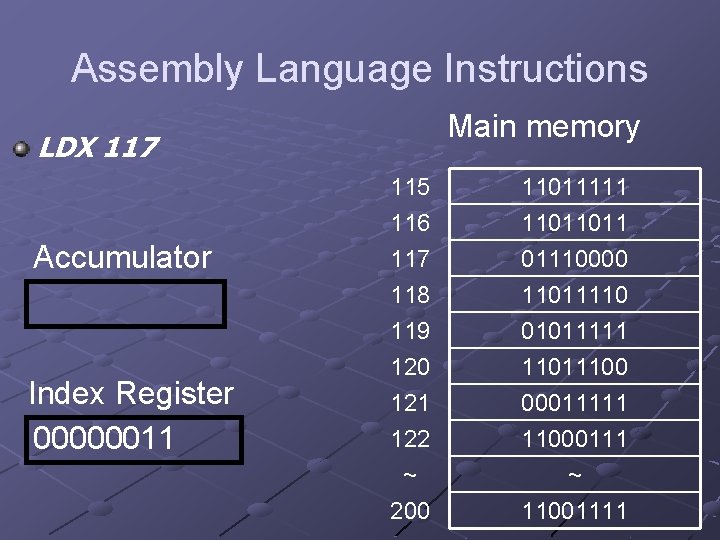

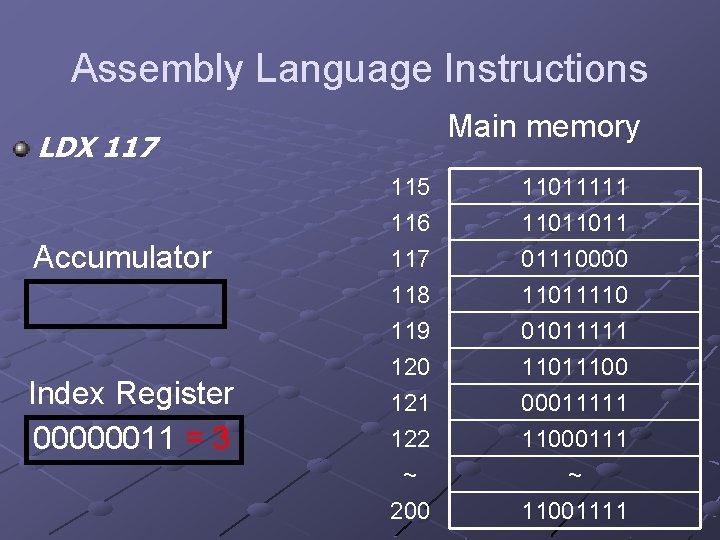

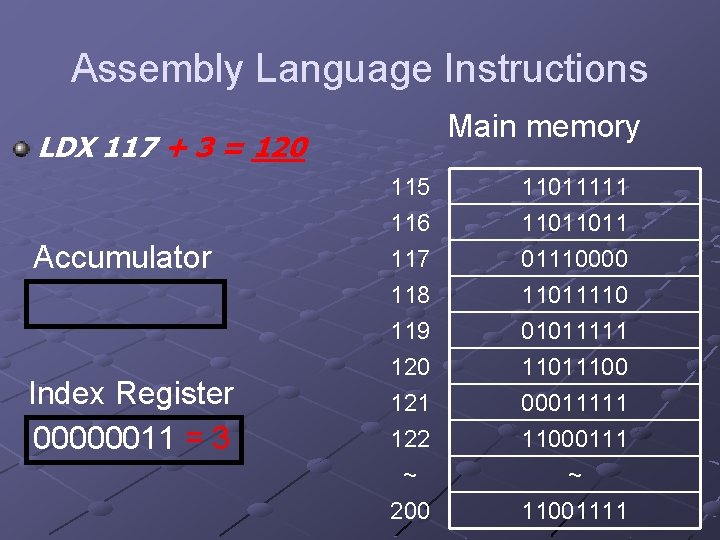

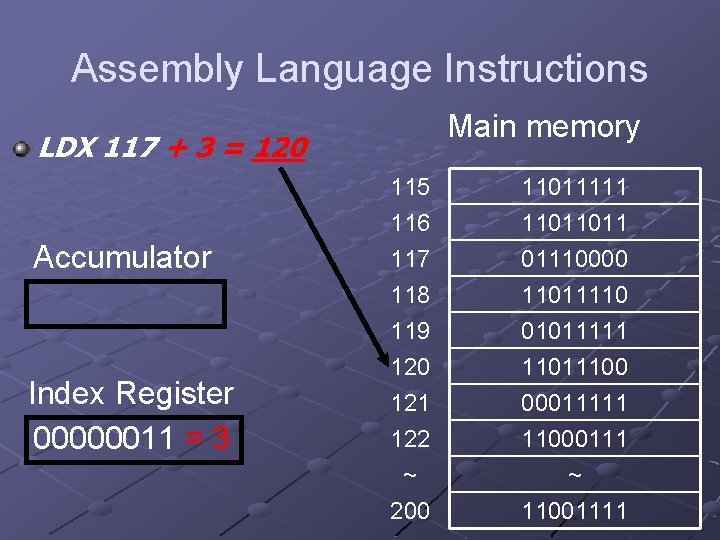

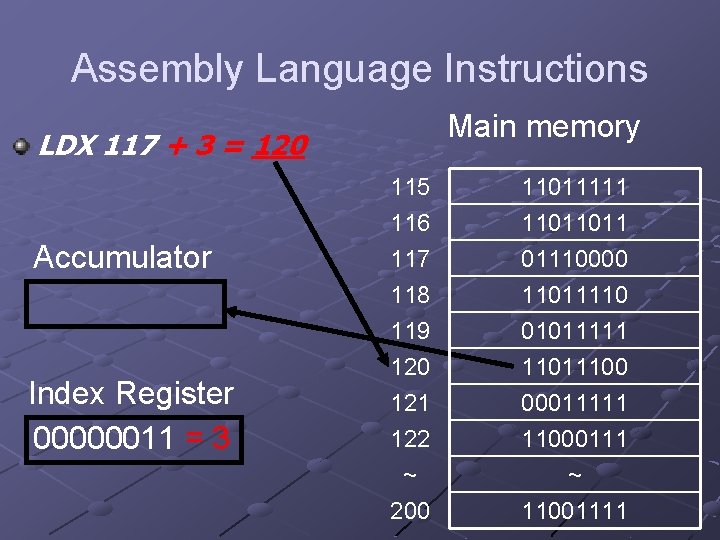

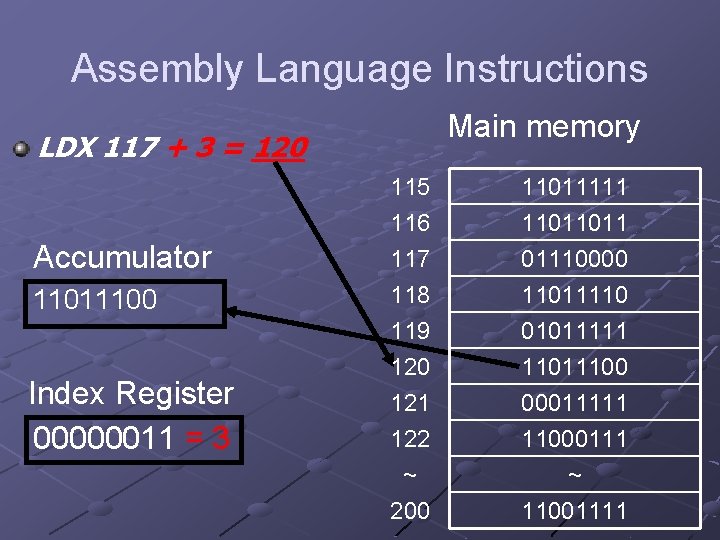

Assembly Language Instructions Instruction Op Code Operand Explanation LDD <address> Load using direct addressing LDI <address> Load using indirect addressing LDX <address> Load using indexed addressing

Assembly Language Instructions Main memory LDX 117 Accumulator Index Register 00000011 115 116 117 118 11011111 11011011 01110000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDX 117 Accumulator Index Register 00000011 = 3 115 116 117 118 11011111 11011011 01110000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDX 117 + 3 = 120 Accumulator Index Register 00000011 = 3 115 116 117 118 11011111 11011011 01110000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDX 117 + 3 = 120 Accumulator Index Register 00000011 = 3 115 116 117 118 11011111 11011011 01110000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDX 117 + 3 = 120 Accumulator Index Register 00000011 = 3 115 116 117 118 11011111 11011011 01110000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

Assembly Language Instructions Main memory LDX 117 + 3 = 120 Accumulator 11011100 Index Register 00000011 = 3 115 116 117 118 11011111 11011011 01110000 11011110 119 120 121 122 ~ 200 01011111 11011100 00011111 11000111 ~ 11001111

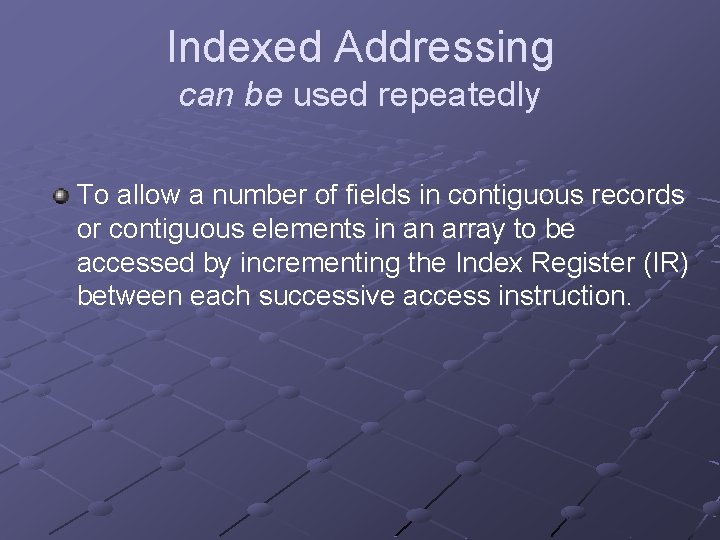

Indexed Addressing can be used repeatedly To allow a number of fields in contiguous records or contiguous elements in an array to be accessed by incrementing the Index Register (IR) between each successive access instruction.

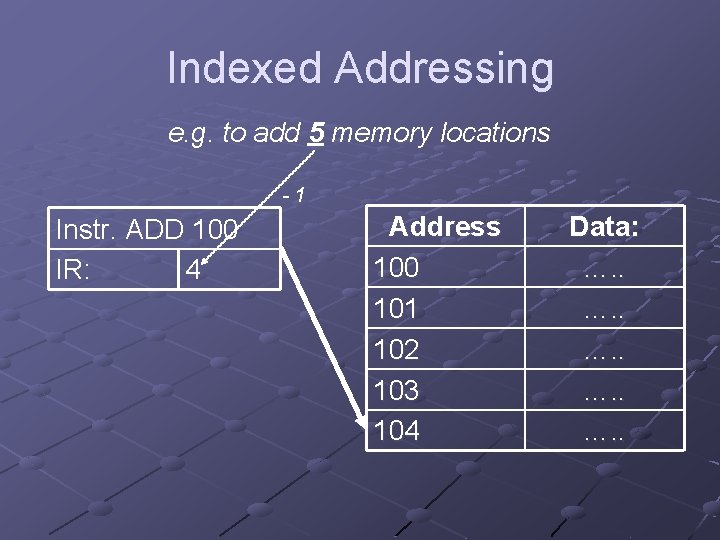

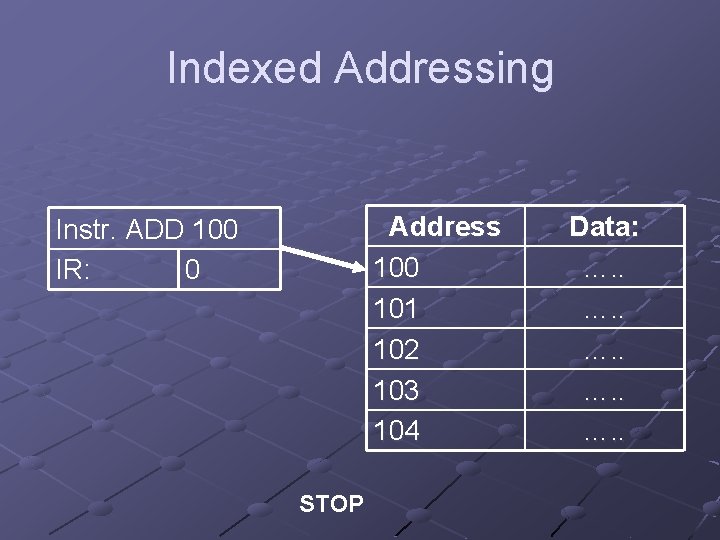

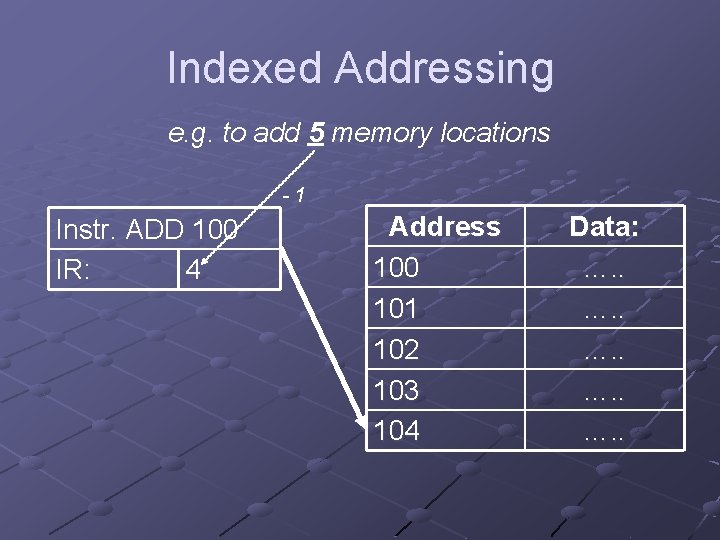

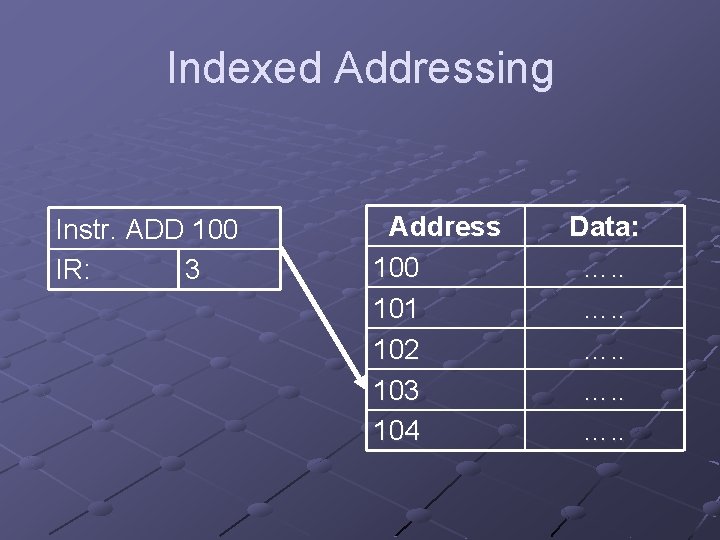

Indexed Addressing e. g. to add 5 memory locations -1 Instr. ADD 100 IR: 4 Address 100 101 102 103 104 Data: …. .

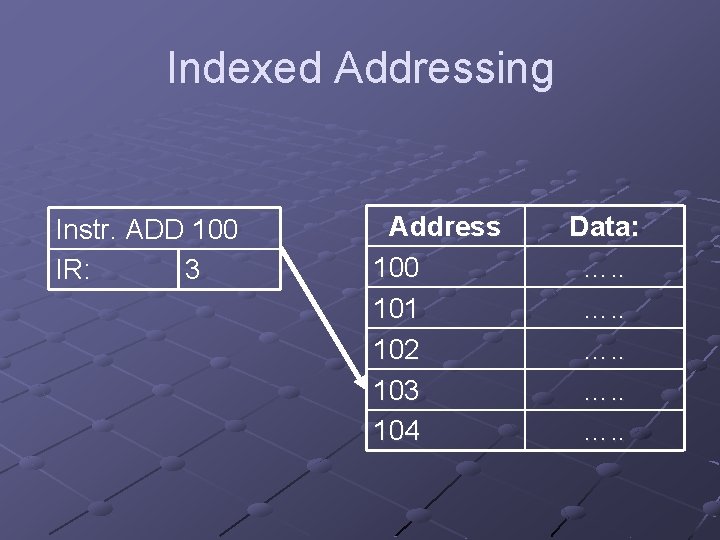

Indexed Addressing Instr. ADD 100 IR: 3 Address 100 101 102 103 104 Data: …. .

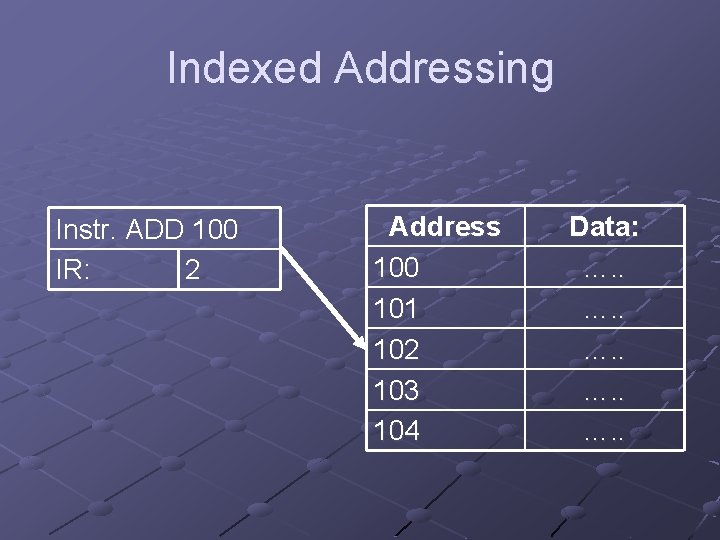

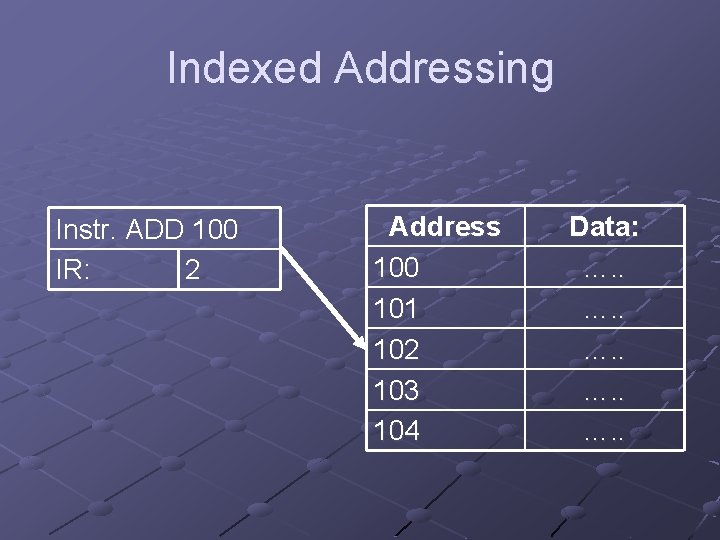

Indexed Addressing Instr. ADD 100 IR: 2 Address 100 101 102 103 104 Data: …. .

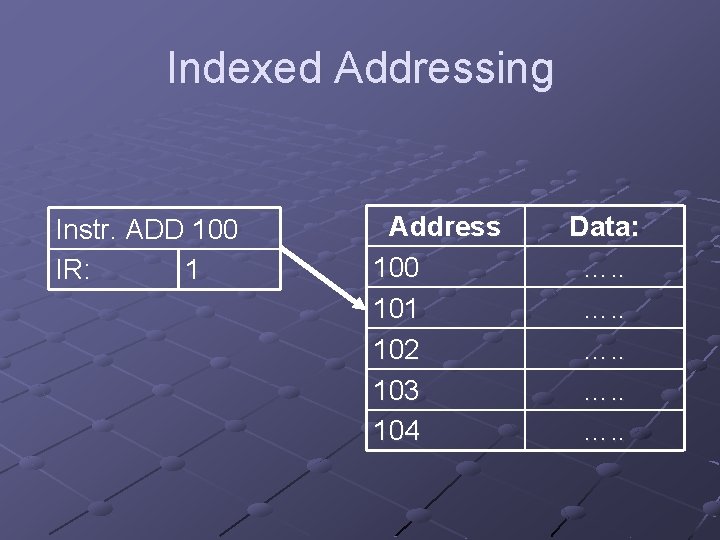

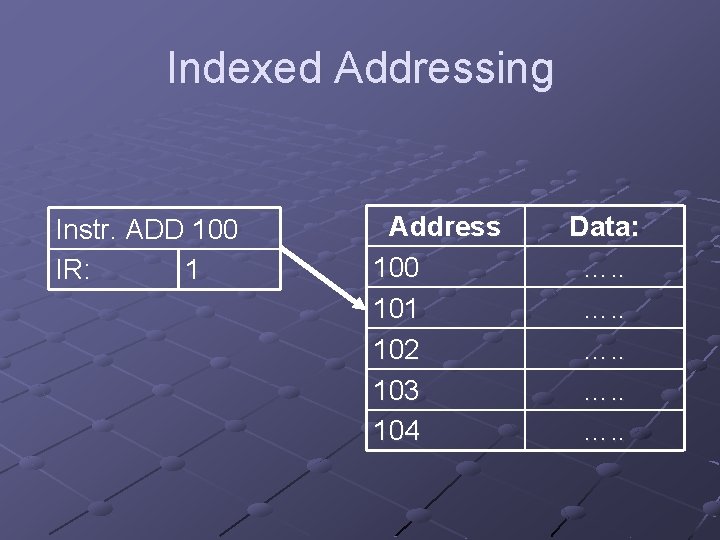

Indexed Addressing Instr. ADD 100 IR: 1 Address 100 101 102 103 104 Data: …. .

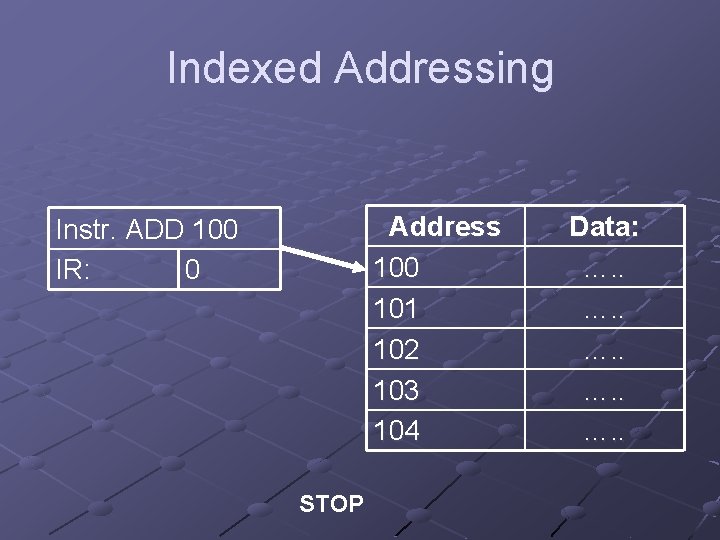

Indexed Addressing Address 100 101 102 103 104 Instr. ADD 100 IR: 0 STOP Data: …. .

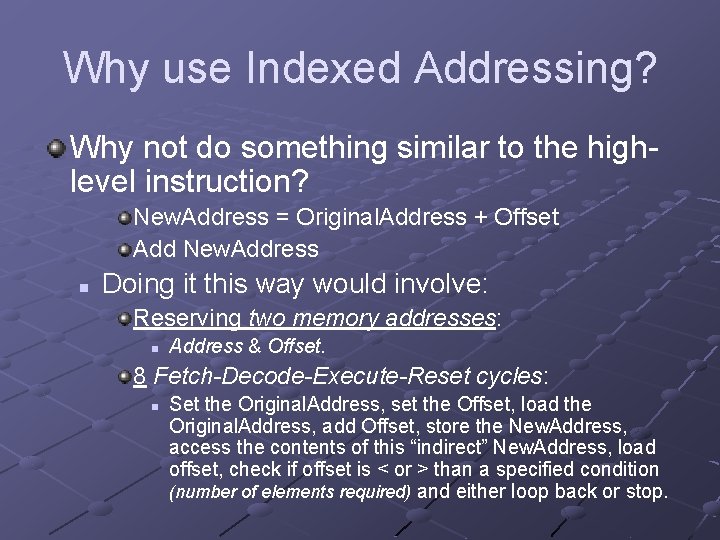

Why use Indexed Addressing? Why not do something similar to the highlevel instruction? New. Address = Original. Address + Offset Add New. Address n Doing it this way would involve: Reserving two memory addresses: n Address & Offset. 8 Fetch-Decode-Execute-Reset cycles: n Set the Original. Address, set the Offset, load the Original. Address, add Offset, store the New. Address, access the contents of this “indirect” New. Address, load offset, check if offset is < or > than a specified condition (number of elements required) and either loop back or stop.

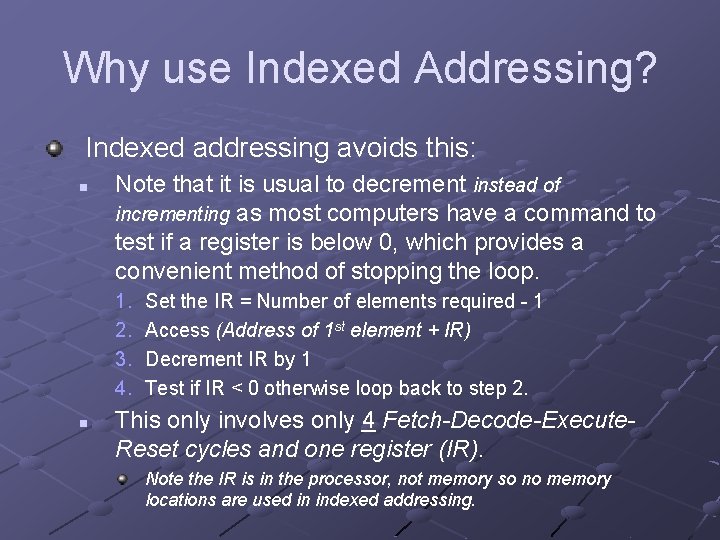

Why use Indexed Addressing? Indexed addressing avoids this: n Note that it is usual to decrement instead of incrementing as most computers have a command to test if a register is below 0, which provides a convenient method of stopping the loop. 1. 2. 3. 4. n Set the IR = Number of elements required - 1 Access (Address of 1 st element + IR) Decrement IR by 1 Test if IR < 0 otherwise loop back to step 2. This only involves only 4 Fetch-Decode-Execute. Reset cycles and one register (IR). Note the IR is in the processor, not memory so no memory locations are used in indexed addressing.

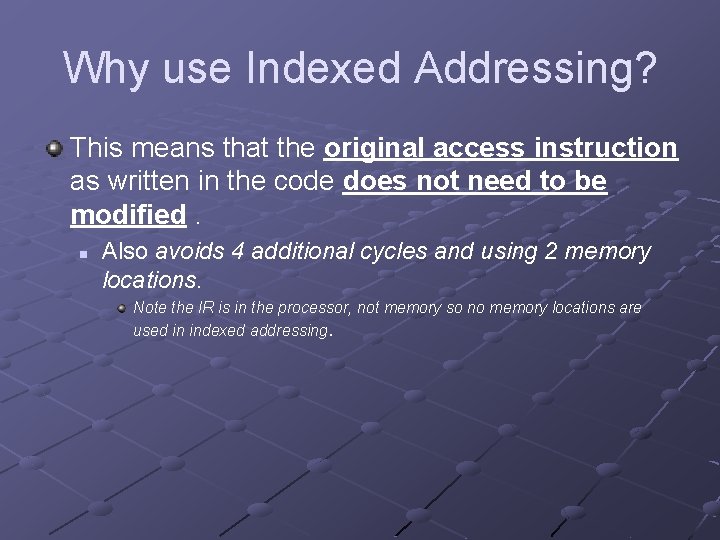

Why use Indexed Addressing? This means that the original access instruction as written in the code does not need to be modified. n Also avoids 4 additional cycles and using 2 memory locations. Note the IR is in the processor, not memory so no memory locations are used in indexed addressing.

Why use Indexed Addressing? Note for fields in a record then: n Set the IR = (No of records required – 1)*offset st record n Address in access instruction = Address of 1 n Decrement IR by offset.

For more research: http: //www. docstoc. com/docs/21677063/IN STRUCTION-ADDRESSING-MODES

4. Relative Addressing

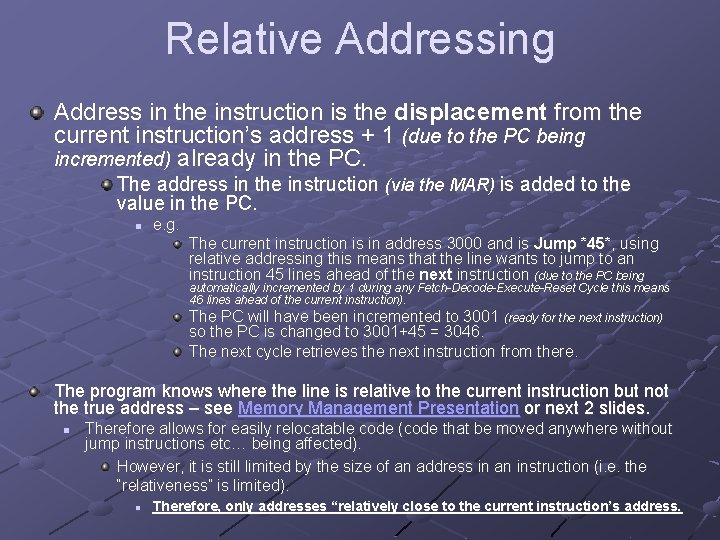

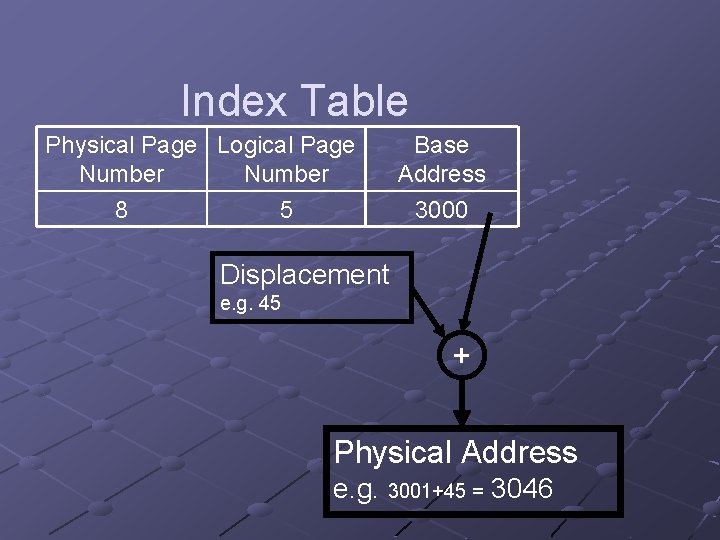

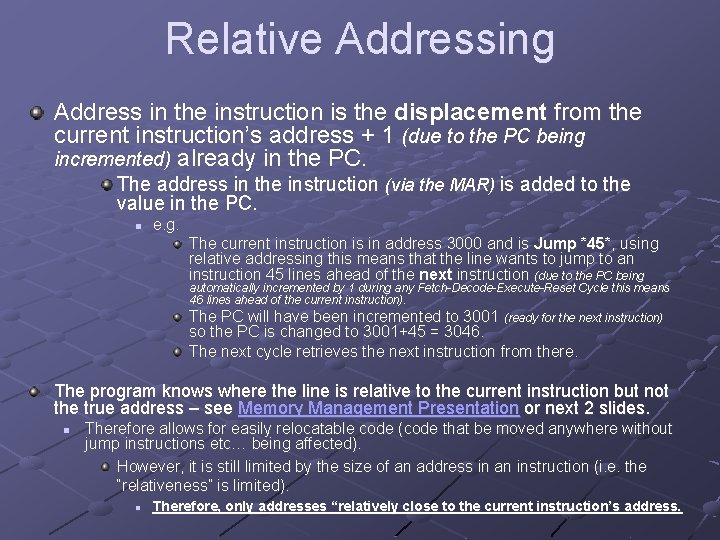

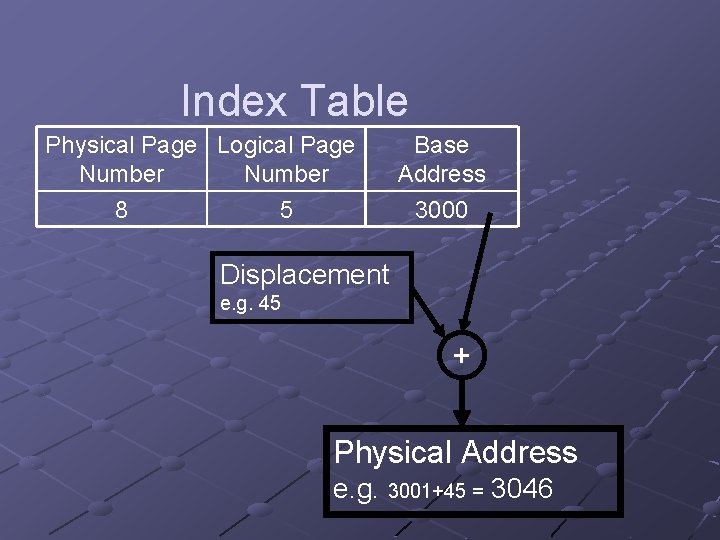

Relative Addressing Address in the instruction is the displacement from the current instruction’s address + 1 (due to the PC being incremented) already in the PC. The address in the instruction (via the MAR) is added to the value in the PC. n e. g. The current instruction is in address 3000 and is Jump *45*, using relative addressing this means that the line wants to jump to an instruction 45 lines ahead of the next instruction (due to the PC being automatically incremented by 1 during any Fetch-Decode-Execute-Reset Cycle this means 46 lines ahead of the current instruction). The PC will have been incremented to 3001 (ready for the next instruction) so the PC is changed to 3001+45 = 3046. The next cycle retrieves the next instruction from there. The program knows where the line is relative to the current instruction but not the true address – see Memory Management Presentation or next 2 slides. n Therefore allows for easily relocatable code (code that be moved anywhere without jump instructions etc… being affected). However, it is still limited by the size of an address in an instruction (i. e. the “relativeness” is limited). n Therefore, only addresses “relatively close to the current instruction’s address.

Index Table Physical Page Logical Page Number 8 5 Base Address 3000 Displacement e. g. 45 + Physical Address e. g. 3001+45 = 3046

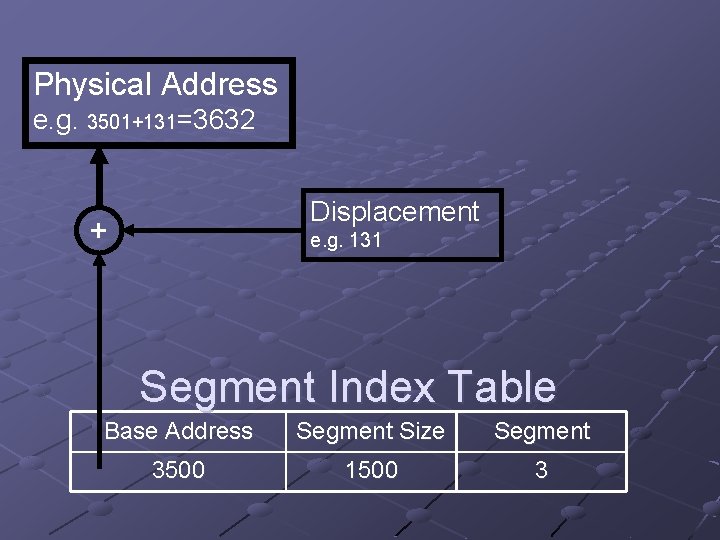

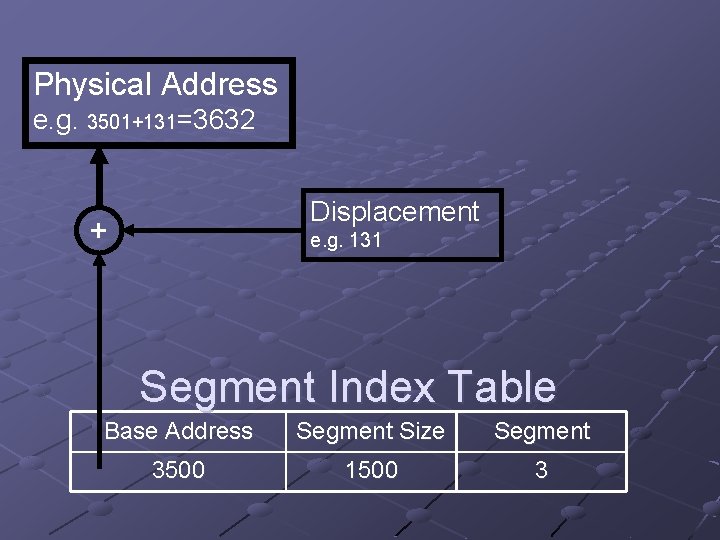

Physical Address e. g. 3501+131=3632 Displacement + e. g. 131 Segment Index Table Base Address Segment Size Segment 3500 1500 3

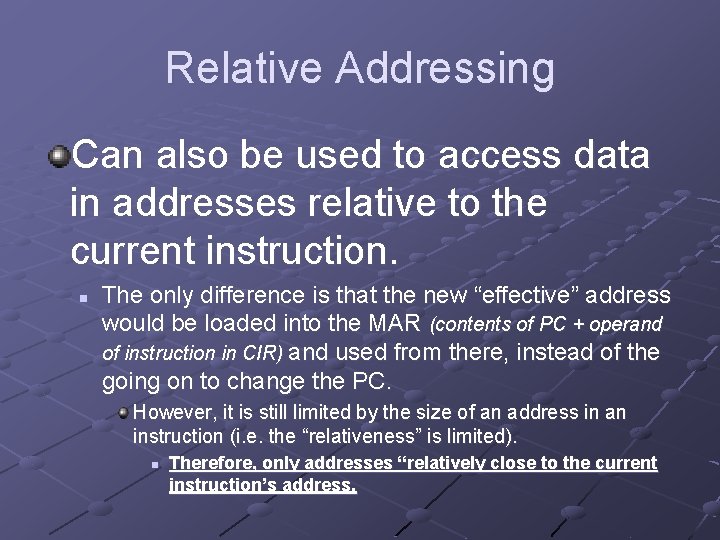

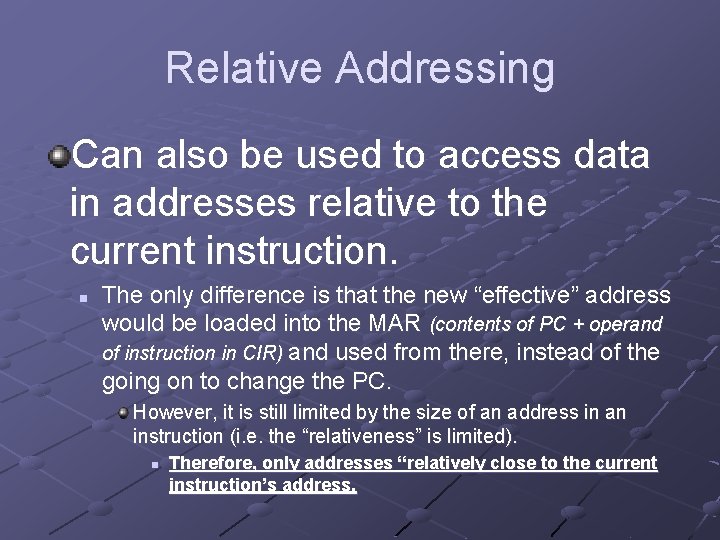

Relative Addressing Can also be used to access data in addresses relative to the current instruction. n The only difference is that the new “effective” address would be loaded into the MAR (contents of PC + operand of instruction in CIR) and used from there, instead of the going on to change the PC. However, it is still limited by the size of an address in an instruction (i. e. the “relativeness” is limited). n Therefore, only addresses “relatively close to the current instruction’s address.

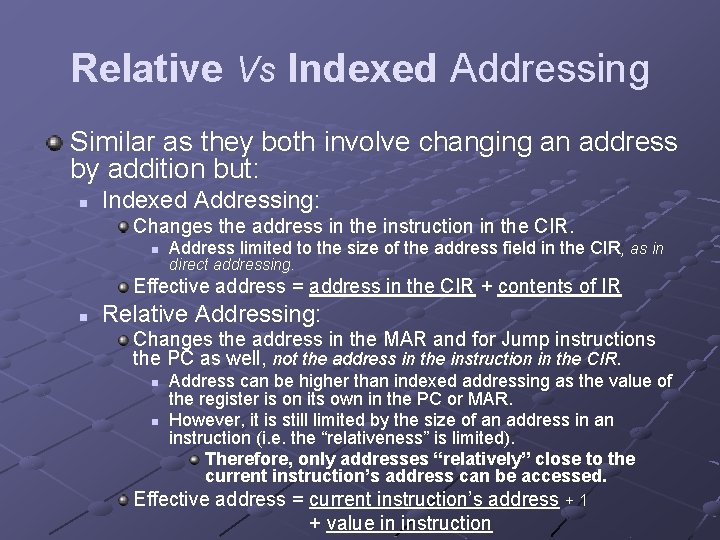

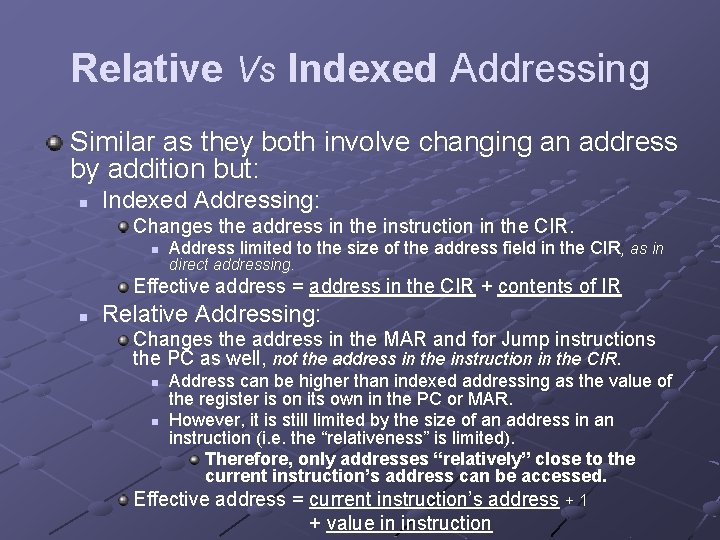

Relative Vs Indexed Addressing Similar as they both involve changing an address by addition but: n Indexed Addressing: Changes the address in the instruction in the CIR. n Address limited to the size of the address field in the CIR, as in direct addressing. Effective address = address in the CIR + contents of IR n Relative Addressing: Changes the address in the MAR and for Jump instructions the PC as well, not the address in the instruction in the CIR. n n Address can be higher than indexed addressing as the value of the register is on its own in the PC or MAR. However, it is still limited by the size of an address in an instruction (i. e. the “relativeness” is limited). Therefore, only addresses “relatively” close to the current instruction’s address can be accessed. Effective address = current instruction’s address + 1 + value in instruction

For more research http: //www. edsim 51. com/8051 Notes/8051/ instruction. Set. Summary. html http: //en. wikipedia. org/wiki/Addressing_mo des

5. Immediate Addressing

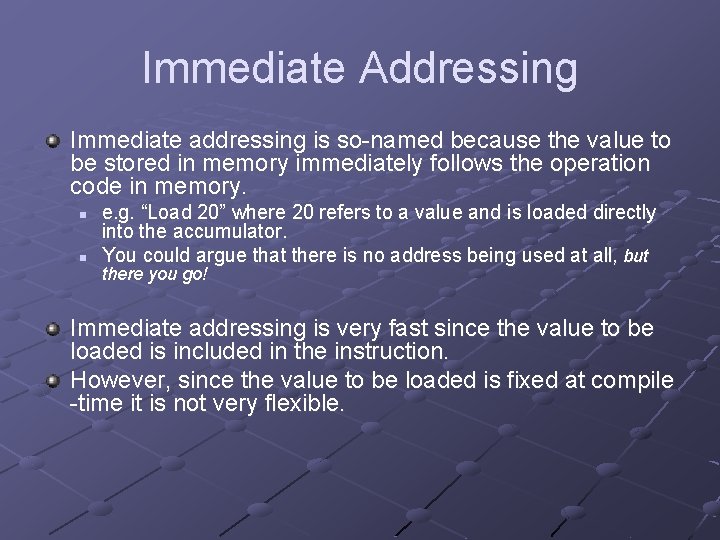

Immediate Addressing Immediate addressing is so-named because the value to be stored in memory immediately follows the operation code in memory. n n e. g. “Load 20” where 20 refers to a value and is loaded directly into the accumulator. You could argue that there is no address being used at all, but there you go! Immediate addressing is very fast since the value to be loaded is included in the instruction. However, since the value to be loaded is fixed at compile -time it is not very flexible.

Immediate Addressing Advantage: n No memory reference other than instruction fetch is required to obtain the data to be used. Disadvantage: n The size of the number is limited to the size of the address field, which most instruction sets is small compared to word length. n This is similar to the problem “direct addressing” has.

For more research: http: //www. edsim 51. com/8051 Notes/8051/ instruction. Set. Summary. html http: //www. docstoc. com/docs/21677063/IN STRUCTION-ADDRESSING-MODES

Plenary State the 5 methods of memory addressing and explain why they are used.