Comprehensive VHDL Module 9 More on Types November

Comprehensive VHDL Module 9 More on Types November 2000

More on Types Aim © To understand the use of integer and array types Topics covered © Package declarations © Integer subtypes, operators and literals © Array types and memories © Array attributes and type attributes © Aggregates © Qualified expressions 9 -2 • Comprehensive VHDL: More on Types Copyright © 2000 Doulos

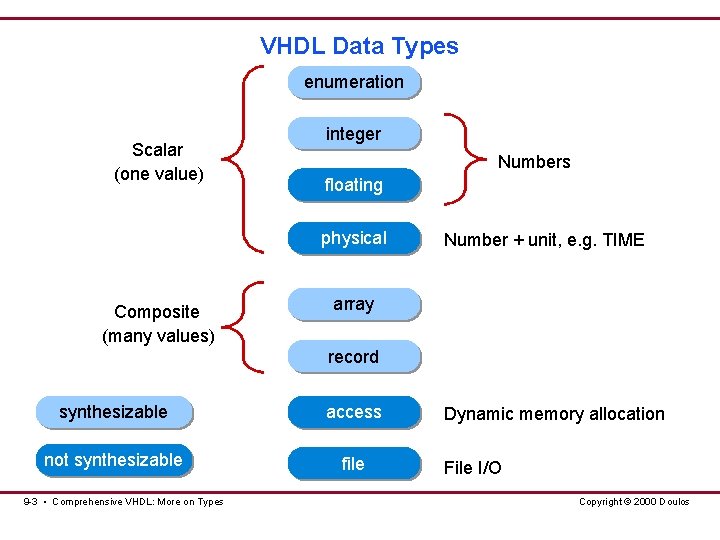

VHDL Data Types enumeration Scalar (one value) integer Numbers floating physical Composite (many values) Number + unit, e. g. TIME array record synthesizable access not synthesizable file 9 -3 • Comprehensive VHDL: More on Types Dynamic memory allocation File I/O Copyright © 2000 Doulos

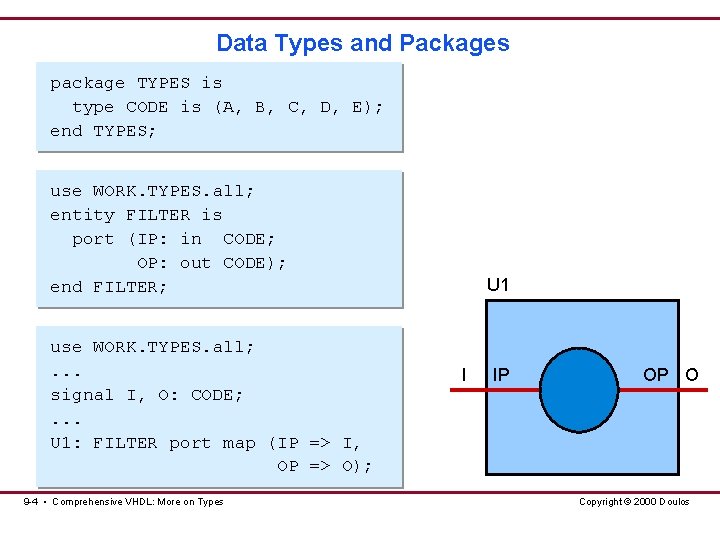

Data Types and Packages package TYPES is type CODE is (A, B, C, D, E); end TYPES; use WORK. TYPES. all; entity FILTER is port (IP: in CODE; OP: out CODE); end FILTER; use WORK. TYPES. all; . . . signal I, O: CODE; . . . U 1: FILTER port map (IP => I, OP => O); 9 -4 • Comprehensive VHDL: More on Types U 1 I IP OP O Copyright © 2000 Doulos

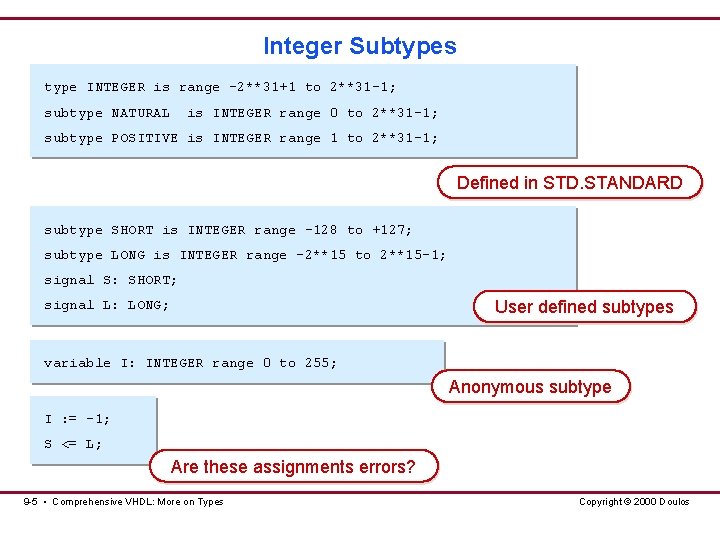

Integer Subtypes type INTEGER is range -2**31+1 to 2**31 -1; subtype NATURAL is INTEGER range 0 to 2**31 -1; subtype POSITIVE is INTEGER range 1 to 2**31 -1; Defined in STD. STANDARD subtype SHORT is INTEGER range -128 to +127; subtype LONG is INTEGER range -2**15 to 2**15 -1; signal S: SHORT; User defined subtypes signal L: LONG; variable I: INTEGER range 0 to 255; Anonymous subtype I : = -1; S <= L; Are these assignments errors? 9 -5 • Comprehensive VHDL: More on Types Copyright © 2000 Doulos

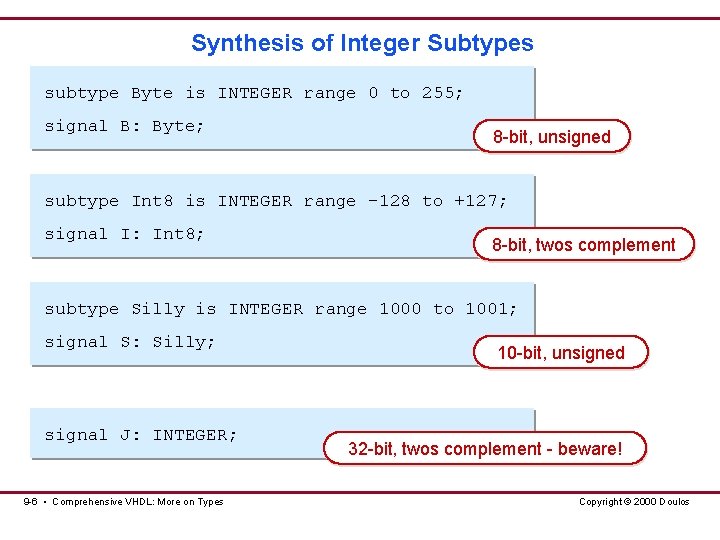

Synthesis of Integer Subtypes subtype Byte is INTEGER range 0 to 255; signal B: Byte; 8 -bit, unsigned subtype Int 8 is INTEGER range -128 to +127; signal I: Int 8; 8 -bit, twos complement subtype Silly is INTEGER range 1000 to 1001; signal S: Silly; signal J: INTEGER; 9 -6 • Comprehensive VHDL: More on Types 10 -bit, unsigned 32 -bit, twos complement - beware! Copyright © 2000 Doulos

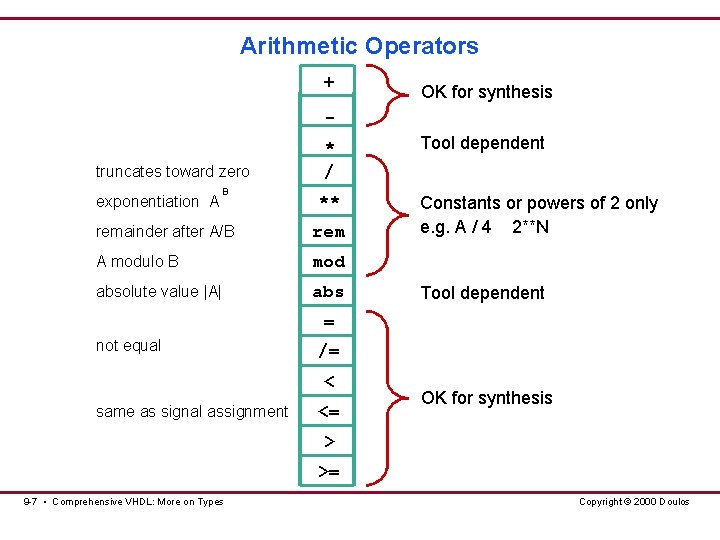

Arithmetic Operators + OK for synthesis truncates toward zero exponentiation A B * / ** remainder after A/B rem A modulo B mod absolute value |A| abs Tool dependent Constants or powers of 2 only e. g. A / 4 2**N Tool dependent = not equal /= < same as signal assignment <= OK for synthesis > >= 9 -7 • Comprehensive VHDL: More on Types Copyright © 2000 Doulos

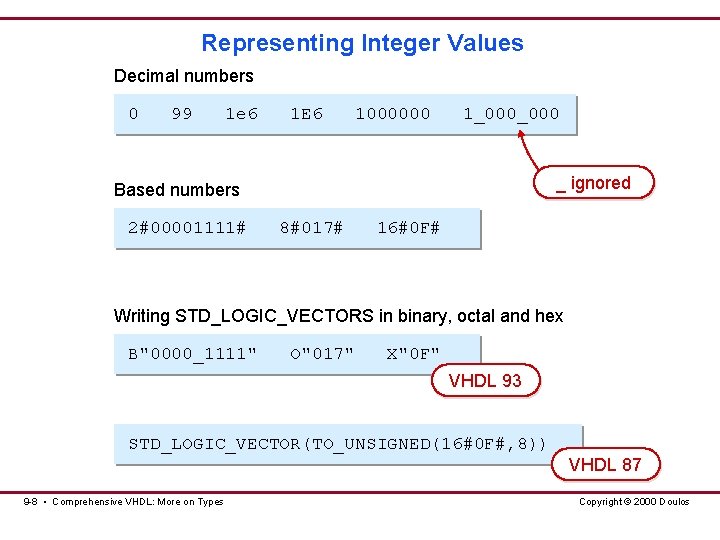

Representing Integer Values Decimal numbers 0 99 1 e 6 1 E 6 1000000 1_000 _ ignored Based numbers 2#00001111# 8#017# 16#0 F# Writing STD_LOGIC_VECTORS in binary, octal and hex B"0000_1111" O"017" X"0 F" VHDL 93 STD_LOGIC_VECTOR(TO_UNSIGNED(16#0 F#, 8)) VHDL 87 9 -8 • Comprehensive VHDL: More on Types Copyright © 2000 Doulos

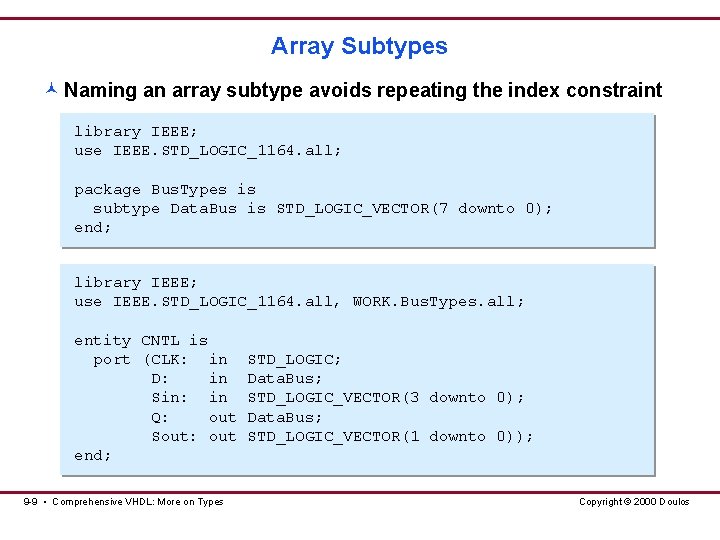

Array Subtypes © Naming an array subtype avoids repeating the index constraint library IEEE; use IEEE. STD_LOGIC_1164. all; package Bus. Types is subtype Data. Bus is STD_LOGIC_VECTOR(7 downto 0); end; library IEEE; use IEEE. STD_LOGIC_1164. all, WORK. Bus. Types. all; entity CNTL is port (CLK: in D: in Sin: in Q: out Sout: out end; 9 -9 • Comprehensive VHDL: More on Types STD_LOGIC; Data. Bus; STD_LOGIC_VECTOR(3 downto 0); Data. Bus; STD_LOGIC_VECTOR(1 downto 0)); Copyright © 2000 Doulos

Array Types Unconstrained array type STD_LOGIC_VECTOR is array (NATURAL range <>) of STD_LOGIC; Index type Element type subtype BYTE is STD_LOGIC_VECTOR(7 downto 0); type RAM 1 Kx 8 is array (0 to 1023) of BYTE; variable RAM: RAM 1 Kx 8; 9 -10 • Comprehensive VHDL: More on Types Constrained array type Copyright © 2000 Doulos

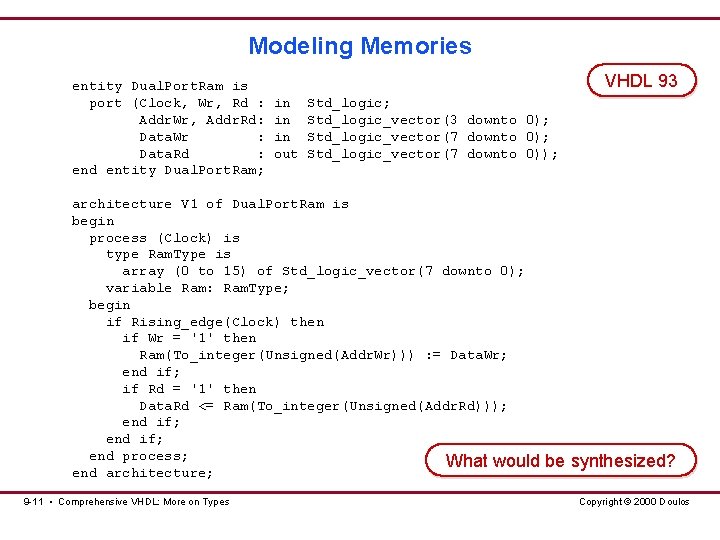

Modeling Memories entity Dual. Port. Ram is port (Clock, Wr, Rd : Addr. Wr, Addr. Rd: Data. Wr : Data. Rd : end entity Dual. Port. Ram; VHDL 93 in in in out Std_logic; Std_logic_vector(3 downto 0); Std_logic_vector(7 downto 0)); architecture V 1 of Dual. Port. Ram is begin process (Clock) is type Ram. Type is array (0 to 15) of Std_logic_vector(7 downto 0); variable Ram: Ram. Type; begin if Rising_edge(Clock) then if Wr = '1' then Ram(To_integer(Unsigned(Addr. Wr))) : = Data. Wr; end if; if Rd = '1' then Data. Rd <= Ram(To_integer(Unsigned(Addr. Rd))); end if; end process; What would end architecture; 9 -11 • Comprehensive VHDL: More on Types be synthesized? Copyright © 2000 Doulos

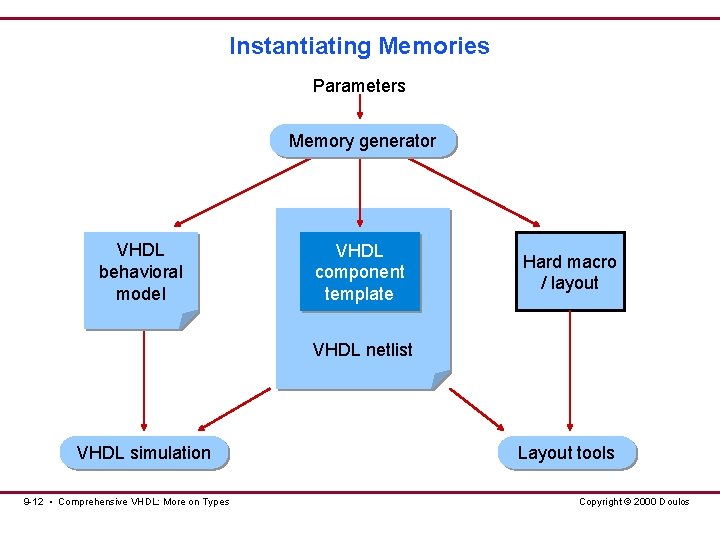

Instantiating Memories Parameters Memory generator VHDL behavioral model VHDL component template Hard macro / layout VHDL netlist VHDL simulation 9 -12 • Comprehensive VHDL: More on Types Layout tools Copyright © 2000 Doulos

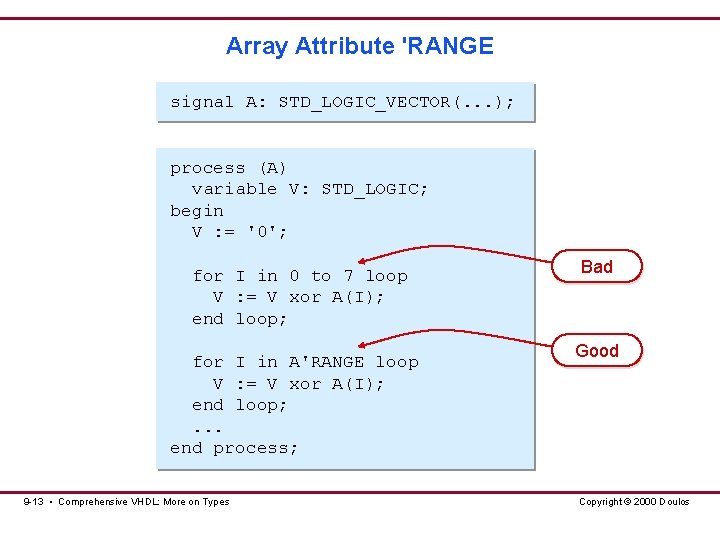

Array Attribute 'RANGE signal A: STD_LOGIC_VECTOR(. . . ); process (A) variable V: STD_LOGIC; begin V : = '0'; for I in 0 to 7 loop V : = V xor A(I); end loop; for I in A'RANGE loop V : = V xor A(I); end loop; . . . end process; 9 -13 • Comprehensive VHDL: More on Types Bad Good Copyright © 2000 Doulos

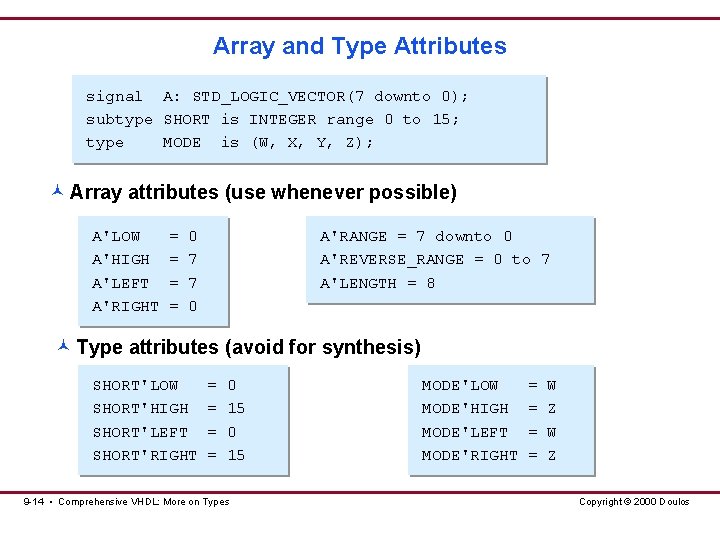

Array and Type Attributes signal A: STD_LOGIC_VECTOR(7 downto 0); subtype SHORT is INTEGER range 0 to 15; type MODE is (W, X, Y, Z); © Array attributes (use whenever possible) A'LOW A'HIGH A'LEFT A'RIGHT = = 0 7 7 0 A'RANGE = 7 downto 0 A'REVERSE_RANGE = 0 to 7 A'LENGTH = 8 © Type attributes (avoid for synthesis) SHORT'LOW SHORT'HIGH SHORT'LEFT SHORT'RIGHT = = 0 15 9 -14 • Comprehensive VHDL: More on Types MODE'LOW MODE'HIGH MODE'LEFT MODE'RIGHT = = W Z Copyright © 2000 Doulos

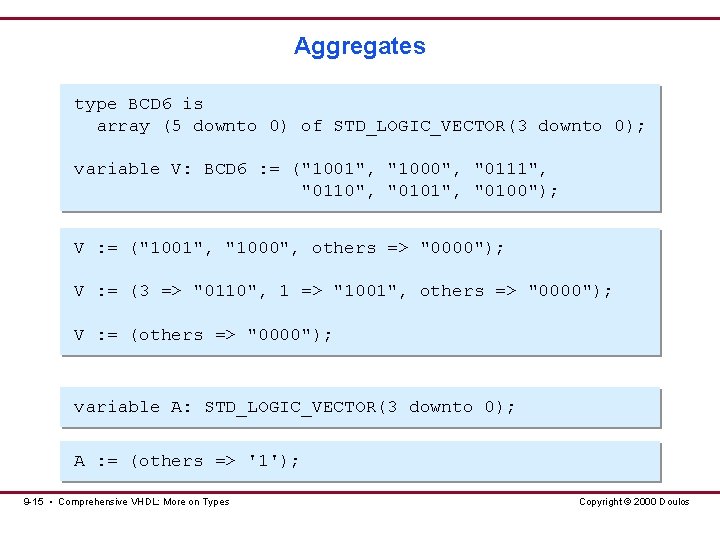

Aggregates type BCD 6 is array (5 downto 0) of STD_LOGIC_VECTOR(3 downto 0); variable V: BCD 6 : = ("1001", "1000", "0111", "0110", "0101", "0100"); V : = ("1001", "1000", others => "0000"); V : = (3 => "0110", 1 => "1001", others => "0000"); V : = (others => "0000"); variable A: STD_LOGIC_VECTOR(3 downto 0); A : = (others => '1'); 9 -15 • Comprehensive VHDL: More on Types Copyright © 2000 Doulos

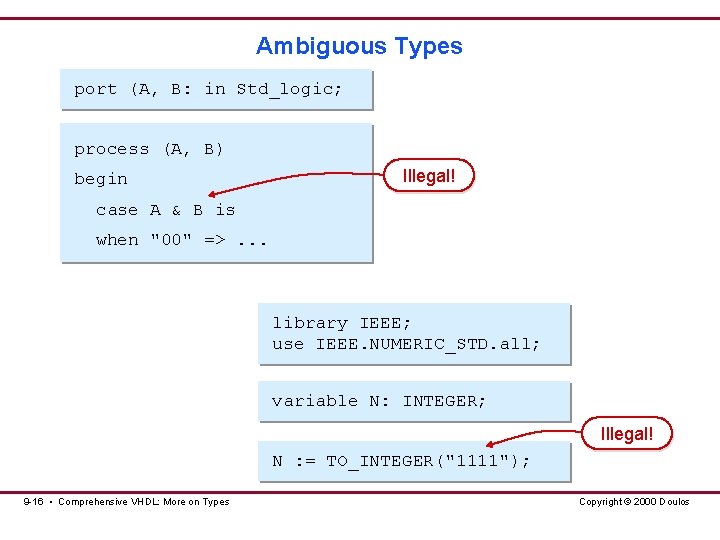

Ambiguous Types port (A, B: in Std_logic; process (A, B) begin Illegal! case A & B is when "00" =>. . . library IEEE; use IEEE. NUMERIC_STD. all; variable N: INTEGER; Illegal! N : = TO_INTEGER("1111"); 9 -16 • Comprehensive VHDL: More on Types Copyright © 2000 Doulos

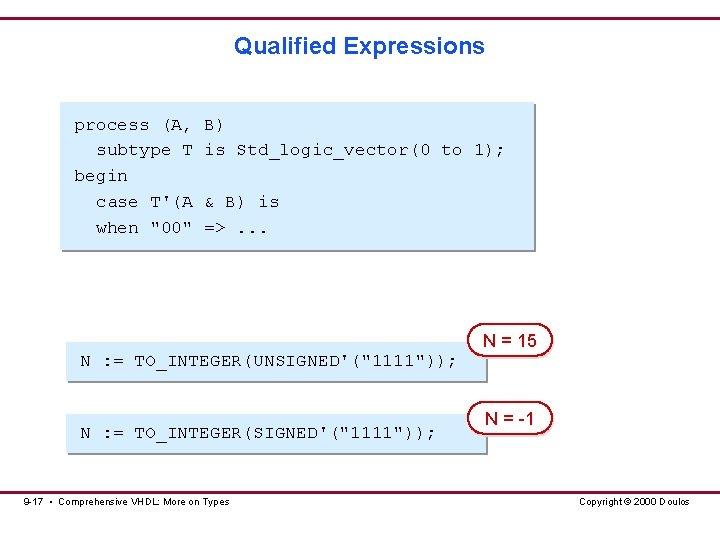

Qualified Expressions process (A, subtype T begin case T'(A when "00" B) is Std_logic_vector(0 to 1); & B) is =>. . . N = 15 N : = TO_INTEGER(UNSIGNED'("1111")); N : = TO_INTEGER(SIGNED'("1111")); 9 -17 • Comprehensive VHDL: More on Types N = -1 Copyright © 2000 Doulos

- Slides: 17