Compiler Construction Dr Naveed Ejaz Lecture 3 Abstract

Compiler Construction Dr. Naveed Ejaz Lecture 3

Abstract Syntax Trees §. § Compilers often use an abstract syntax tree (AST). 2

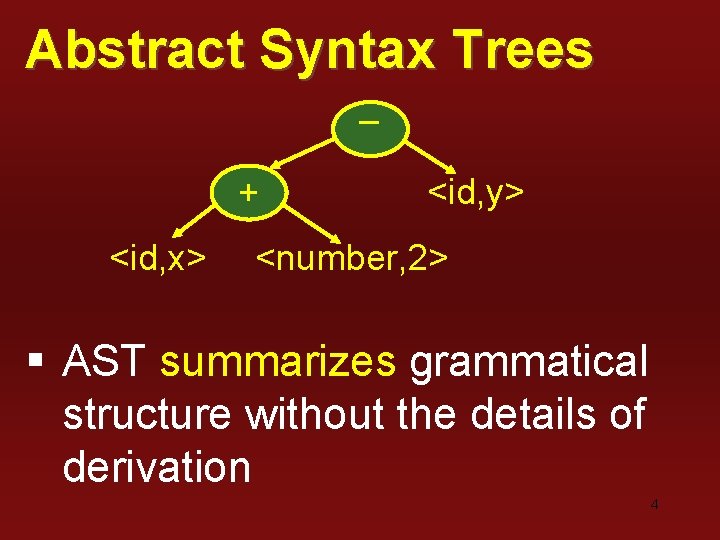

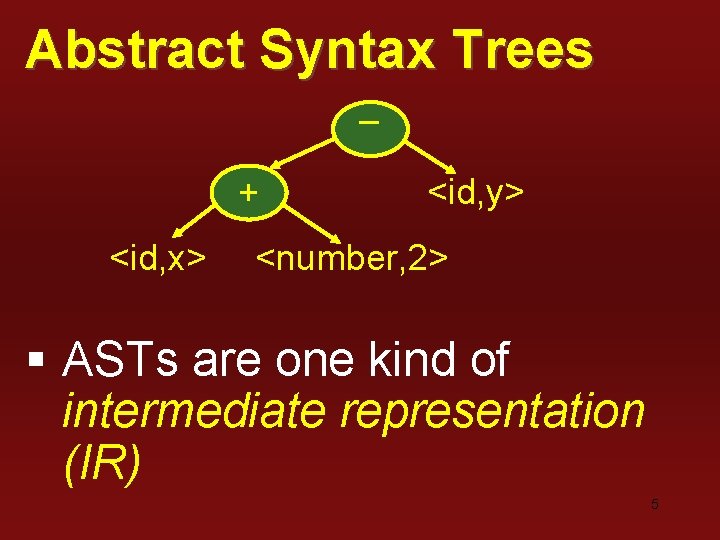

Abstract Syntax Trees x+2 -y – + <id, x> <id, y> <number, 2> 3

Abstract Syntax Trees – + <id, x> <id, y> <number, 2> § AST summarizes grammatical structure without the details of derivation 4

Abstract Syntax Trees – + <id, x> <id, y> <number, 2> § ASTs are one kind of intermediate representation (IR) 5

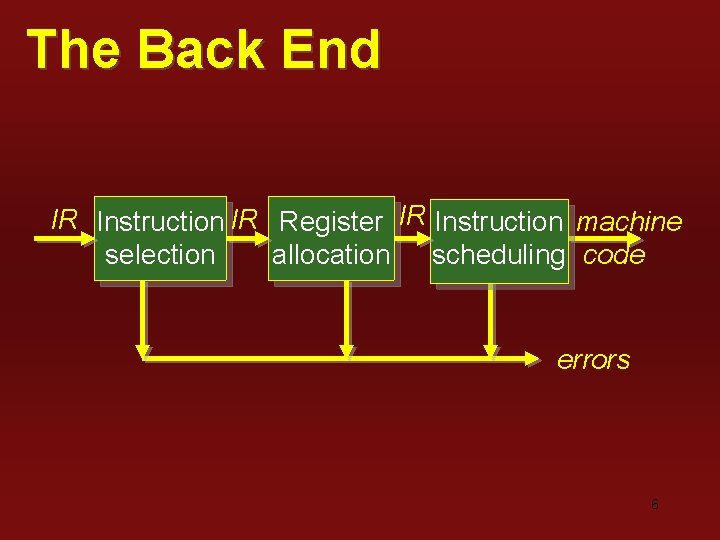

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors 6

The Back End § Translate IR into target machine code. § Choose machine (assembly) instructions to implement each IR operation 7

The Back End § Ensure conformance with system interfaces § Decide which values to keep in registers 8

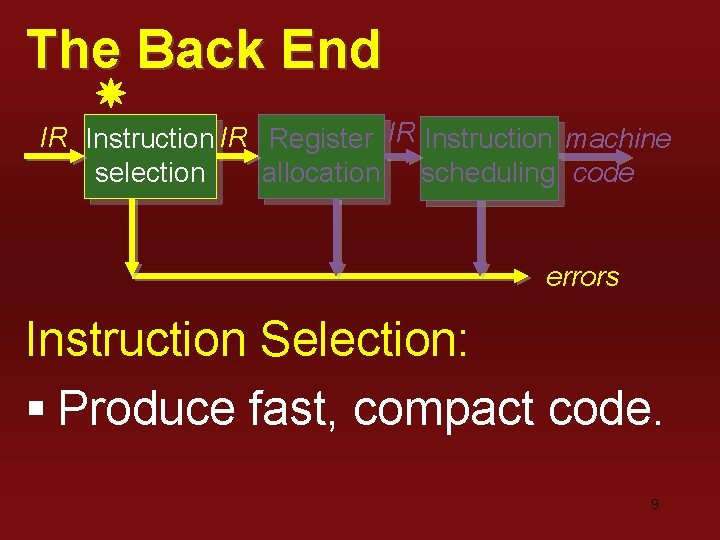

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Selection: § Produce fast, compact code. 9

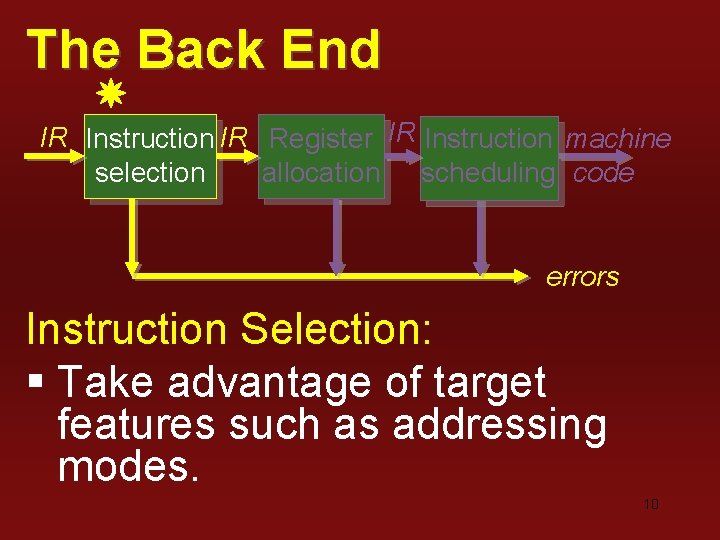

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Selection: § Take advantage of target features such as addressing modes. 10

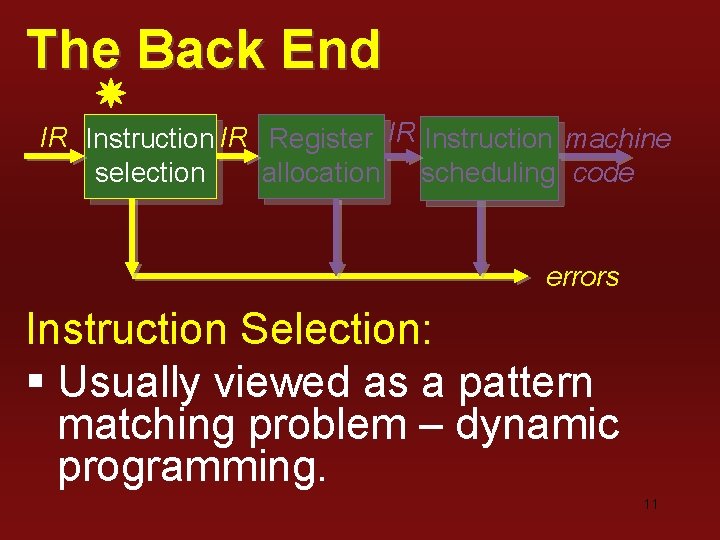

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Selection: § Usually viewed as a pattern matching problem – dynamic programming. 11

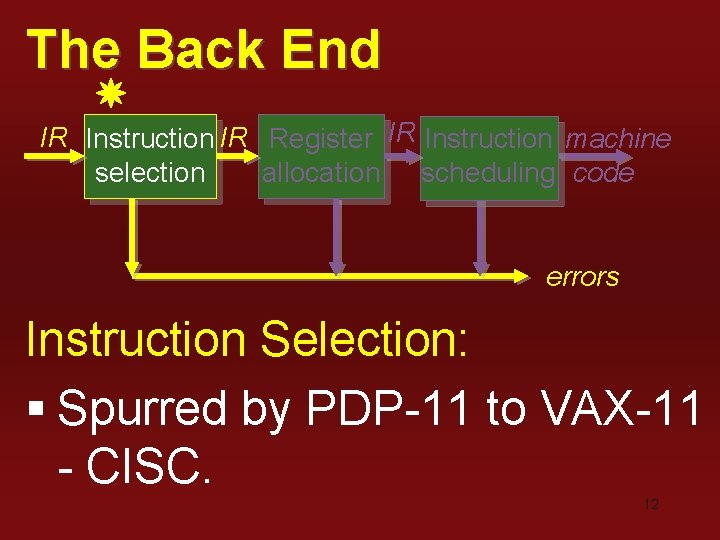

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Selection: § Spurred by PDP-11 to VAX-11 - CISC. 12

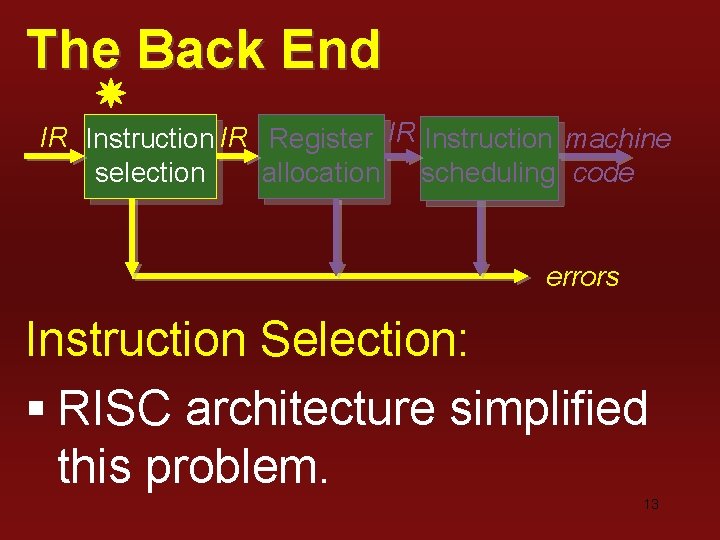

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Selection: § RISC architecture simplified this problem. 13

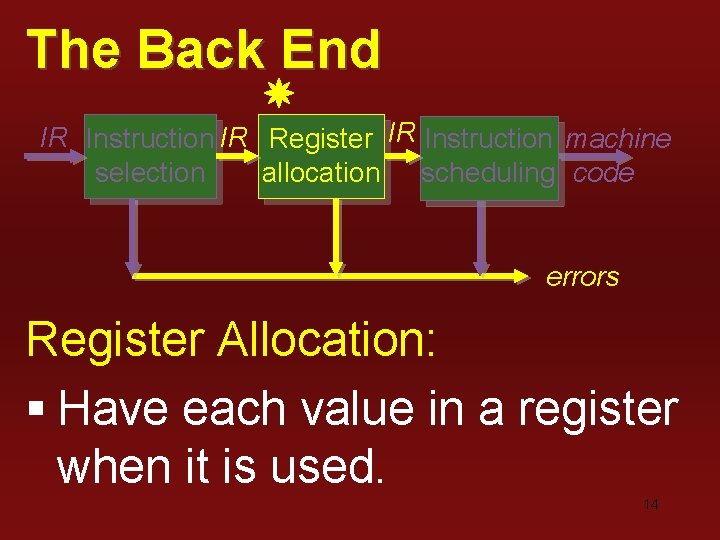

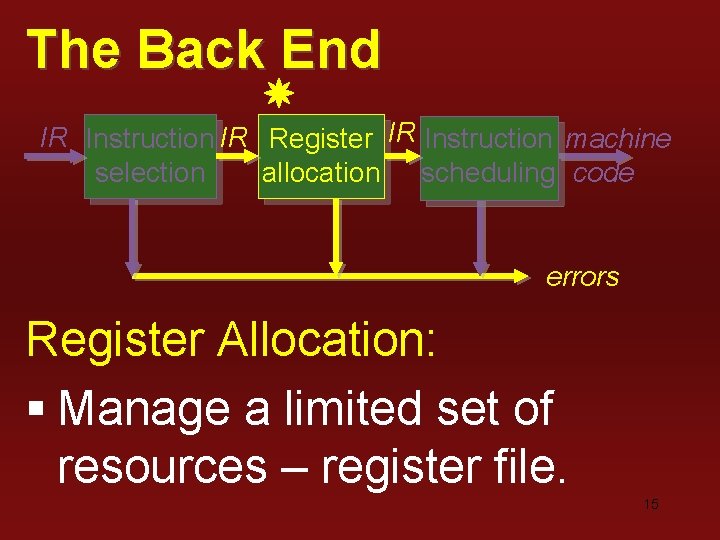

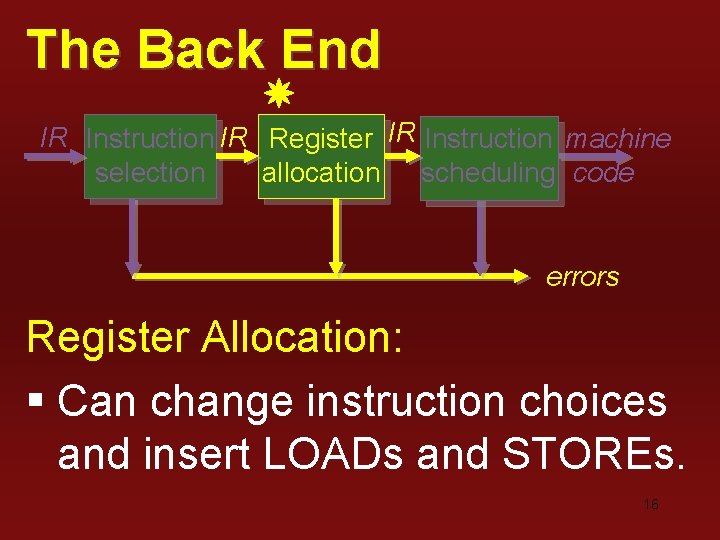

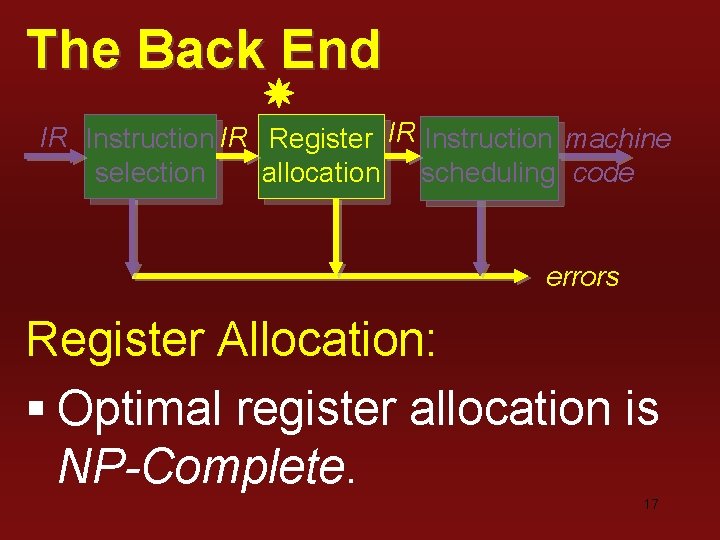

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Register Allocation: § Have each value in a register when it is used. 14

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Register Allocation: § Manage a limited set of resources – register file. 15

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Register Allocation: § Can change instruction choices and insert LOADs and STOREs. 16

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Register Allocation: § Optimal register allocation is NP-Complete. 17

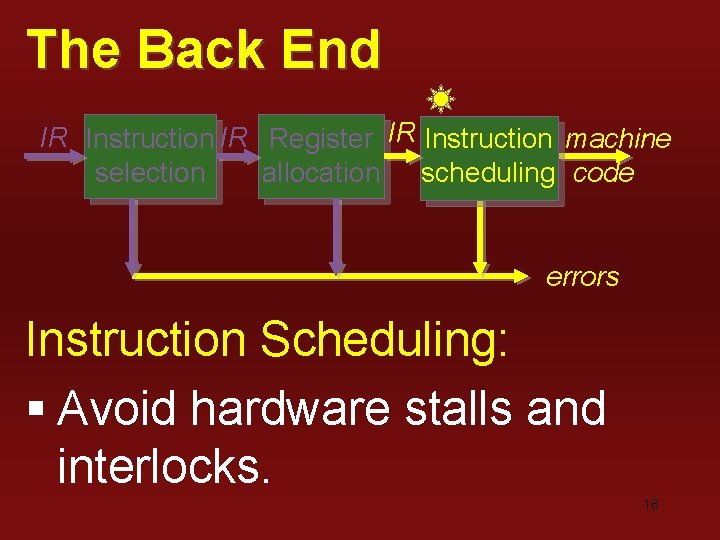

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Scheduling: § Avoid hardware stalls and interlocks. 18

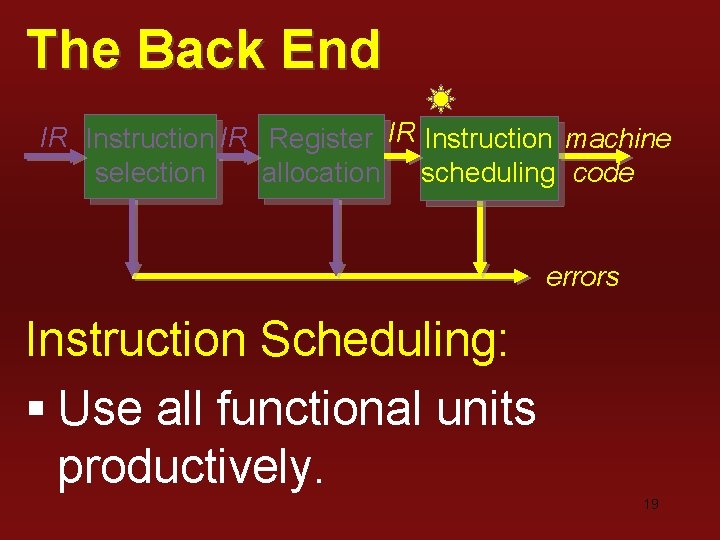

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Scheduling: § Use all functional units productively. 19

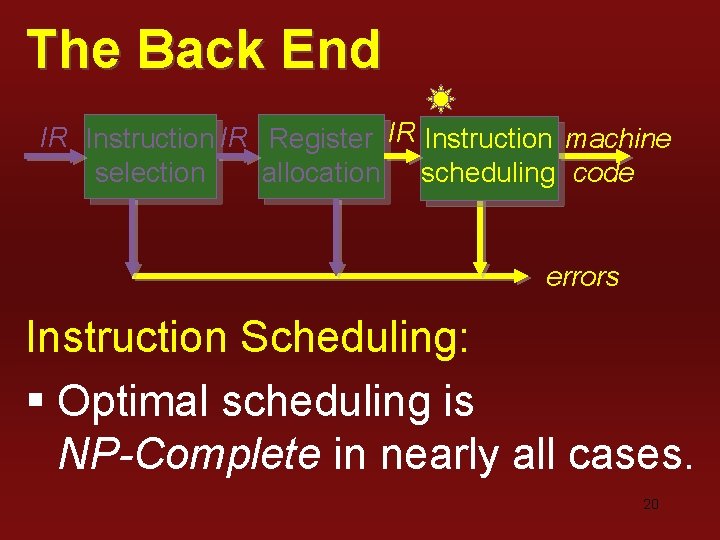

The Back End IR Instruction IR Register IR Instruction machine selection allocation scheduling code errors Instruction Scheduling: § Optimal scheduling is NP-Complete in nearly all cases. 20

- Slides: 20