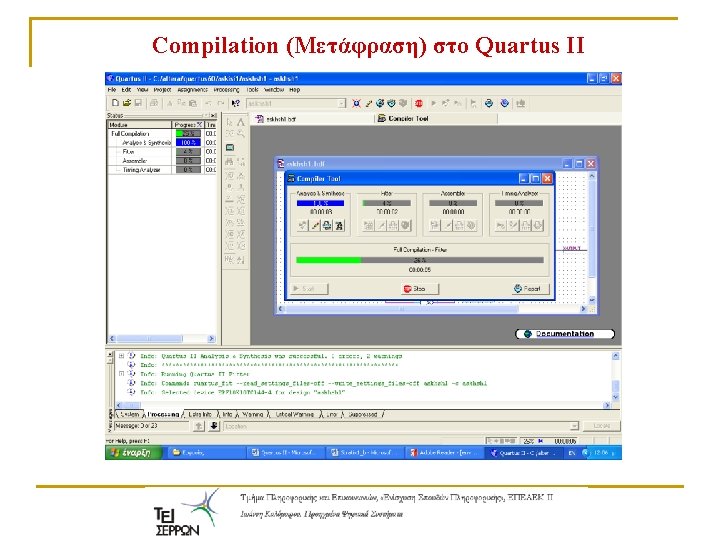

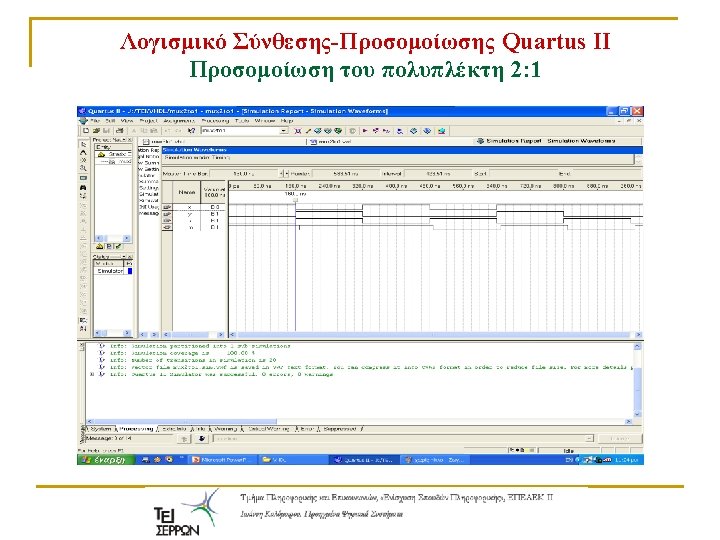

Compilation Quartus II 2 1 VHDL LIBRARY ieee

Compilation (Μετάφραση) στο Quartus II

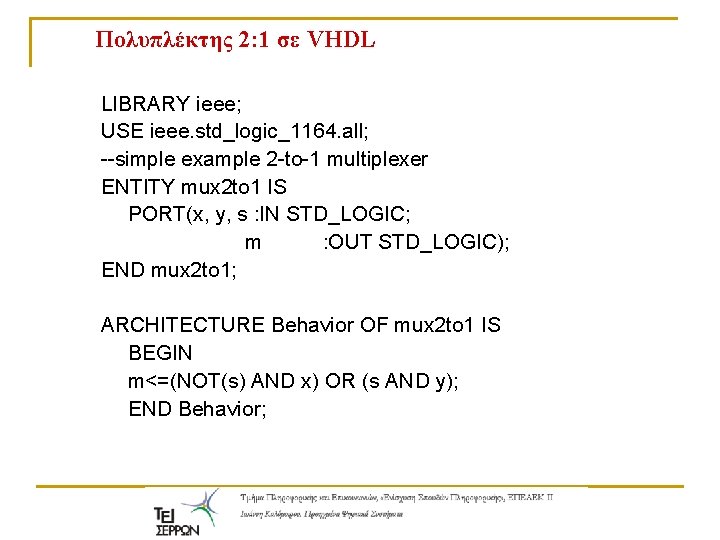

Πολυπλέκτης 2: 1 σε VHDL LIBRARY ieee; USE ieee. std_logic_1164. all; --simple example 2 -to-1 multiplexer ENTITY mux 2 to 1 IS PORT(x, y, s : IN STD_LOGIC; m : OUT STD_LOGIC); END mux 2 to 1; ARCHITECTURE Behavior OF mux 2 to 1 IS BEGIN m<=(NOT(s) AND x) OR (s AND y); END Behavior;

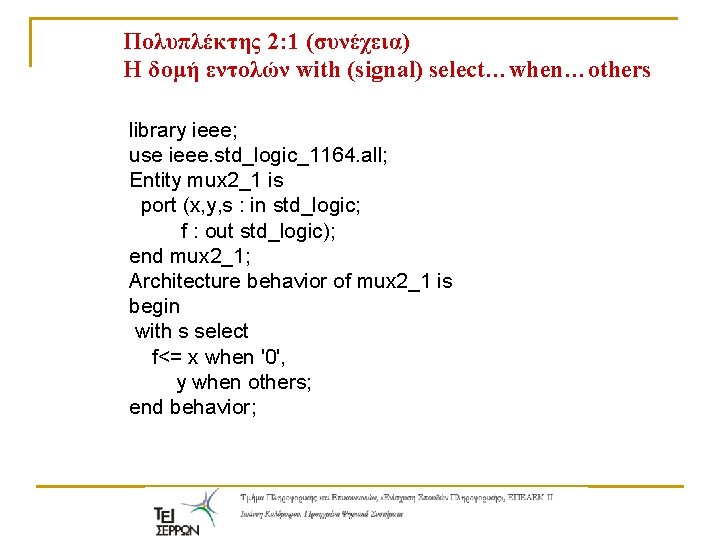

Πολυπλέκτης 2: 1 (συνέχεια) Η δομή εντολών with (signal) select…when…others library ieee; use ieee. std_logic_1164. all; Εntity mux 2_1 is port (x, y, s : in std_logic; f : out std_logic); end mux 2_1; Αrchitecture behavior of mux 2_1 is begin with s select f<= x when '0', y when others; end behavior;

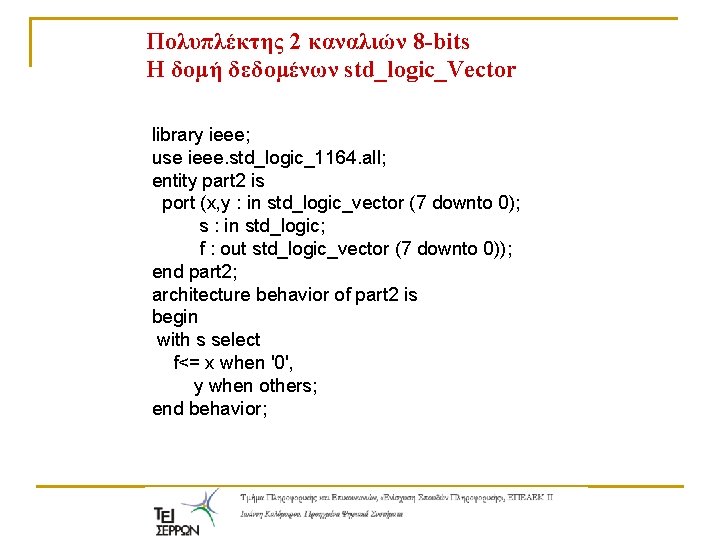

Πολυπλέκτης 2 καναλιών 8 -bits H δομή δεδομένων std_logic_Vector library ieee; use ieee. std_logic_1164. all; entity part 2 is port (x, y : in std_logic_vector (7 downto 0); s : in std_logic; f : out std_logic_vector (7 downto 0)); end part 2; architecture behavior of part 2 is begin with s select f<= x when '0', y when others; end behavior;

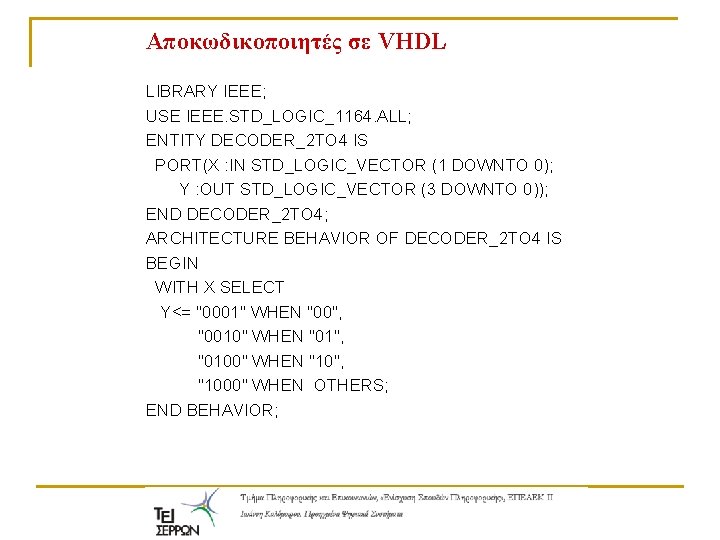

Αποκωδικοποιητές σε VHDL LIBRARY IEEE; USE IEEE. STD_LOGIC_1164. ALL; ENTITY DECODER_2 TO 4 IS PORT(X : IN STD_LOGIC_VECTOR (1 DOWNTO 0); Y : OUT STD_LOGIC_VECTOR (3 DOWNTO 0)); END DECODER_2 TO 4; ARCHITECTURE BEHAVIOR OF DECODER_2 TO 4 IS BEGIN WITH X SELECT Y<= "0001" WHEN "00", "0010" WHEN "01", "0100" WHEN "10", "1000" WHEN OTHERS; END BEHAVIOR;

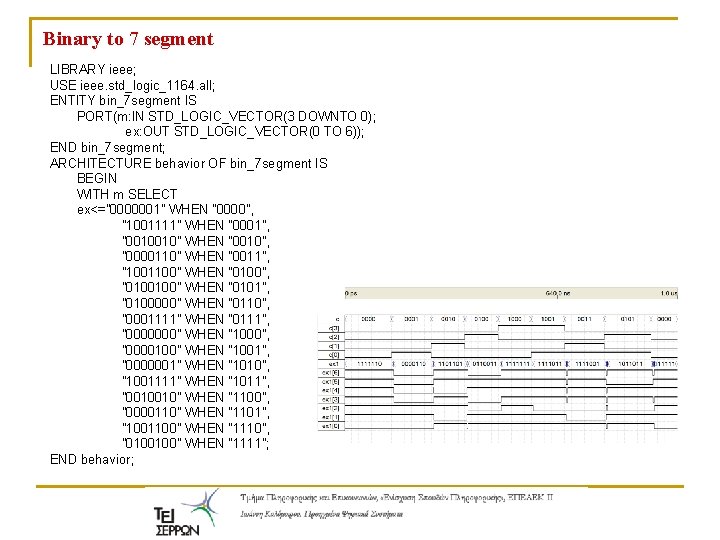

Binary to 7 segment LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY bin_7 segment IS PORT(m: IN STD_LOGIC_VECTOR(3 DOWNTO 0); ex: OUT STD_LOGIC_VECTOR(0 TO 6)); END bin_7 segment; ARCHITECTURE behavior OF bin_7 segment IS BEGIN WITH m SELECT ex<="0000001" WHEN "0000", "1001111" WHEN "0001", "0010010" WHEN "0010", "0000110" WHEN "0011", "1001100" WHEN "0100", "0100100" WHEN "0101", "0100000" WHEN "0110", "0001111" WHEN "0111", "0000000" WHEN "1000", "0000100" WHEN "1001", "0000001" WHEN "1010", "1001111" WHEN "1011", "0010010" WHEN "1100", "0000110" WHEN "1101", "1001100" WHEN "1110", "0100100" WHEN "1111"; END behavior;

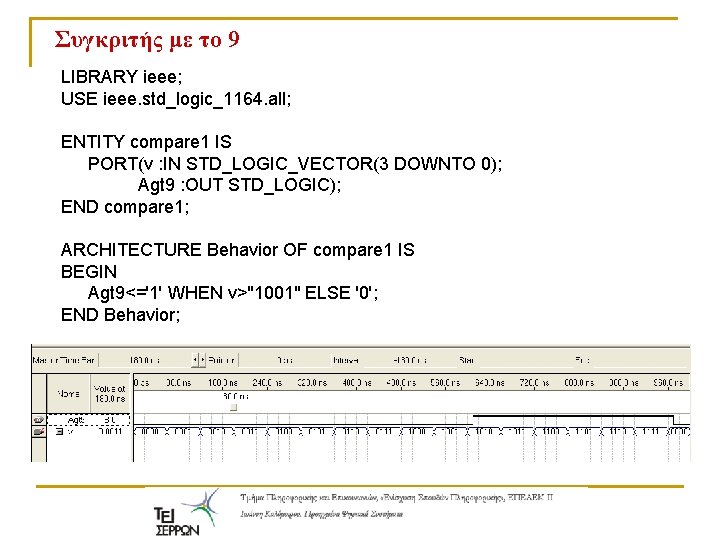

Συγκριτής με το 9 LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY compare 1 IS PORT(v : IN STD_LOGIC_VECTOR(3 DOWNTO 0); Agt 9 : OUT STD_LOGIC); END compare 1; ARCHITECTURE Behavior OF compare 1 IS BEGIN Agt 9<='1' WHEN v>"1001" ELSE '0'; END Behavior;

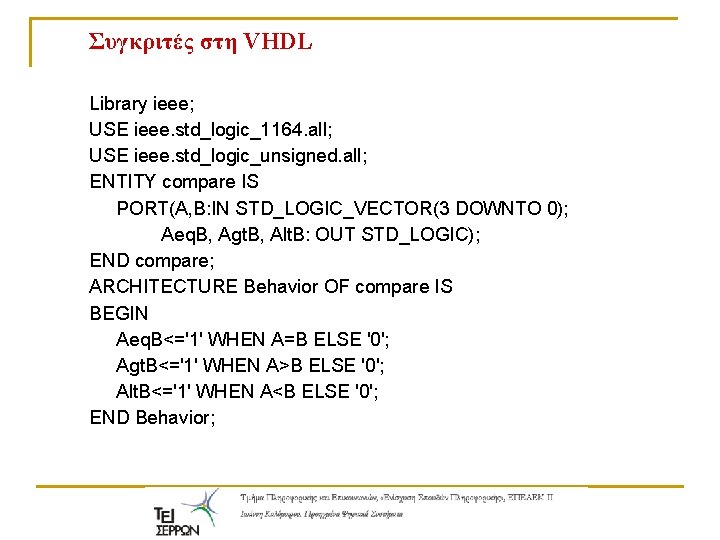

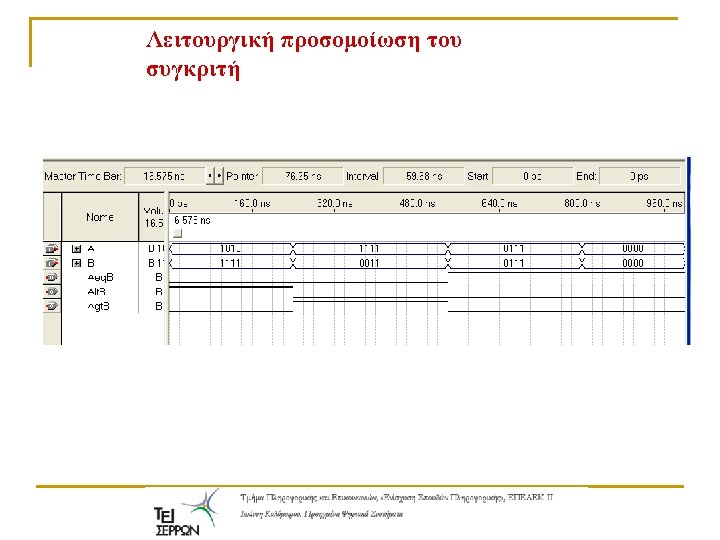

Συγκριτές στη VHDL Library ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_unsigned. all; ENTITY compare IS PORT(A, B: IN STD_LOGIC_VECTOR(3 DOWNTO 0); Aeq. B, Agt. B, Alt. B: OUT STD_LOGIC); END compare; ARCHITECTURE Behavior OF compare IS BEGIN Aeq. B<='1' WHEN A=B ELSE '0'; Agt. B<='1' WHEN A>B ELSE '0'; Alt. B<='1' WHEN A<B ELSE '0'; END Behavior;

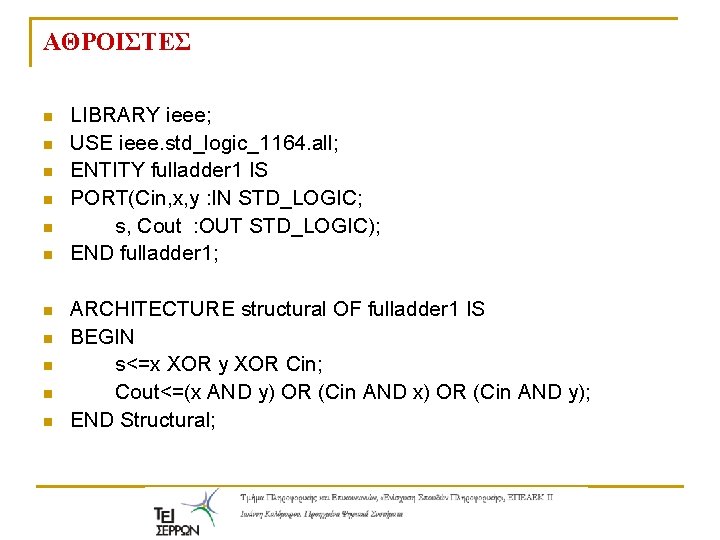

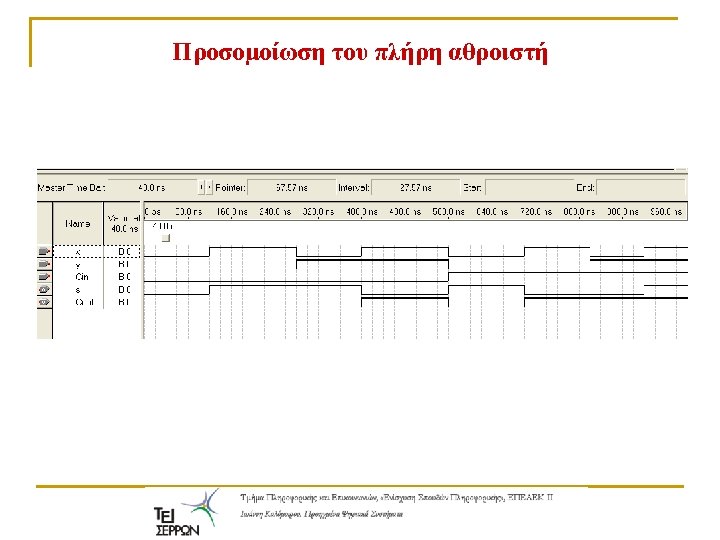

ΑΘΡΟΙΣΤΕΣ n n n LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY fulladder 1 IS PORT(Cin, x, y : IN STD_LOGIC; s, Cout : OUT STD_LOGIC); END fulladder 1; ARCHITECTURE structural OF fulladder 1 IS BEGIN s<=x XOR y XOR Cin; Cout<=(x AND y) OR (Cin AND x) OR (Cin AND y); END Structural;

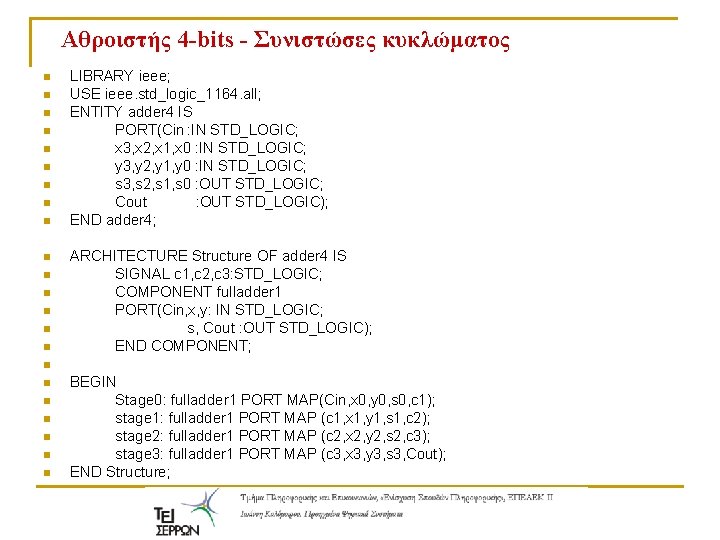

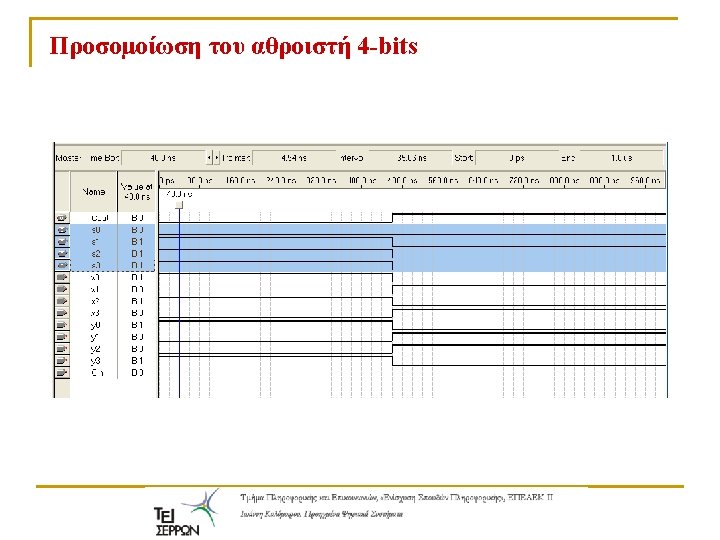

Αθροιστής 4 -bits - Συνιστώσες κυκλώματος n n n n LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY adder 4 IS PORT(Cin : IN STD_LOGIC; x 3, x 2, x 1, x 0 : IN STD_LOGIC; y 3, y 2, y 1, y 0 : IN STD_LOGIC; s 3, s 2, s 1, s 0 : OUT STD_LOGIC; Cout : OUT STD_LOGIC); END adder 4; ARCHITECTURE Structure OF adder 4 IS SIGNAL c 1, c 2, c 3: STD_LOGIC; COMPONENT fulladder 1 PORT(Cin, x, y: IN STD_LOGIC; s, Cout : OUT STD_LOGIC); END COMPONENT; n n n n BEGIN Stage 0: fulladder 1 PORT MAP(Cin, x 0, y 0, s 0, c 1); stage 1: fulladder 1 PORT MAP (c 1, x 1, y 1, s 1, c 2); stage 2: fulladder 1 PORT MAP (c 2, x 2, y 2, s 2, c 3); stage 3: fulladder 1 PORT MAP (c 3, x 3, y 3, s 3, Cout); END Structure;

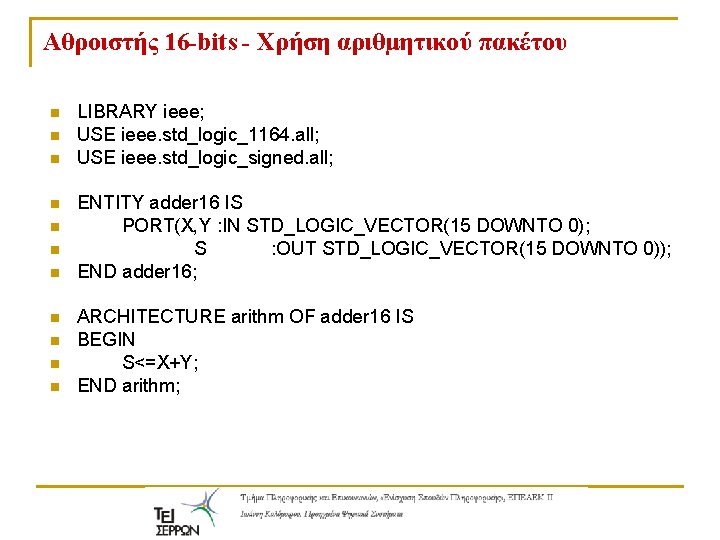

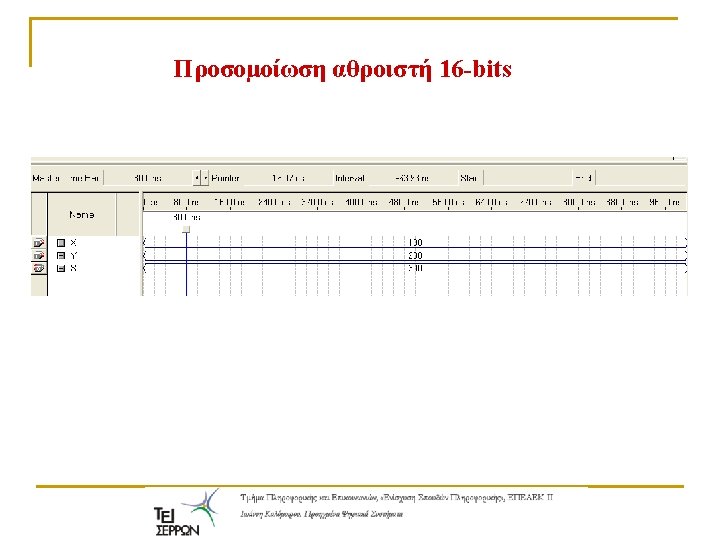

Aθροιστής 16 -bits - Χρήση αριθμητικού πακέτου n n n LIBRARY ieee; USE ieee. std_logic_1164. all; USE ieee. std_logic_signed. all; ENTITY adder 16 IS PORT(X, Y : IN STD_LOGIC_VECTOR(15 DOWNTO 0); S : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)); END adder 16; ARCHITECTURE arithm OF adder 16 IS BEGIN S<=X+Y; END arithm;

- Slides: 21