Comparison Study of Bulk and SOI CMOS Technologies

Comparison Study of Bulk and SOI CMOS Technologies based Rad-hard ADCs in Space Feitao Qi , Tao Liu , Hainan Liu , Chuanbin Zeng , Bo Li , Fazhan Zhao , Jiantou Gao , Gang Zhang , Jiajun Luo , Zhengsheng Han , and Zhongli Liu Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, CHINA Key Laboratory of Silicon Device Technology, Chinese Academy of Sciences, Beijing 100029, CHINA AMICSA 2016 -6 -14 1

Overview IMECAS • INTRODUCTION • SYSTEM ARCHITECTURE • CIRCUITS DESIGN • HARDENED APPROACHES • EXPERIMENTAL RESULTS • CONCLUSION AMICSA 2016 -6 -14 2

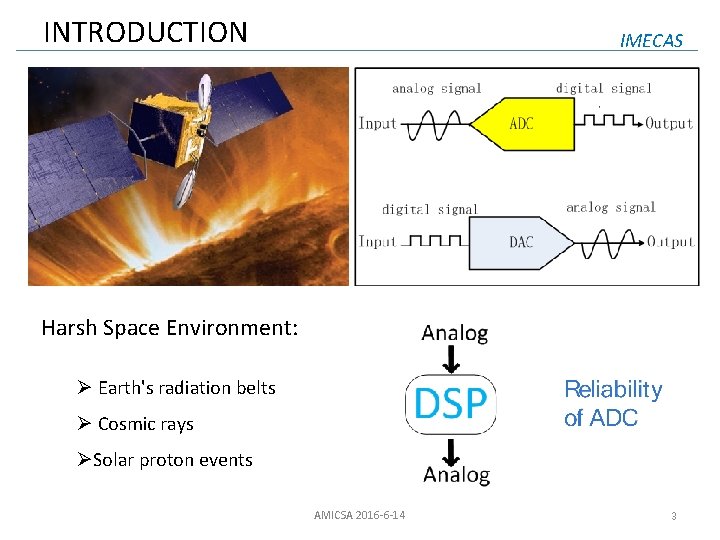

INTRODUCTION IMECAS Harsh Space Environment: Ø Earth's radiation belts Ø Cosmic rays ØSolar proton events AMICSA 2016 -6 -14 3

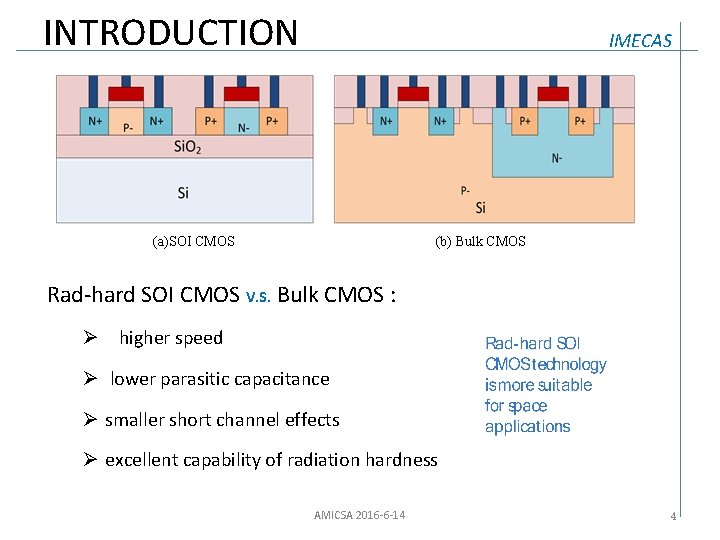

INTRODUCTION IMECAS (a)SOI CMOS (b) Bulk CMOS Rad-hard SOI CMOS V. S. Bulk CMOS : Ø higher speed Ø lower parasitic capacitance Ø smaller short channel effects Ø excellent capability of radiation hardness AMICSA 2016 -6 -14 4

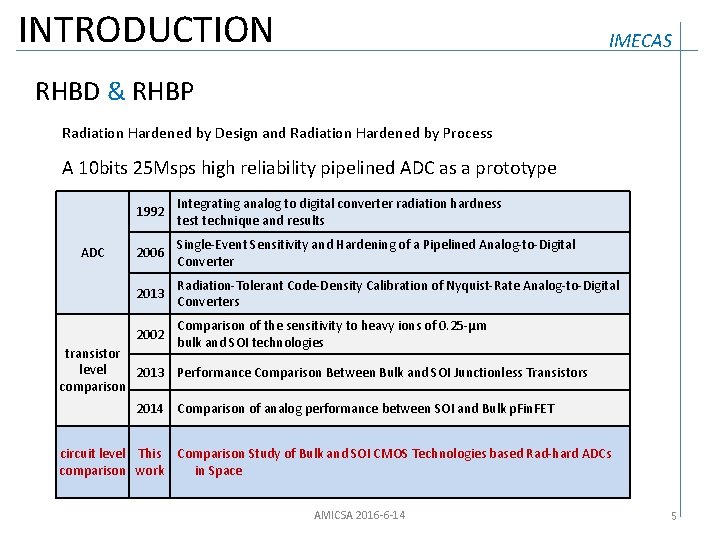

INTRODUCTION IMECAS RHBD & RHBP Radiation Hardened by Design and Radiation Hardened by Process A 10 bits 25 Msps high reliability pipelined ADC as a prototype ADC 1992 Integrating analog to digital converter radiation hardness test technique and results 2006 Single-Event Sensitivity and Hardening of a Pipelined Analog-to-Digital Converter 2013 Radiation-Tolerant Code-Density Calibration of Nyquist-Rate Analog-to-Digital Converters 2002 Comparison of the sensitivity to heavy ions of 0. 25 -μm bulk and SOI technologies transistor level 2013 Performance Comparison Between Bulk and SOI Junctionless Transistors comparison 2014 Comparison of analog performance between SOI and Bulk p. Fin. FET circuit level This Comparison Study of Bulk and SOI CMOS Technologies based Rad-hard ADCs comparison work in Space AMICSA 2016 -6 -14 5

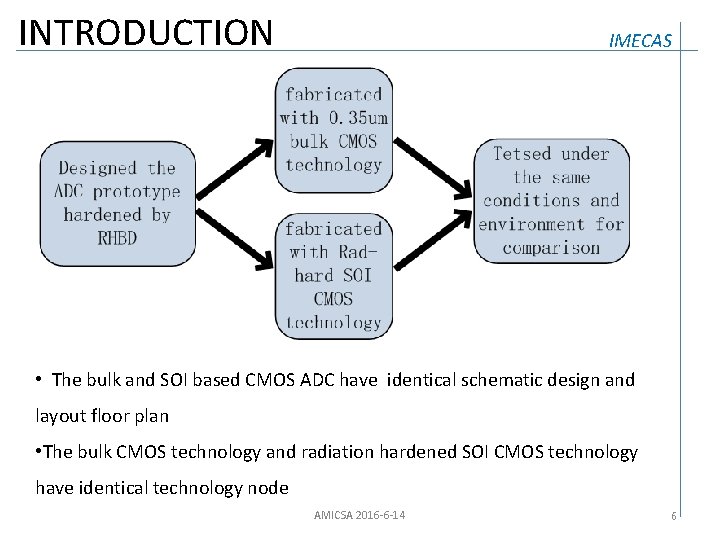

INTRODUCTION IMECAS • The bulk and SOI based CMOS ADC have identical schematic design and layout floor plan • The bulk CMOS technology and radiation hardened SOI CMOS technology have identical technology node AMICSA 2016 -6 -14 6

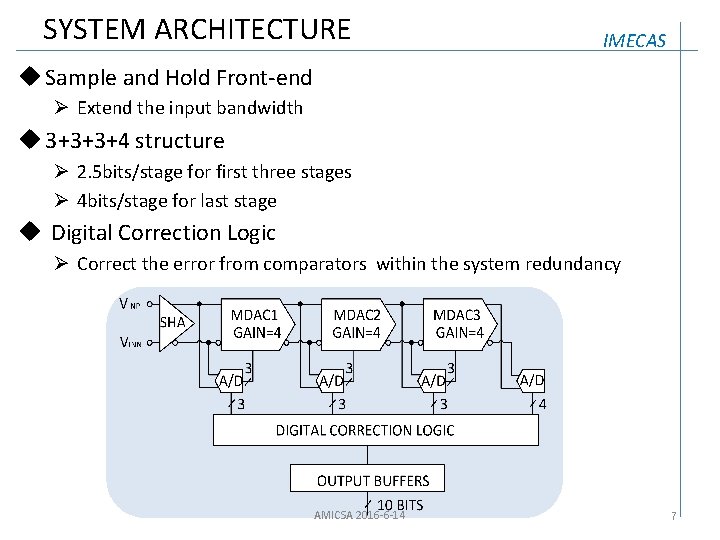

SYSTEM ARCHITECTURE IMECAS u Sample and Hold Front-end Ø Extend the input bandwidth u 3+3+3+4 structure Ø 2. 5 bits/stage for first three stages Ø 4 bits/stage for last stage u Digital Correction Logic Ø Correct the error from comparators within the system redundancy AMICSA 2016 -6 -14 7

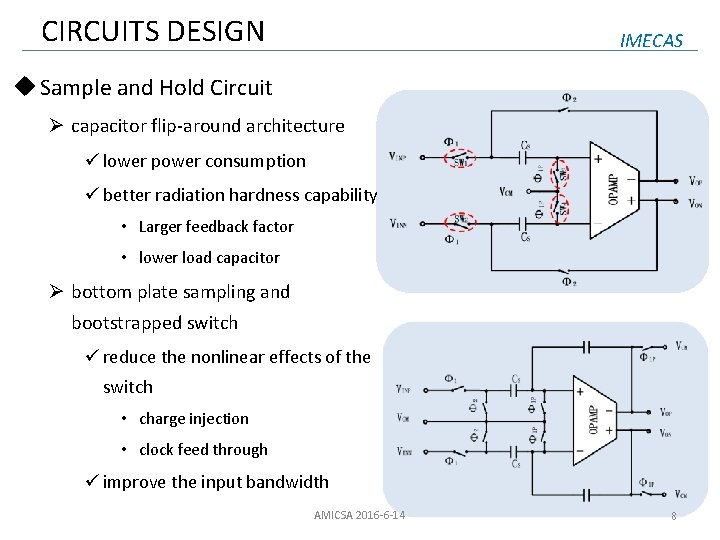

CIRCUITS DESIGN IMECAS u Sample and Hold Circuit Ø capacitor flip-around architecture ü lower power consumption ü better radiation hardness capability • Larger feedback factor • lower load capacitor Ø bottom plate sampling and bootstrapped switch ü reduce the nonlinear effects of the switch • charge injection • clock feed through ü improve the input bandwidth AMICSA 2016 -6 -14 8

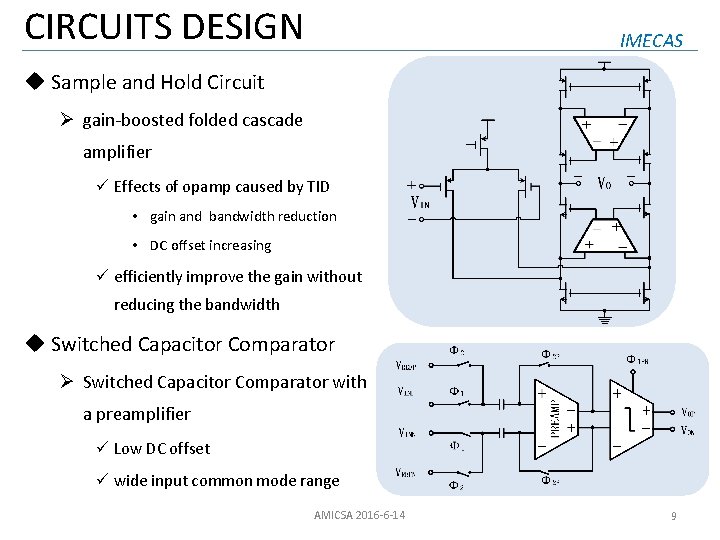

CIRCUITS DESIGN IMECAS u Sample and Hold Circuit Ø gain-boosted folded cascade amplifier ü Effects of opamp caused by TID • gain and bandwidth reduction • DC offset increasing ü efficiently improve the gain without reducing the bandwidth u Switched Capacitor Comparator Ø Switched Capacitor Comparator with a preamplifier ü Low DC offset ü wide input common mode range AMICSA 2016 -6 -14 9

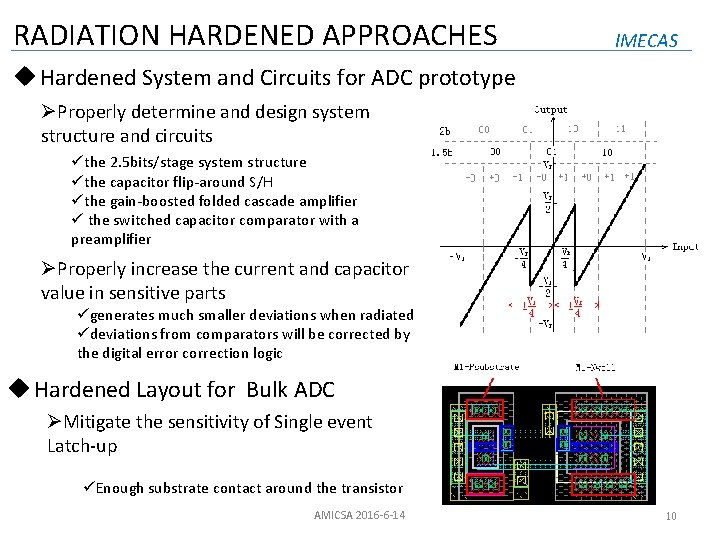

RADIATION HARDENED APPROACHES IMECAS u Hardened System and Circuits for ADC prototype ØProperly determine and design system structure and circuits üthe 2. 5 bits/stage system structure üthe capacitor flip-around S/H üthe gain-boosted folded cascade amplifier ü the switched capacitor comparator with a preamplifier ØProperly increase the current and capacitor value in sensitive parts ügenerates much smaller deviations when radiated üdeviations from comparators will be corrected by the digital error correction logic u Hardened Layout for Bulk ADC ØMitigate the sensitivity of Single event Latch-up üEnough substrate contact around the transistor AMICSA 2016 -6 -14 10

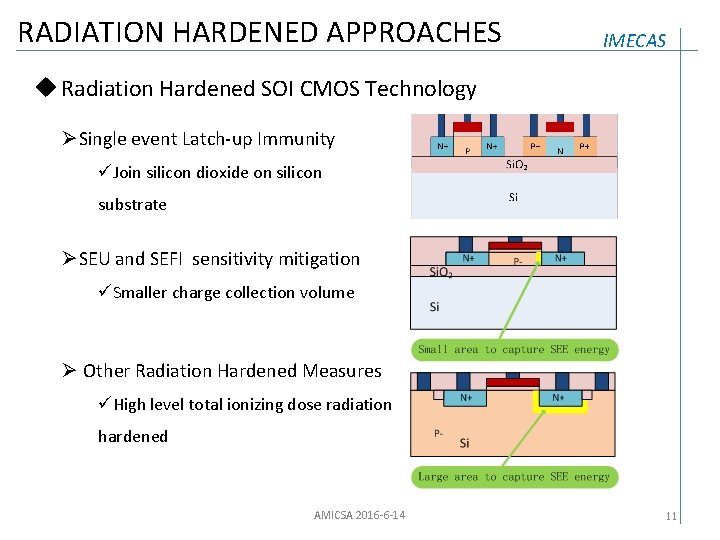

RADIATION HARDENED APPROACHES IMECAS u Radiation Hardened SOI CMOS Technology ØSingle event Latch-up Immunity üJoin silicon dioxide on silicon substrate ØSEU and SEFI sensitivity mitigation üSmaller charge collection volume Ø Other Radiation Hardened Measures üHigh level total ionizing dose radiation hardened AMICSA 2016 -6 -14 11

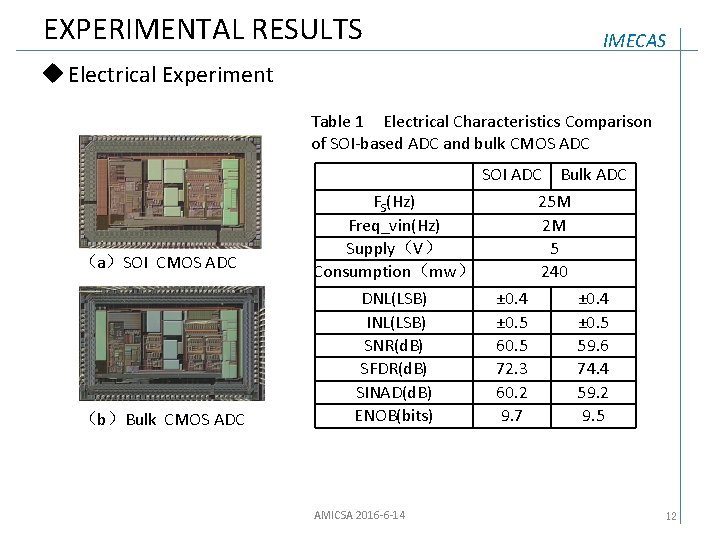

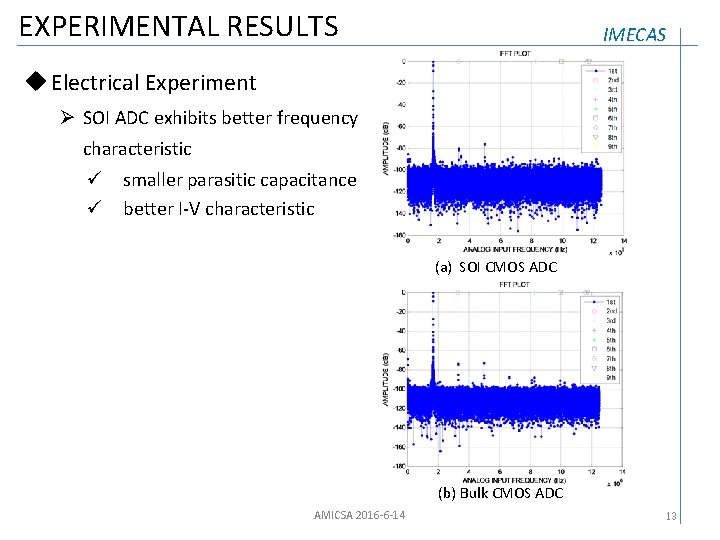

EXPERIMENTAL RESULTS IMECAS u Electrical Experiment Table 1 Electrical Characteristics Comparison of SOI-based ADC and bulk CMOS ADC SOI ADC (a)SOI CMOS ADC (b)Bulk CMOS ADC FS(Hz) Freq_vin(Hz) Supply(V) Consumption(mw) DNL(LSB) INL(LSB) SNR(d. B) SFDR(d. B) SINAD(d. B) ENOB(bits) AMICSA 2016 -6 -14 Bulk ADC 25 M 2 M 5 240 ± 0. 4 ± 0. 5 60. 5 72. 3 60. 2 9. 7 ± 0. 4 ± 0. 5 59. 6 74. 4 59. 2 9. 5 12

EXPERIMENTAL RESULTS IMECAS u Electrical Experiment Ø SOI ADC exhibits better frequency characteristic ü smaller parasitic capacitance ü better I-V characteristic (a) SOI CMOS ADC (b) Bulk CMOS ADC AMICSA 2016 -6 -14 13

EXPERIMENTAL RESULTS IMECAS u. TID Experiment ØExperiment conditions üRadiation • • • Cobalt-60 gamma radiation source at the room temperature static bias state dose rate of 50 rad(Si)/s irradiated to 500 krad(Si) üAnneal • static bias state • 168 hours • at 100℃ ØMeasure point üpre-radiation, 50 k, 100 k, 150 k, 300 k, 500 krad(Si) and after anneal AMICSA 2016 -6 -14 14

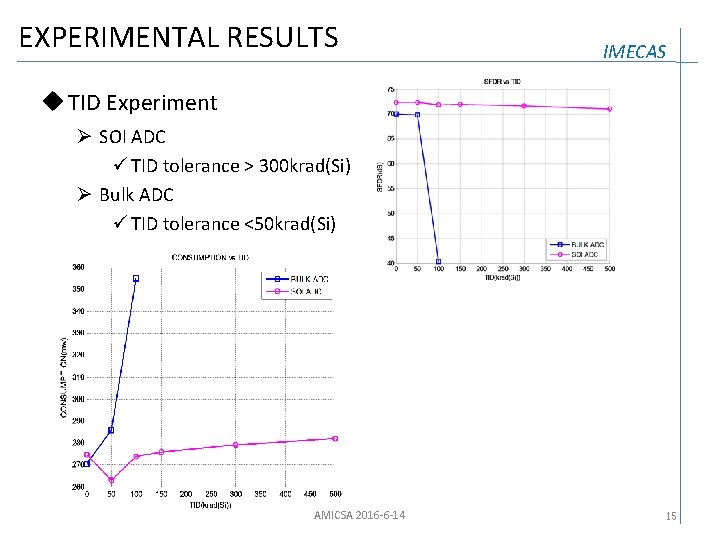

EXPERIMENTAL RESULTS IMECAS u TID Experiment Ø SOI ADC ü TID tolerance > 300 krad(Si) Ø Bulk ADC ü TID tolerance <50 krad(Si) AMICSA 2016 -6 -14 15

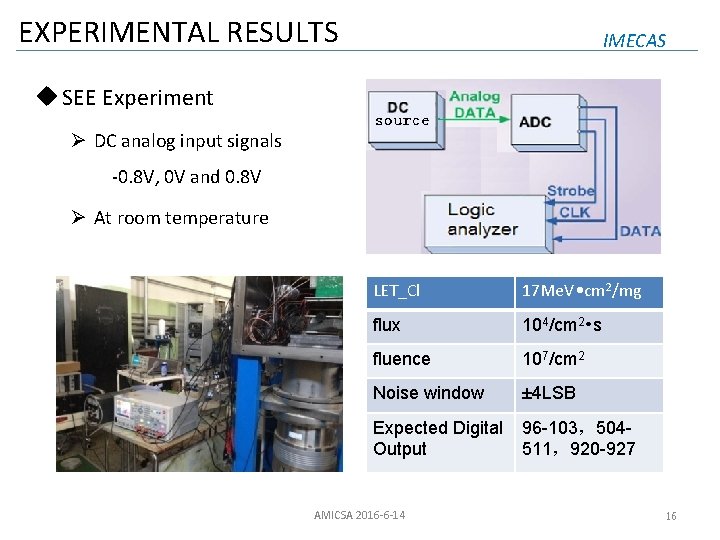

EXPERIMENTAL RESULTS IMECAS u SEE Experiment Ø DC analog input signals -0. 8 V, 0 V and 0. 8 V Ø At room temperature LET_Cl 17 Me. V • cm 2/mg flux 104/cm 2 • s fluence 107/cm 2 Noise window ± 4 LSB Expected Digital Output 96 -103,504511,920 -927 AMICSA 2016 -6 -14 16

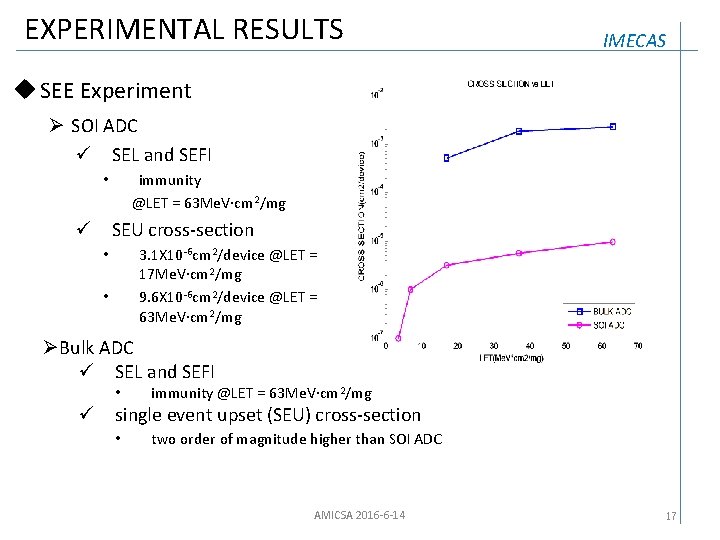

EXPERIMENTAL RESULTS IMECAS u SEE Experiment Ø SOI ADC ü SEL and SEFI • immunity @LET = 63 Me. V·cm 2/mg ü SEU cross-section 3. 1 X 10 -6 cm 2/device @LET = 17 Me. V·cm 2/mg 9. 6 X 10 -6 cm 2/device @LET = 63 Me. V·cm 2/mg • • ØBulk ADC ü SEL and SEFI • immunity @LET = 63 Me. V·cm 2/mg ü single event upset (SEU) cross-section • two order of magnitude higher than SOI ADC AMICSA 2016 -6 -14 17

CONCLUSION IMECAS In conclusion, by implementing simple RHBD approaches and taking the inherent advantage of the rad-hard SOI technology, the SOI-based ADC achieves the TID tolerance of 300 krad(Si) at least, nearly one order of magnitude higher than bulk ADC, and the SEU cross-section of 9. 6 X 106 cm 2/device at 63 Me. V·cm 2/mg LET, lower than bulk ADC by two orders of magnitude, more suitable for harsh radiation environment applications. AMICSA 2016 -6 -14 18

- Slides: 18