Comparison of fullband Monte Carlo and Nonequilibrium Greens

Comparison of full-band Monte Carlo and Non-equilibrium Green’s function simulations Ranganathan Ravishankar, Gulzar Kathawala, Umberto Ravaioli University of Illinois, Urbana-Champaign Collaboration with Sayed Hasan and Mark Lundstrom Purdue University International Workshop on Computational Electronics - 10 Oct 26, 2004 1

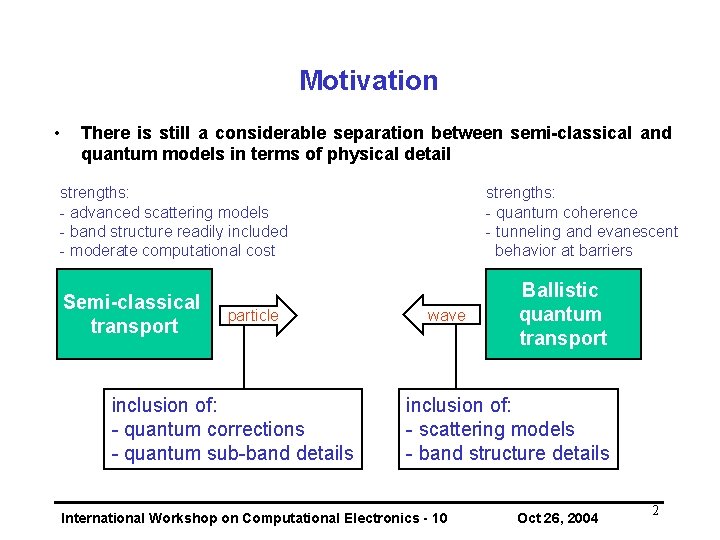

Motivation • There is still a considerable separation between semi-classical and quantum models in terms of physical detail strengths: - advanced scattering models - band structure readily included - moderate computational cost Semi-classical transport particle inclusion of: - quantum corrections - quantum sub-band details strengths: - quantum coherence - tunneling and evanescent behavior at barriers wave Ballistic quantum transport inclusion of: - scattering models - band structure details International Workshop on Computational Electronics - 10 Oct 26, 2004 2

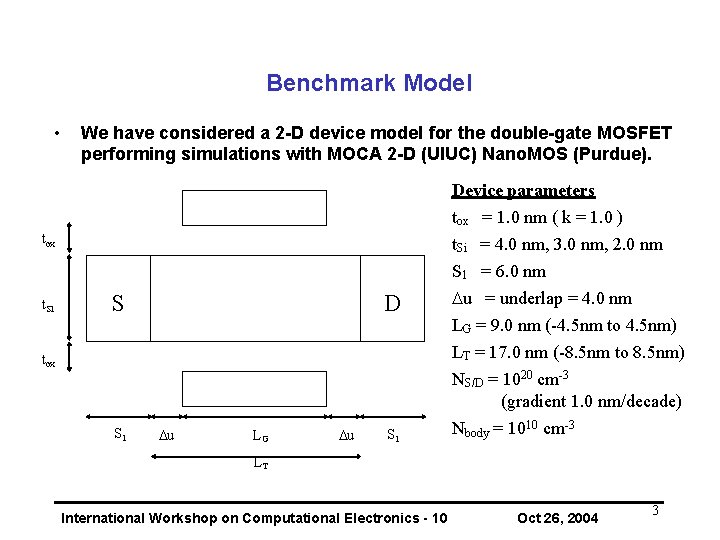

Benchmark Model • We have considered a 2 -D device model for the double-gate MOSFET performing simulations with MOCA 2 -D (UIUC) Nano. MOS (Purdue). tox t. SI S D tox S 1 u LG u S 1 Device parameters tox = 1. 0 nm ( k = 1. 0 ) t. Si = 4. 0 nm, 3. 0 nm, 2. 0 nm S 1 = 6. 0 nm u = underlap = 4. 0 nm LG = 9. 0 nm (-4. 5 nm to 4. 5 nm) LT = 17. 0 nm (-8. 5 nm to 8. 5 nm) NS/D = 1020 cm-3 (gradient 1. 0 nm/decade) Nbody = 1010 cm-3 LT International Workshop on Computational Electronics - 10 Oct 26, 2004 3

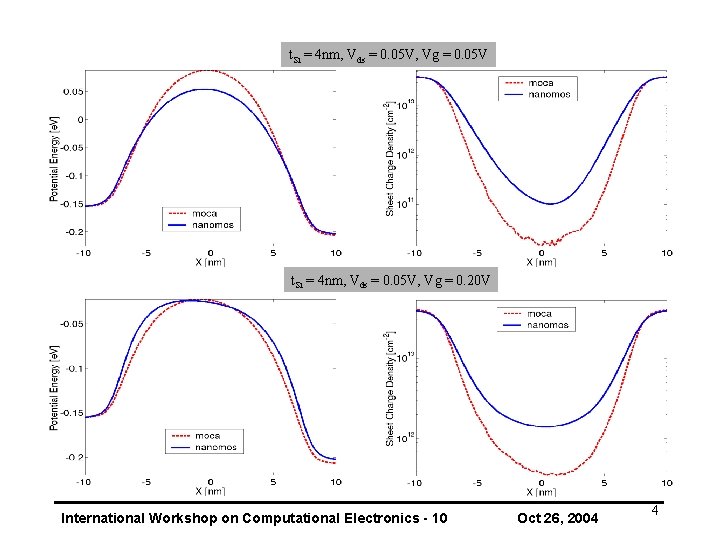

t. Si = 4 nm, Vds = 0. 05 V, Vg = 0. 05 V t. Si = 4 nm, Vds = 0. 05 V, Vg = 0. 20 V International Workshop on Computational Electronics - 10 Oct 26, 2004 4

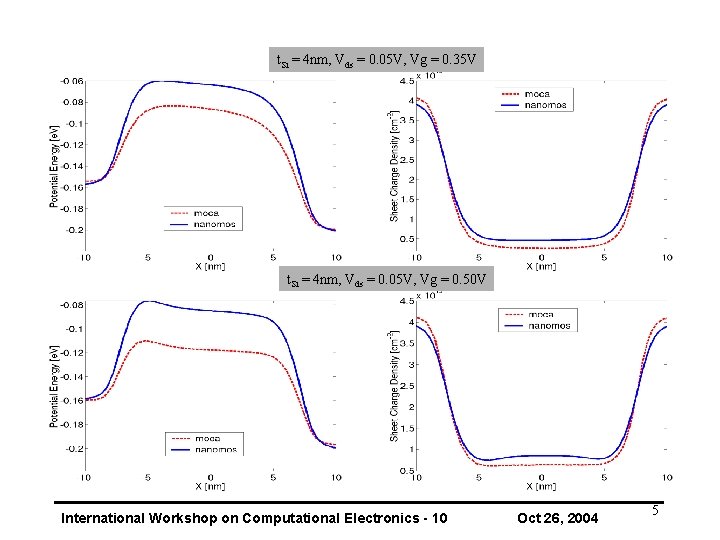

t. Si = 4 nm, Vds = 0. 05 V, Vg = 0. 35 V t. Si = 4 nm, Vds = 0. 05 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 5

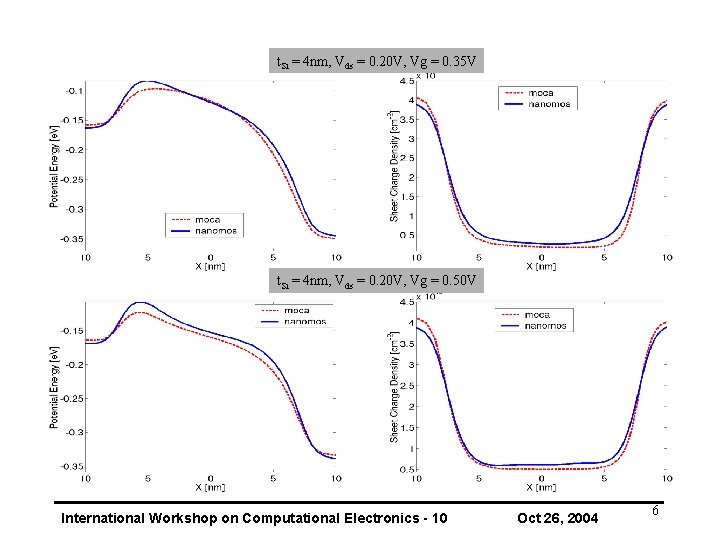

t. Si = 4 nm, Vds = 0. 20 V, Vg = 0. 35 V t. Si = 4 nm, Vds = 0. 20 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 6

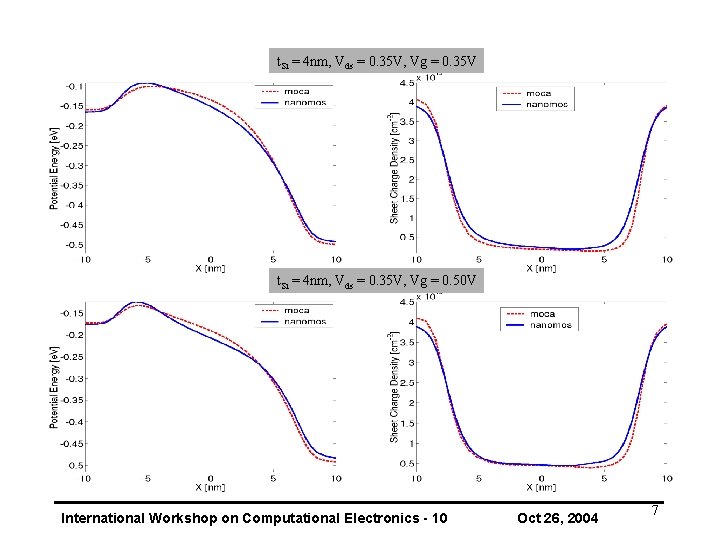

t. Si = 4 nm, Vds = 0. 35 V, Vg = 0. 35 V t. Si = 4 nm, Vds = 0. 35 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 7

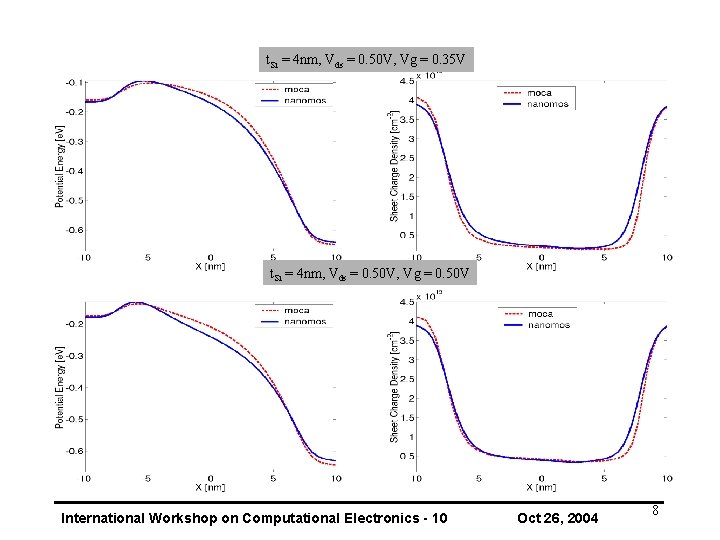

t. Si = 4 nm, Vds = 0. 50 V, Vg = 0. 35 V t. Si = 4 nm, Vds = 0. 50 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 8

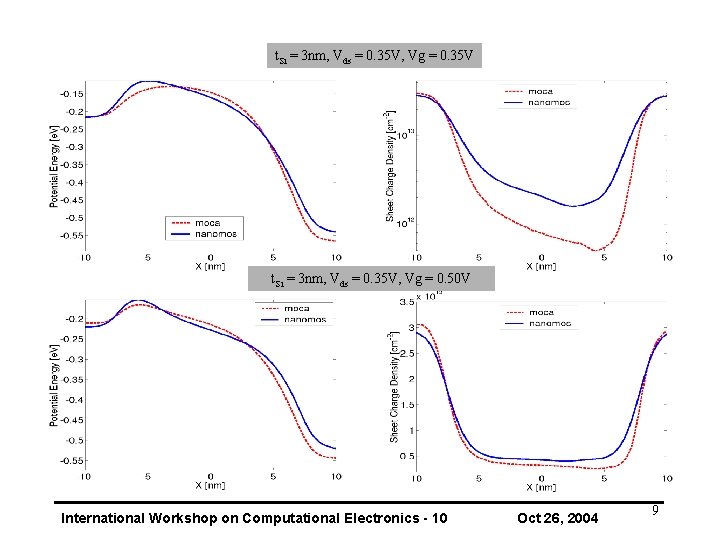

t. Si = 3 nm, Vds = 0. 35 V, Vg = 0. 35 V t. Si = 3 nm, Vds = 0. 35 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 9

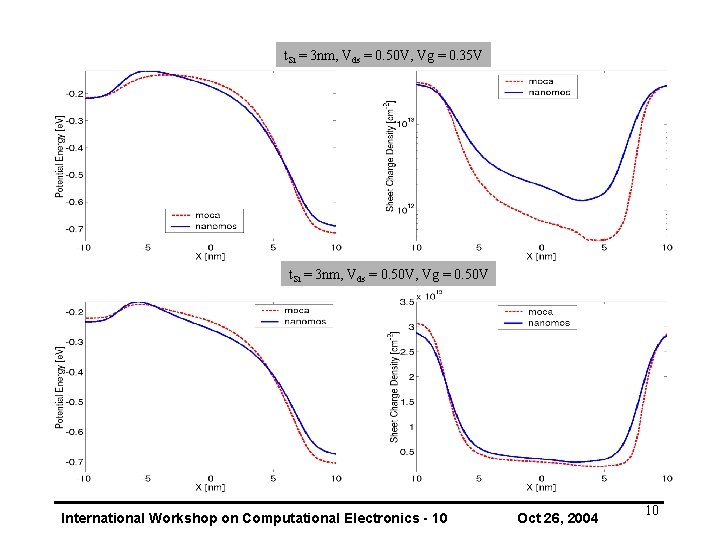

t. Si = 3 nm, Vds = 0. 50 V, Vg = 0. 35 V t. Si = 3 nm, Vds = 0. 50 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 10

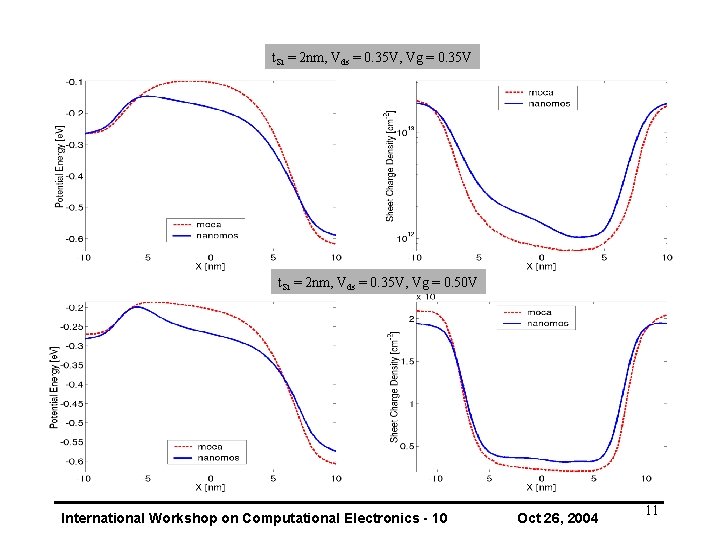

t. Si = 2 nm, Vds = 0. 35 V, Vg = 0. 35 V t. Si = 2 nm, Vds = 0. 35 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 11

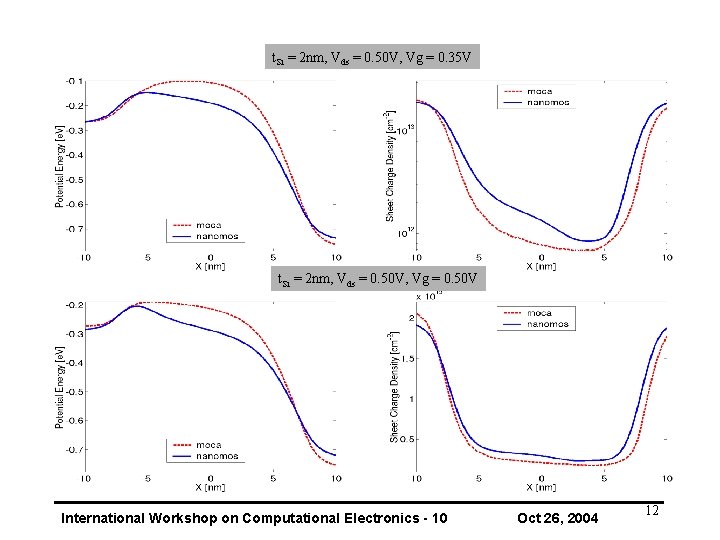

t. Si = 2 nm, Vds = 0. 50 V, Vg = 0. 35 V t. Si = 2 nm, Vds = 0. 50 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 12

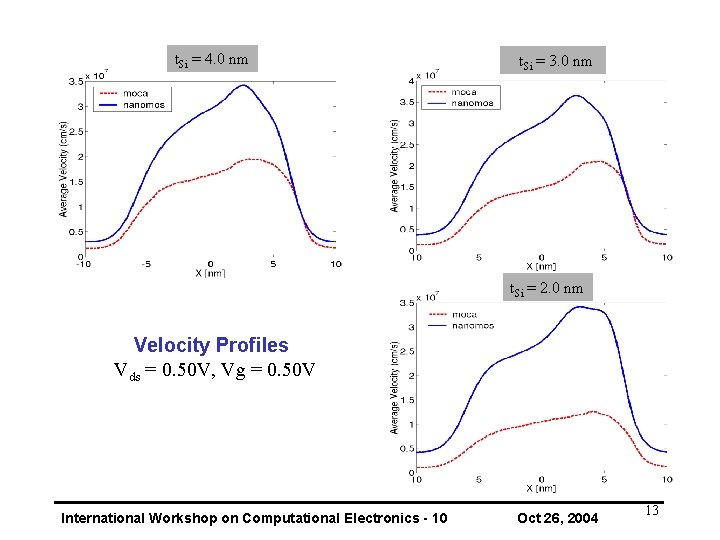

t. Si = 4. 0 nm t. Si = 3. 0 nm t. Si = 2. 0 nm Velocity Profiles Vds = 0. 50 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 13

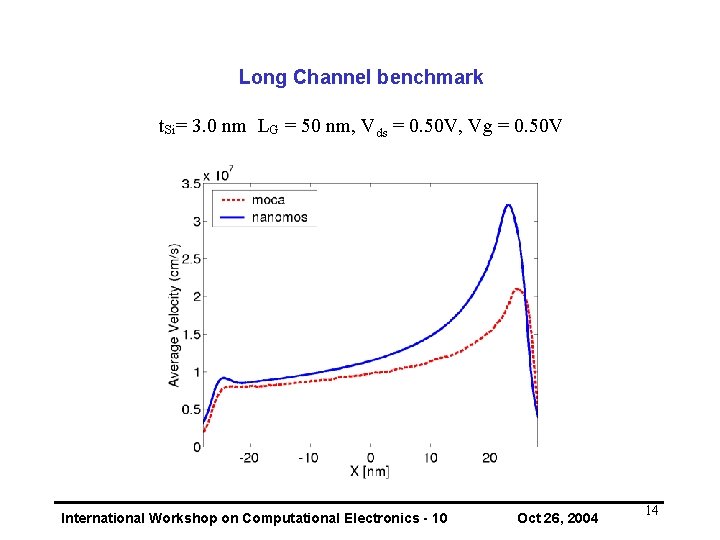

Long Channel benchmark t. Si= 3. 0 nm LG = 50 nm, Vds = 0. 50 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 14

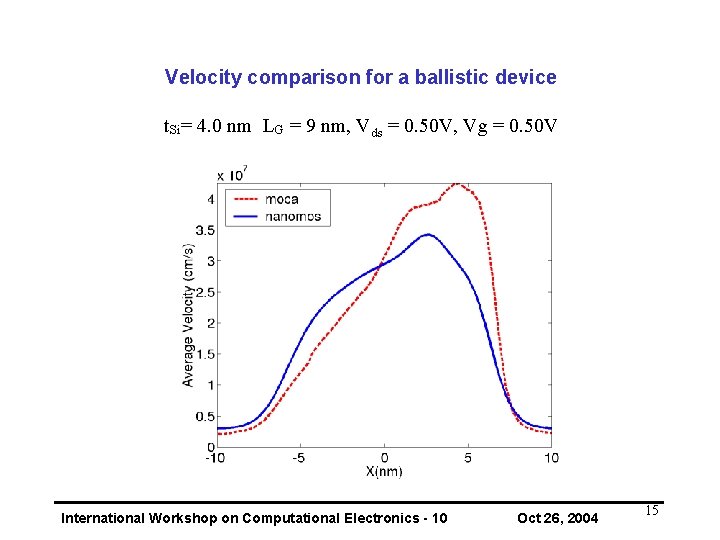

Velocity comparison for a ballistic device t. Si= 4. 0 nm LG = 9 nm, Vds = 0. 50 V, Vg = 0. 50 V International Workshop on Computational Electronics - 10 Oct 26, 2004 15

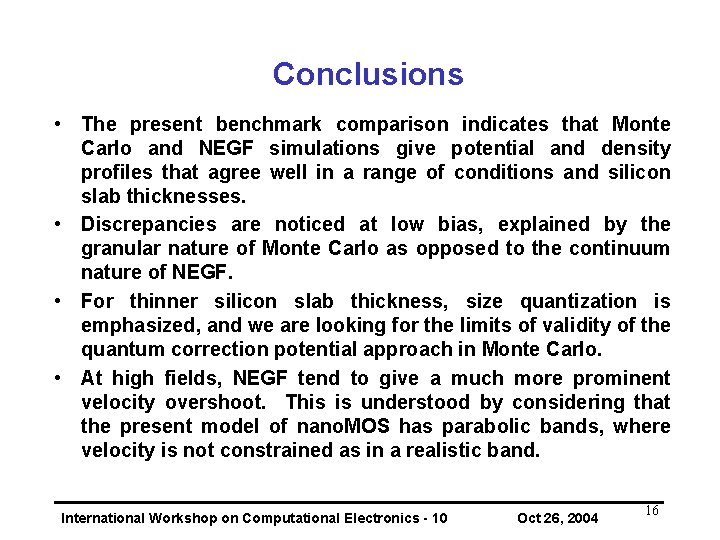

Conclusions • The present benchmark comparison indicates that Monte Carlo and NEGF simulations give potential and density profiles that agree well in a range of conditions and silicon slab thicknesses. • Discrepancies are noticed at low bias, explained by the granular nature of Monte Carlo as opposed to the continuum nature of NEGF. • For thinner silicon slab thickness, size quantization is emphasized, and we are looking for the limits of validity of the quantum correction potential approach in Monte Carlo. • At high fields, NEGF tend to give a much more prominent velocity overshoot. This is understood by considering that the present model of nano. MOS has parabolic bands, where velocity is not constrained as in a realistic band. International Workshop on Computational Electronics - 10 Oct 26, 2004 16

- Slides: 16