Comparing CPU Time CPU time Seconds Program Instructions

- Slides: 23

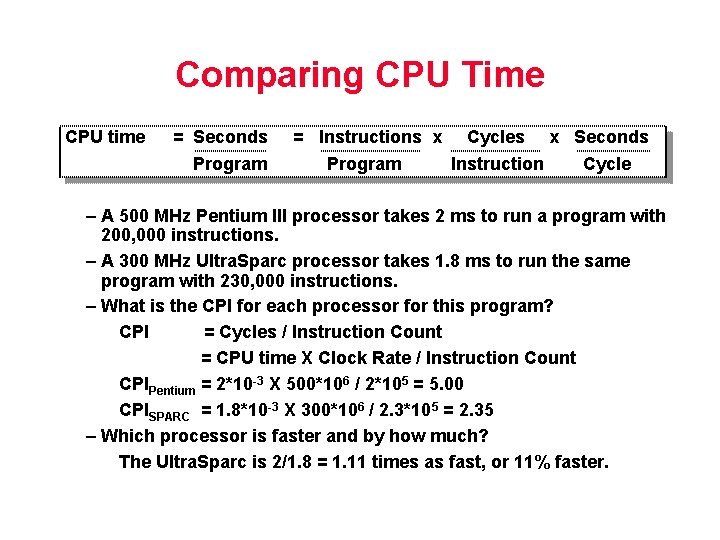

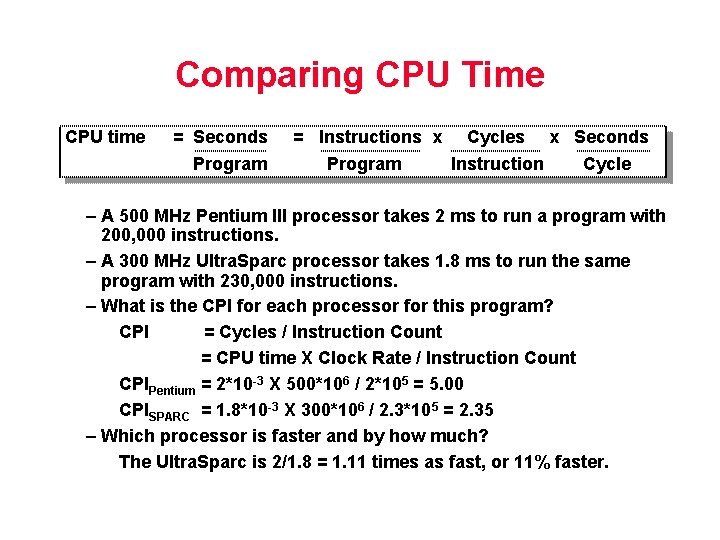

Comparing CPU Time CPU time = Seconds Program = Instructions x Cycles Program Instruction x Seconds Cycle – A 500 MHz Pentium III processor takes 2 ms to run a program with 200, 000 instructions. – A 300 MHz Ultra. Sparc processor takes 1. 8 ms to run the same program with 230, 000 instructions. – What is the CPI for each processor for this program? CPI = Cycles / Instruction Count = CPU time X Clock Rate / Instruction Count CPIPentium = 2*10 3 X 500*106 / 2*105 = 5. 00 CPISPARC = 1. 8*10 3 X 300*106 / 2. 3*105 = 2. 35 – Which processor is faster and by how much? The Ultra. Sparc is 2/1. 8 = 1. 11 times as fast, or 11% faster.

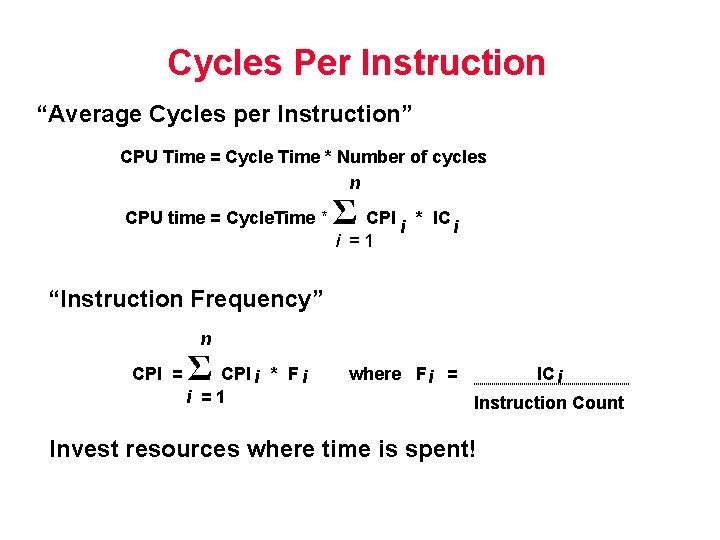

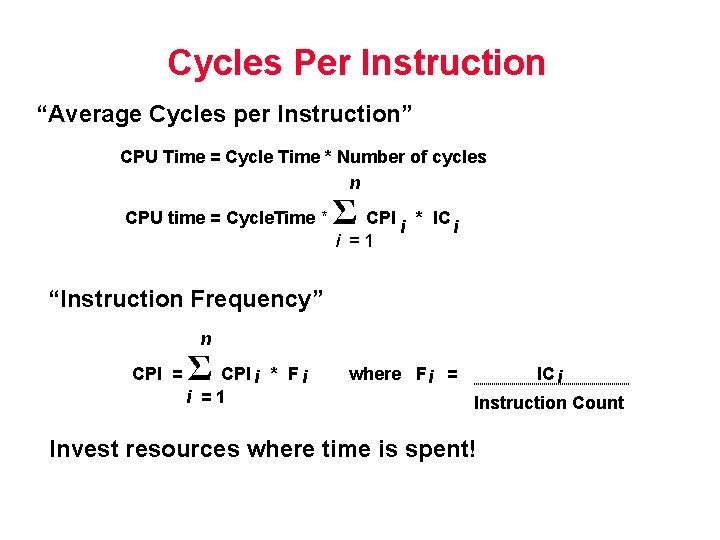

Cycles Per Instruction “Average Cycles per Instruction” CPU Time = Cycle Time * Number of cycles n CPU time = Cycle. Time * Σ CPI i i =1 * IC i “Instruction Frequency” n CPI = Σ CPI i i =1 * Fi where F i = IC i Instruction Count Invest resources where time is spent!

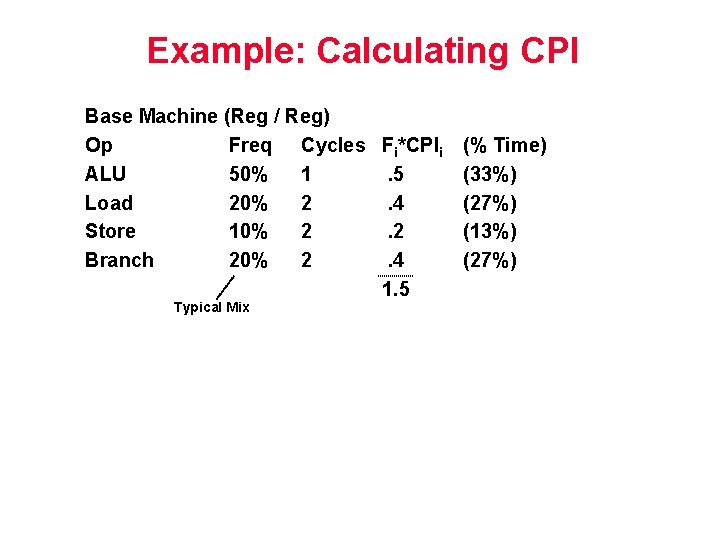

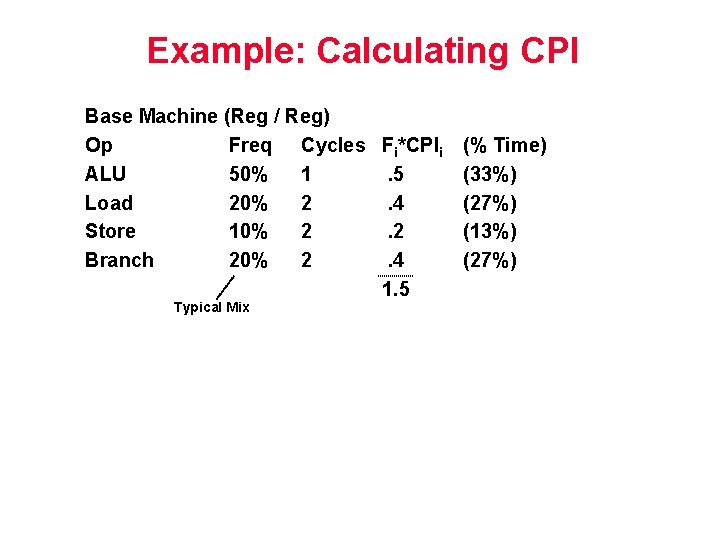

Example: Calculating CPI Base Machine (Reg / Reg) Op Freq Cycles Fi*CPIi ALU 50% 1. 5 Load 20% 2. 4 Store 10% 2. 2 Branch 20% 2. 4 1. 5 Typical Mix (% Time) (33%) (27%) (13%) (27%)

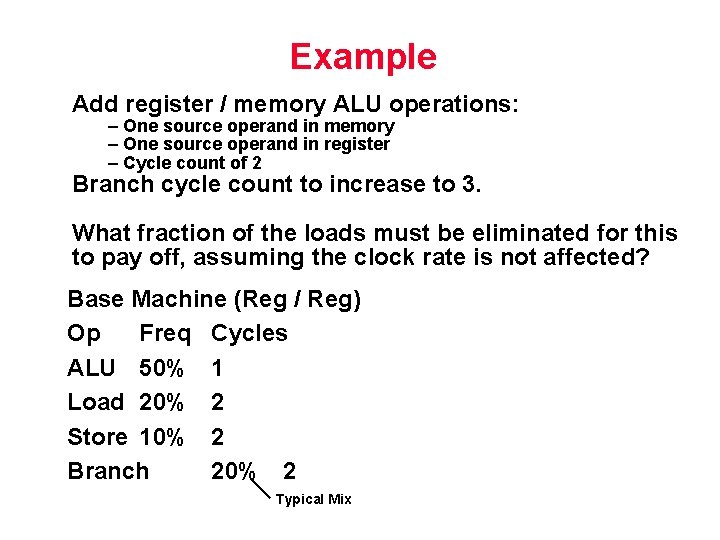

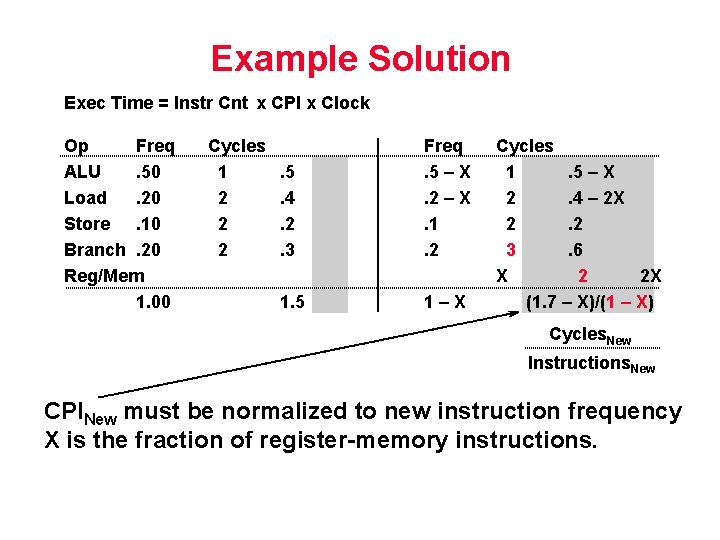

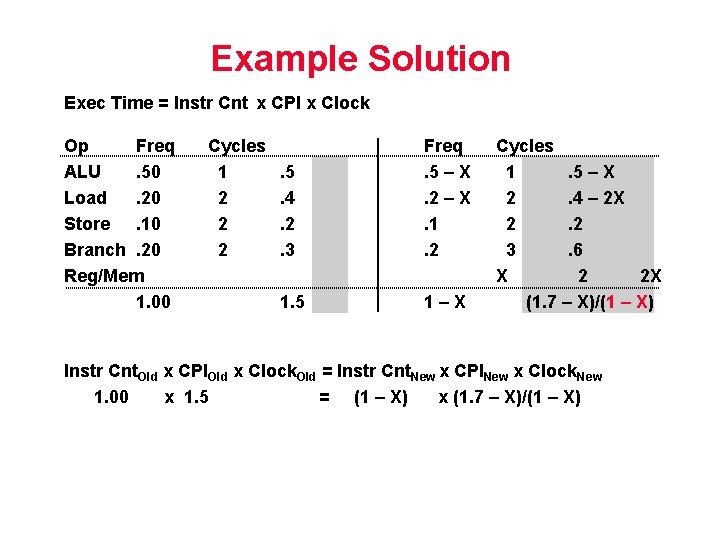

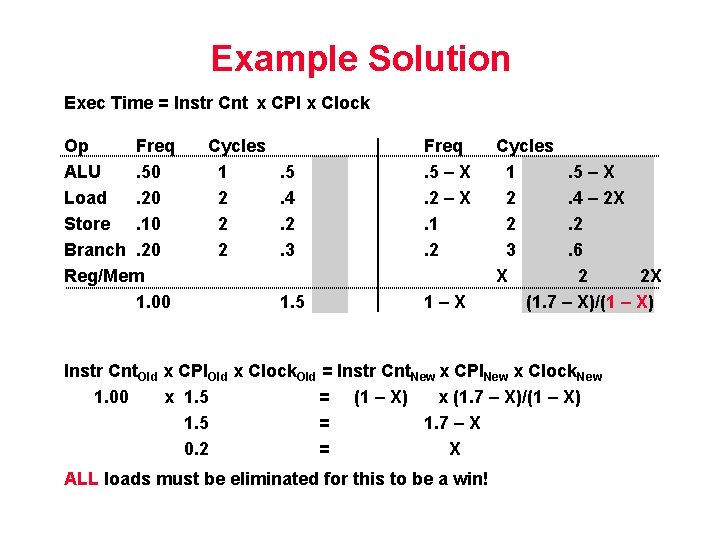

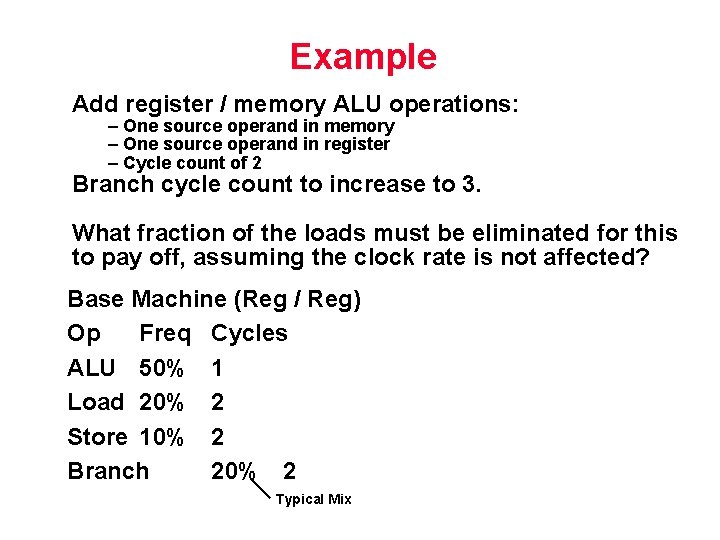

Example Add register / memory ALU operations: – One source operand in memory – One source operand in register – Cycle count of 2 Branch cycle count to increase to 3. What fraction of the loads must be eliminated for this to pay off, assuming the clock rate is not affected? Base Machine (Reg / Reg) Op Freq Cycles ALU 50% 1 Load 20% 2 Store 10% 2 Branch 20% 2 Typical Mix

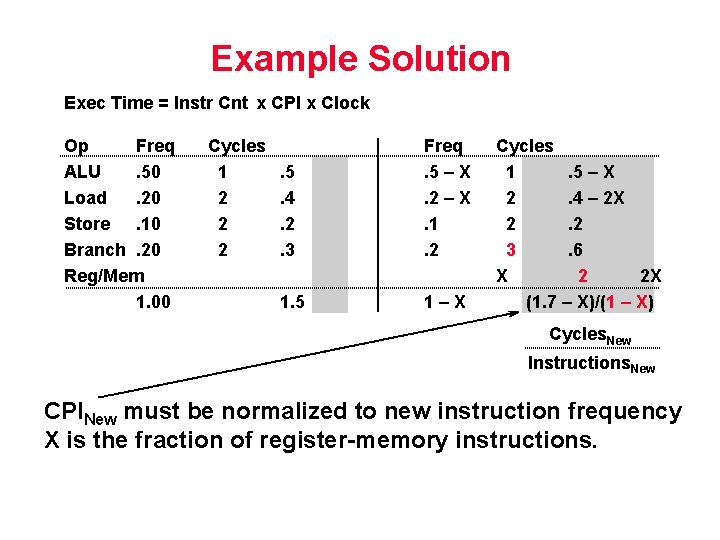

Example Solution Exec Time = Instr Cnt x CPI x Clock Op Freq ALU. 50 Load. 20 Store. 10 Branch. 20 Reg/Mem 1. 00 Cycles 1 2 2 2 . 5. 4. 2. 4 1. 5

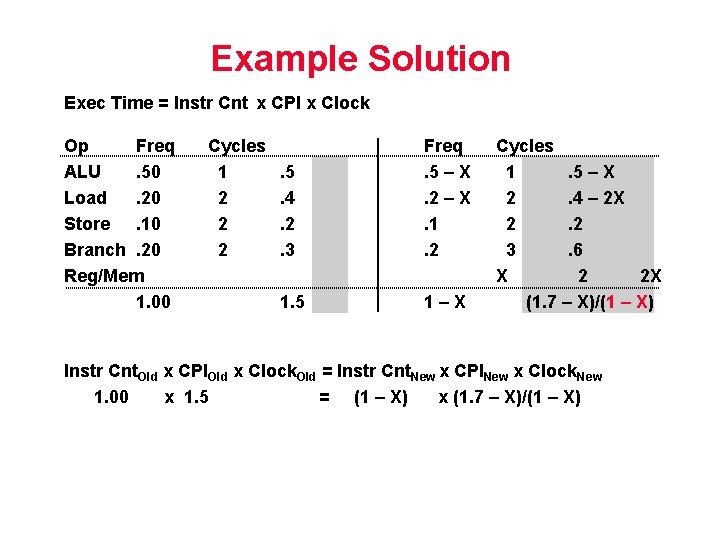

Example Solution Exec Time = Instr Cnt x CPI x Clock Op Freq ALU. 50 Load. 20 Store. 10 Branch. 20 Reg/Mem 1. 00 Cycles 1 2 2 2 . 5. 4. 2. 3 Freq. 5 – X. 2 – X. 1. 2 1. 5 1–X Cycles 1. 5 – X 2. 4 – 2 X 2. 2 3. 6 X 2 2 X (1. 7 – X)/(1 – X) Cycles. New Instructions. New CPINew must be normalized to new instruction frequency X is the fraction of register memory instructions.

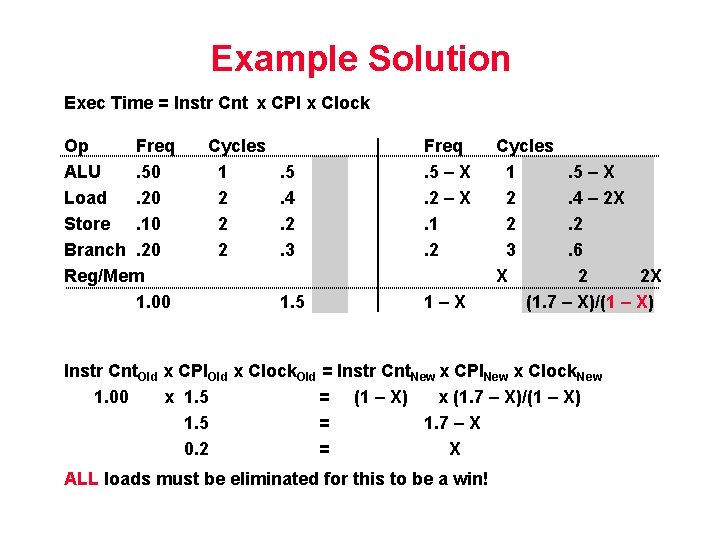

Example Solution Exec Time = Instr Cnt x CPI x Clock Op Freq ALU. 50 Load. 20 Store. 10 Branch. 20 Reg/Mem 1. 00 Cycles 1 2 2 2 . 5. 4. 2. 3 Freq. 5 – X. 2 – X. 1. 2 1. 5 1–X Cycles 1. 5 – X 2. 4 – 2 X 2. 2 3. 6 X 2 2 X (1. 7 – X)/(1 – X) Instr Cnt. Old x CPIOld x Clock. Old = Instr Cnt. New x CPINew x Clock. New 1. 00 x 1. 5 = (1 – X) x (1. 7 – X)/(1 – X)

Example Solution Exec Time = Instr Cnt x CPI x Clock Op Freq ALU. 50 Load. 20 Store. 10 Branch. 20 Reg/Mem 1. 00 Cycles 1 2 2 2 . 5. 4. 2. 3 Freq. 5 – X. 2 – X. 1. 2 1. 5 1–X Cycles 1. 5 – X 2. 4 – 2 X 2. 2 3. 6 X 2 2 X (1. 7 – X)/(1 – X) Instr Cnt. Old x CPIOld x Clock. Old = Instr Cnt. New x CPINew x Clock. New 1. 00 x 1. 5 = (1 – X) x (1. 7 – X)/(1 – X) 1. 5 = 1. 7 – X 0. 2 = X ALL loads must be eliminated for this to be a win!

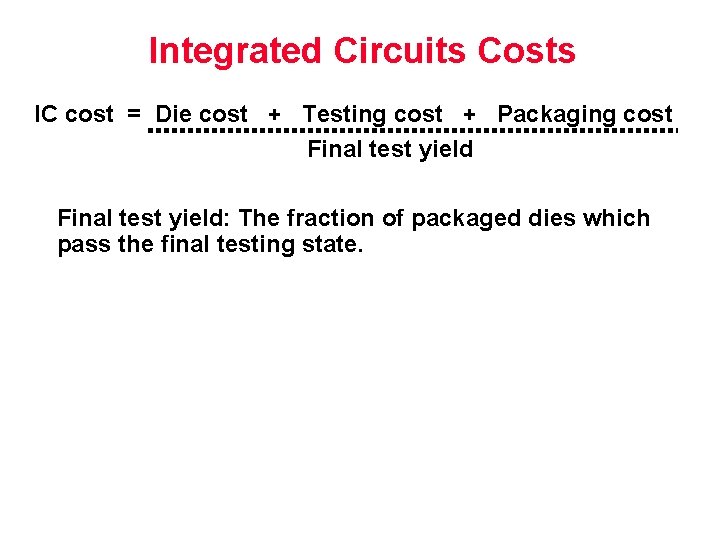

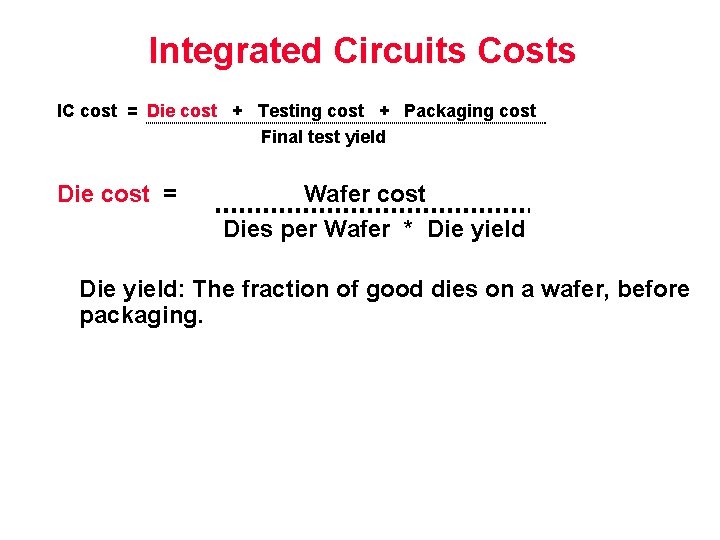

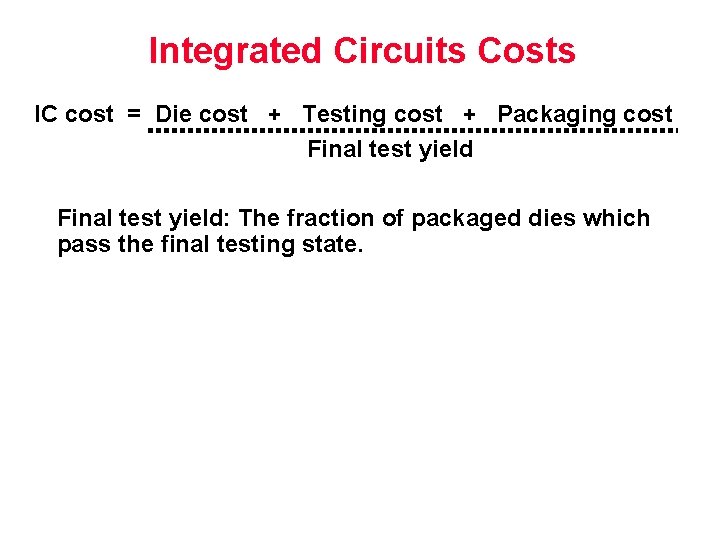

Integrated Circuits Costs IC cost = Die cost + Testing cost + Packaging cost Final test yield: The fraction of packaged dies which pass the final testing state.

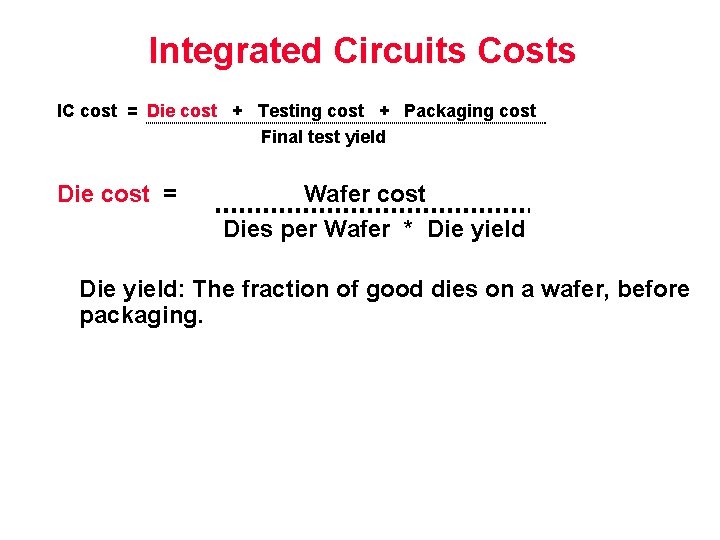

Integrated Circuits Costs IC cost = Die cost + Testing cost + Packaging cost Final test yield Die cost = Wafer cost Dies per Wafer * Die yield: The fraction of good dies on a wafer, before packaging.

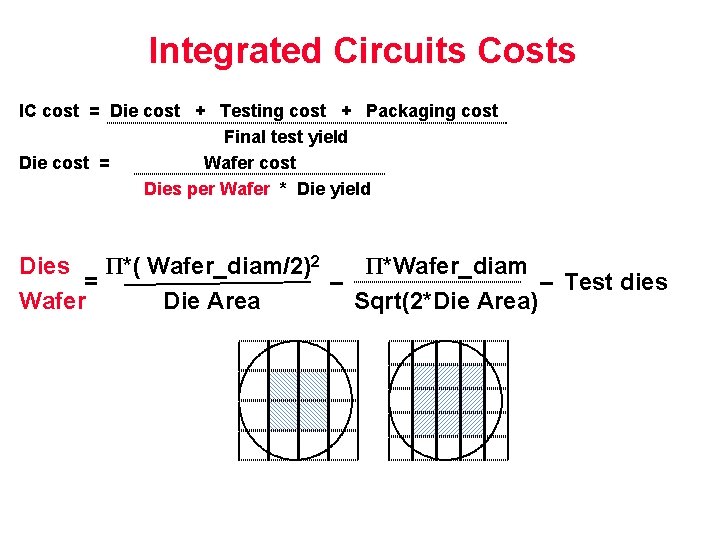

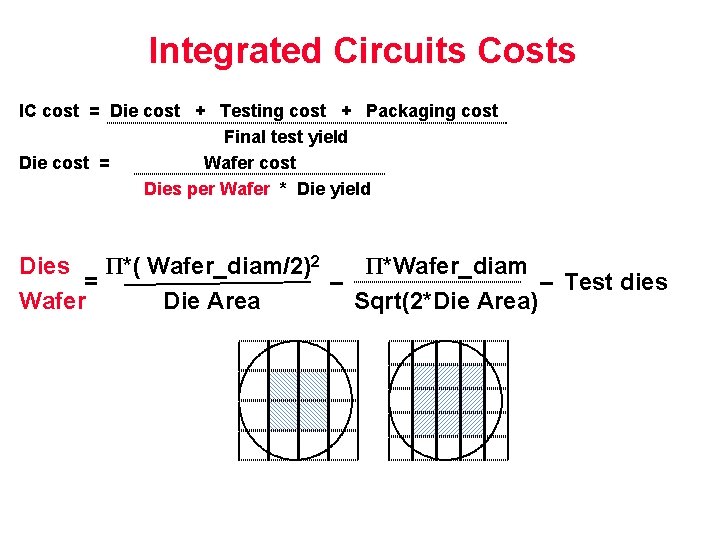

Integrated Circuits Costs IC cost = Die cost + Testing cost + Packaging cost Final test yield Die cost = Wafer cost Dies per Wafer * Die yield Dies Π*( Wafer_diam/2)2 Π*Wafer_diam = – – Test dies Wafer Die Area Sqrt(2*Die Area)

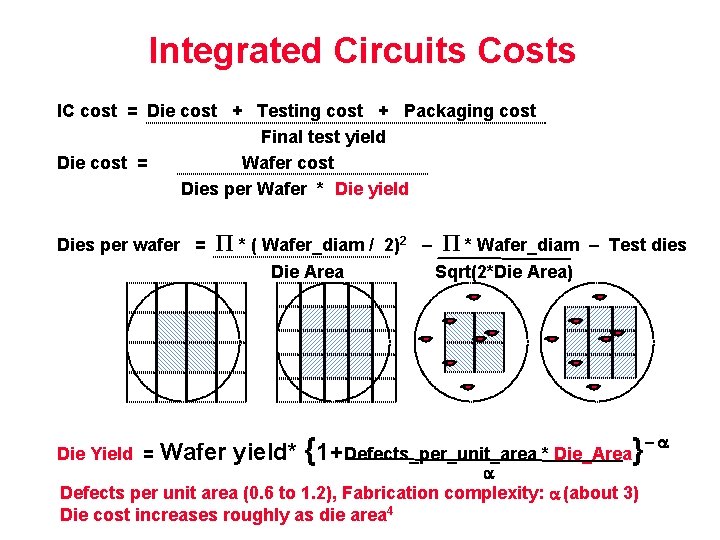

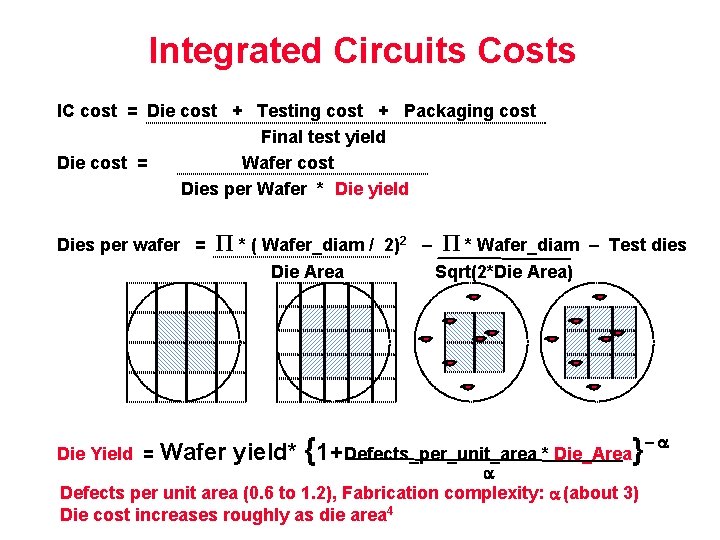

Integrated Circuits Costs IC cost = Die cost + Testing cost + Packaging cost Final test yield Die cost = Wafer cost Dies per Wafer * Die yield Dies per wafer = Π * ( Wafer_diam / Die Area Die Yield = 2)2 – Π * Wafer_diam – Test dies Sqrt(2*Die Area) Wafer yield* {1+Defects_per_unit_area * Die_Area}- a a Defects per unit area (0. 6 to 1. 2), Fabrication complexity: a (about 3) Die cost increases roughly as die area 4

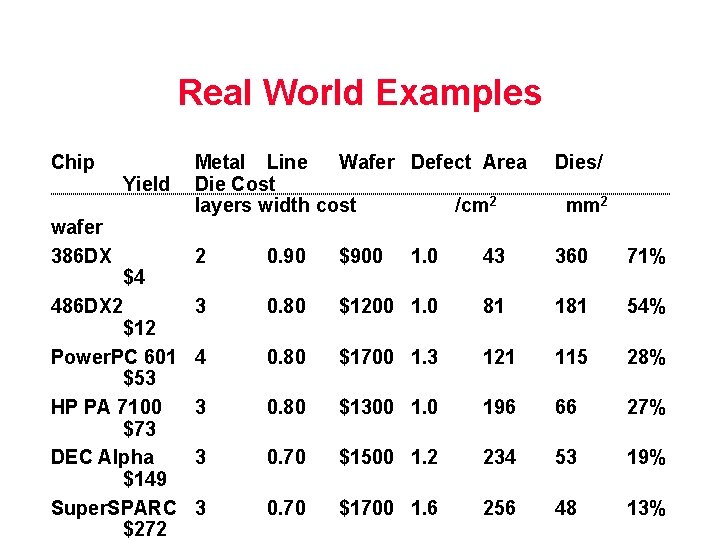

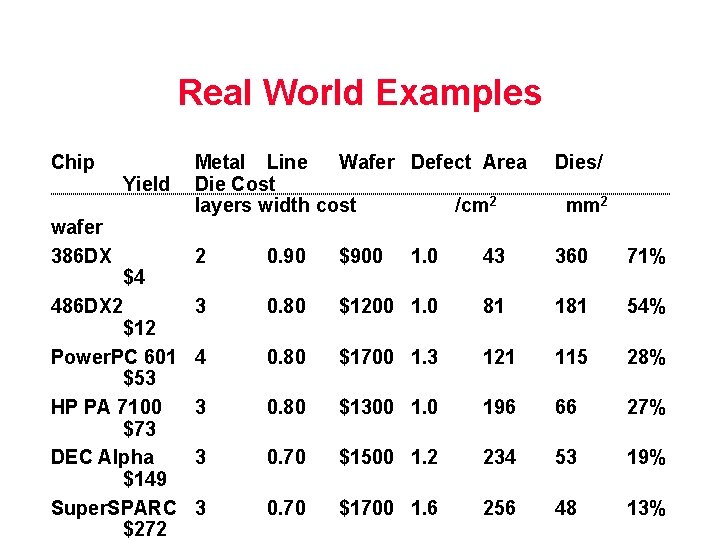

Real World Examples Chip wafer 386 DX Yield $4 486 DX 2 $12 Power. PC 601 $53 HP PA 7100 $73 DEC Alpha $149 Super. SPARC $272 Metal Line Wafer Defect Area Die Cost layers width cost /cm 2 Dies/ 2 0. 90 $900 1. 0 43 360 71% 3 0. 80 $1200 1. 0 81 181 54% 4 0. 80 $1700 1. 3 121 115 28% 3 0. 80 $1300 1. 0 196 66 27% 3 0. 70 $1500 1. 2 234 53 19% 3 0. 70 $1700 1. 6 256 48 13% mm 2

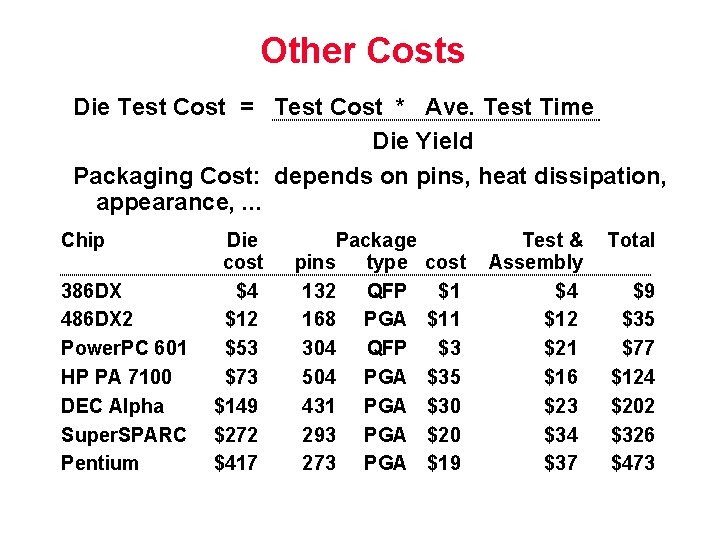

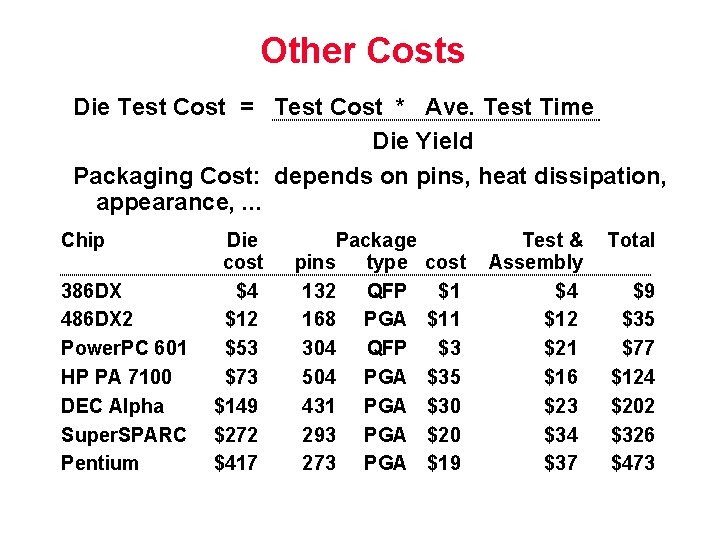

Other Costs Die Test Cost = Test Cost * Ave. Test Time Die Yield Packaging Cost: depends on pins, heat dissipation, appearance, . . . Chip 386 DX 486 DX 2 Power. PC 601 HP PA 7100 DEC Alpha Super. SPARC Pentium Die cost $4 $12 $53 $73 $149 $272 $417 Package pins type 132 QFP 168 PGA 304 QFP 504 PGA 431 PGA 293 PGA 273 PGA cost $1 $11 $3 $35 $30 $20 $19 Test & Assembly $4 $12 $21 $16 $23 $34 $37 Total $9 $35 $77 $124 $202 $326 $473

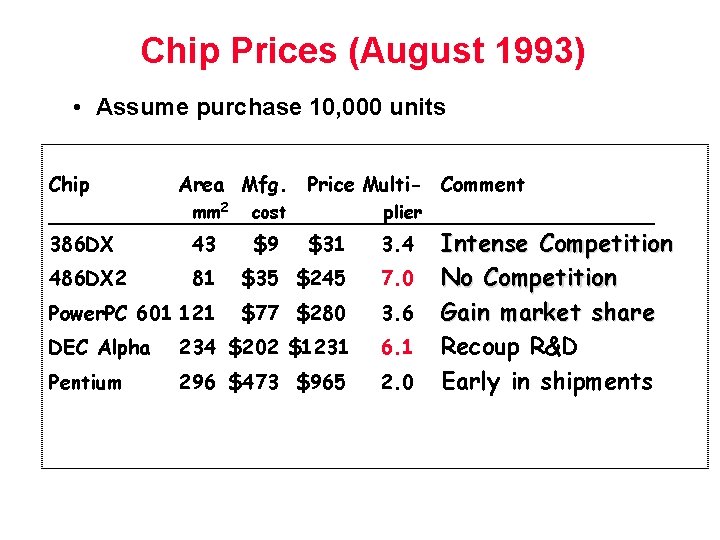

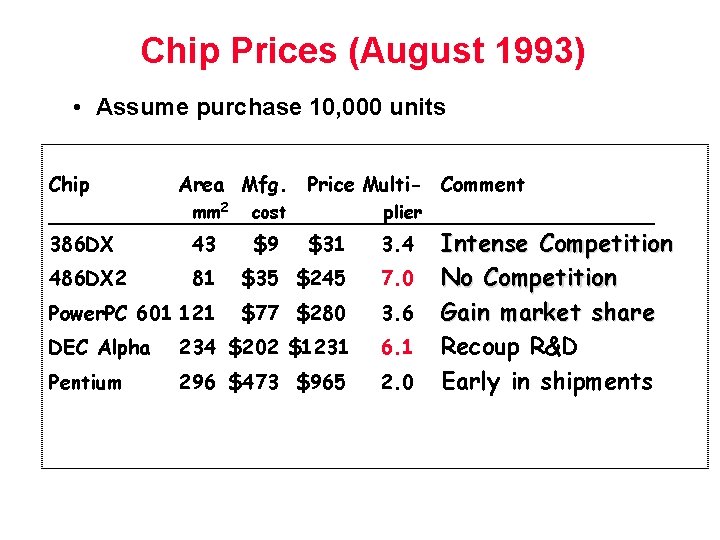

Chip Prices (August 1993) • Assume purchase 10, 000 units Chip Area Mfg. mm 2 cost 386 DX 43 $9 486 DX 2 Price Multi- Comment plier $31 3. 4 81 $35 $245 7. 0 Power. PC 601 121 $77 $280 3. 6 DEC Alpha 234 $202 $1231 6. 1 Pentium 296 $473 $965 2. 0 Intense Competition No Competition Gain market share Recoup R&D Early in shipments

Source: Intel Power Dissipation ÊLead processor power increases every generation ËCompactions provide higher performance at lower power

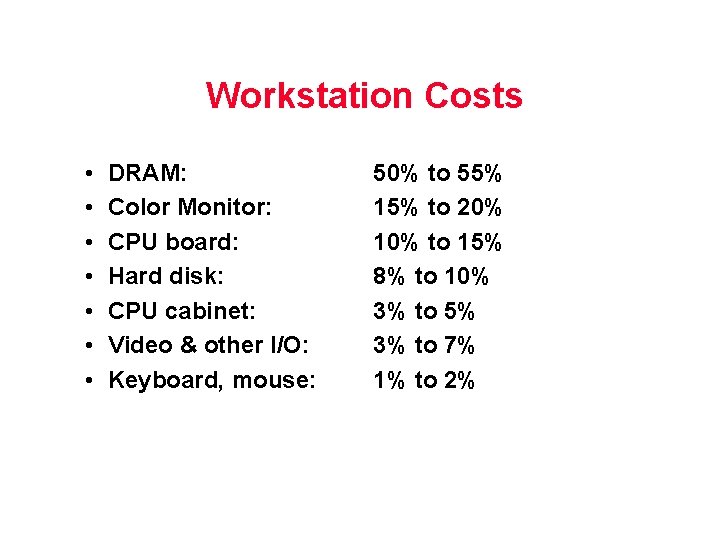

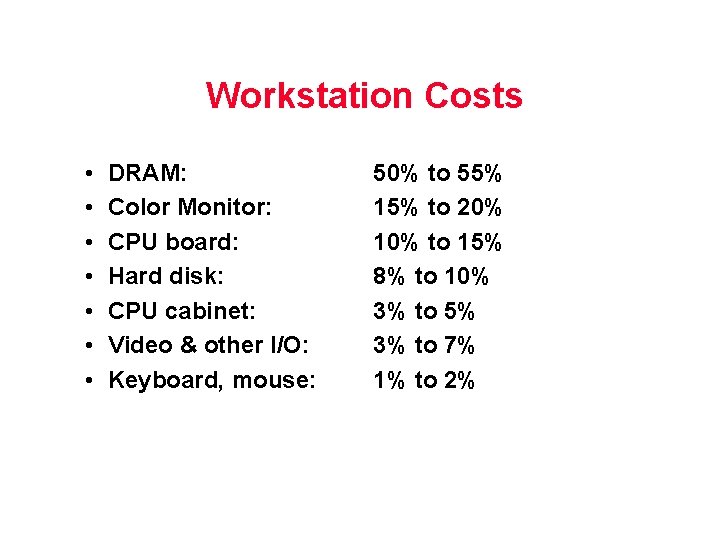

Workstation Costs • • DRAM: Color Monitor: CPU board: Hard disk: CPU cabinet: Video & other I/O: Keyboard, mouse: 50% to 55% 15% to 20% 10% to 15% 8% to 10% 3% to 5% 3% to 7% 1% to 2%

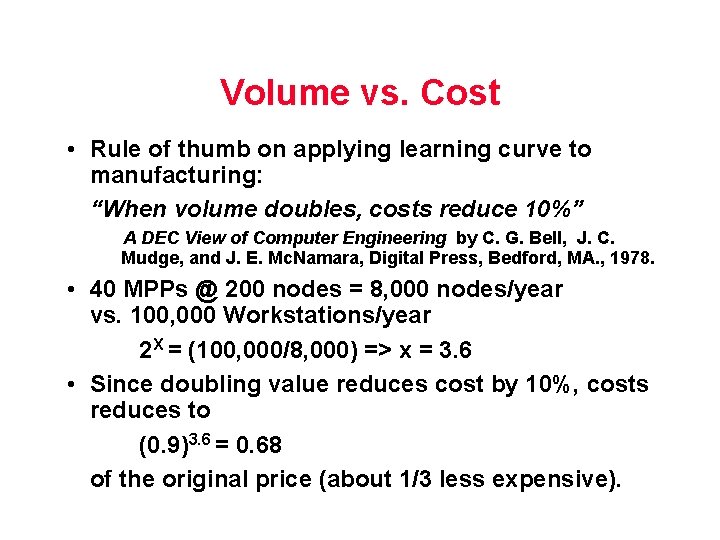

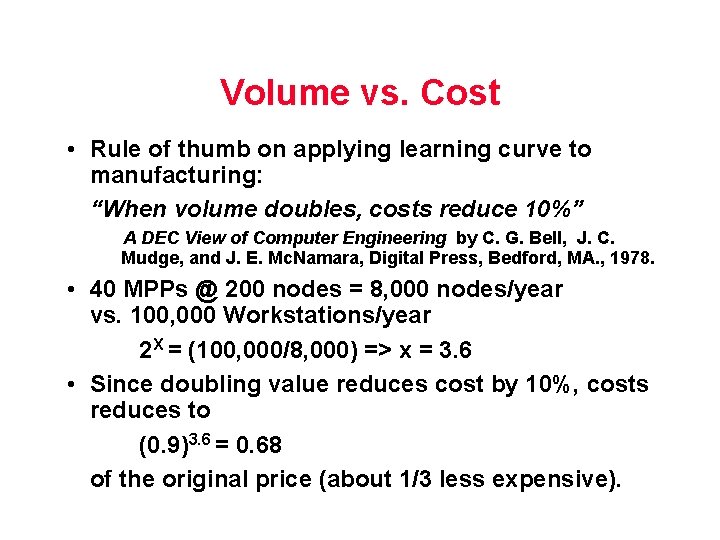

Volume vs. Cost • Rule of thumb on applying learning curve to manufacturing: “When volume doubles, costs reduce 10%” A DEC View of Computer Engineering by C. G. Bell, J. C. Mudge, and J. E. Mc. Namara, Digital Press, Bedford, MA. , 1978. • 40 MPPs @ 200 nodes = 8, 000 nodes/year vs. 100, 000 Workstations/year 2 X = (100, 000/8, 000) => x = 3. 6 • Since doubling value reduces cost by 10%, costs reduces to (0. 9)3. 6 = 0. 68 of the original price (about 1/3 less expensive).

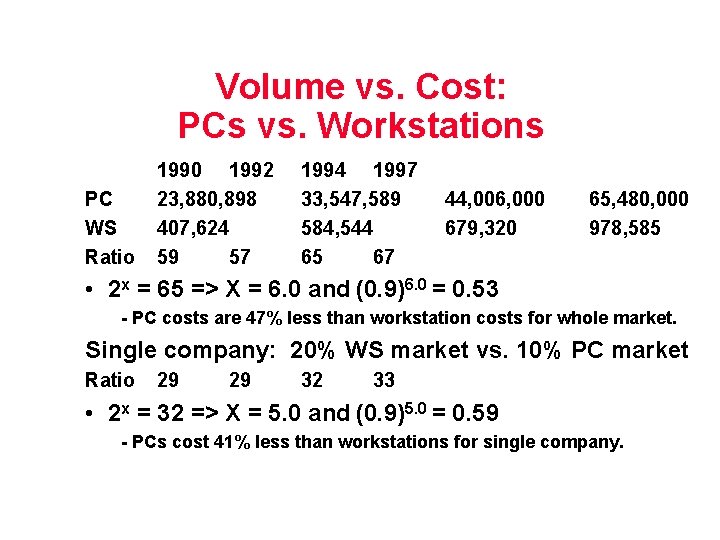

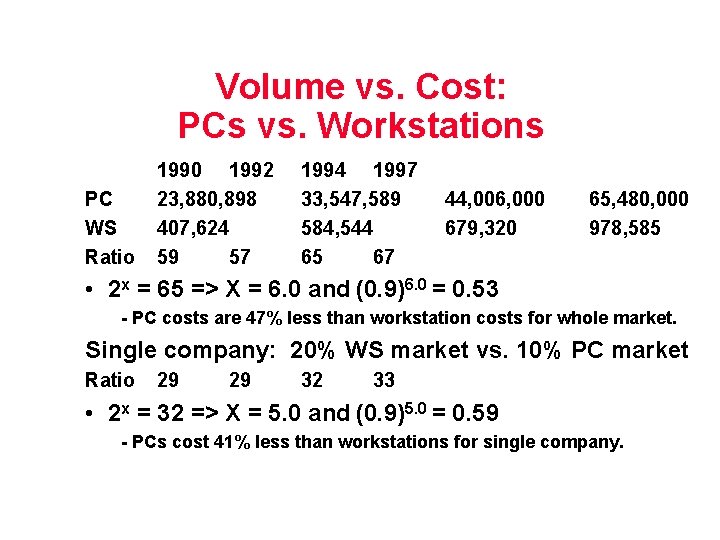

Volume vs. Cost: PCs vs. Workstations PC WS Ratio 1990 1992 23, 880, 898 407, 624 59 57 1994 1997 33, 547, 589 584, 544 65 67 44, 006, 000 679, 320 65, 480, 000 978, 585 • 2 x = 65 => X = 6. 0 and (0. 9)6. 0 = 0. 53 PC costs are 47% less than workstation costs for whole market. Single company: 20% WS market vs. 10% PC market Ratio 29 29 32 33 • 2 x = 32 => X = 5. 0 and (0. 9)5. 0 = 0. 59 PCs cost 41% less than workstations for single company.

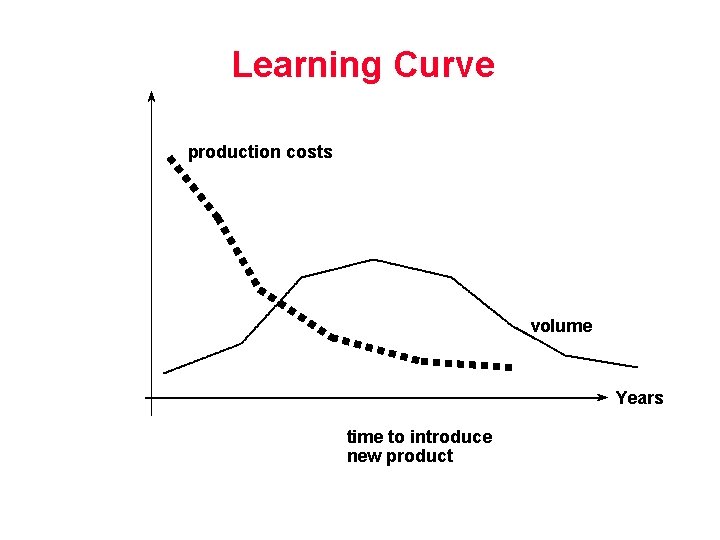

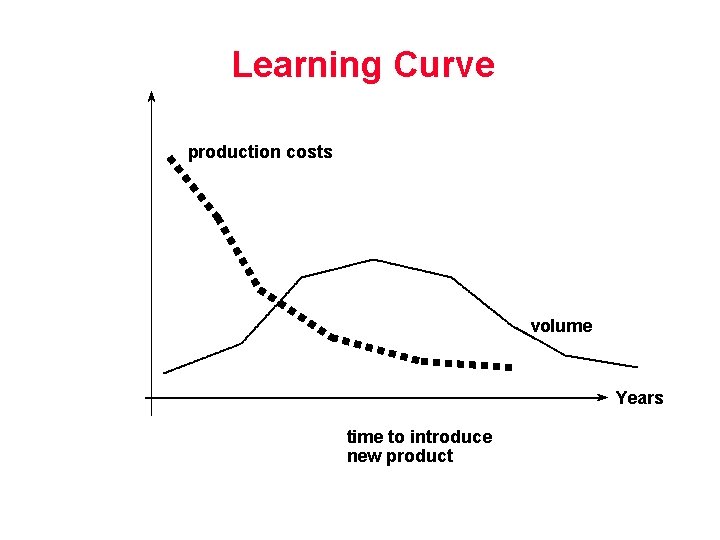

Learning Curve production costs volume Years time to introduce new product

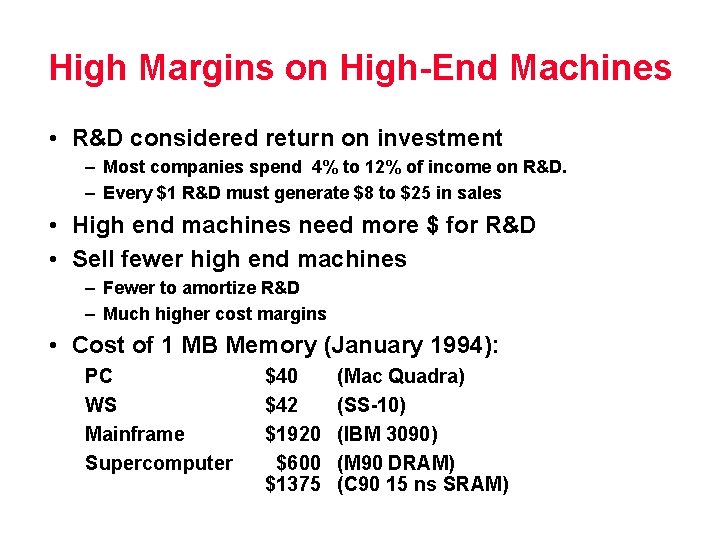

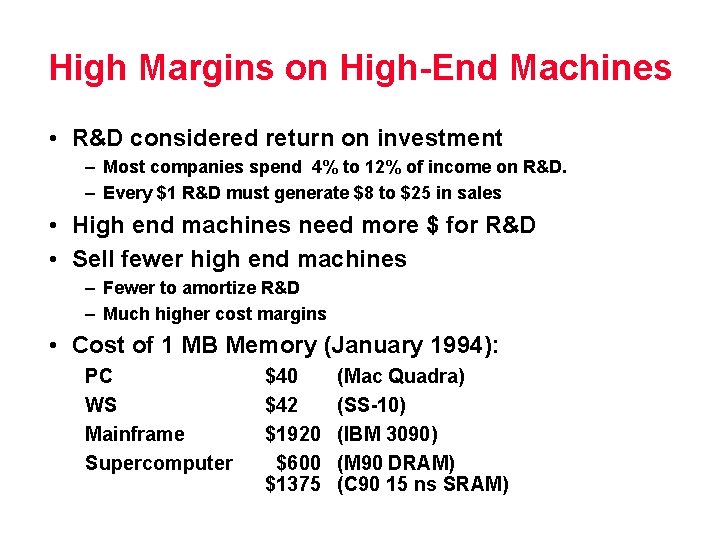

High Margins on High End Machines • R&D considered return on investment – Most companies spend 4% to 12% of income on R&D. – Every $1 R&D must generate $8 to $25 in sales • High end machines need more $ for R&D • Sell fewer high end machines – Fewer to amortize R&D – Much higher cost margins • Cost of 1 MB Memory (January 1994): PC WS Mainframe Supercomputer $40 $42 $1920 $600 $1375 (Mac Quadra) (SS 10) (IBM 3090) (M 90 DRAM) (C 90 15 ns SRAM)

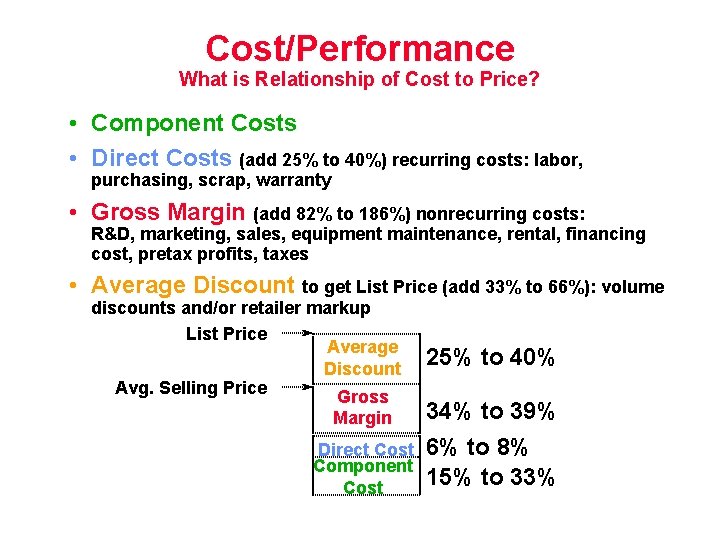

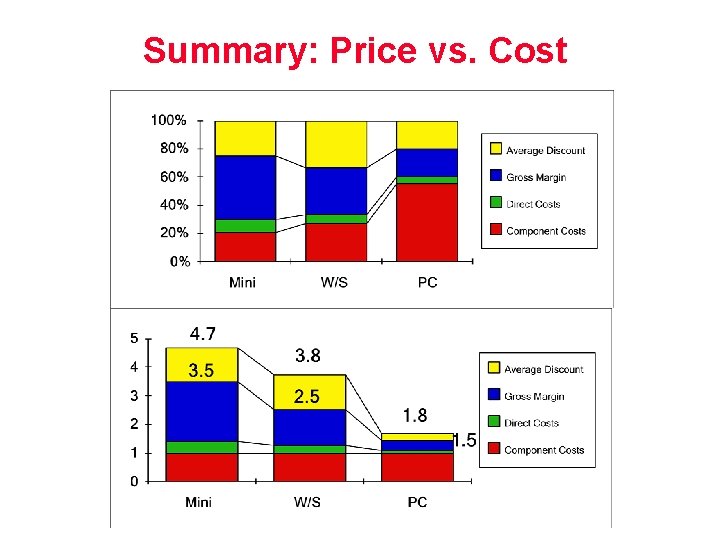

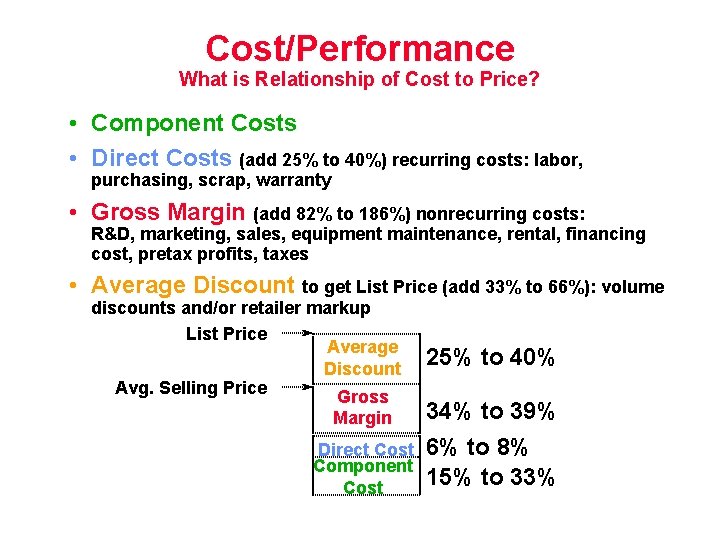

Cost/Performance What is Relationship of Cost to Price? • Component Costs • Direct Costs (add 25% to 40%) recurring costs: labor, purchasing, scrap, warranty • Gross Margin (add 82% to 186%) nonrecurring costs: R&D, marketing, sales, equipment maintenance, rental, financing cost, pretax profits, taxes • Average Discount to get List Price (add 33% to 66%): volume discounts and/or retailer markup List Price Average Discount Avg. Selling Price Gross Margin Direct Cost Component Cost 25% to 40% 34% to 39% 6% to 8% 15% to 33%

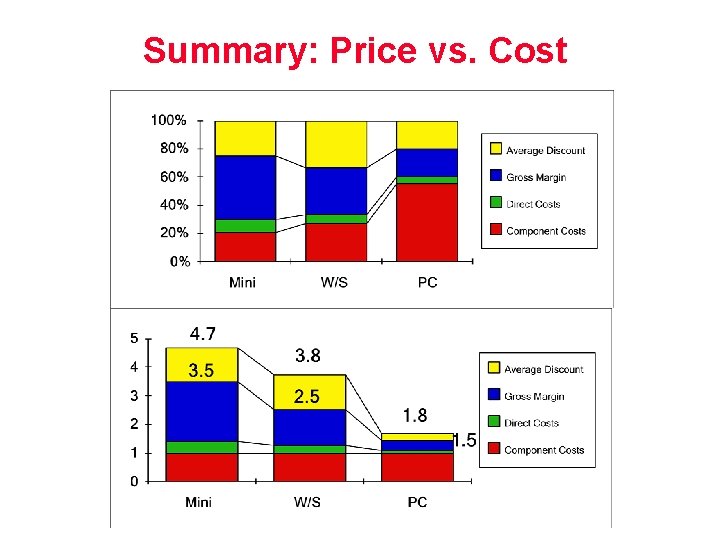

Summary: Price vs. Cost