Combiner functionalities BEAM PERMIT CONTROL Beam dump line

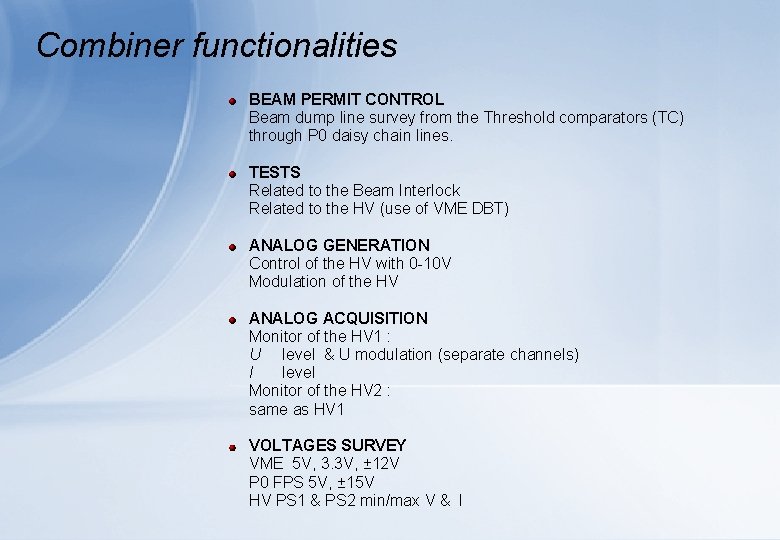

Combiner functionalities BEAM PERMIT CONTROL Beam dump line survey from the Threshold comparators (TC) through P 0 daisy chain lines. TESTS Related to the Beam Interlock Related to the HV (use of VME DBT) ANALOG GENERATION Control of the HV with 0 -10 V Modulation of the HV ANALOG ACQUISITION Monitor of the HV 1 : U level & U modulation (separate channels) I level Monitor of the HV 2 : same as HV 1 VOLTAGES SURVEY VME 5 V, 3. 3 V, ± 12 V P 0 FPS 5 V, ± 15 V HV PS 1 & PS 2 min/max V & I

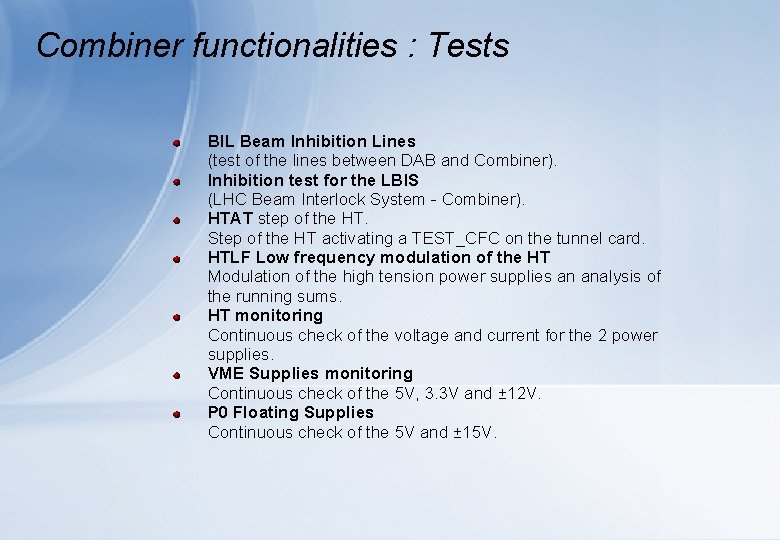

Combiner functionalities : Tests BIL Beam Inhibition Lines (test of the lines between DAB and Combiner). Inhibition test for the LBIS (LHC Beam Interlock System - Combiner). HTAT step of the HT. Step of the HT activating a TEST_CFC on the tunnel card. HTLF Low frequency modulation of the HT Modulation of the high tension power supplies an analysis of the running sums. HT monitoring Continuous check of the voltage and current for the 2 power supplies. VME Supplies monitoring Continuous check of the 5 V, 3. 3 V and ± 12 V. P 0 Floating Supplies Continuous check of the 5 V and ± 15 V.

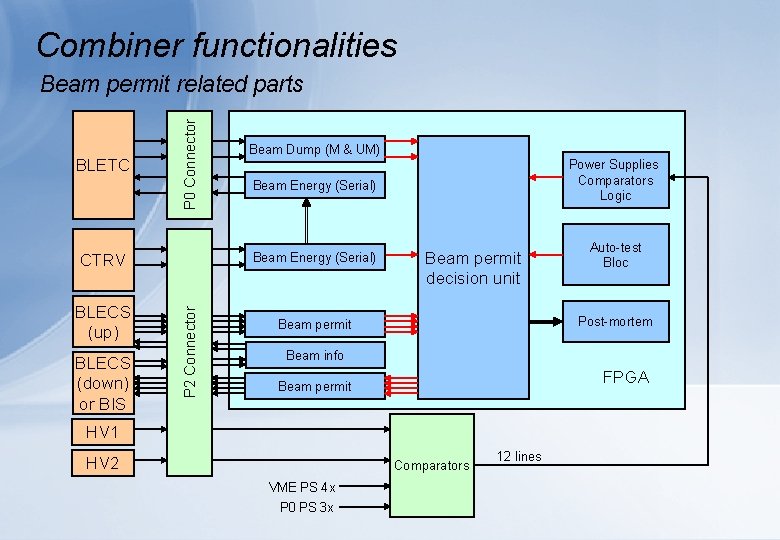

Combiner functionalities BLETC P 0 Connector Beam permit related parts P 2 Connector BLECS (down) or BIS Power Supplies Comparators Logic Beam Energy (Serial) CTRV BLECS (up) Beam Dump (M & UM) Beam permit decision unit Auto-test Bloc Post-mortem Beam permit Beam info FPGA Beam permit HV 1 HV 2 Comparators VME PS 4 x P 0 PS 3 x 12 lines

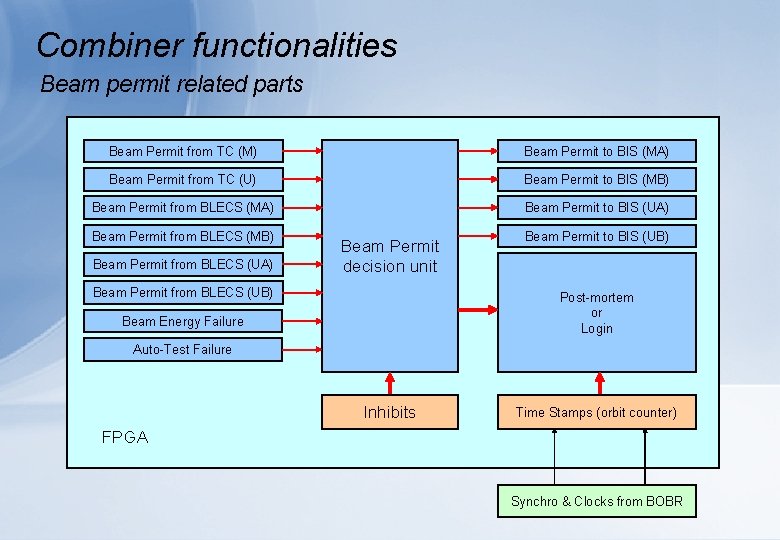

Combiner functionalities Beam permit related parts Beam Permit from TC (M) Beam Permit to BIS (MA) Beam Permit from TC (U) Beam Permit to BIS (MB) Beam Permit from BLECS (MA) Beam Permit to BIS (UA) Beam Permit from BLECS (MB) Beam Permit from BLECS (UA) Beam Permit decision unit Beam Permit from BLECS (UB) Beam Permit to BIS (UB) Post-mortem or Login Beam Energy Failure Auto-Test Failure Inhibits Time Stamps (orbit counter) FPGA Synchro & Clocks from BOBR

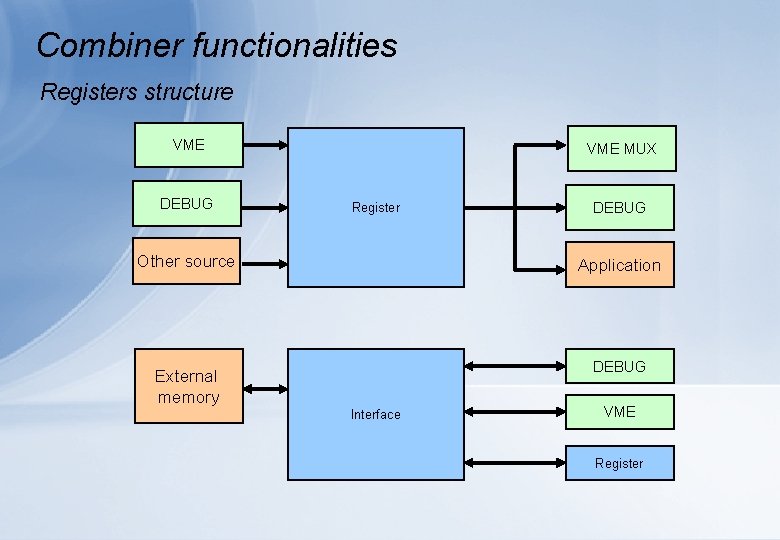

Combiner functionalities Registers structure VME DEBUG VME MUX Register Other source DEBUG Application DEBUG External memory Interface VME Register

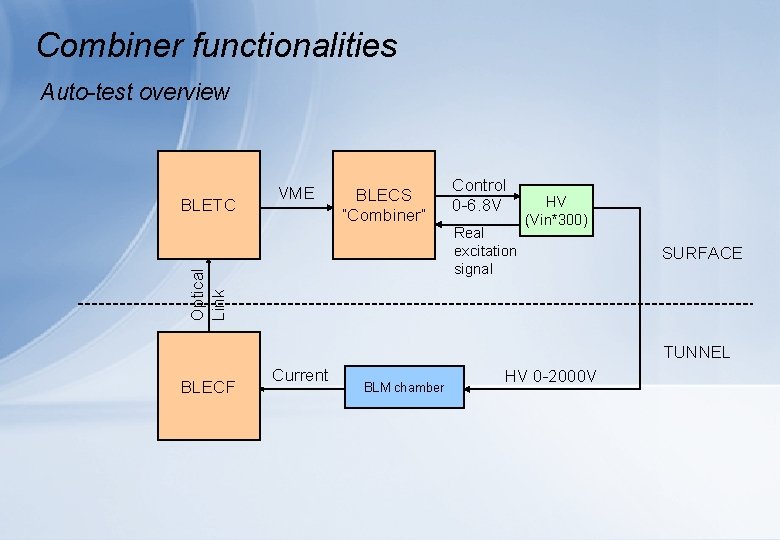

Combiner functionalities Auto-test overview BLECS “Combiner” Optical Link BLETC VME Control 0 -6. 8 V Real excitation signal HV (Vin*300) SURFACE TUNNEL BLECF Current BLM chamber HV 0 -2000 V

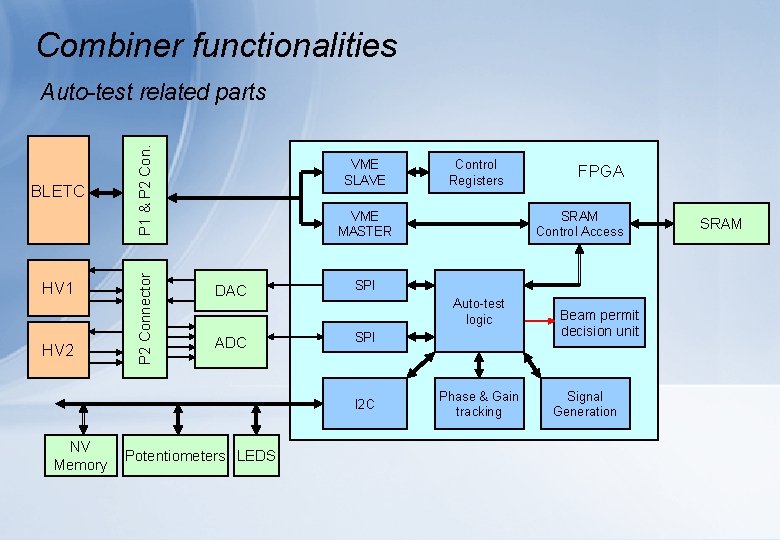

Combiner functionalities HV 1 HV 2 P 2 Connector BLETC P 1 & P 2 Con. Auto-test related parts VME SLAVE VME MASTER DAC ADC Potentiometers LEDS FPGA SRAM Control Access SPI Auto-test logic SPI I 2 C NV Memory Control Registers Phase & Gain tracking Beam permit decision unit Signal Generation SRAM

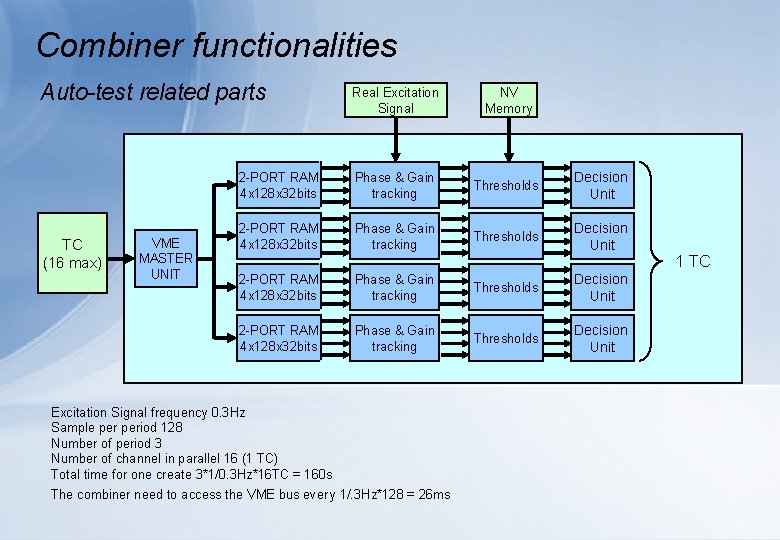

Combiner functionalities Auto-test related parts TC (16 max) VME MASTER UNIT Real Excitation Signal NV Memory 2 -PORT RAM 4 x 128 x 32 bits Phase & Gain tracking Thresholds Decision Unit Excitation Signal frequency 0. 3 Hz Sample period 128 Number of period 3 Number of channel in parallel 16 (1 TC) Total time for one create 3*1/0. 3 Hz*16 TC = 160 s The combiner need to access the VME bus every 1/. 3 Hz*128 = 26 ms 1 TC

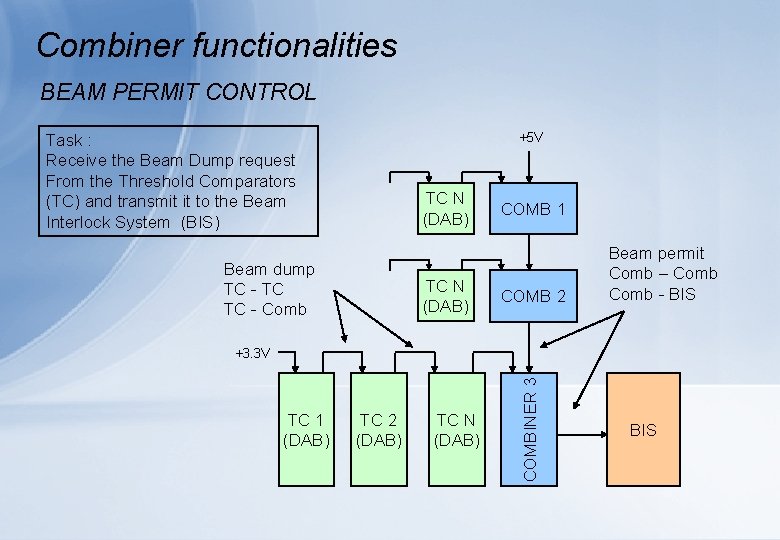

Combiner functionalities BEAM PERMIT CONTROL +5 V Task : Receive the Beam Dump request From the Threshold Comparators (TC) and transmit it to the Beam Interlock System (BIS) TC N (DAB) Beam dump TC - TC TC - Comb TC N (DAB) COMB 1 COMB 2 Beam permit Comb – Comb - BIS TC 1 (DAB) TC 2 (DAB) TC N (DAB) COMBINER 3 +3. 3 V BIS

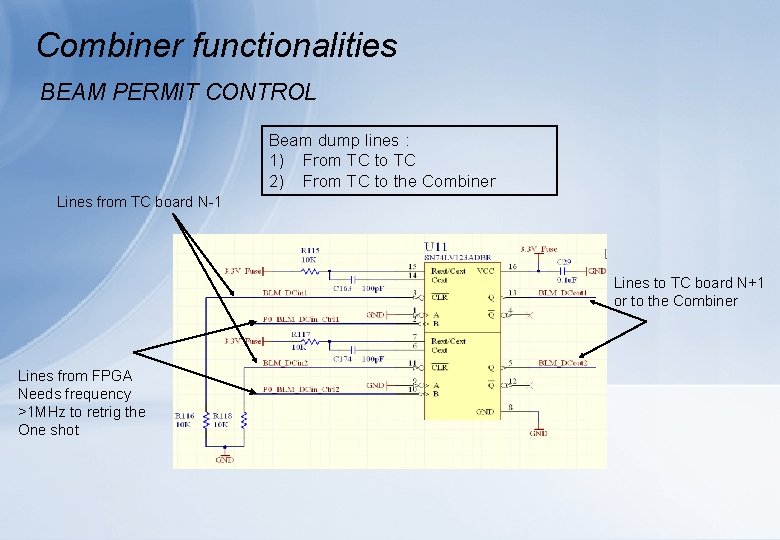

Combiner functionalities BEAM PERMIT CONTROL Beam dump lines : 1) From TC to TC 2) From TC to the Combiner Lines from TC board N-1 Lines to TC board N+1 or to the Combiner Lines from FPGA Needs frequency >1 MHz to retrig the One shot

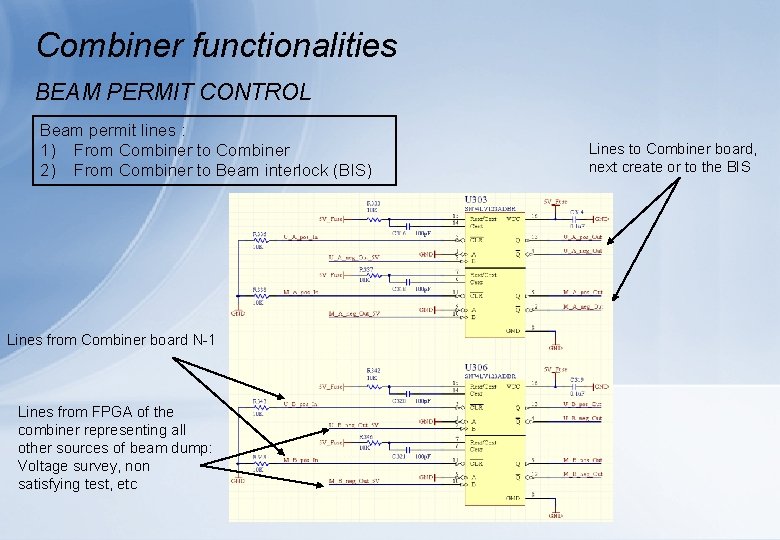

Combiner functionalities BEAM PERMIT CONTROL Beam permit lines : 1) From Combiner to Combiner 2) From Combiner to Beam interlock (BIS) Lines from Combiner board N-1 Lines from FPGA of the combiner representing all other sources of beam dump: Voltage survey, non satisfying test, etc Lines to Combiner board, next create or to the BIS

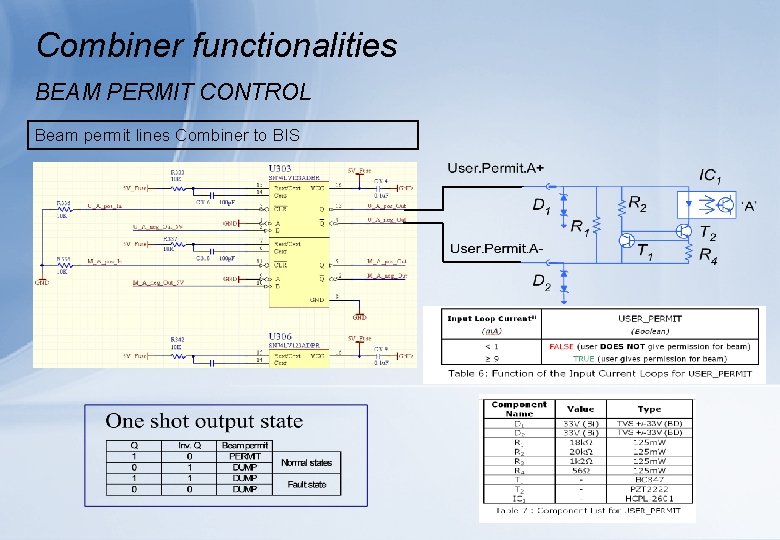

Combiner functionalities BEAM PERMIT CONTROL Beam permit lines Combiner to BIS

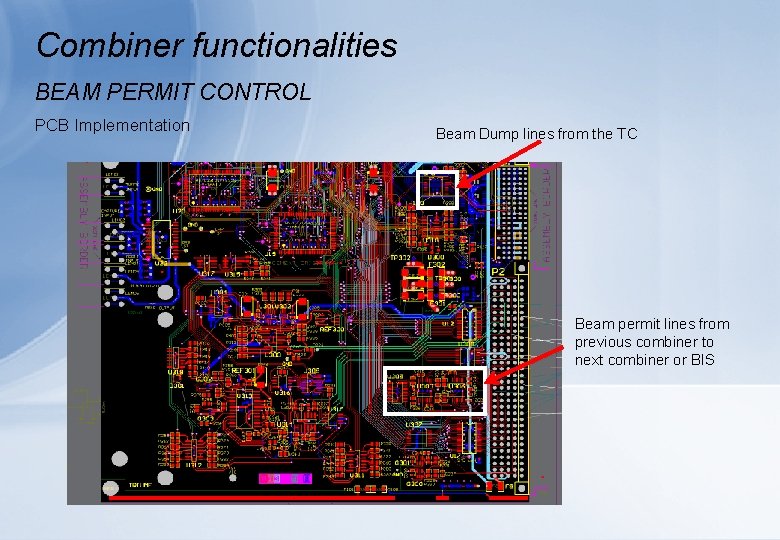

Combiner functionalities BEAM PERMIT CONTROL PCB Implementation Beam Dump lines from the TC Beam permit lines from previous combiner to next combiner or BIS

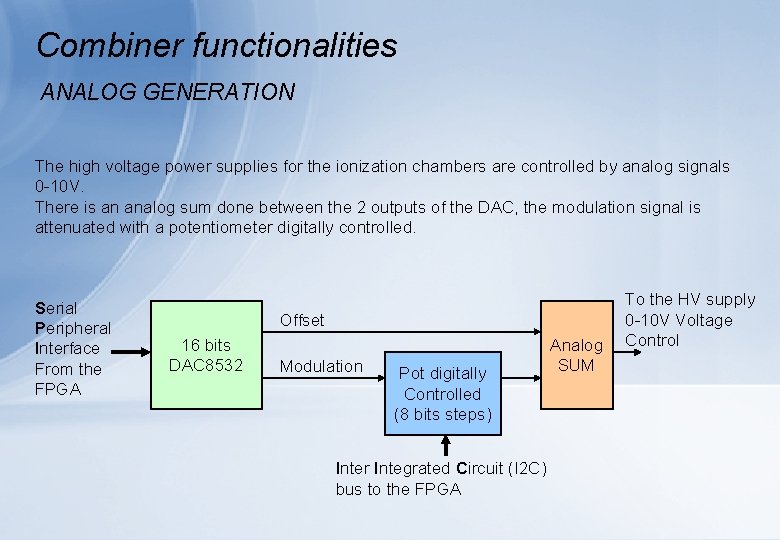

Combiner functionalities ANALOG GENERATION The high voltage power supplies for the ionization chambers are controlled by analog signals 0 -10 V. There is an analog sum done between the 2 outputs of the DAC, the modulation signal is attenuated with a potentiometer digitally controlled. Serial Peripheral Interface From the FPGA Offset 16 bits DAC 8532 Modulation Pot digitally Controlled (8 bits steps) Inter Integrated Circuit (I 2 C) bus to the FPGA Analog SUM To the HV supply 0 -10 V Voltage Control

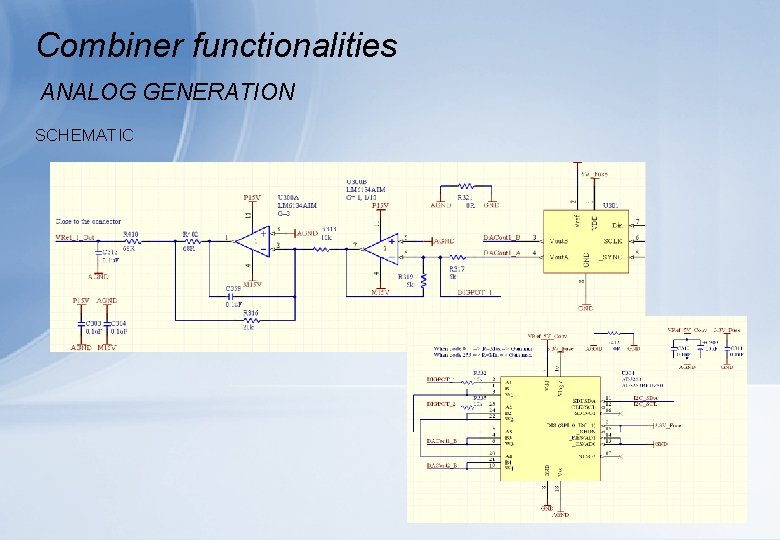

Combiner functionalities ANALOG GENERATION SCHEMATIC

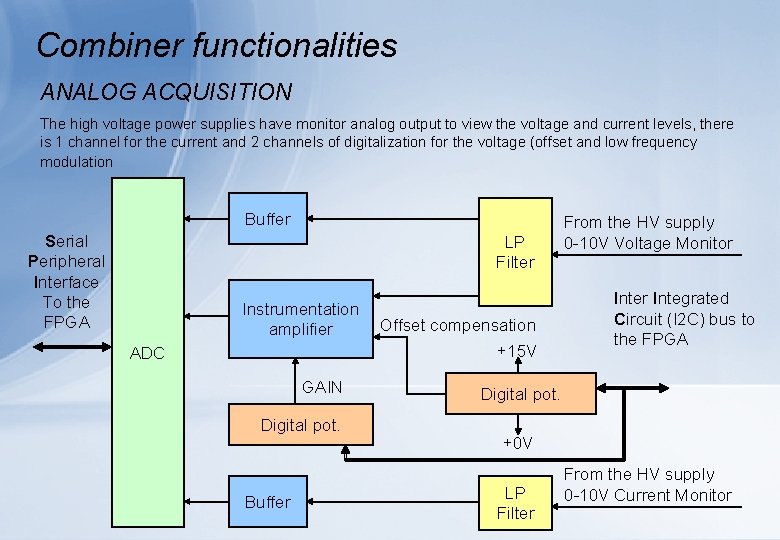

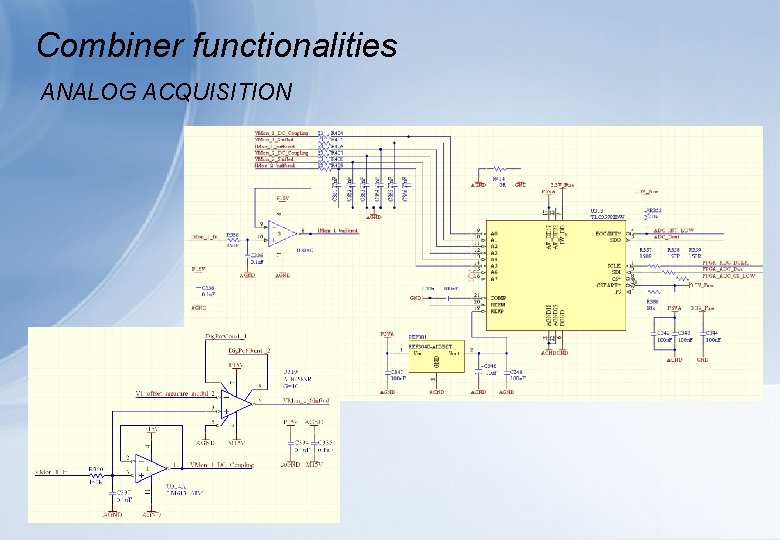

Combiner functionalities ANALOG ACQUISITION The high voltage power supplies have monitor analog output to view the voltage and current levels, there is 1 channel for the current and 2 channels of digitalization for the voltage (offset and low frequency modulation Buffer Serial Peripheral Interface To the FPGA LP Filter Instrumentation amplifier Offset compensation +15 V ADC GAIN Digital pot. Buffer From the HV supply 0 -10 V Voltage Monitor Integrated Circuit (I 2 C) bus to the FPGA Digital pot. +0 V LP Filter From the HV supply 0 -10 V Current Monitor

Combiner functionalities ANALOG ACQUISITION

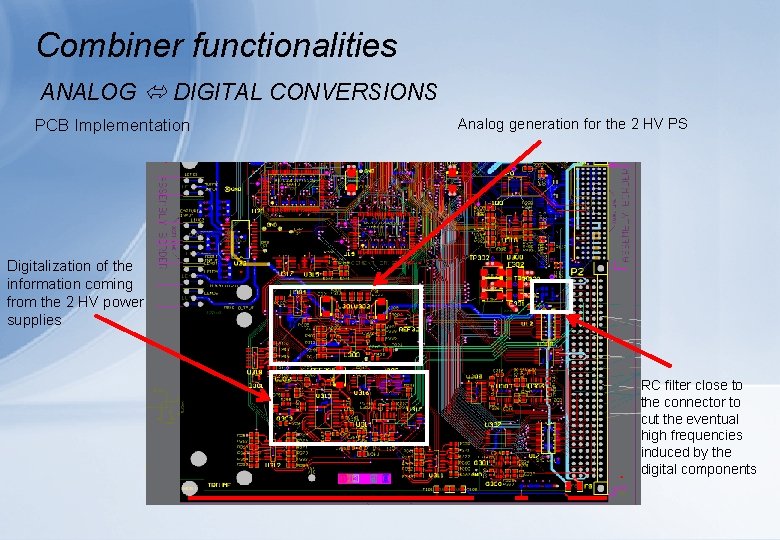

Combiner functionalities ANALOG DIGITAL CONVERSIONS PCB Implementation Analog generation for the 2 HV PS Digitalization of the information coming from the 2 HV power supplies RC filter close to the connector to cut the eventual high frequencies induced by the digital components

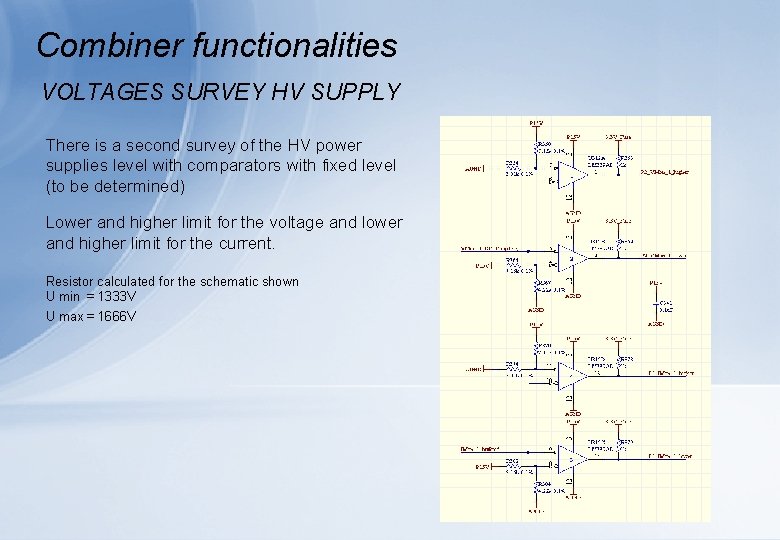

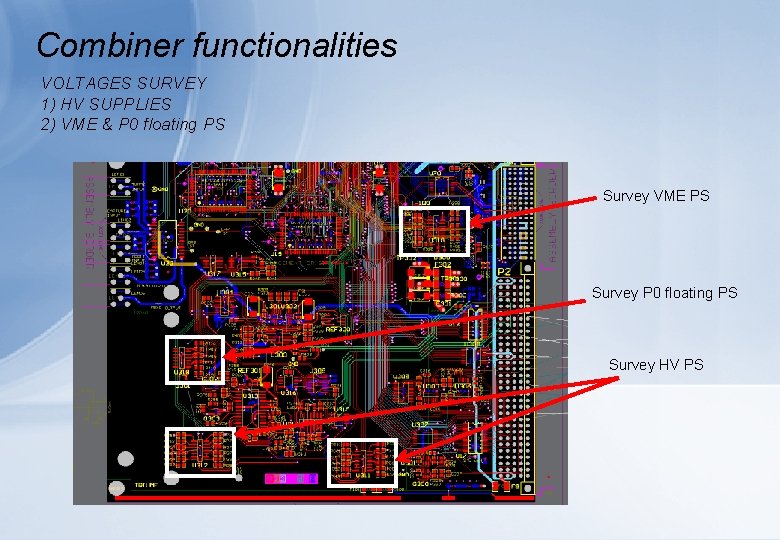

Combiner functionalities VOLTAGES SURVEY HV SUPPLY There is a second survey of the HV power supplies level with comparators with fixed level (to be determined) Lower and higher limit for the voltage and lower and higher limit for the current. Resistor calculated for the schematic shown U min = 1333 V U max = 1666 V

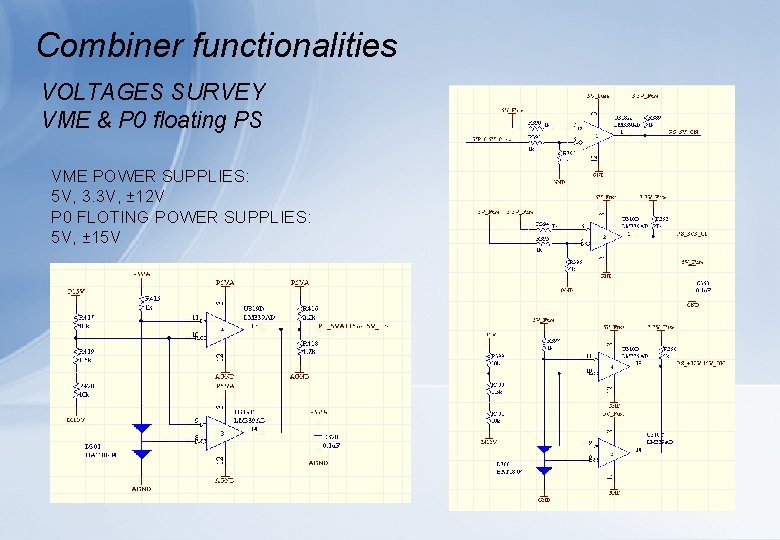

Combiner functionalities VOLTAGES SURVEY VME & P 0 floating PS VME POWER SUPPLIES: 5 V, 3. 3 V, ± 12 V P 0 FLOTING POWER SUPPLIES: 5 V, ± 15 V

Combiner functionalities VOLTAGES SURVEY 1) HV SUPPLIES 2) VME & P 0 floating PS Survey VME PS Survey P 0 floating PS Survey HV PS

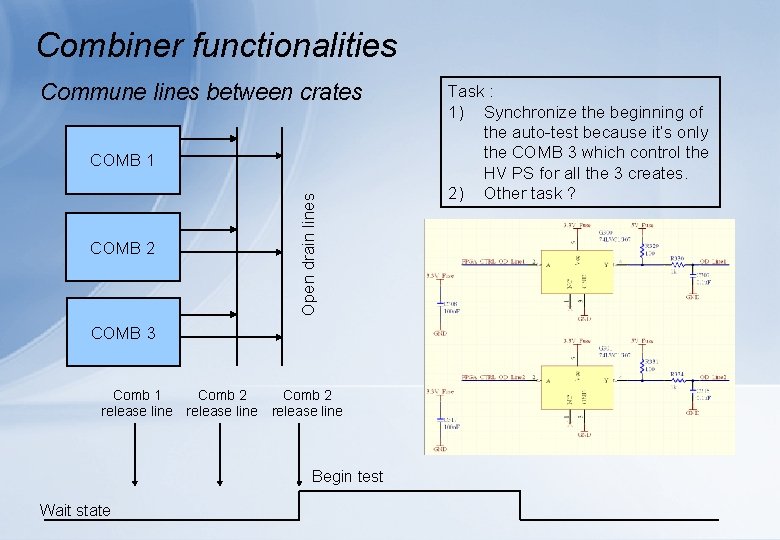

Combiner functionalities Commune lines between crates COMB 2 Open drain lines COMB 1 COMB 3 Comb 1 Comb 2 release line Begin test Wait state Task : 1) Synchronize the beginning of the auto-test because it’s only the COMB 3 which control the HV PS for all the 3 creates. 2) Other task ?

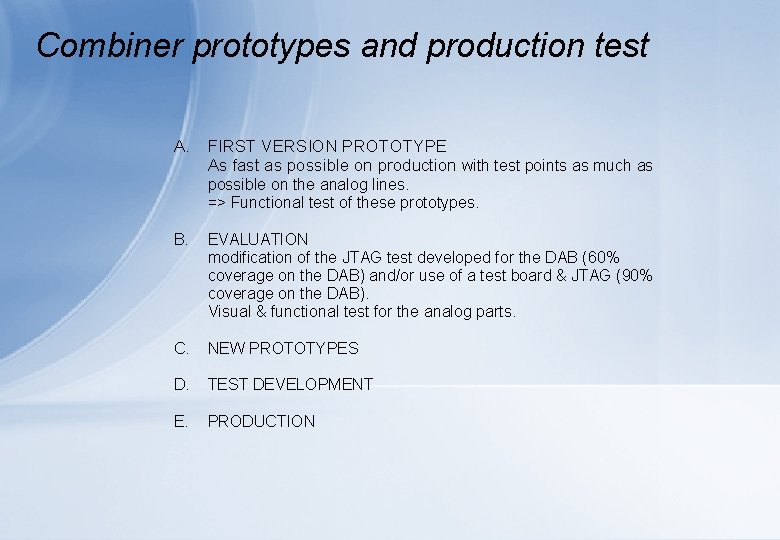

Combiner prototypes and production test A. FIRST VERSION PROTOTYPE As fast as possible on production with test points as much as possible on the analog lines. => Functional test of these prototypes. B. EVALUATION modification of the JTAG test developed for the DAB (60% coverage on the DAB) and/or use of a test board & JTAG (90% coverage on the DAB). Visual & functional test for the analog parts. C. NEW PROTOTYPES D. TEST DEVELOPMENT E. PRODUCTION

- Slides: 23