Combinational Logic Other Gate Types Gate classifications Primitive

Combinational Logic: Other Gate Types

Gate classifications • Primitive gate - a gate that can be described using a single primitive operation type (AND or OR) plus an optional inversion(s). • Complex gate - a gate that requires more than one primitive operation type for its description 2

primitive gates ♦ NAND ♦ NOR 3

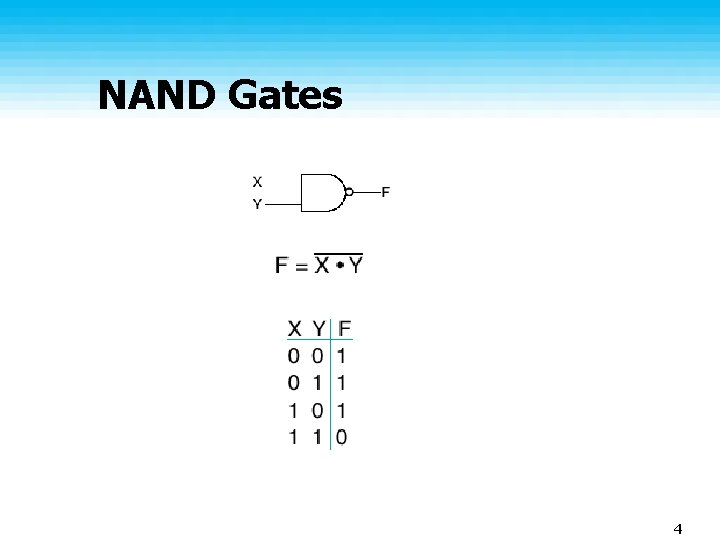

NAND Gates 4

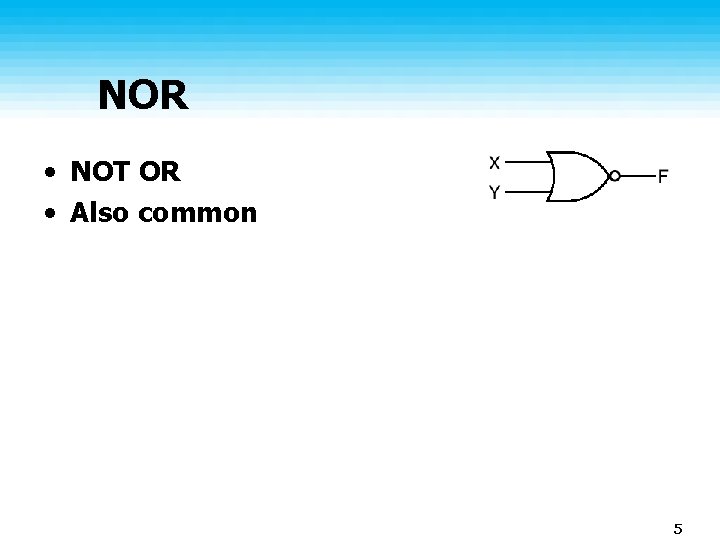

NOR • NOT OR • Also common 5

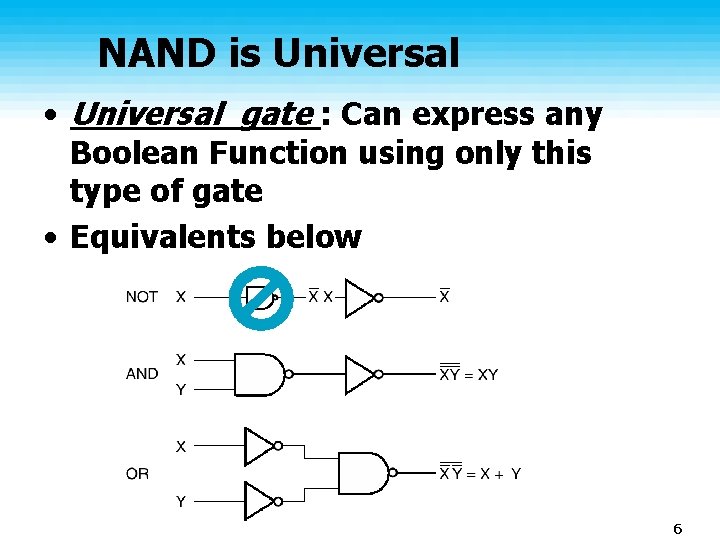

NAND is Universal • Universal gate : Can express any Boolean Function using only this type of gate • Equivalents below 6

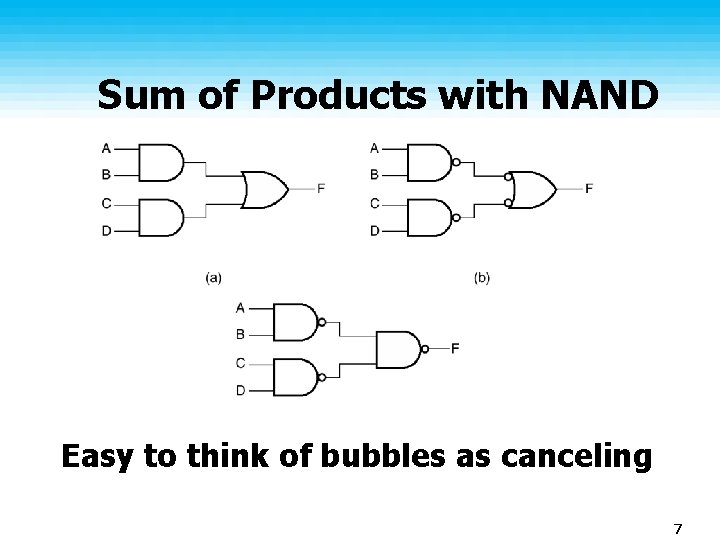

Sum of Products with NAND Easy to think of bubbles as canceling 7

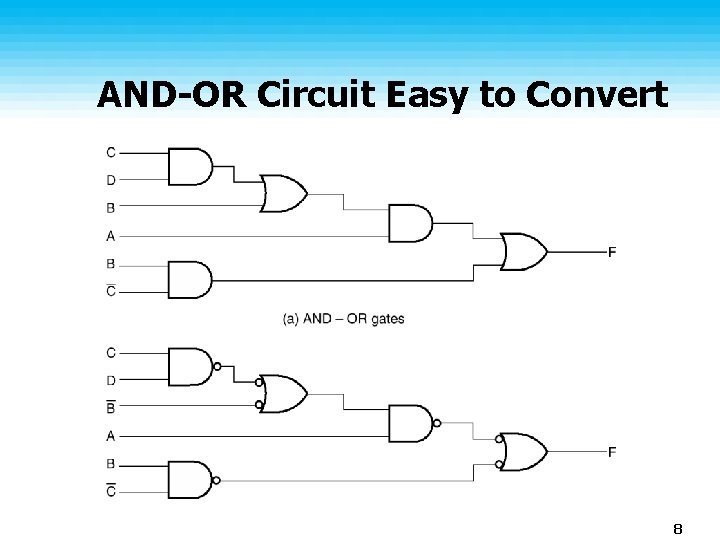

AND-OR Circuit Easy to Convert 8

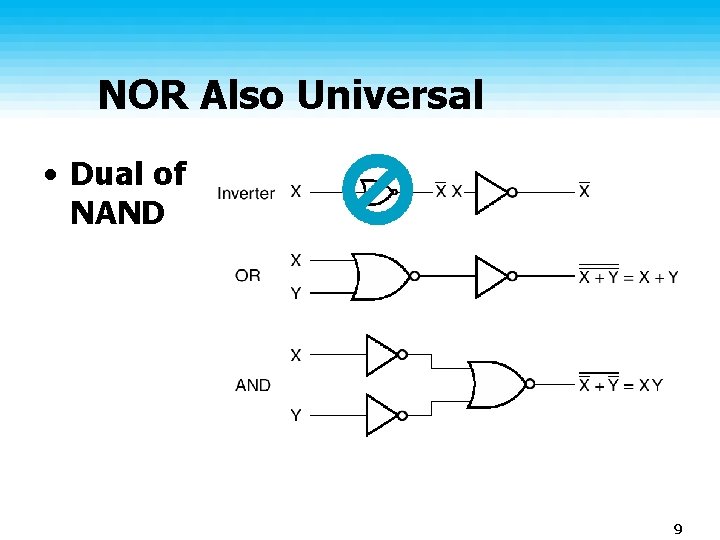

NOR Also Universal • Dual of NAND 9

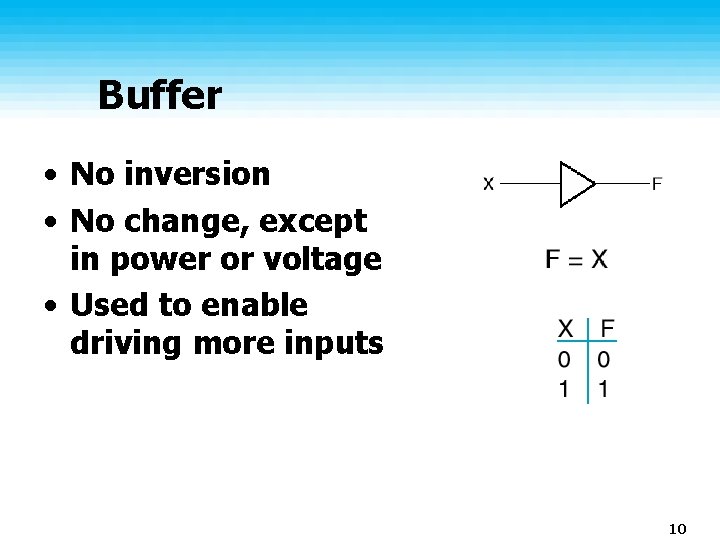

Buffer • No inversion • No change, except in power or voltage • Used to enable driving more inputs 10

Parity Function • How does parity work ? • Given 7 - bit ASCII code for A (100 0001) ♦ What is the ASCII code for A with even parity ? • Write truth table for two input even parity generator • What needs to be generated for parity bit? • What function of two inputs gives you this? ♦ This is called: Exclusive OR function 11

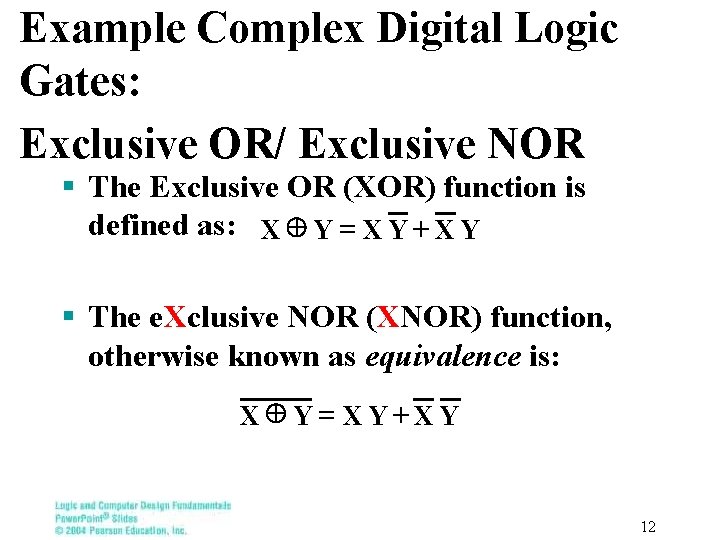

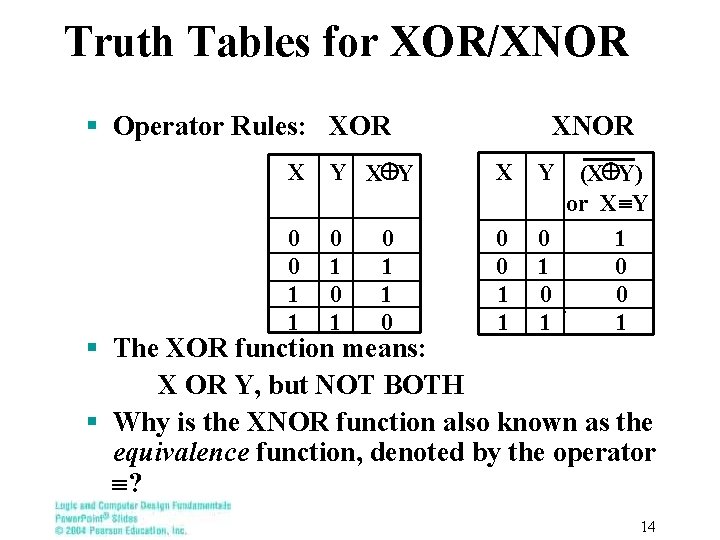

Example Complex Digital Logic Gates: Exclusive OR/ Exclusive NOR § The Exclusive OR (XOR) function is defined as: X Å Y = X Y + X Y § The e. Xclusive NOR (XNOR) function, otherwise known as equivalence is: XÅY = XY+XY 12

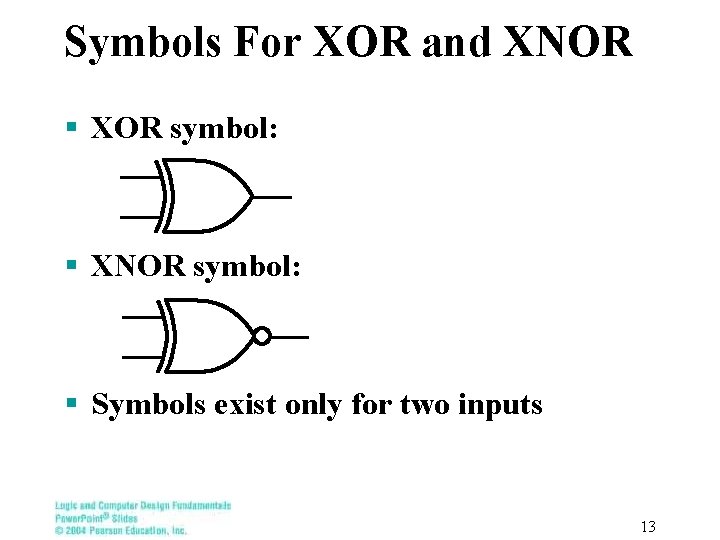

Symbols For XOR and XNOR § XOR symbol: § XNOR symbol: § Symbols exist only for two inputs 13

Truth Tables for XOR/XNOR § Operator Rules: XOR XNOR X Y XÅY X 0 0 1 1 0 1 0 0 1 1 0 Y (XÅY) or X Y 0 1 1 0 0 0 1 1 § The XOR function means: X OR Y, but NOT BOTH § Why is the XNOR function also known as the equivalence function, denoted by the operator ? 14

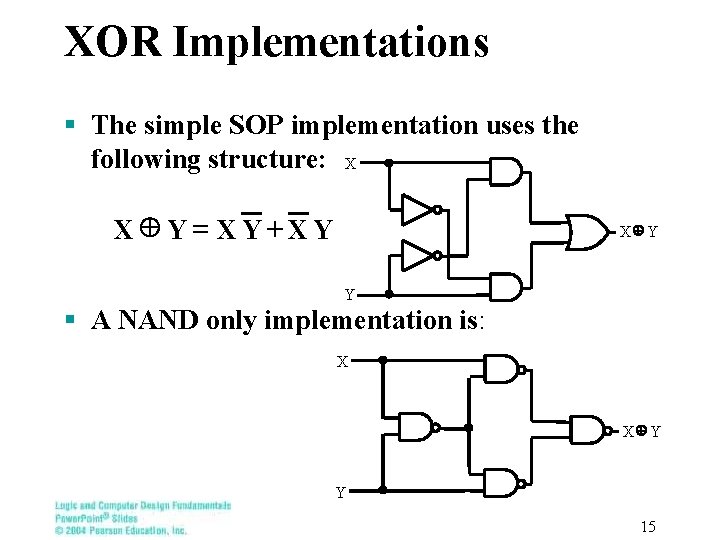

XOR Implementations § The simple SOP implementation uses the following structure: X XÅY = XY+XY X Y Y § A NAND only implementation is: X X Y Y 15

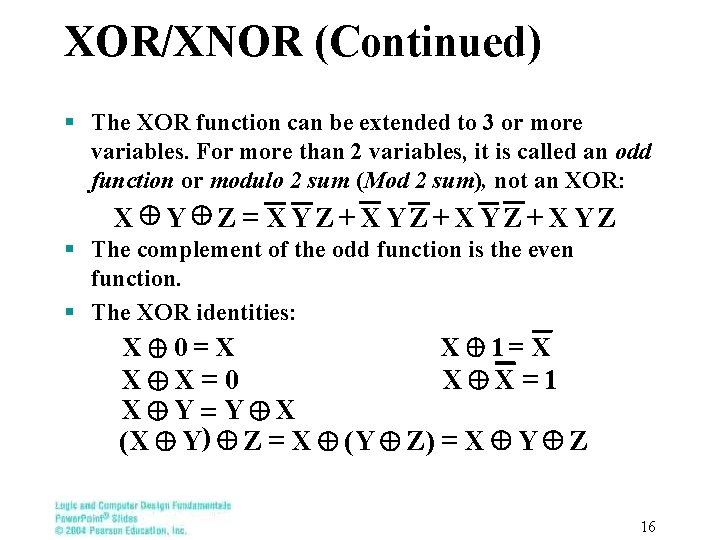

XOR/XNOR (Continued) § The XOR function can be extended to 3 or more variables. For more than 2 variables, it is called an odd function or modulo 2 sum (Mod 2 sum), not an XOR: X Å YÅ Z = XYZ+ XYZ § The complement of the odd function is the even function. § The XOR identities: XÅ0 = X X Å1 = X XÅX =0 XÅX =1 XÅY = YÅX ( X Å Y) Å Z = X Å ( Y Å Z ) = X Å Y Å Z 16

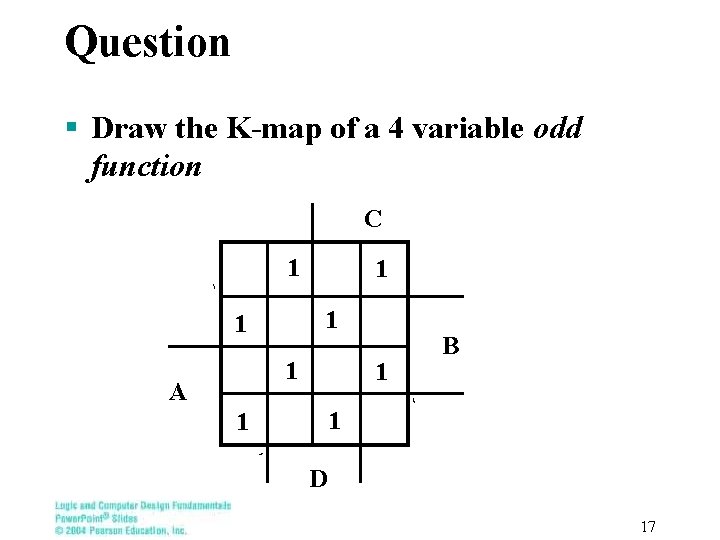

Question § Draw the K-map of a 4 variable odd function C 1 1 1 A 1 B 1 1 D 17

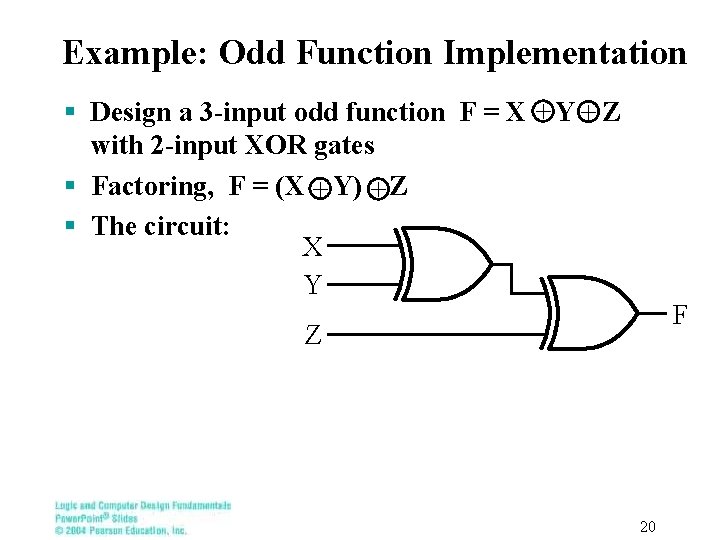

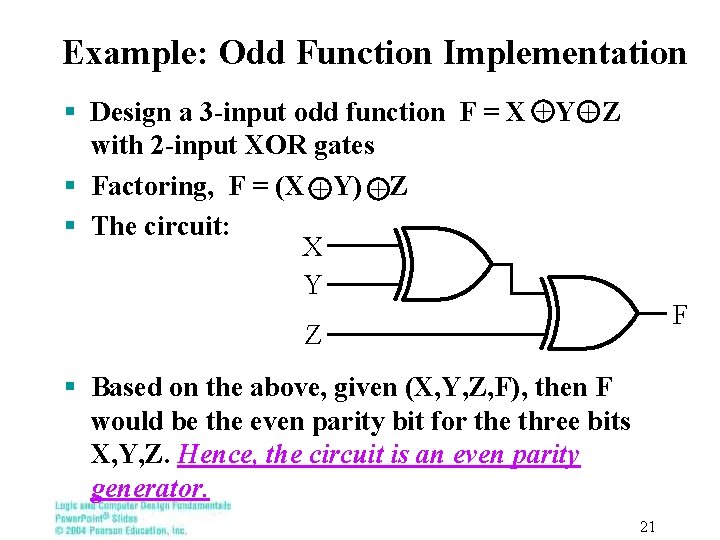

Example: Odd Function Implementation § Design a 3 -input odd function F = X + Y + Z with 2 -input XOR gates 18

Example: Odd Function Implementation § Design a 3 -input odd function F = X + Y + Z with 2 -input XOR gates § Factoring, F = (X + Y) + Z 19

Example: Odd Function Implementation § Design a 3 -input odd function F = X + Y + Z with 2 -input XOR gates § Factoring, F = (X + Y) + Z § The circuit: X Y F Z 20

Example: Odd Function Implementation § Design a 3 -input odd function F = X + Y + Z with 2 -input XOR gates § Factoring, F = (X + Y) + Z § The circuit: X Y F Z § Based on the above, given (X, Y, Z, F), then F would be the even parity bit for the three bits X, Y, Z. Hence, the circuit is an even parity generator. 21

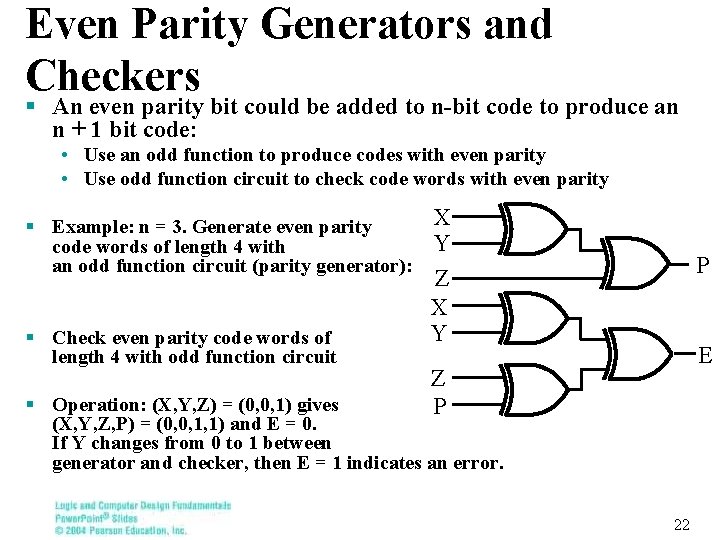

Even Parity Generators and Checkers § An even parity bit could be added to n-bit code to produce an n + 1 bit code: • Use an odd function to produce codes with even parity • Use odd function circuit to check code words with even parity § Example: n = 3. Generate even parity code words of length 4 with an odd function circuit (parity generator): § Check even parity code words of length 4 with odd function circuit X Y Z X Y P E Z P § Operation: (X, Y, Z) = (0, 0, 1) gives (X, Y, Z, P) = (0, 0, 1, 1) and E = 0. If Y changes from 0 to 1 between generator and checker, then E = 1 indicates an error. 22

Odd Parity Generators and Checkers Similarly, an odd parity bit could be added to n-bit code to produce an n + 1 bit code • Use an even function to produce codes with odd parity • Use even function circuit to check code words with odd parity 23

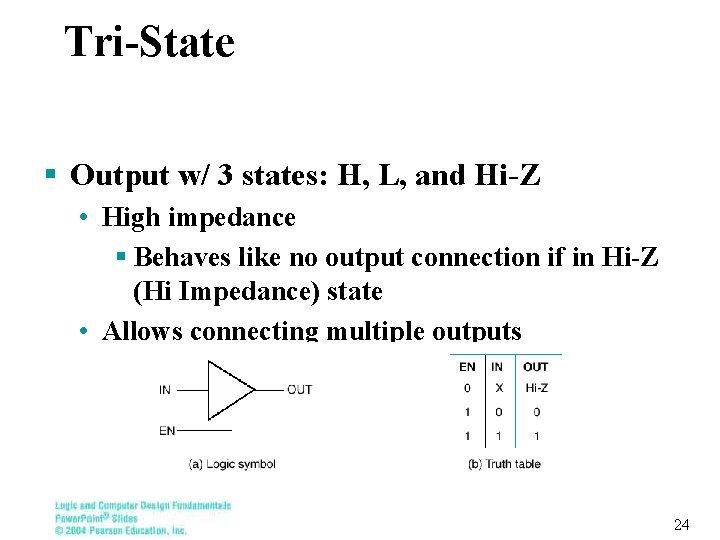

Tri-State § Output w/ 3 states: H, L, and Hi-Z • High impedance § Behaves like no output connection if in Hi-Z (Hi Impedance) state • Allows connecting multiple outputs 24

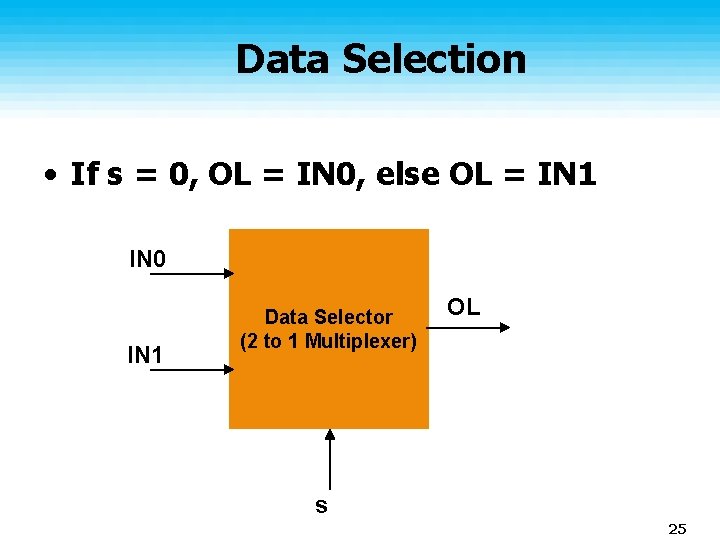

Data Selection • If s = 0, OL = IN 0, else OL = IN 1 IN 0 IN 1 Data Selector (2 to 1 Multiplexer) OL s 25

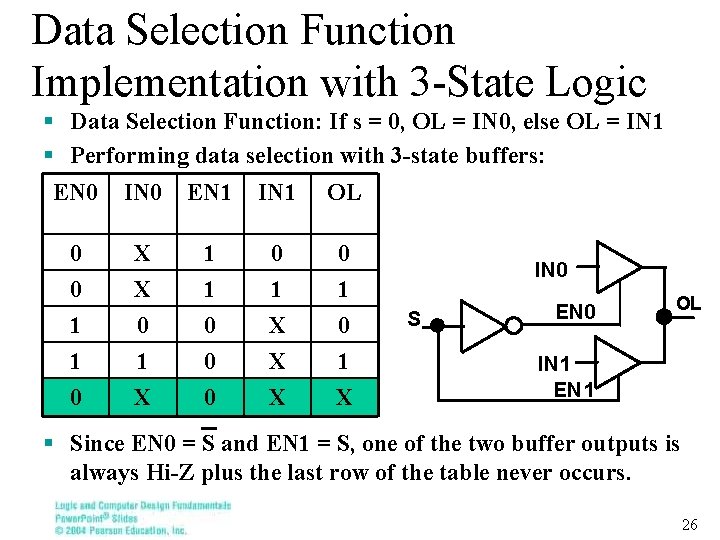

Data Selection Function Implementation with 3 -State Logic § Data Selection Function: If s = 0, OL = IN 0, else OL = IN 1 § Performing data selection with 3 -state buffers: EN 0 IN 0 EN 1 IN 1 OL 0 0 X X 1 1 0 1 1 1 0 0 1 X 0 0 0 X X X 0 1 X IN 0 S EN 0 OL IN 1 EN 1 § Since EN 0 = S and EN 1 = S, one of the two buffer outputs is always Hi-Z plus the last row of the table never occurs. 26

- Slides: 26