Combinational Logic mostly review z Logic functions truth

Combinational Logic (mostly review!) z Logic functions, truth tables, and switches y NOT, AND, OR, NAND, NOR, XOR, . . . y Minimal set z Axioms and theorems of Boolean algebra y Proofs by re-writing y Proofs by perfect induction z Gate logic y Networks of Boolean functions y Time behavior z Canonical forms y Two-level y Incompletely specified functions CS 150 - Fall 2005 – Lec #2: Combinational Logic - 1

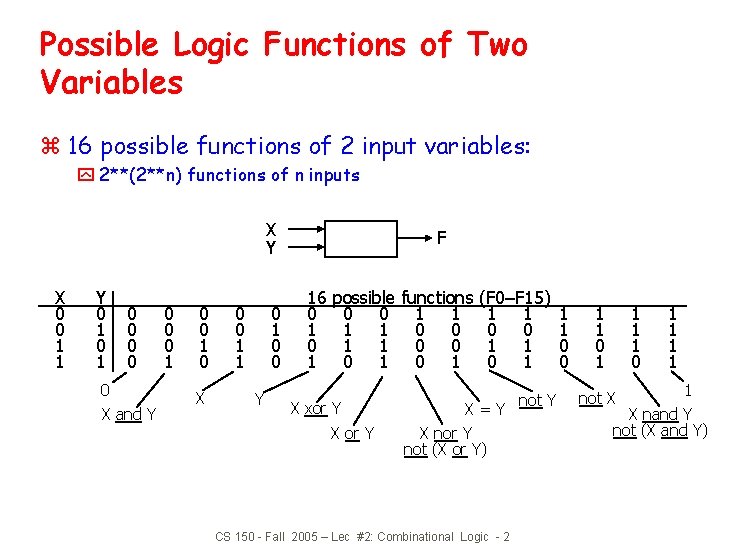

Possible Logic Functions of Two Variables z 16 possible functions of 2 input variables: y 2**(2**n) functions of n inputs X Y X 0 0 1 1 Y 0 1 0 0 0 X and Y 0 0 0 1 0 X 0 0 1 1 0 0 Y F 16 0 1 possible functions (F 0–F 15) 0 0 1 1 1 0 0 1 1 0 1 0 1 X xor Y X=Y X nor Y not (X or Y) CS 150 - Fall 2005 – Lec #2: Combinational Logic - 2 not Y 1 1 0 0 1 1 1 1 0 1 1 1 X nand Y not (X and Y) not X

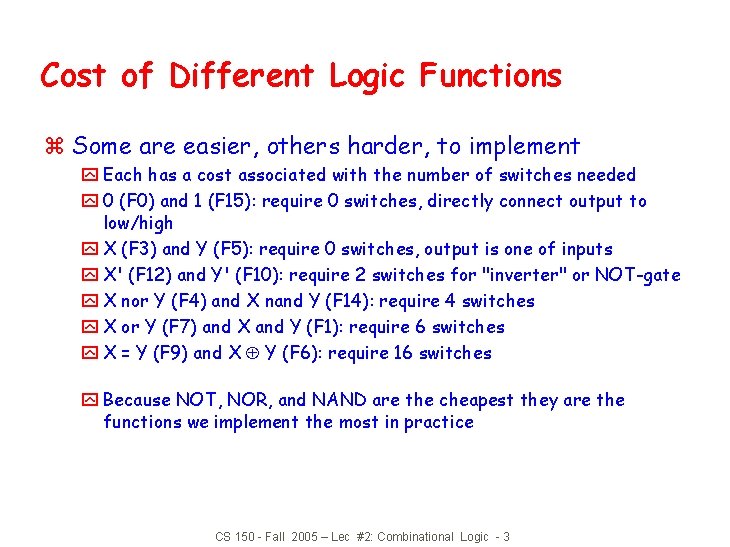

Cost of Different Logic Functions z Some are easier, others harder, to implement y Each has a cost associated with the number of switches needed y 0 (F 0) and 1 (F 15): require 0 switches, directly connect output to low/high y X (F 3) and Y (F 5): require 0 switches, output is one of inputs y X' (F 12) and Y' (F 10): require 2 switches for "inverter" or NOT-gate y X nor Y (F 4) and X nand Y (F 14): require 4 switches y X or Y (F 7) and X and Y (F 1): require 6 switches y X = Y (F 9) and X Y (F 6): require 16 switches y Because NOT, NOR, and NAND are the cheapest they are the functions we implement the most in practice CS 150 - Fall 2005 – Lec #2: Combinational Logic - 3

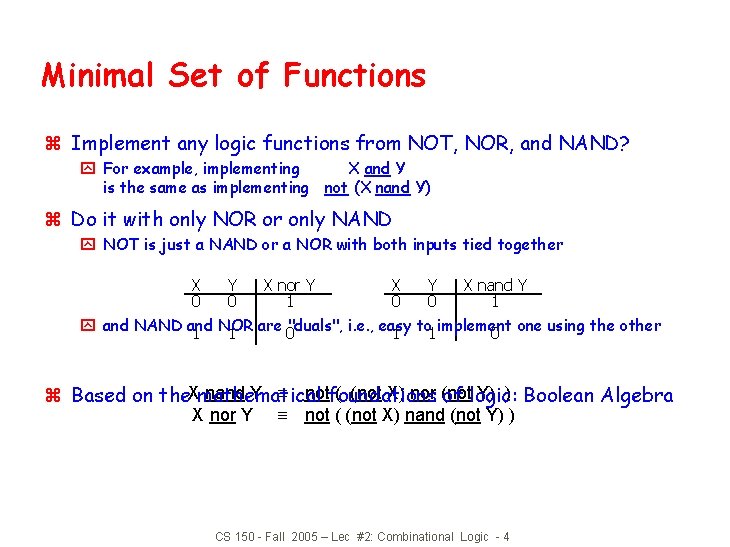

Minimal Set of Functions z Implement any logic functions from NOT, NOR, and NAND? y For example, implementing X and Y is the same as implementing not (X nand Y) z Do it with only NOR or only NAND y NOT is just a NAND or a NOR with both inputs tied together X Y X nor Y X nand Y 0 0 1 y and NAND and NOR are "duals", i. e. , easy to implement one using the other 1 1 0 nand Y notfoundations ( (not X) nor (not Y) ) Boolean Algebra z Based on the. Xmathematical of logic: X nor Y not ( (not X) nand (not Y) ) CS 150 - Fall 2005 – Lec #2: Combinational Logic - 4

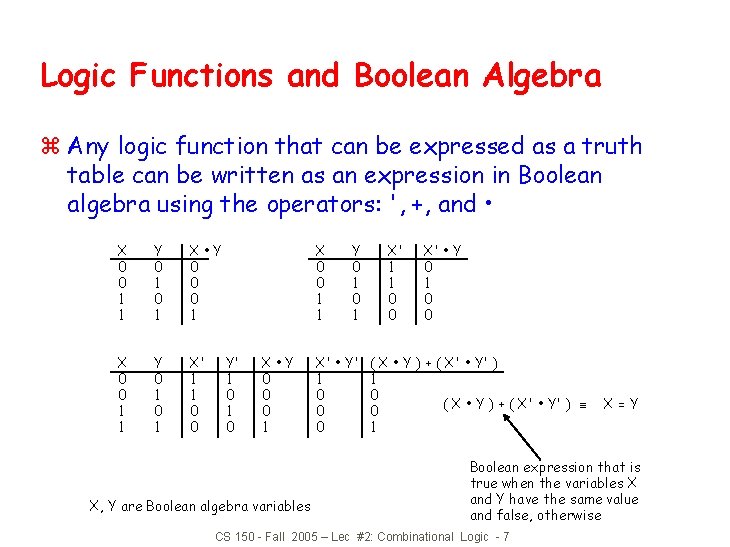

Logic Functions and Boolean Algebra z Any logic function that can be expressed as a truth table can be written as an expression in Boolean algebra using the operators: ', +, and • X 0 0 1 1 Y 0 1 X • Y 0 0 0 1 X 0 0 1 1 Y 0 1 X' 1 1 0 0 X 0 0 1 1 Y' 1 0 X • Y 0 0 0 1 X, Y are Boolean algebra variables Y 0 1 X' • Y' 1 0 0 0 X' 1 1 0 0 X' • Y 0 1 0 0 ( X • Y ) + ( X' • Y' ) 1 0 ( X • Y ) + ( X' • Y' ) 0 1 X = Y Boolean expression that is true when the variables X and Y have the same value and false, otherwise CS 150 - Fall 2005 – Lec #2: Combinational Logic - 7

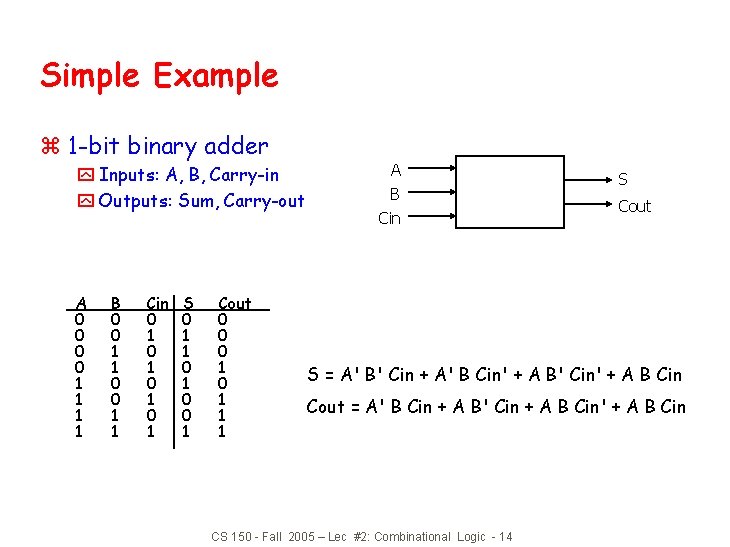

Simple Example z 1 -bit binary adder y Inputs: A, B, Carry-in y Outputs: Sum, Carry-out A 0 0 1 1 B 0 0 1 1 Cin 0 1 0 1 S 0 1 1 0 0 1 Cout 0 0 0 1 1 1 A B Cin S Cout S = A' B' Cin + A' B Cin' + A B' Cin' + A B Cin Cout = A' B Cin + A B' Cin + A B Cin' + A B Cin CS 150 - Fall 2005 – Lec #2: Combinational Logic - 14

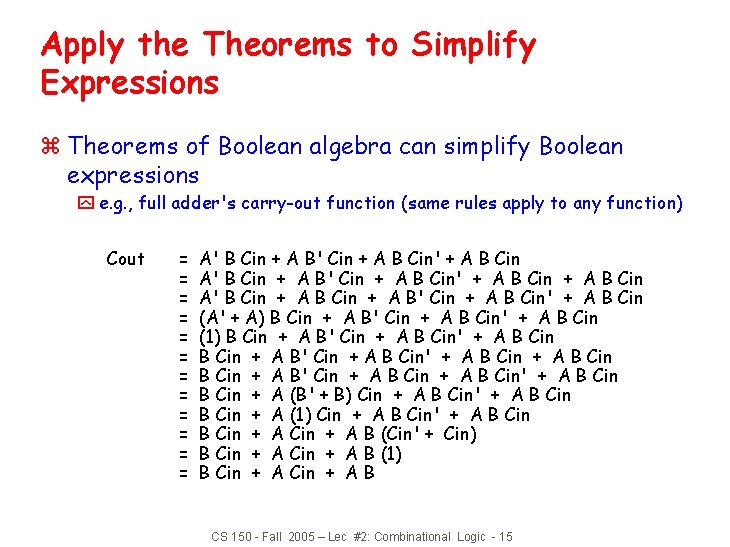

Apply the Theorems to Simplify Expressions z Theorems of Boolean algebra can simplify Boolean expressions y e. g. , full adder's carry-out function (same rules apply to any function) Cout = = = A' B Cin + A B' Cin + A B Cin' + A B Cin A' B Cin + A B' Cin + A B Cin' + A B Cin (A' + A) B Cin + A B' Cin + A B Cin' + A B Cin (1) B Cin + A B' Cin + A B Cin' + A B Cin + A (B' + B) Cin + A B Cin' + A B Cin + A (1) Cin + A B Cin' + A B Cin + A B (Cin' + Cin) B Cin + A B (1) B Cin + A B CS 150 - Fall 2005 – Lec #2: Combinational Logic - 15

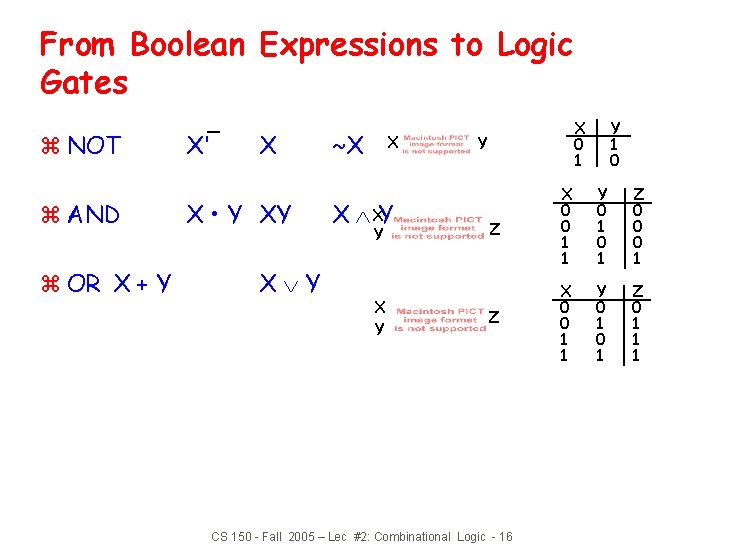

From Boolean Expressions to Logic Gates z NOT z AND z OR X + Y X' X X • Y XY X Y ~X X X XY Y X 0 1 Y Y 1 0 Z X 0 0 1 1 Y 0 1 Z 0 0 0 1 Z X 0 0 1 1 Y 0 1 Z 0 1 1 1 CS 150 - Fall 2005 – Lec #2: Combinational Logic - 16

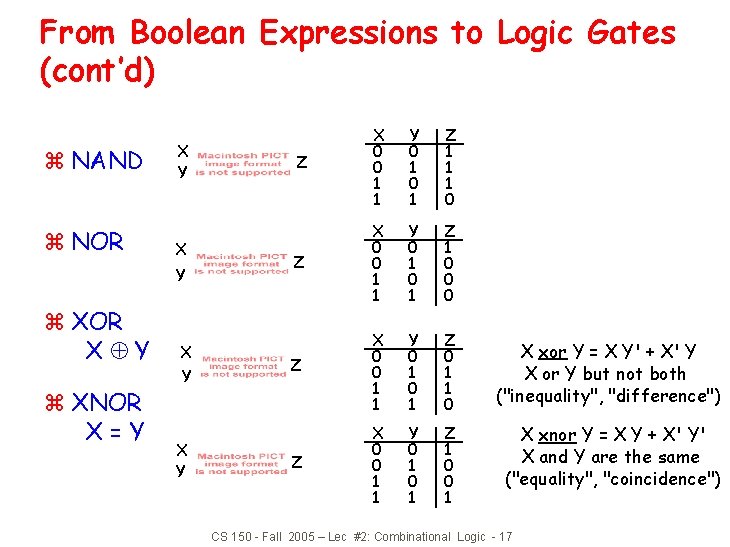

From Boolean Expressions to Logic Gates (cont’d) z NAND z NOR X Y z XOR X Y z XNOR X=Y X Y Z X 0 0 1 1 Y 0 1 Z 1 1 1 0 Z X 0 0 1 1 Y 0 1 Z 1 0 0 0 Z X 0 0 1 1 Y 0 1 Z 0 1 1 0 Z X 0 0 1 1 Y 0 1 Z 1 0 0 1 X xor Y = X Y' + X' Y X or Y but not both ("inequality", "difference") X xnor Y = X Y + X' Y' X and Y are the same ("equality", "coincidence") CS 150 - Fall 2005 – Lec #2: Combinational Logic - 17

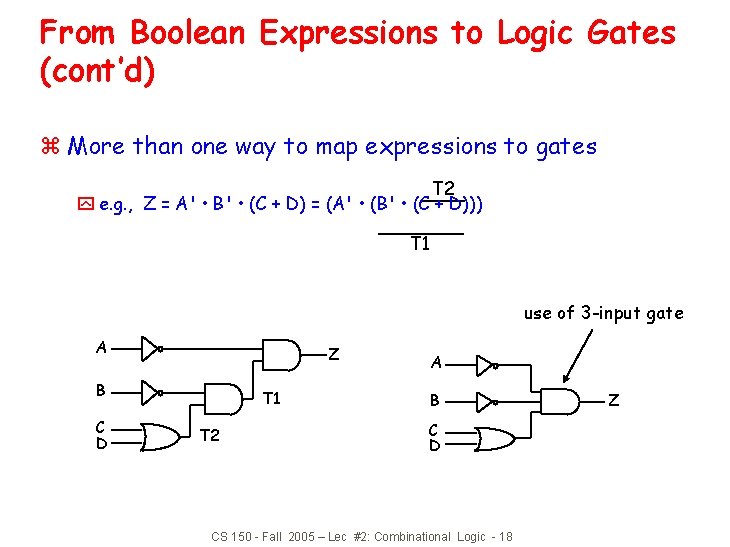

From Boolean Expressions to Logic Gates (cont’d) z More than one way to map expressions to gates T 2 y e. g. , Z = A' • B' • (C + D) = (A' • (B' • (C + D))) T 1 use of 3 -input gate A Z B C D T 1 T 2 A B C D CS 150 - Fall 2005 – Lec #2: Combinational Logic - 18 Z

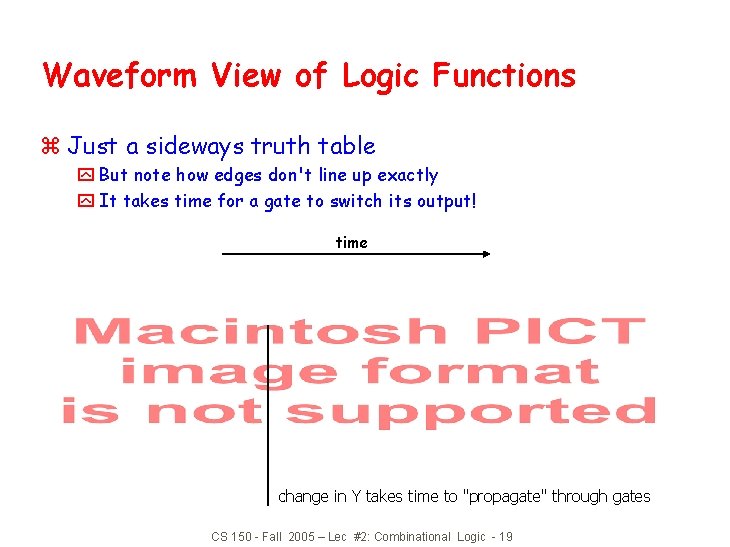

Waveform View of Logic Functions z Just a sideways truth table y But note how edges don't line up exactly y It takes time for a gate to switch its output! time change in Y takes time to "propagate" through gates CS 150 - Fall 2005 – Lec #2: Combinational Logic - 19

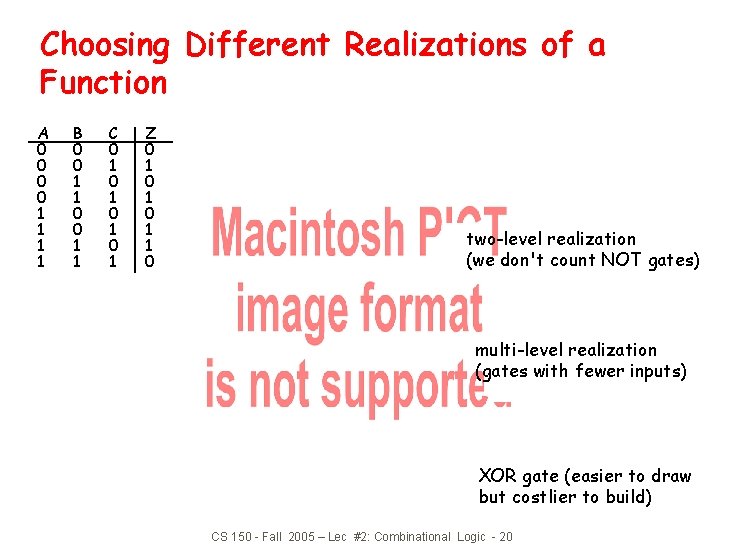

Choosing Different Realizations of a Function A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 Z 0 1 0 1 1 0 two-level realization (we don't count NOT gates) multi-level realization (gates with fewer inputs) XOR gate (easier to draw but costlier to build) CS 150 - Fall 2005 – Lec #2: Combinational Logic - 20

Which Realization is Best? z Reduce number of inputs y literal: input variable (complemented or not) xcan approximate cost of logic gate as 2 transistors per literal xwhy not count inverters? y Fewer literals means less transistors xsmaller circuits y Fewer inputs implies faster gates xgates are smaller and thus also faster y Fan-ins (# of gate inputs) are limited in some technologies z Reduce number of gates y Fewer gates (and the packages they come in) means smaller circuits xdirectly influences manufacturing costs CS 150 - Fall 2005 – Lec #2: Combinational Logic - 21

Which is the Best Realization? (cont’d) z Reduce number of levels of gates y Fewer level of gates implies reduced signal propagation delays y Minimum delay configuration typically requires more gates xwider, less deep circuits z How do we explore tradeoffs between increased circuit delay and size? y Automated tools to generate different solutions y Logic minimization: reduce number of gates and complexity y Logic optimization: reduction while trading off against delay CS 150 - Fall 2005 – Lec #2: Combinational Logic - 22

Are All Realizations Equivalent? z Under the same inputs, the alternative implementations have almost the same waveform behavior y Delays are different y Glitches (hazards) may arise y Variations due to differences in number of gate levels and structure z Three implementations are functionally equivalent CS 150 - Fall 2005 – Lec #2: Combinational Logic - 23

Implementing Boolean Functions z Technology independent y Canonical forms y Two-level forms y Multi-level forms z Technology choices y Packages of a few gates y Regular logic y Two-level programmable logic y Multi-level programmable logic CS 150 - Fall 2005 – Lec #2: Combinational Logic - 24

Canonical Forms z Truth table is the unique signature of a Boolean function z Many alternative gate realizations may have the same truth table z Canonical forms y Standard forms for a Boolean expression y Provides a unique algebraic signature CS 150 - Fall 2005 – Lec #2: Combinational Logic - 25

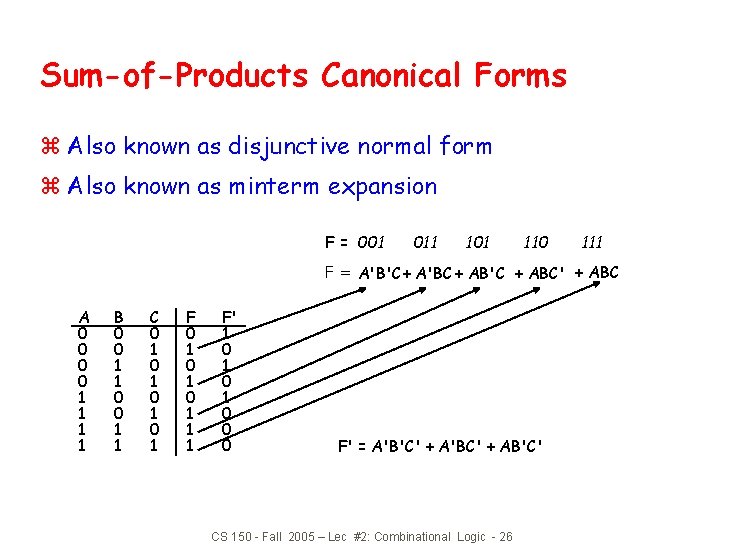

Sum-of-Products Canonical Forms z Also known as disjunctive normal form z Also known as minterm expansion F = 001 011 101 110 111 F = A'B'C + A'BC + AB'C + ABC' + ABC A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 F 0 1 0 1 1 1 F' 1 0 1 0 0 0 F' = A'B'C' + A'BC' + AB'C' CS 150 - Fall 2005 – Lec #2: Combinational Logic - 26

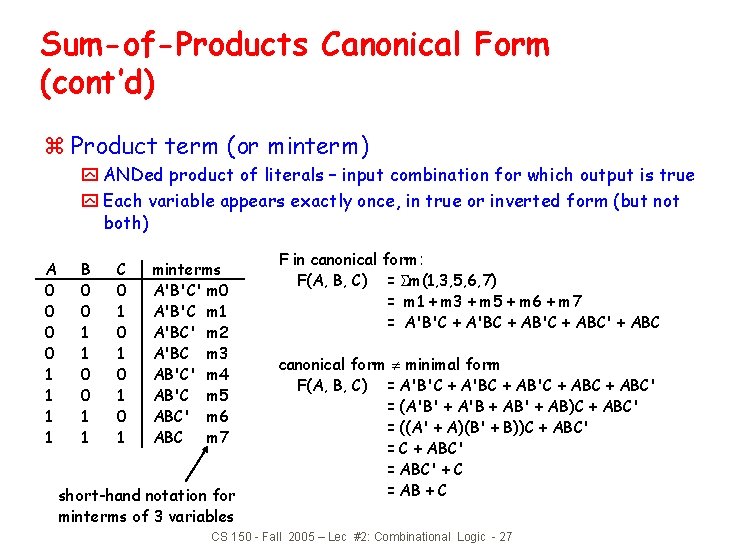

Sum-of-Products Canonical Form (cont’d) z Product term (or minterm) y ANDed product of literals – input combination for which output is true y Each variable appears exactly once, in true or inverted form (but not both) A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 minterms A'B'C' m 0 A'B'C m 1 A'BC' m 2 A'BC m 3 AB'C' m 4 AB'C m 5 ABC' m 6 ABC m 7 short-hand notation for minterms of 3 variables F in canonical form: F(A, B, C) = m(1, 3, 5, 6, 7) = m 1 + m 3 + m 5 + m 6 + m 7 = A'B'C + A'BC + AB'C + ABC' + ABC canonical form minimal form F(A, B, C) = A'B'C + A'BC + AB'C + ABC' = (A'B' + A'B + AB' + AB)C + ABC' = ((A' + A)(B' + B))C + ABC' = ABC' + C = AB + C CS 150 - Fall 2005 – Lec #2: Combinational Logic - 27

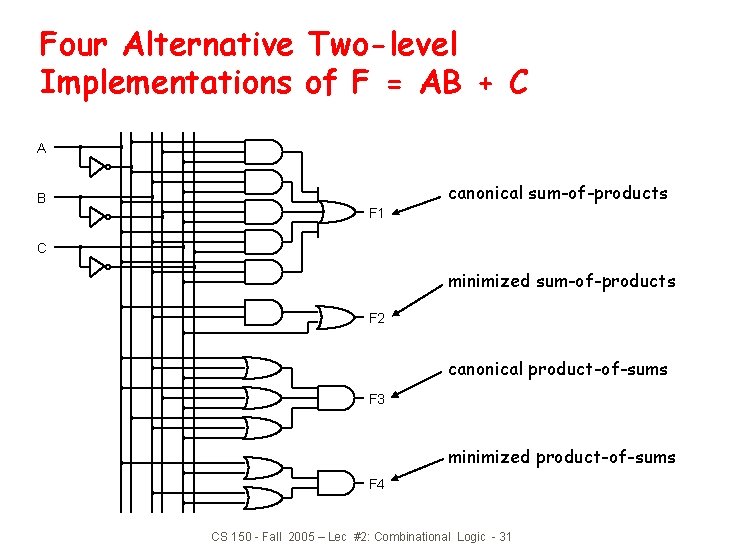

Four Alternative Two-level Implementations of F = AB + C A B canonical sum-of-products F 1 C minimized sum-of-products F 2 canonical product-of-sums F 3 minimized product-of-sums F 4 CS 150 - Fall 2005 – Lec #2: Combinational Logic - 31

Waveforms for the Four Alternatives z Waveforms are essentially identical y Except for timing hazards (glitches) y Delays almost identical (modeled as a delay per level, not type of gate or number of inputs to gate) CS 150 - Fall 2005 – Lec #2: Combinational Logic - 32

Mapping Between Canonical Forms z Minterm to maxterm conversion y Use maxterms whose indices do not appear in minterm expansion y e. g. , F(A, B, C) = m(1, 3, 5, 6, 7) = M(0, 2, 4) z Maxterm to minterm conversion y Use minterms whose indices do not appear in maxterm expansion y e. g. , F(A, B, C) = M(0, 2, 4) = m(1, 3, 5, 6, 7) z Minterm expansion of F to minterm expansion of F' y Use minterms whose indices do not appear y e. g. , F(A, B, C) = m(1, 3, 5, 6, 7) F'(A, B, C) = m(0, 2, 4) z Maxterm expansion of F to maxterm expansion of F' y Use maxterms whose indices do not appear y e. g. , F(A, B, C) = M(0, 2, 4) F'(A, B, C) = M(1, 3, 5, 6, 7) CS 150 - Fall 2005 – Lec #2: Combinational Logic - 33

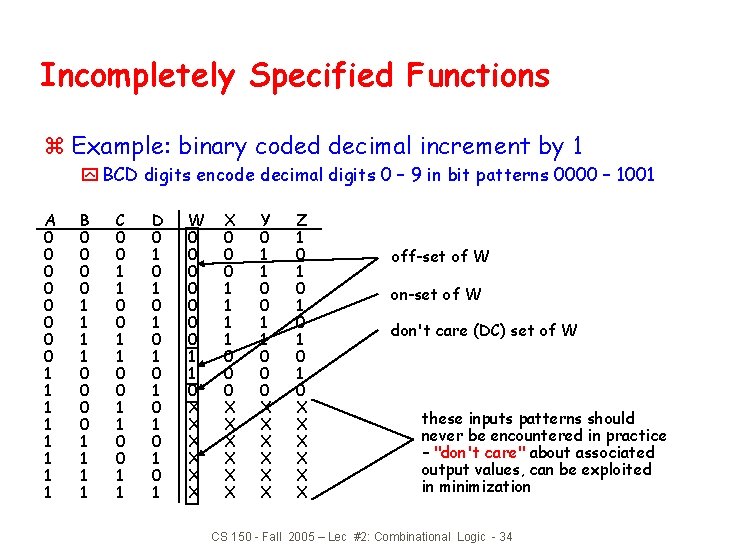

Incompletely Specified Functions z Example: binary coded decimal increment by 1 y BCD digits encode decimal digits 0 – 9 in bit patterns 0000 – 1001 A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 D 0 1 0 1 W 0 0 0 0 1 1 0 X X X X 0 0 0 1 1 0 0 0 X X X Y 0 1 1 0 0 0 X X X Z 1 0 1 0 1 0 X X X off-set of W on-set of W don't care (DC) set of W these inputs patterns should never be encountered in practice – "don't care" about associated output values, can be exploited in minimization CS 150 - Fall 2005 – Lec #2: Combinational Logic - 34

Notation for Incompletely Specified Functions z Don't cares and canonical forms y So far, only represented on-set y Also represent don't-care-set y Need two of the three sets (on-set, off-set, dc-set) z Canonical representations of the BCD increment by 1 function: y Z = m 0 + m 2 + m 4 + m 6 + m 8 + d 10 + d 11 + d 12 + d 13 + d 14 + d 15 y Z = [ m(0, 2, 4, 6, 8) + d(10, 11, 12, 13, 14, 15) ] y Z = M 1 • M 3 • M 5 • M 7 • M 9 • D 10 • D 11 • D 12 • D 13 • D 14 • D 15 y Z = [ M(1, 3, 5, 7, 9) • D(10, 11, 12, 13, 14, 15) ] CS 150 - Fall 2005 – Lec #2: Combinational Logic - 35

Administrative Announcement z All discussion sections to meet in 125 Cory z Moving F 10 -11 AM discussion to F 11 -noon z Students on wait list: y W 9 -12 Lab is still available y W 5 -8 lab is at capacity y We can take a VERY small number of students into the Tu labs y Email your preference to Head TA Po-Kai z Instructional Web now mirrors Randy’s web site y http: //inst. eecs. Berkeley. edu/~cs 150 y HW #1 and Lab #1 now on-line CS 150 - Fall 2005 – Lec #2: Combinational Logic - 37

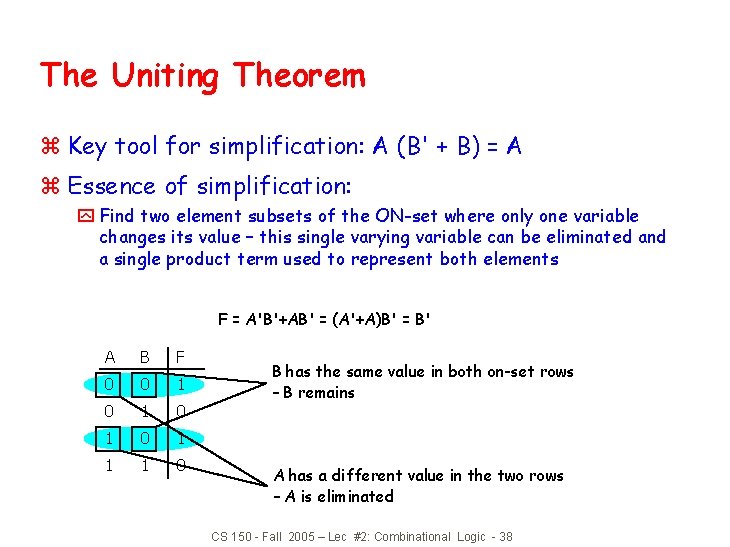

The Uniting Theorem z Key tool for simplification: A (B' + B) = A z Essence of simplification: y Find two element subsets of the ON-set where only one variable changes its value – this single varying variable can be eliminated and a single product term used to represent both elements F = A'B'+AB' = (A'+A)B' = B' A B F 0 0 1 0 1 1 1 0 B has the same value in both on-set rows – B remains A has a different value in the two rows – A is eliminated CS 150 - Fall 2005 – Lec #2: Combinational Logic - 38

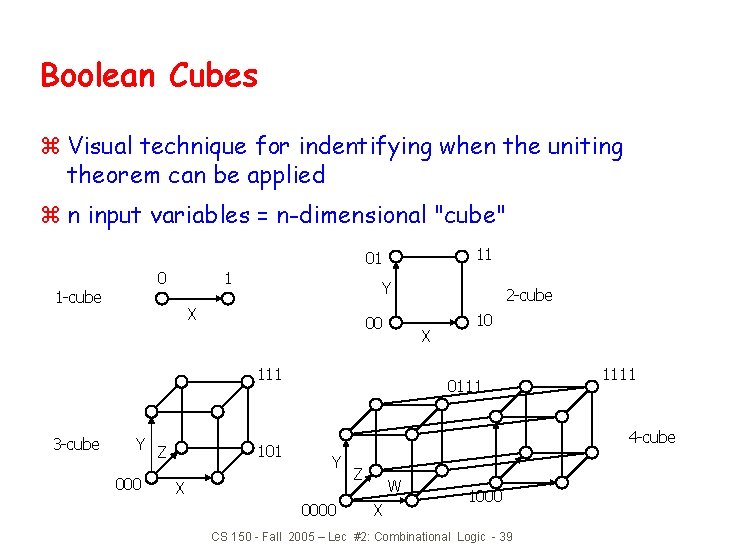

Boolean Cubes z Visual technique for indentifying when the uniting theorem can be applied z n input variables = n-dimensional "cube" 11 01 0 1 -cube 1 Y X 00 X 111 3 -cube Y Z 000 101 2 -cube 10 0111 1111 4 -cube Y X 0000 Z W X 1000 CS 150 - Fall 2005 – Lec #2: Combinational Logic - 39

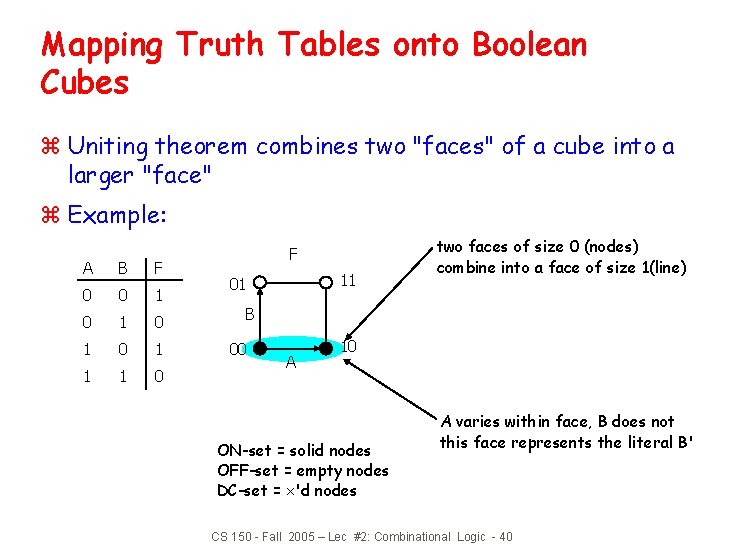

Mapping Truth Tables onto Boolean Cubes z Uniting theorem combines two "faces" of a cube into a larger "face" z Example: A B F 0 0 1 0 1 1 1 0 F 11 01 two faces of size 0 (nodes) combine into a face of size 1(line) B 00 A 10 ON-set = solid nodes OFF-set = empty nodes DC-set = 'd nodes A varies within face, B does not this face represents the literal B' CS 150 - Fall 2005 – Lec #2: Combinational Logic - 40

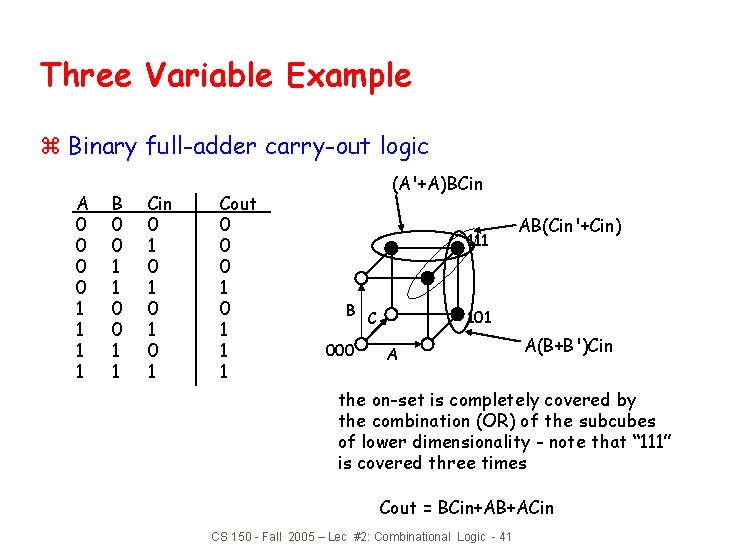

Three Variable Example z Binary full-adder carry-out logic A 0 0 1 1 B 0 0 1 1 Cin 0 1 0 1 Cout 0 0 0 1 1 1 (A'+A)BCin 111 B C 000 AB(Cin'+Cin) 101 A A(B+B')Cin the on-set is completely covered by the combination (OR) of the subcubes of lower dimensionality - note that “ 111” is covered three times Cout = BCin+AB+ACin CS 150 - Fall 2005 – Lec #2: Combinational Logic - 41

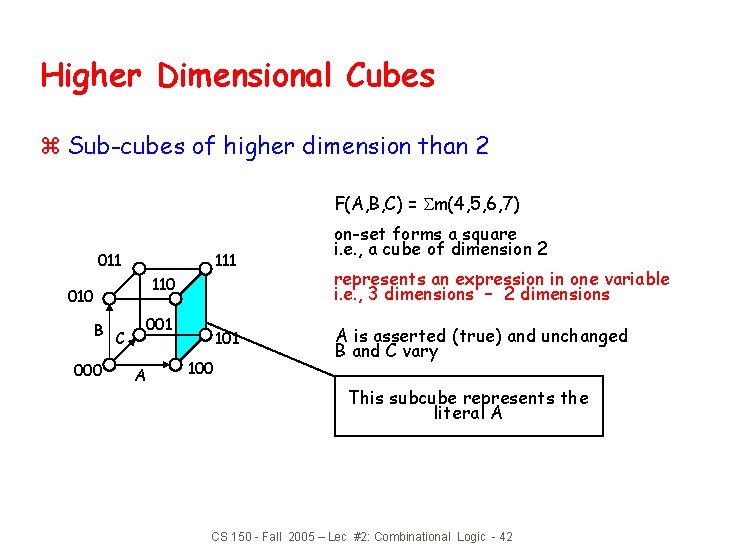

Higher Dimensional Cubes z Sub-cubes of higher dimension than 2 F(A, B, C) = m(4, 5, 6, 7) 011 110 010 B C 000 001 A 101 100 on-set forms a square i. e. , a cube of dimension 2 represents an expression in one variable i. e. , 3 dimensions – 2 dimensions A is asserted (true) and unchanged B and C vary This subcube represents the literal A CS 150 - Fall 2005 – Lec #2: Combinational Logic - 42

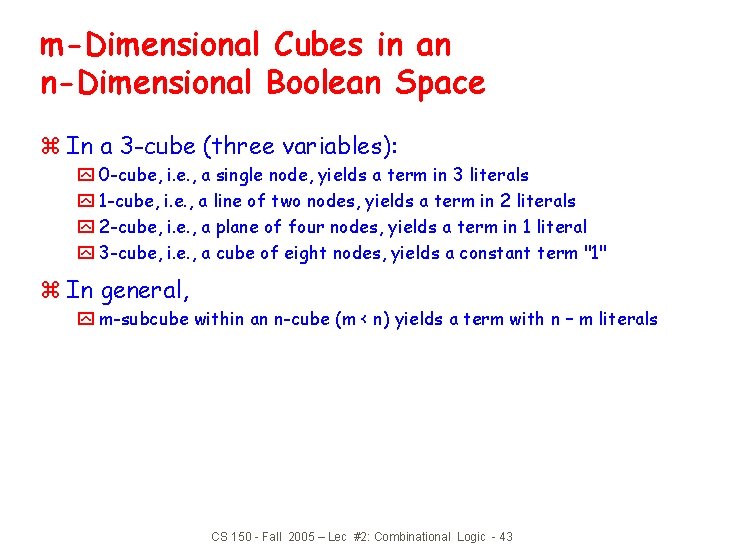

m-Dimensional Cubes in an n-Dimensional Boolean Space z In a 3 -cube (three variables): y 0 -cube, i. e. , a single node, yields a term in 3 literals y 1 -cube, i. e. , a line of two nodes, yields a term in 2 literals y 2 -cube, i. e. , a plane of four nodes, yields a term in 1 literal y 3 -cube, i. e. , a cube of eight nodes, yields a constant term "1" z In general, y m-subcube within an n-cube (m < n) yields a term with n – m literals CS 150 - Fall 2005 – Lec #2: Combinational Logic - 43

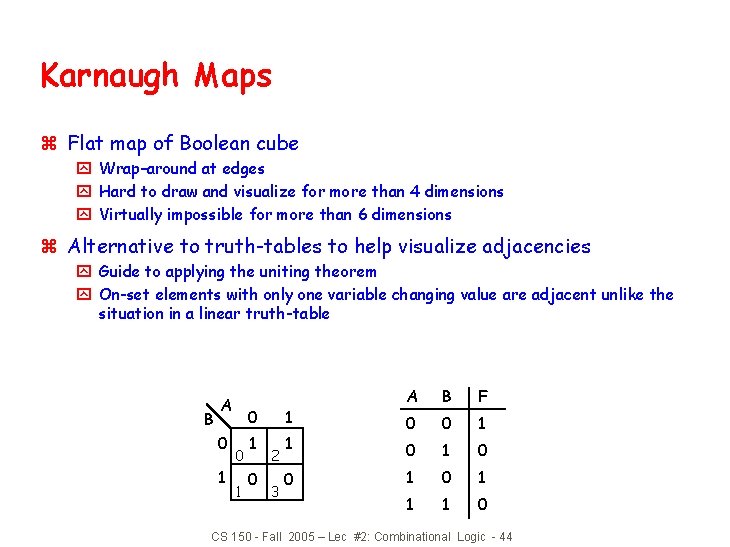

Karnaugh Maps z Flat map of Boolean cube y Wrap–around at edges y Hard to draw and visualize for more than 4 dimensions y Virtually impossible for more than 6 dimensions z Alternative to truth-tables to help visualize adjacencies y Guide to applying the uniting theorem y On-set elements with only one variable changing value are adjacent unlike the situation in a linear truth-table B A 0 1 0 0 1 1 0 1 2 3 1 0 A B F 0 0 1 0 1 1 1 0 CS 150 - Fall 2005 – Lec #2: Combinational Logic - 44

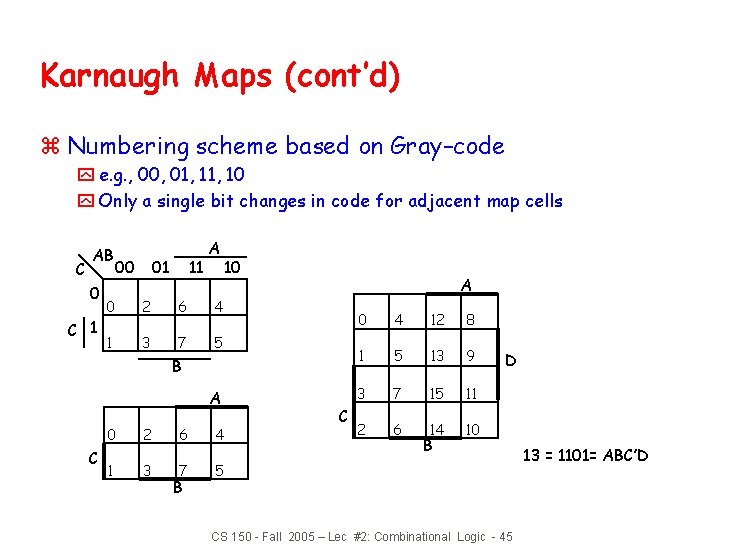

Karnaugh Maps (cont’d) z Numbering scheme based on Gray–code y e. g. , 00, 01, 10 y Only a single bit changes in code for adjacent map cells C AB 0 C 1 00 11 01 A 0 2 6 4 1 3 7 5 10 A B A C 0 2 6 4 1 3 7 5 B C 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 B D CS 150 - Fall 2005 – Lec #2: Combinational Logic - 45 13 = 1101= ABC’D

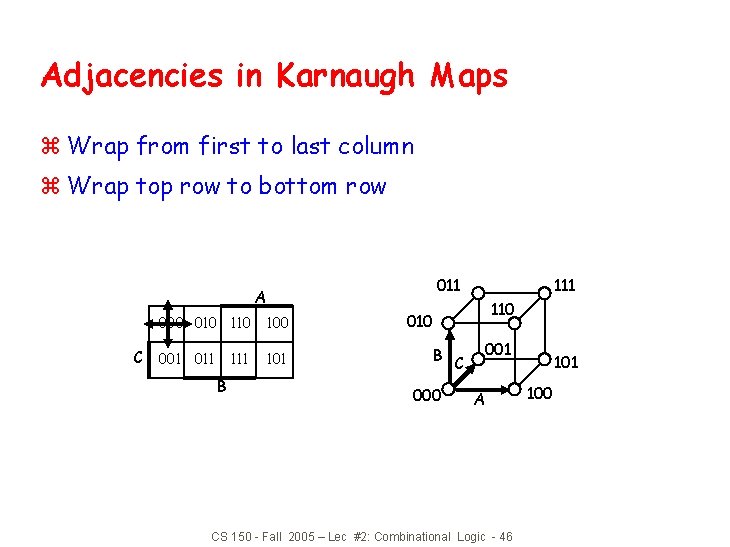

Adjacencies in Karnaugh Maps z Wrap from first to last column z Wrap top row to bottom row 011 A 000 010 100 C 001 011 101 B 111 110 010 B C 000 001 A CS 150 - Fall 2005 – Lec #2: Combinational Logic - 46 101 100

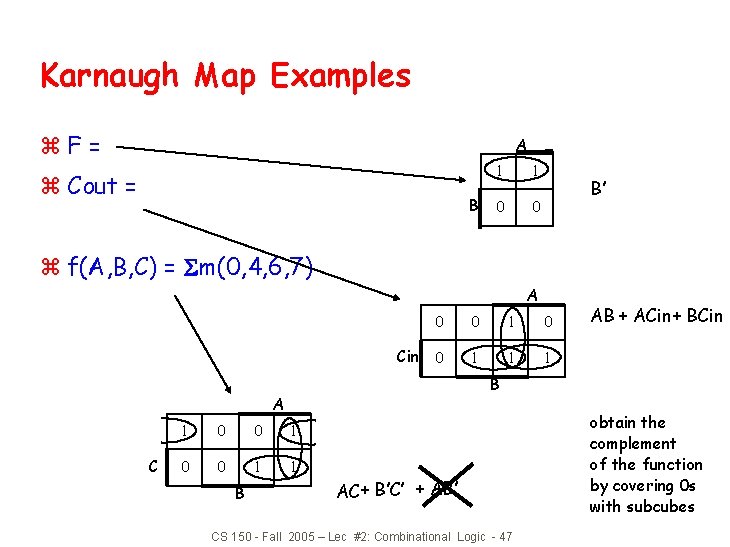

Karnaugh Map Examples z. F= A z Cout = B 1 1 0 0 B’ z f(A, B, C) = m(0, 4, 6, 7) A 0 0 1 0 Cin 0 1 1 1 B A C 1 0 0 1 1 B AB + ACin + BCin AC + B’C’ + AB’ CS 150 - Fall 2005 – Lec #2: Combinational Logic - 47 obtain the complement of the function by covering 0 s with subcubes

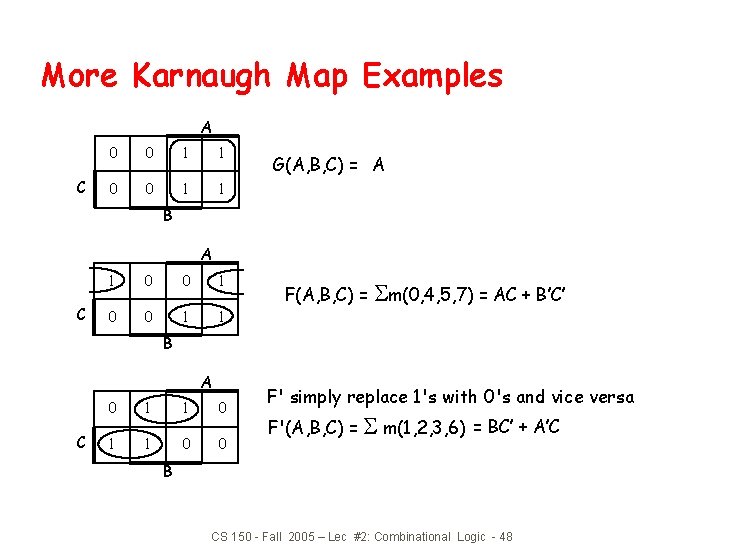

More Karnaugh Map Examples A C 0 0 1 1 G(A, B, C) = A B A C 1 0 0 1 1 F(A, B, C) = m(0, 4, 5, 7) = AC + B’C’ B A C 0 1 1 0 0 F' simply replace 1's with 0's and vice versa F'(A, B, C) = m(1, 2, 3, 6) = BC’ + A’C B CS 150 - Fall 2005 – Lec #2: Combinational Logic - 48

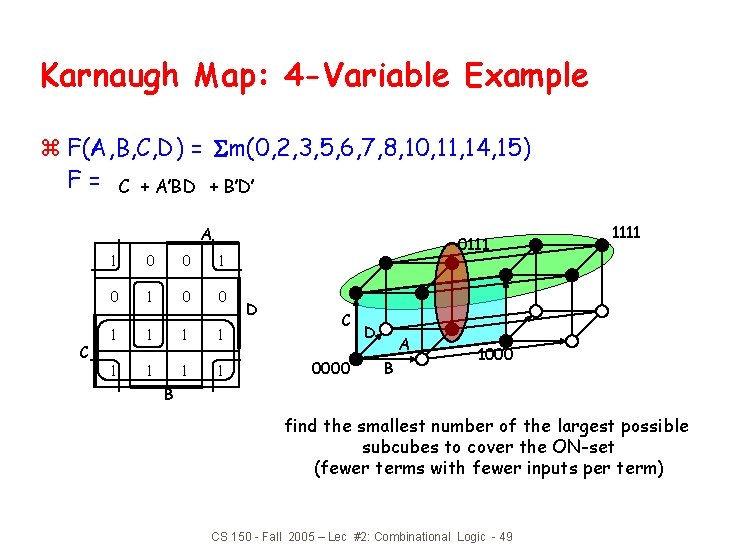

Karnaugh Map: 4 -Variable Example z F(A, B, C, D) = m(0, 2, 3, 5, 6, 7, 8, 10, 11, 14, 15) F = C + A’BD + B’D’ A C 1 0 0 1 1 1 1 0111 D C 0000 D A B 1111 1000 B find the smallest number of the largest possible subcubes to cover the ON-set (fewer terms with fewer inputs per term) CS 150 - Fall 2005 – Lec #2: Combinational Logic - 49

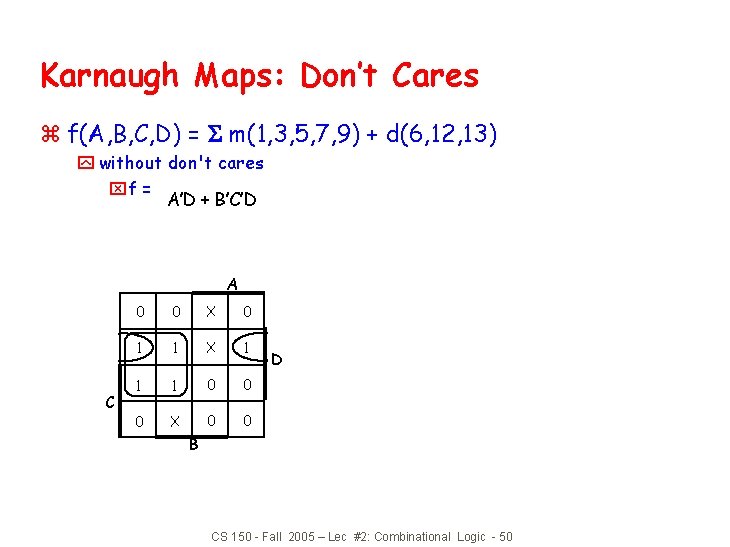

Karnaugh Maps: Don’t Cares z f(A, B, C, D) = m(1, 3, 5, 7, 9) + d(6, 12, 13) y without don't cares xf = A’D + B’C’D A C 0 0 X 0 1 1 X 1 1 1 0 0 0 X 0 0 D B CS 150 - Fall 2005 – Lec #2: Combinational Logic - 50

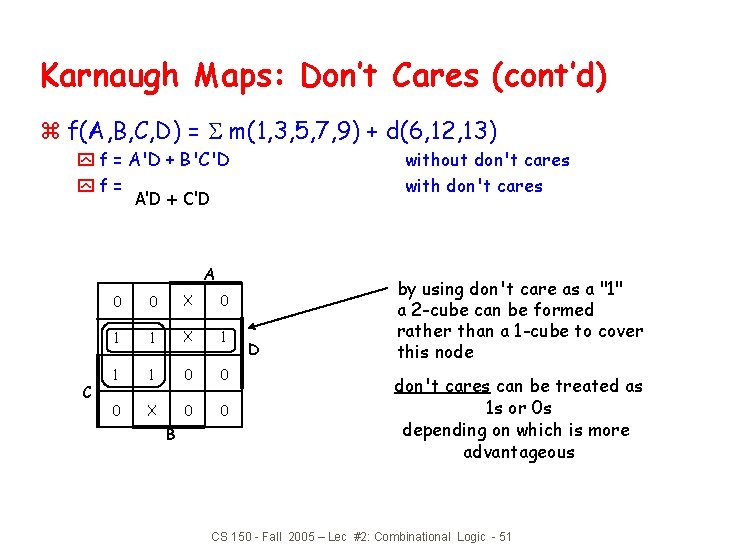

Karnaugh Maps: Don’t Cares (cont’d) z f(A, B, C, D) = m(1, 3, 5, 7, 9) + d(6, 12, 13) y f = A'D + B'C'D yf = A'D + C'D without don't cares with don't cares A C 0 0 X 0 1 1 X 1 1 1 0 0 0 X 0 0 B D by using don't care as a "1" a 2 -cube can be formed rather than a 1 -cube to cover this node don't cares can be treated as 1 s or 0 s depending on which is more advantageous CS 150 - Fall 2005 – Lec #2: Combinational Logic - 51

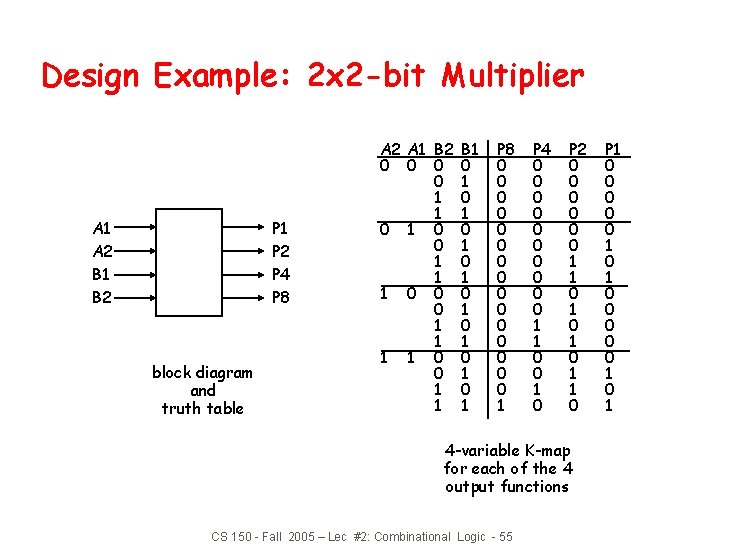

Design Example: 2 x 2 -bit Multiplier A 1 A 2 B 1 B 2 P 1 P 2 P 4 P 8 block diagram and truth table A 2 A 1 B 2 0 0 1 1 1 0 0 0 1 1 B 1 0 1 0 1 P 8 0 0 0 0 1 P 4 0 0 0 0 0 1 1 0 0 1 0 P 2 0 0 0 1 1 0 1 0 1 1 0 4 -variable K-map for each of the 4 output functions CS 150 - Fall 2005 – Lec #2: Combinational Logic - 55 P 1 0 0 0 0 0 1 0 1

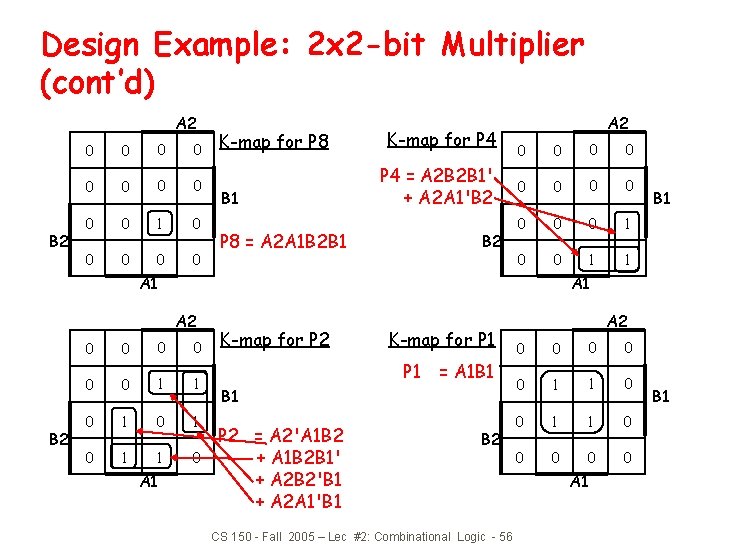

Design Example: 2 x 2 -bit Multiplier (cont’d) A 2 B 2 0 0 0 0 0 1 0 0 0 K-map for P 8 B 1 K-map for P 4 = A 2 B 2 B 1' + A 2 A 1'B 2 P 8 = A 2 A 1 B 2 B 1 B 2 A 2 0 0 0 1 0 0 1 1 A 1 A 2 B 2 0 0 0 1 1 0 1 0 1 1 0 A 1 B 1 K-map for P 2 K-map for P 1 = A 1 B 1 P 2 = A 2'A 1 B 2 + A 1 B 2 B 1' + A 2 B 2'B 1 + A 2 A 1'B 1 B 2 CS 150 - Fall 2005 – Lec #2: Combinational Logic - 56 A 2 0 0 0 1 1 0 0 0 A 1 B 1

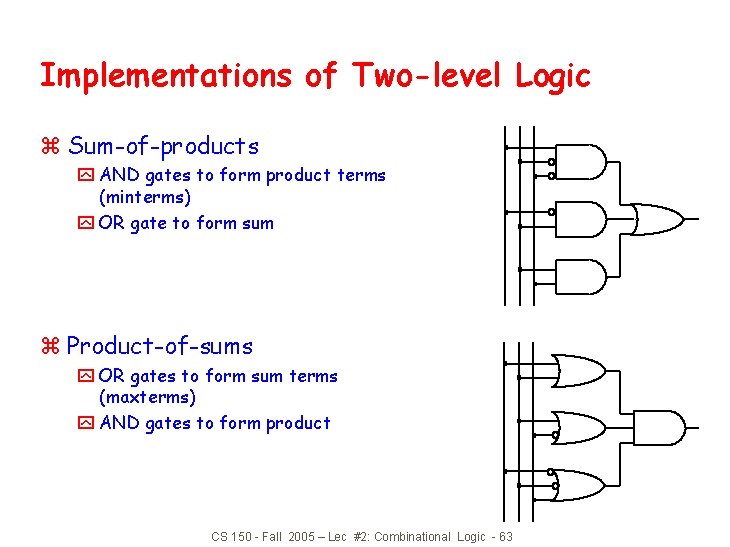

Implementations of Two-level Logic z Sum-of-products y AND gates to form product terms (minterms) y OR gate to form sum z Product-of-sums y OR gates to form sum terms (maxterms) y AND gates to form product CS 150 - Fall 2005 – Lec #2: Combinational Logic - 63

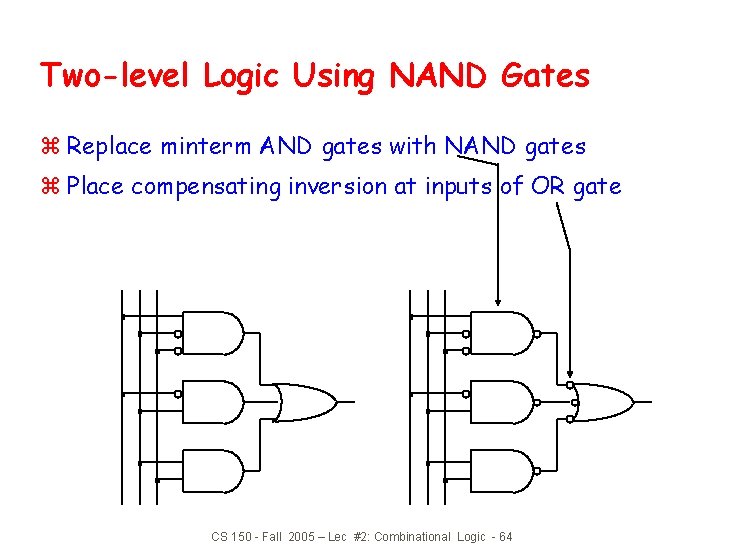

Two-level Logic Using NAND Gates z Replace minterm AND gates with NAND gates z Place compensating inversion at inputs of OR gate CS 150 - Fall 2005 – Lec #2: Combinational Logic - 64

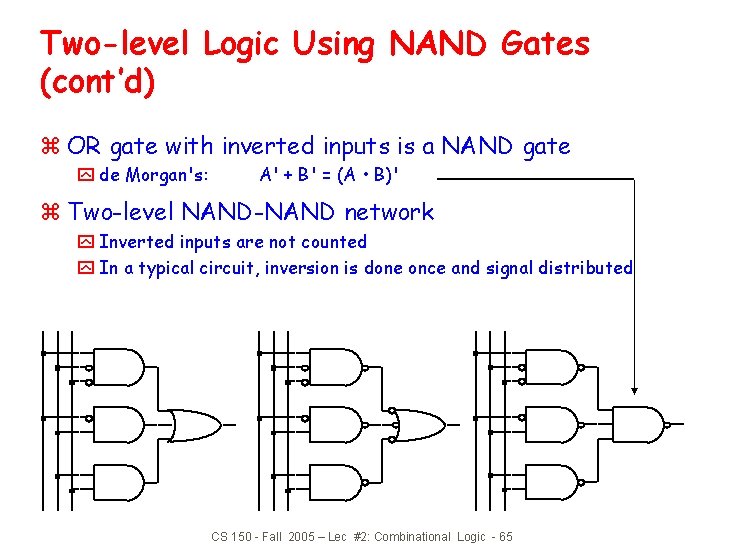

Two-level Logic Using NAND Gates (cont’d) z OR gate with inverted inputs is a NAND gate y de Morgan's: A' + B' = (A • B)' z Two-level NAND-NAND network y Inverted inputs are not counted y In a typical circuit, inversion is done once and signal distributed CS 150 - Fall 2005 – Lec #2: Combinational Logic - 65

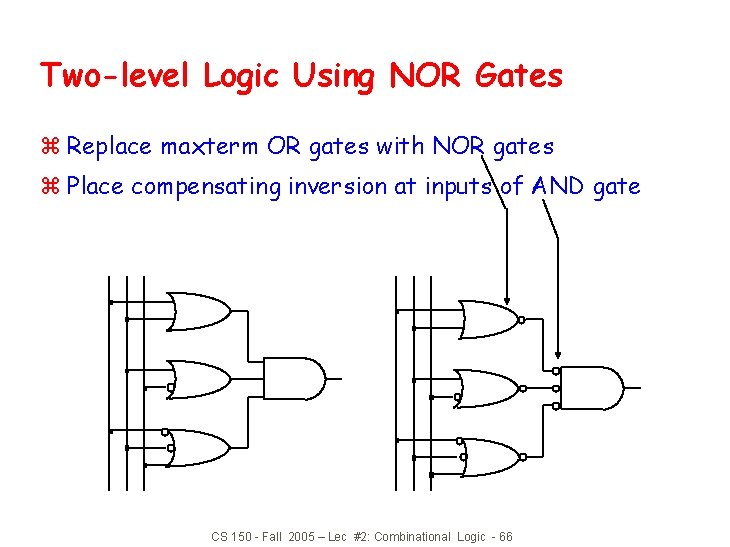

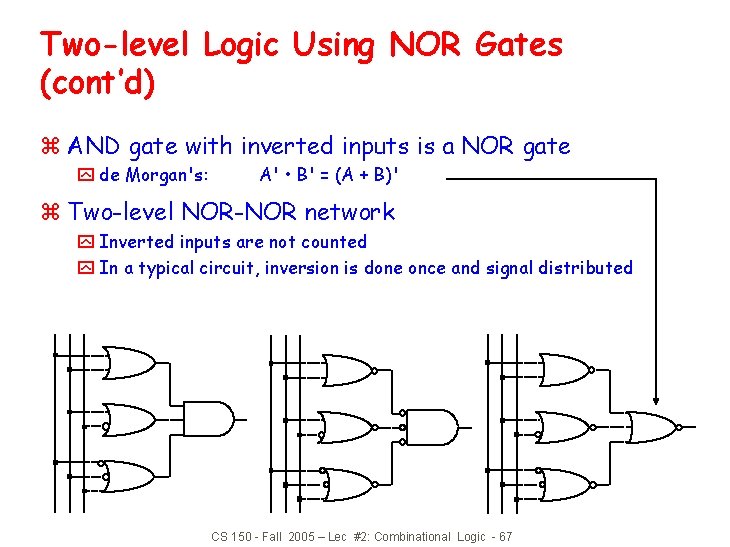

Two-level Logic Using NOR Gates z Replace maxterm OR gates with NOR gates z Place compensating inversion at inputs of AND gate CS 150 - Fall 2005 – Lec #2: Combinational Logic - 66

Two-level Logic Using NOR Gates (cont’d) z AND gate with inverted inputs is a NOR gate y de Morgan's: A' • B' = (A + B)' z Two-level NOR-NOR network y Inverted inputs are not counted y In a typical circuit, inversion is done once and signal distributed CS 150 - Fall 2005 – Lec #2: Combinational Logic - 67

Combinational Logic Summary z Logic functions, truth tables, and switches y NOT, AND, OR, NAND, NOR, XOR, . . . , minimal set z Axioms and theorems of Boolean algebra y Proofs by re-writing and perfect induction z Gate logic y Networks of Boolean functions and their time behavior z Canonical forms y Two-level and incompletely specified functions z Simplification y Two-level simplification CS 150 - Fall 2005 – Lec #2: Combinational Logic - 73

- Slides: 47