COMBINATIONAL LOGIC Digital Integrated Circuits Combinational Logic Prentice

COMBINATIONAL LOGIC Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

Overview Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

Combinational vs. Sequential Logic Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

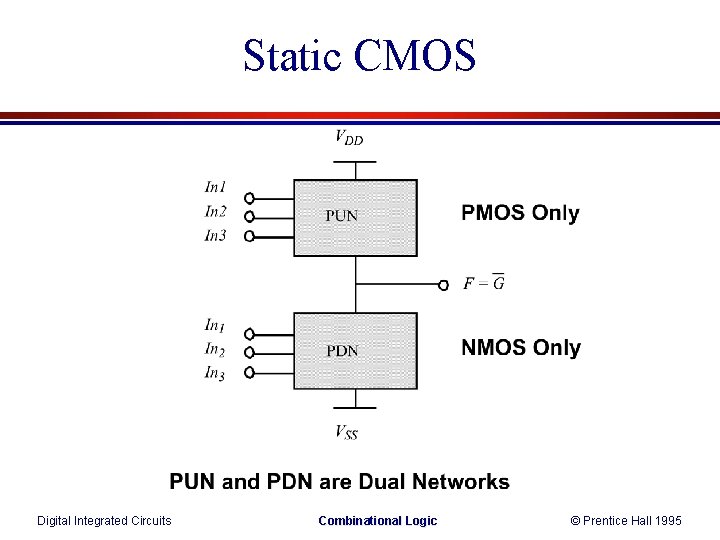

Static CMOS Circuit At every point in time (except during the switching transients) each gate output is connected to either VDD or Vss via a low-resistive path. The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods). This is in contrast to the dynamic circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes. Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

Static CMOS Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

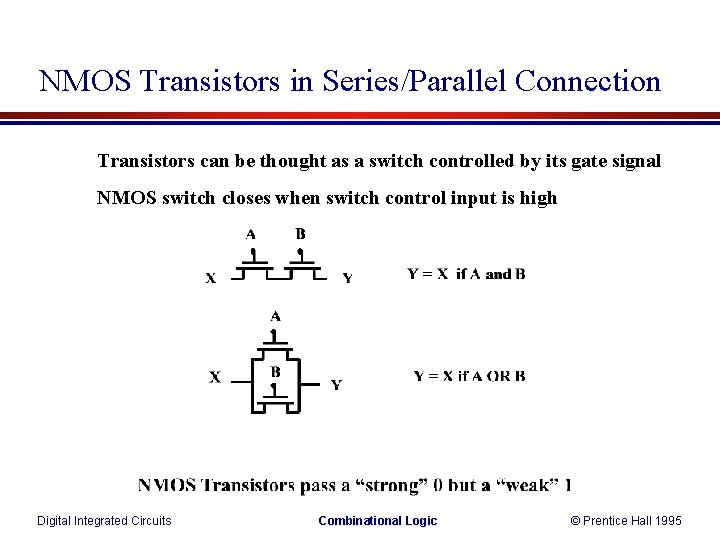

NMOS Transistors in Series/Parallel Connection Transistors can be thought as a switch controlled by its gate signal NMOS switch closes when switch control input is high Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

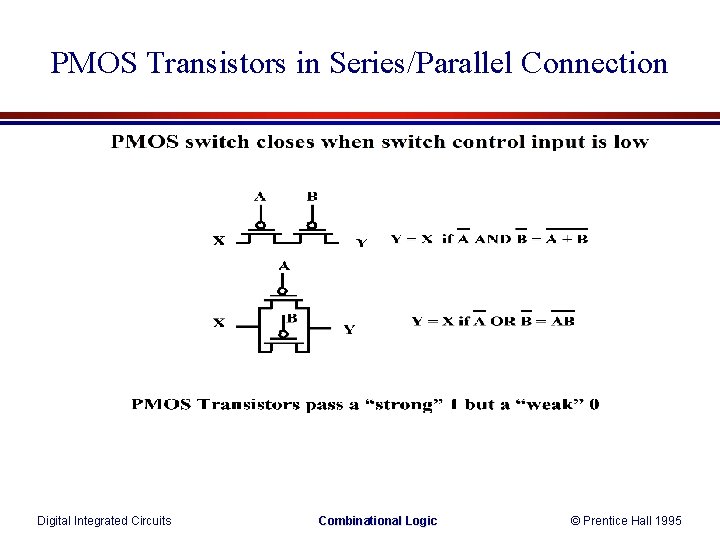

PMOS Transistors in Series/Parallel Connection Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

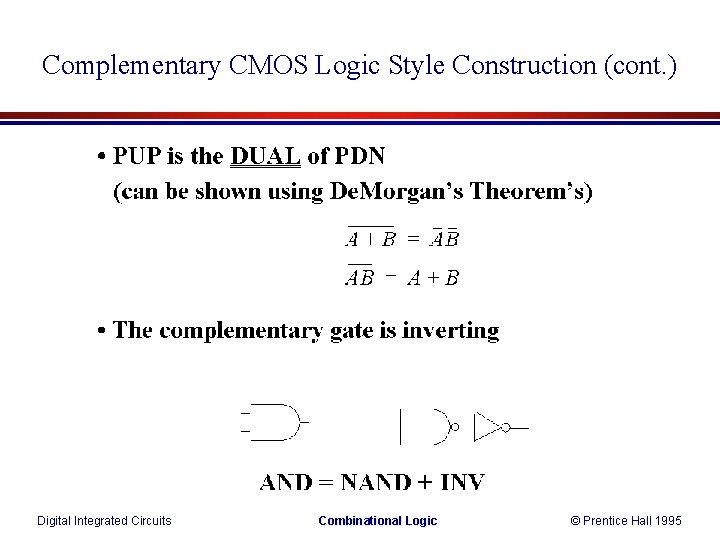

Complementary CMOS Logic Style Construction (cont. ) Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

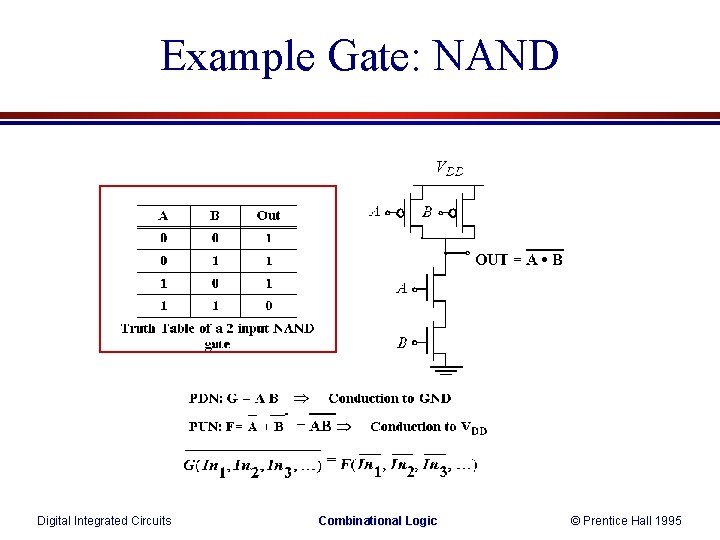

Example Gate: NAND Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

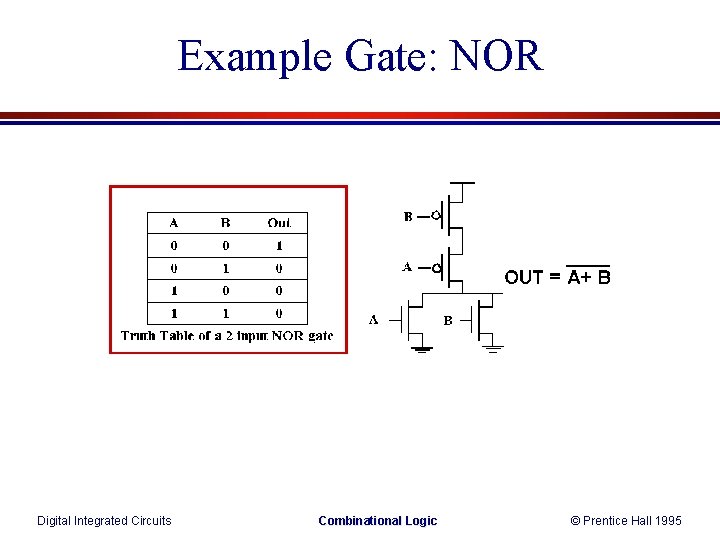

Example Gate: NOR Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

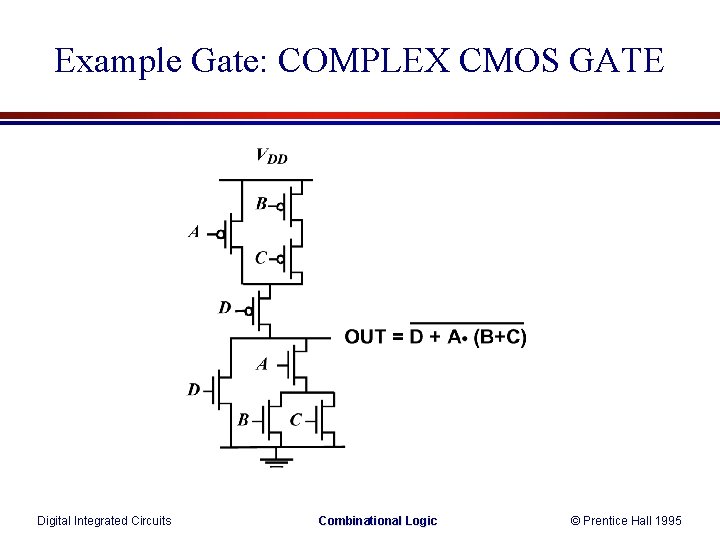

Example Gate: COMPLEX CMOS GATE Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

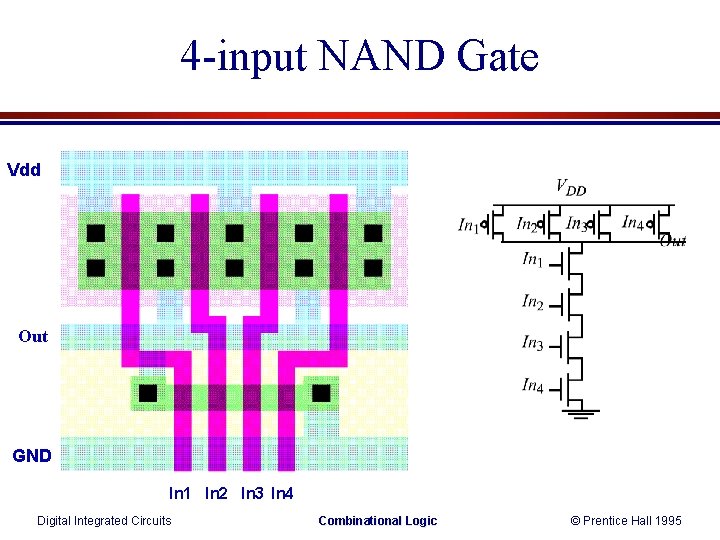

4 -input NAND Gate Vdd Out GND In 1 In 2 In 3 In 4 Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

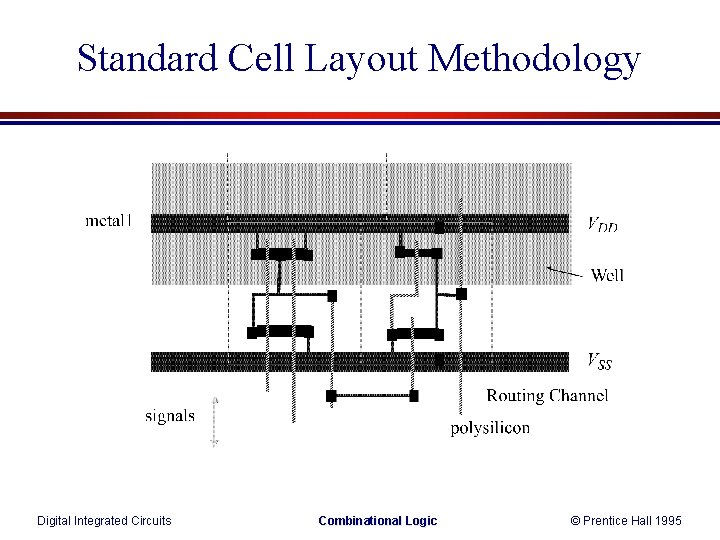

Standard Cell Layout Methodology Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

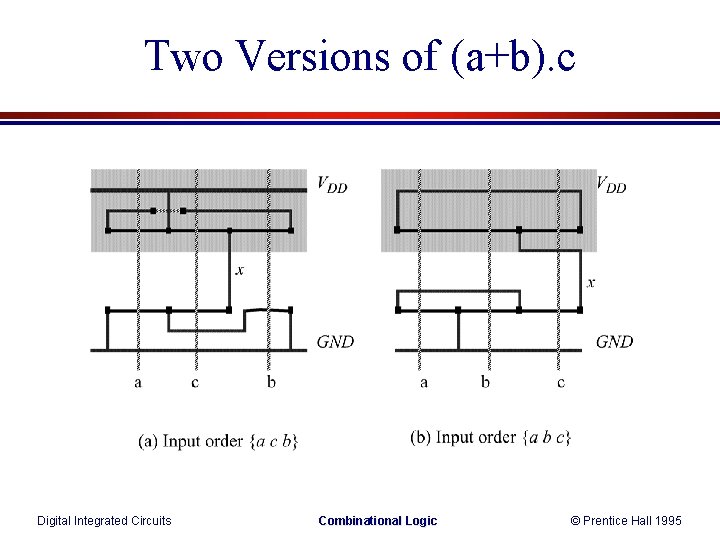

Two Versions of (a+b). c Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

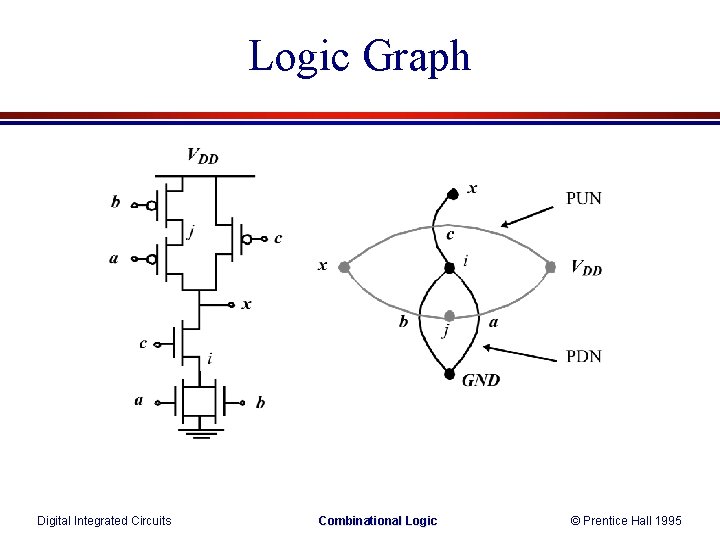

Logic Graph Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

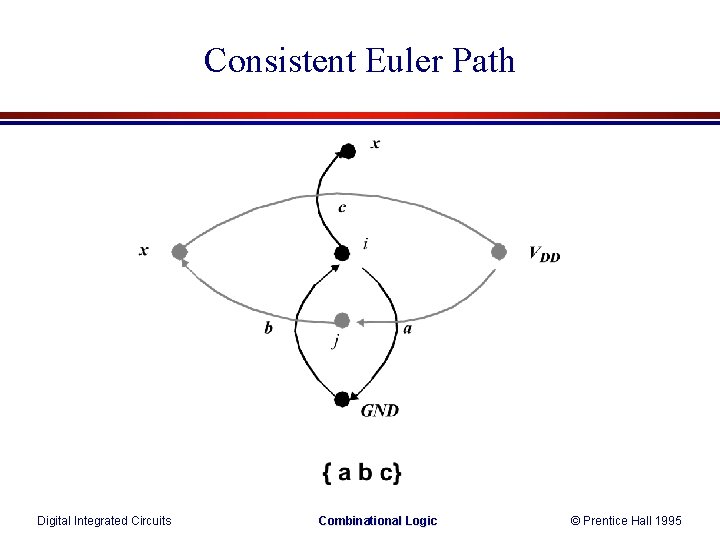

Consistent Euler Path Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

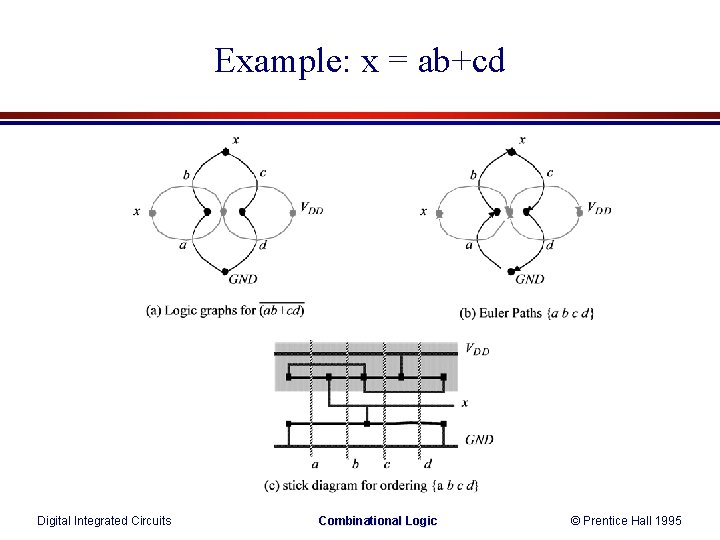

Example: x = ab+cd Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

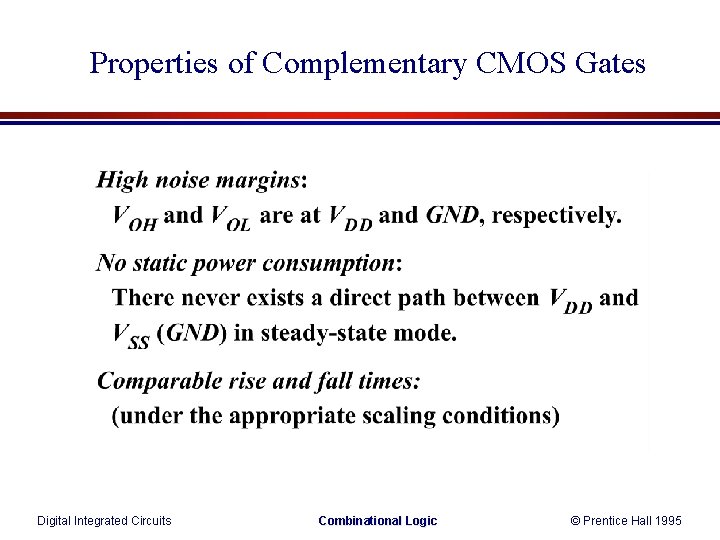

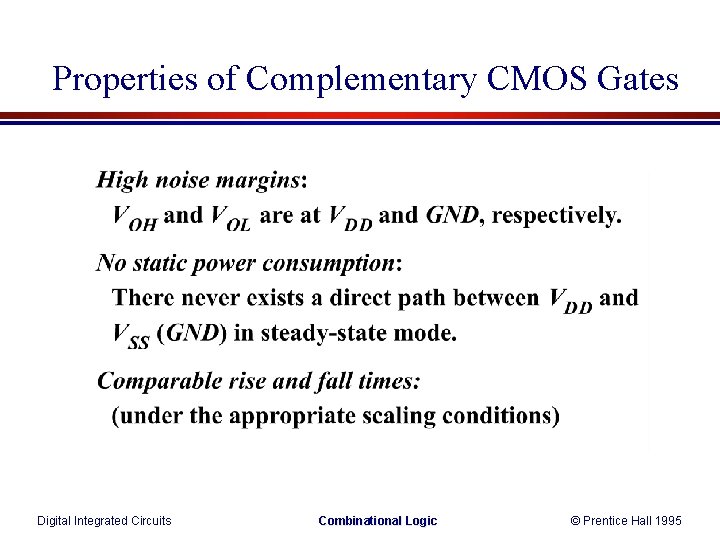

Properties of Complementary CMOS Gates Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

Properties of Complementary CMOS Gates Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

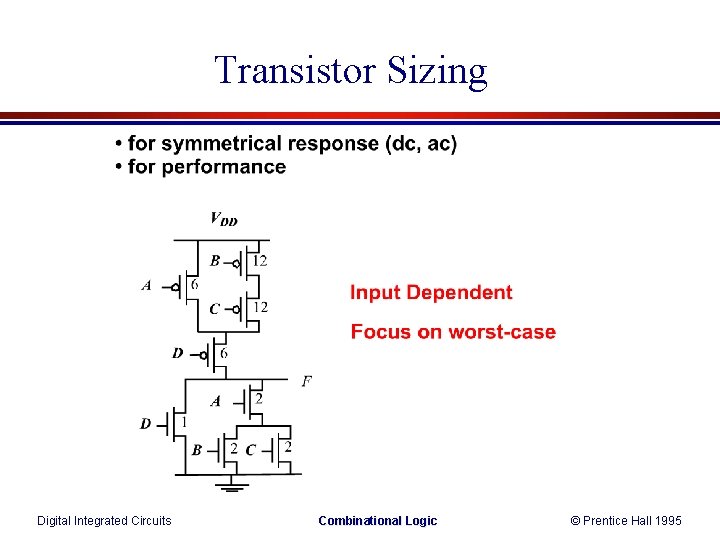

Transistor Sizing Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

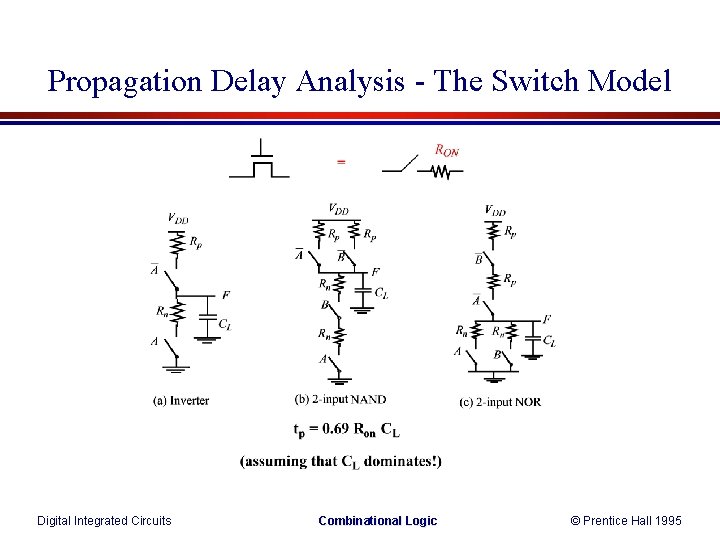

Propagation Delay Analysis - The Switch Model Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

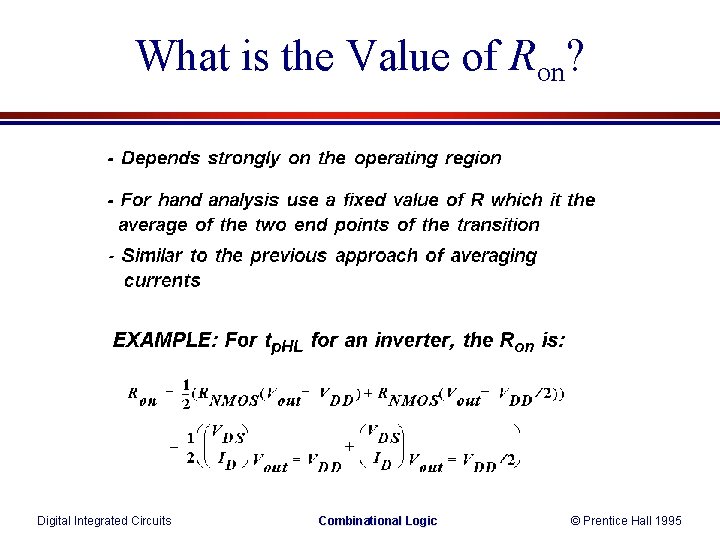

What is the Value of Ron? Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

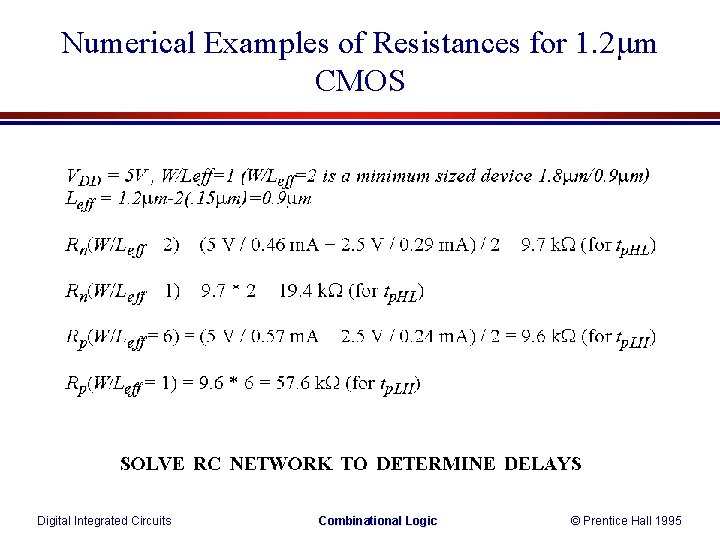

Numerical Examples of Resistances for 1. 2 mm CMOS Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

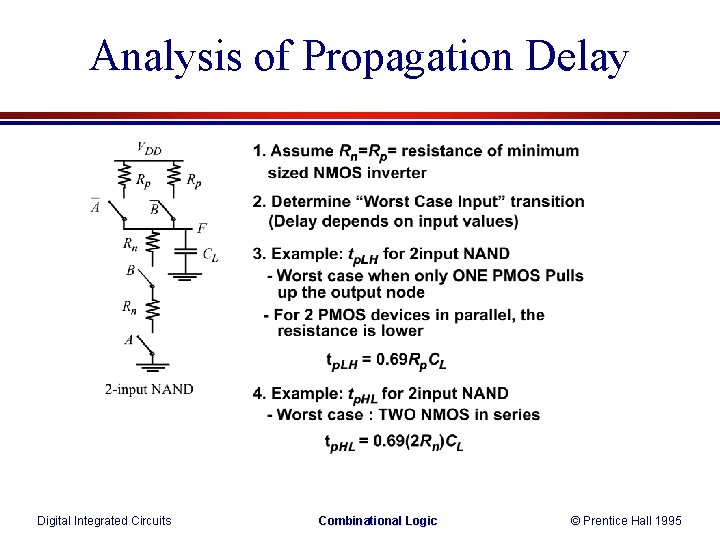

Analysis of Propagation Delay Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

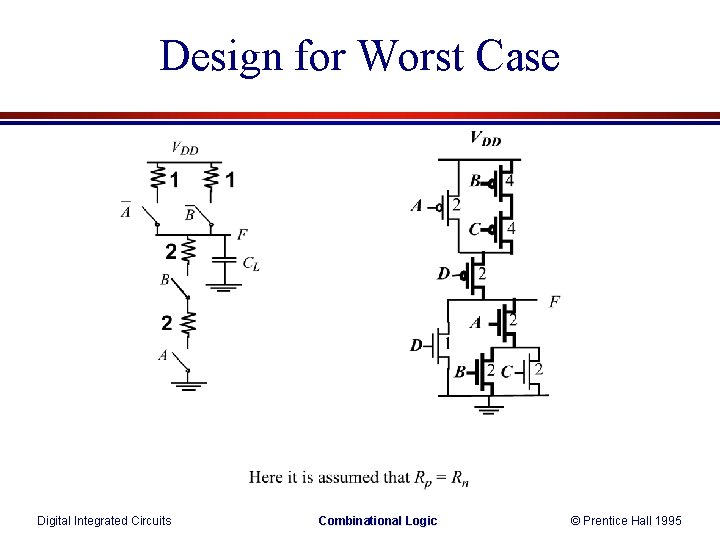

Design for Worst Case Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

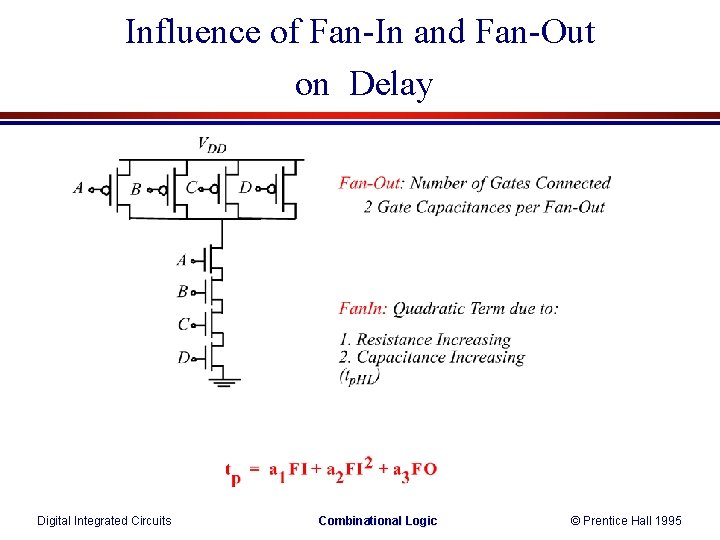

Influence of Fan-In and Fan-Out on Delay Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

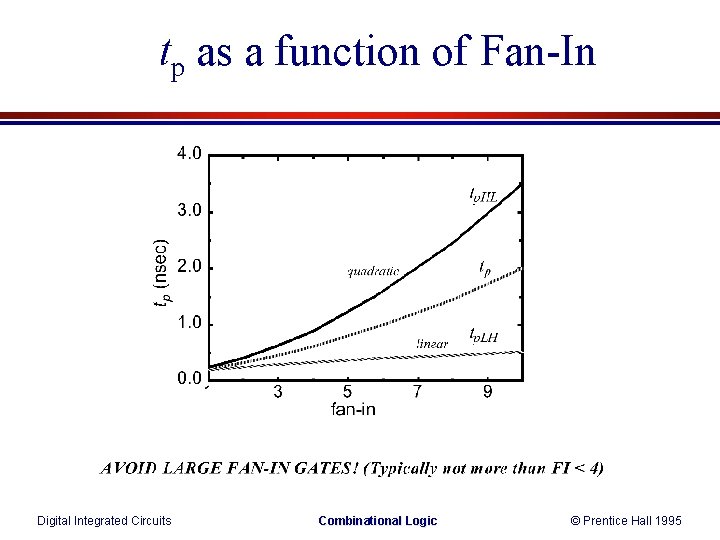

tp as a function of Fan-In Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

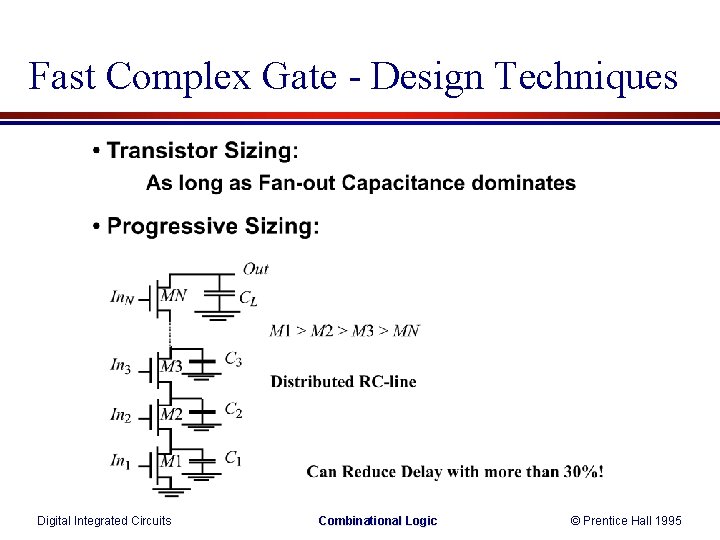

Fast Complex Gate - Design Techniques Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

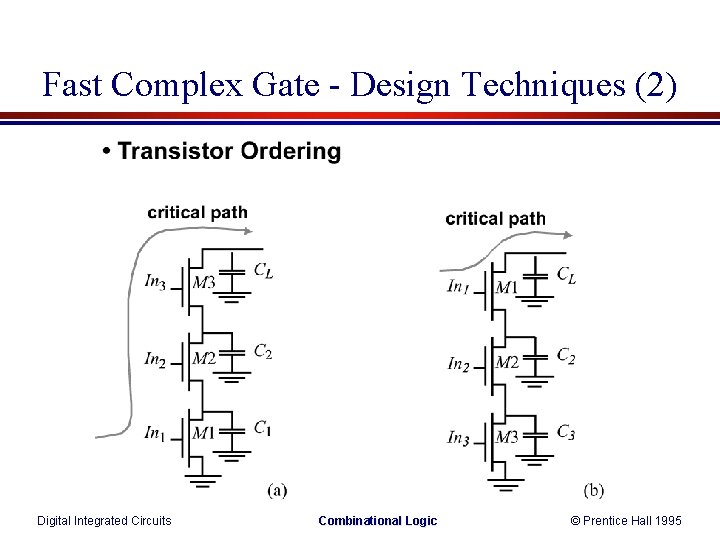

Fast Complex Gate - Design Techniques (2) Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

Fast Complex Gate - Design Techniques (3) Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

Fast Complex Gate - Design Techniques (4) Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

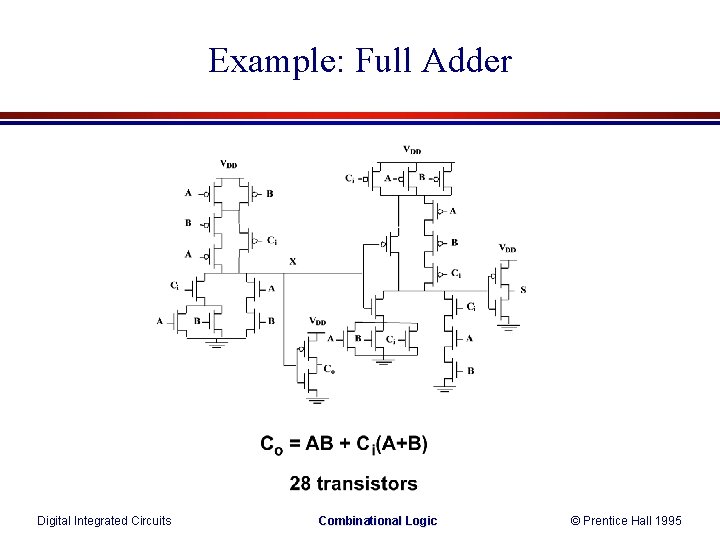

Example: Full Adder Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

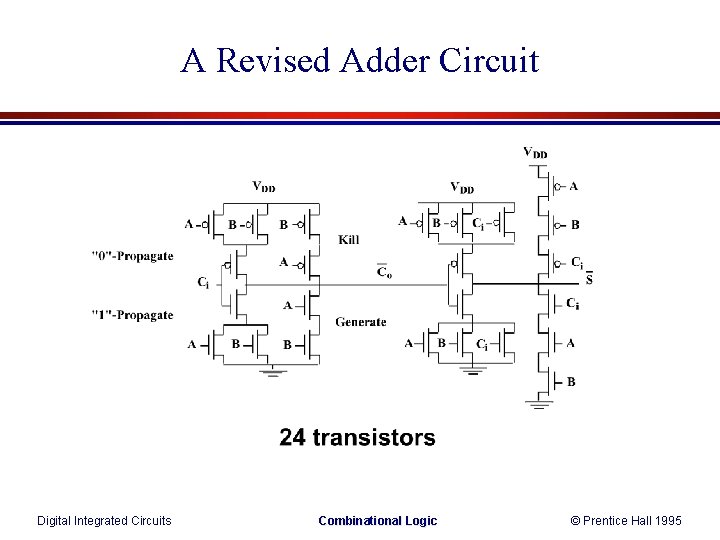

A Revised Adder Circuit Digital Integrated Circuits Combinational Logic © Prentice Hall 1995

- Slides: 33