Combinational Logic Design with VHDL Introduction The combinational

Combinational Logic Design with VHDL

Introduction The combinational logic is probably the easiest to design, since each time the outputs of a combinational circuit depend only on the current state of its inputs ( the circuit has no memory). A system combinational can have multiple outputs. every output must be represented by a logical different function. This time we will see combinational circuits commonly used in the logic design using hardware description language VHDL be modeled.

Signals and Variables Are declared as constants and variables. The difference is that they can be normal, register and bus. If nothing is specified in the declaration means that the compiler is the standard rate. One can say that the signal has two parts one where you write and another which reads. Signals can be declared only architectures packages (package ) or in concurrent blocks ( BLOCK). Used in concurrent executions. Signals It is similar to the concept of variable in other languages. Its value can be changed at any time and can be assigned an initial value. The only variables are declared in processes or subprograms. Used in serial executions.

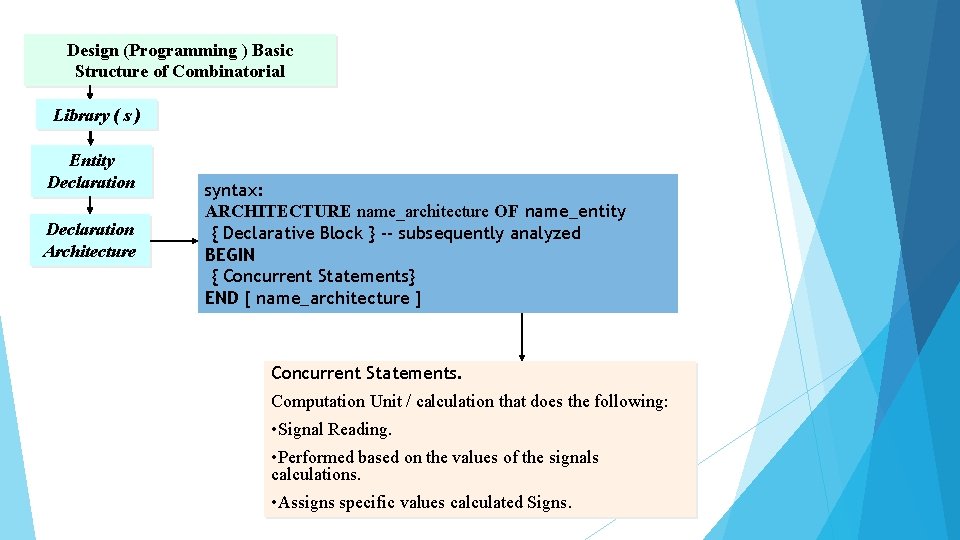

Design (Programming ) Basic Structure of Combinatorial Library ( s ) Entity Declaration Architecture syntax: ARCHITECTURE name_architecture OF name_entity { Declarative Block } -- subsequently analyzed BEGIN { Concurrent Statements} END [ name_architecture ] Concurrent Statements. Computation Unit / calculation that does the following: • Signal Reading. • Performed based on the values of the signals calculations. • Assigns specific values calculated Signs.

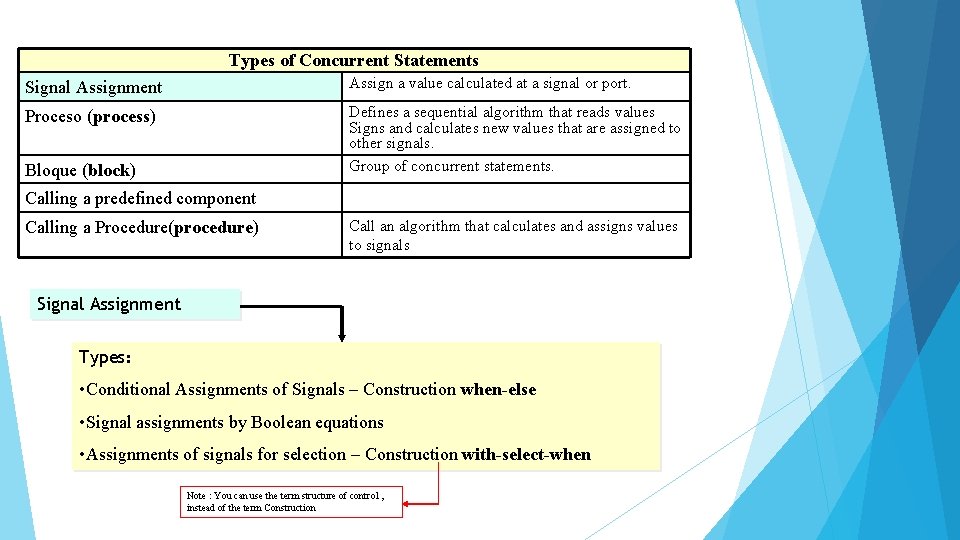

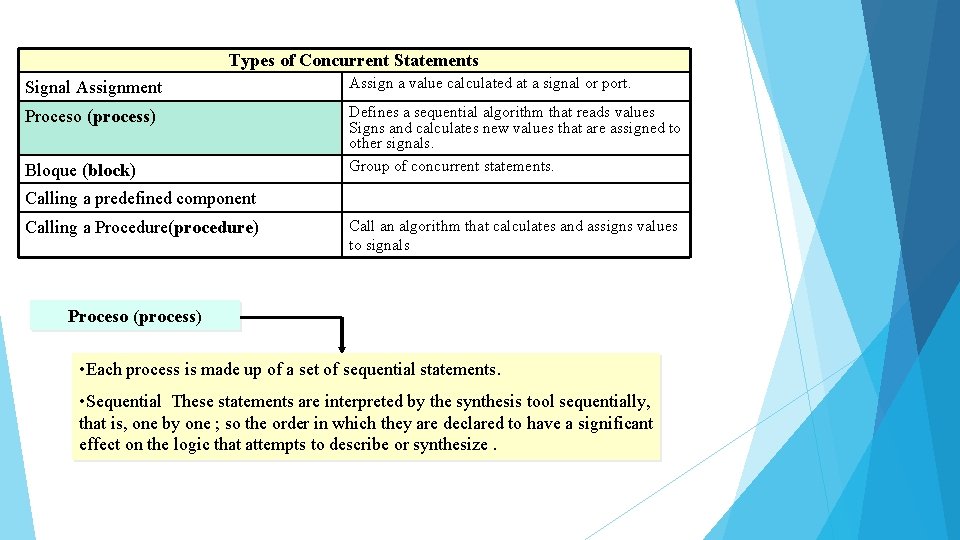

Types of Concurrent Statements Signal Assignment Assign a value calculated at a signal or port. Proceso (process) Defines a sequential algorithm that reads values Signs and calculates new values that are assigned to other signals. Group of concurrent statements. Bloque (block) Calling a predefined component Calling a Procedure(procedure) Call an algorithm that calculates and assigns values to signals Signal Assignment Types: • Conditional Assignments of Signals – Construction when-else • Signal assignments by Boolean equations • Assignments of signals for selection – Construction with-select-when Note : You can use the term structure of control , instead of the term Construction

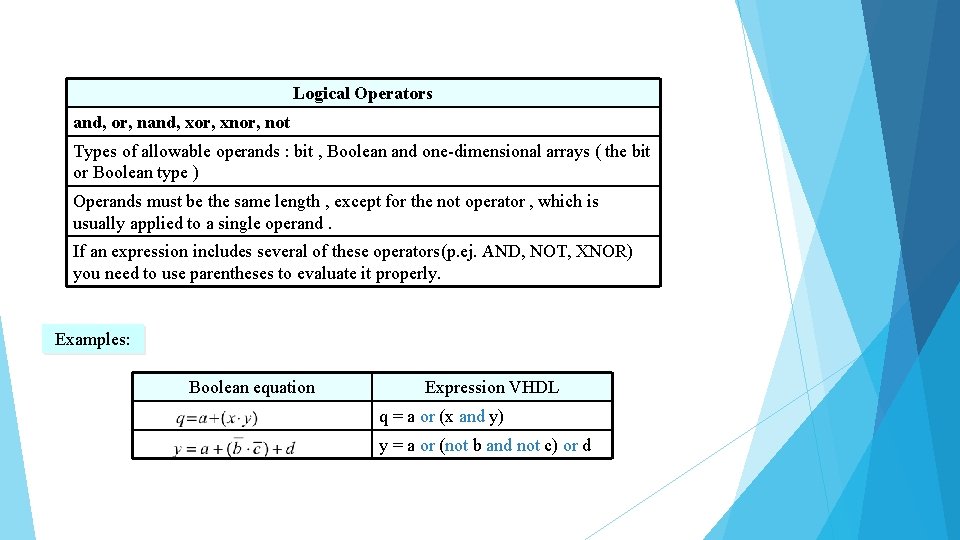

Logical Operators and, or, nand, xor, xnor, not Types of allowable operands : bit , Boolean and one-dimensional arrays ( the bit or Boolean type ) Operands must be the same length , except for the not operator , which is usually applied to a single operand. If an expression includes several of these operators(p. ej. AND, NOT, XNOR) you need to use parentheses to evaluate it properly. Examples: Boolean equation Expression VHDL q = a or (x and y) y = a or (not b and not c) or d

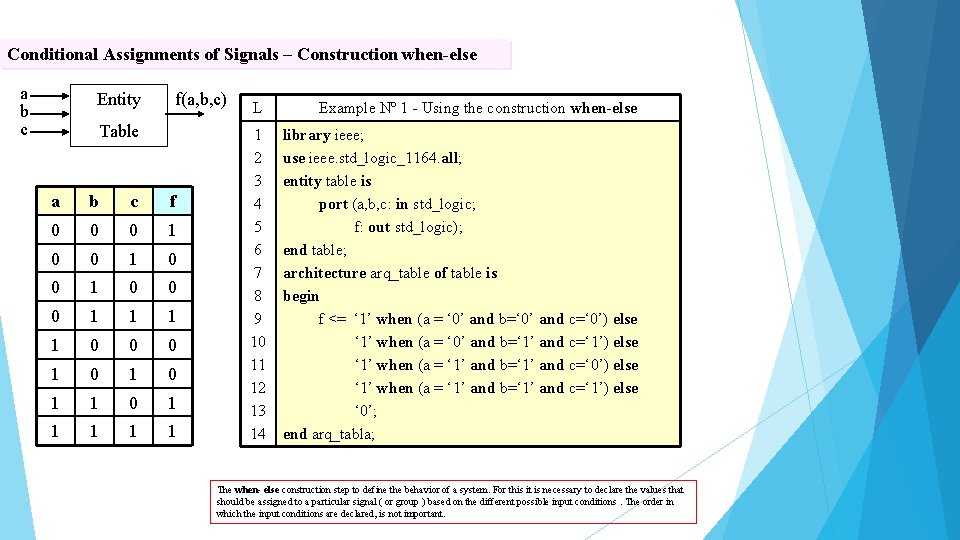

Conditional Assignments of Signals – Construction when-else a b c Entity f(a, b, c) Table a b c f 0 0 0 1 0 0 0 1 1 0 0 0 1 0 1 1 1 1 1 L Example Nº 1 - Using the construction when-else 1 2 3 4 5 6 7 8 9 10 11 12 13 14 library ieee; use ieee. std_logic_1164. all; entity table is port (a, b, c: in std_logic; f: out std_logic); end table; architecture arq_table of table is begin f <= ‘ 1’ when (a = ‘ 0’ and b=‘ 0’ and c=‘ 0’) else ‘ 1’ when (a = ‘ 0’ and b=‘ 1’ and c=‘ 1’) else ‘ 1’ when (a = ‘ 1’ and b=‘ 1’ and c=‘ 0’) else ‘ 1’ when (a = ‘ 1’ and b=‘ 1’ and c=‘ 1’) else ‘ 0’; end arq_tabla; The when- else construction step to define the behavior of a system. For this it is necessary to declare the values that should be assigned to a particular signal ( or group ) based on the different possible input conditions. The order in which the input conditions are declared, is not important.

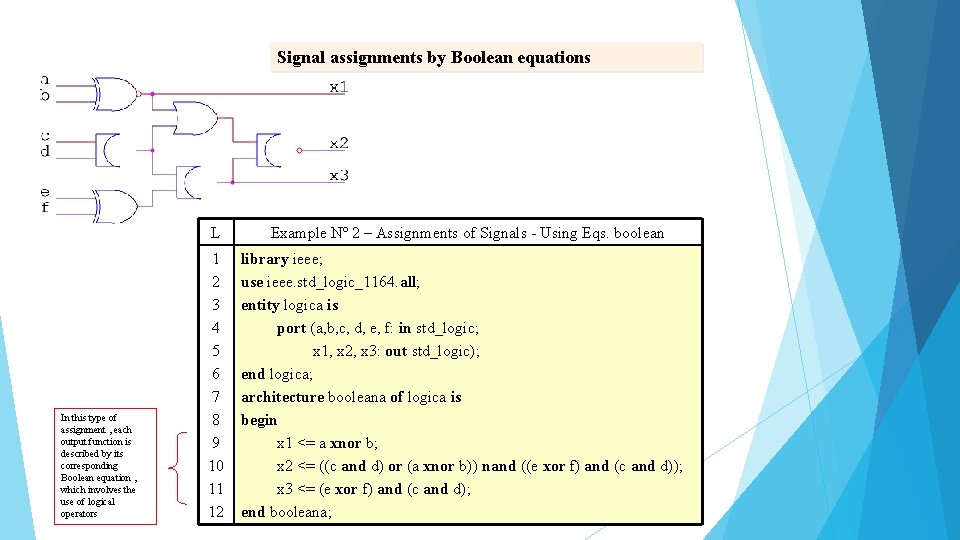

Signal assignments by Boolean equations L In this type of assignment , each output function is described by its corresponding Boolean equation , which involves the use of logical operators 1 2 3 4 5 6 7 8 9 10 11 12 Example Nº 2 – Assignments of Signals - Using Eqs. boolean library ieee; use ieee. std_logic_1164. all; entity logica is port (a, b, c, d, e, f: in std_logic; x 1, x 2, x 3: out std_logic); end logica; architecture booleana of logica is begin x 1 <= a xnor b; x 2 <= ((c and d) or (a xnor b)) nand ((e xor f) and (c and d)); x 3 <= (e xor f) and (c and d); end booleana;

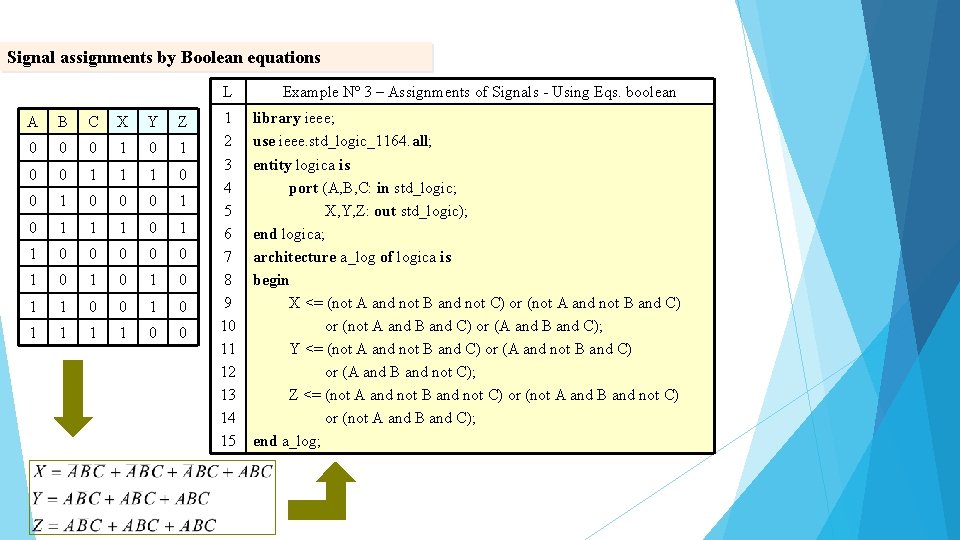

Signal assignments by Boolean equations A B C X Y Z 0 0 0 1 1 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 L Example Nº 3 – Assignments of Signals - Using Eqs. boolean 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 library ieee; use ieee. std_logic_1164. all; entity logica is port (A, B, C: in std_logic; X, Y, Z: out std_logic); end logica; architecture a_log of logica is begin X <= (not A and not B and not C) or (not A and not B and C) or (not A and B and C) or (A and B and C); Y <= (not A and not B and C) or (A and B and not C); Z <= (not A and not B and not C) or (not A and B and C); end a_log;

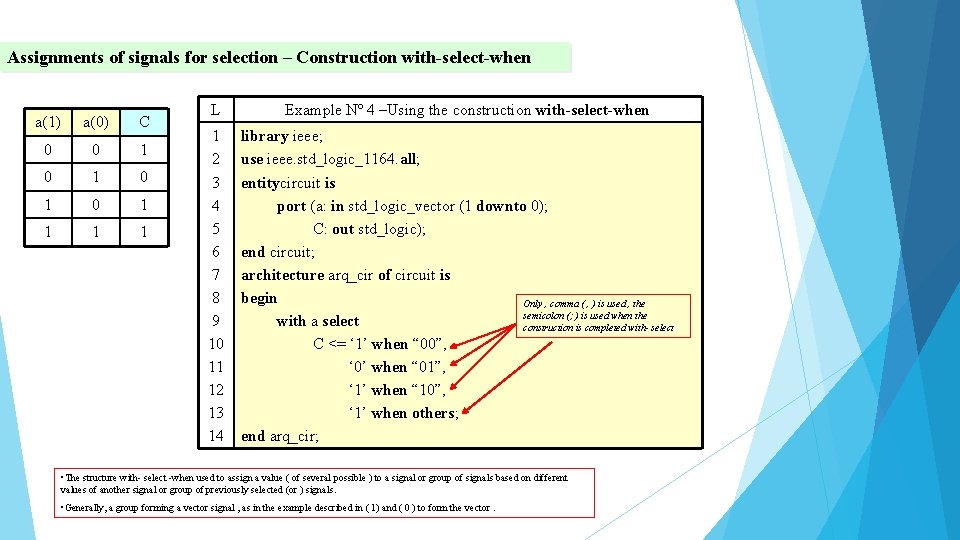

Assignments of signals for selection – Construction with-select-when a(1) a(0) C 0 0 1 0 1 1 1 1 L 1 2 3 4 5 6 7 8 9 10 11 12 13 14 Example Nº 4 –Using the construction with-select-when library ieee; use ieee. std_logic_1164. all; entitycircuit is port (a: in std_logic_vector (1 downto 0); C: out std_logic); end circuit; architecture arq_cir of circuit is begin Only , comma ( , ) is used , the semicolon (; ) is used when the with a select construction is completed with- select C <= ‘ 1’ when “ 00”, ‘ 0’ when “ 01”, ‘ 1’ when “ 10”, ‘ 1’ when others; end arq_cir; • The structure with- select -when used to assign a value ( of several possible ) to a signal or group of signals based on different values of another signal or group of previously selected (or ) signals. • Generally, a group forming a vector signal , as in the example described in ( 1) and ( 0 ) to form the vector.

Types of Concurrent Statements Signal Assignment Assign a value calculated at a signal or port. Proceso (process) Defines a sequential algorithm that reads values Signs and calculates new values that are assigned to other signals. Group of concurrent statements. Bloque (block) Calling a predefined component Calling a Procedure(procedure) Call an algorithm that calculates and assigns values to signals Proceso (process) • Each process is made up of a set of sequential statements. • Sequential These statements are interpreted by the synthesis tool sequentially, that is, one by one ; so the order in which they are declared to have a significant effect on the logic that attempts to describe or synthesize.

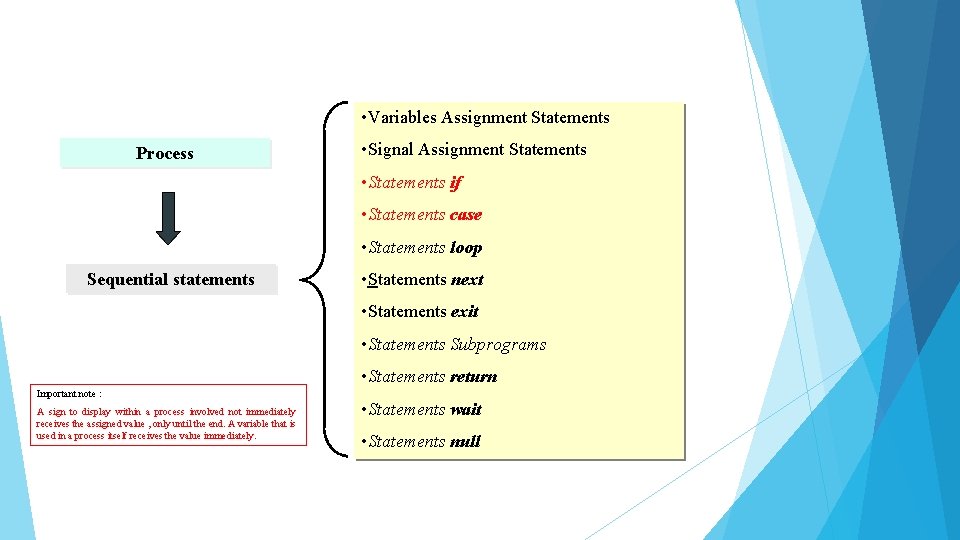

• Variables Assignment Statements Process • Signal Assignment Statements • Statements if • Statements case • Statements loop Sequential statements • Statements next • Statements exit • Statements Subprograms • Statements return Important note : A sign to display within a process involved not immediately receives the assigned value , only until the end. A variable that is used in a process itself receives the value immediately. • Statements wait • Statements null

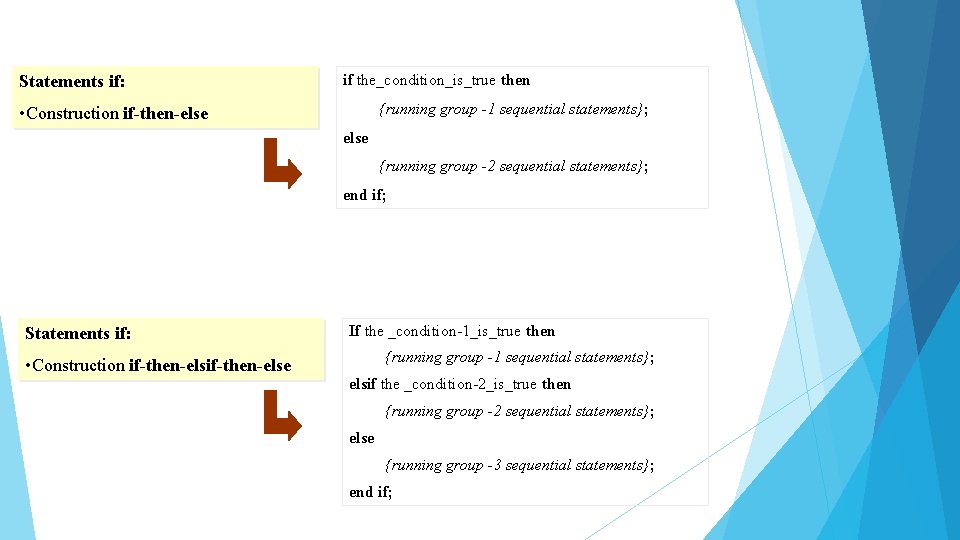

Statements if: if the_condition_is_true then {running group -1 sequential statements}; • Construction if-then-else {running group -2 sequential statements}; end if; Statements if: • Construction if-then-else If the _condition-1_is_true then {running group -1 sequential statements}; elsif the _condition-2_is_true then {running group -2 sequential statements}; else {running group -3 sequential statements}; end if;

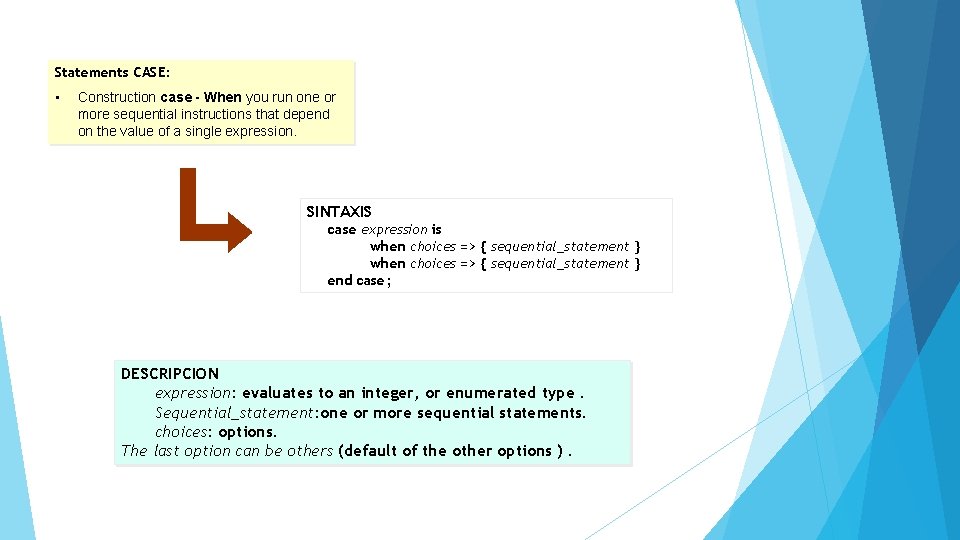

Statements CASE: • Construction case - When you run one or more sequential instructions that depend on the value of a single expression. SINTAXIS case expression is when choices => { sequential_statement } end case; DESCRIPCION expression: evaluates to an integer, or enumerated type. Sequential_statement: one or more sequential statements. choices: options. The last option can be others (default of the other options ).

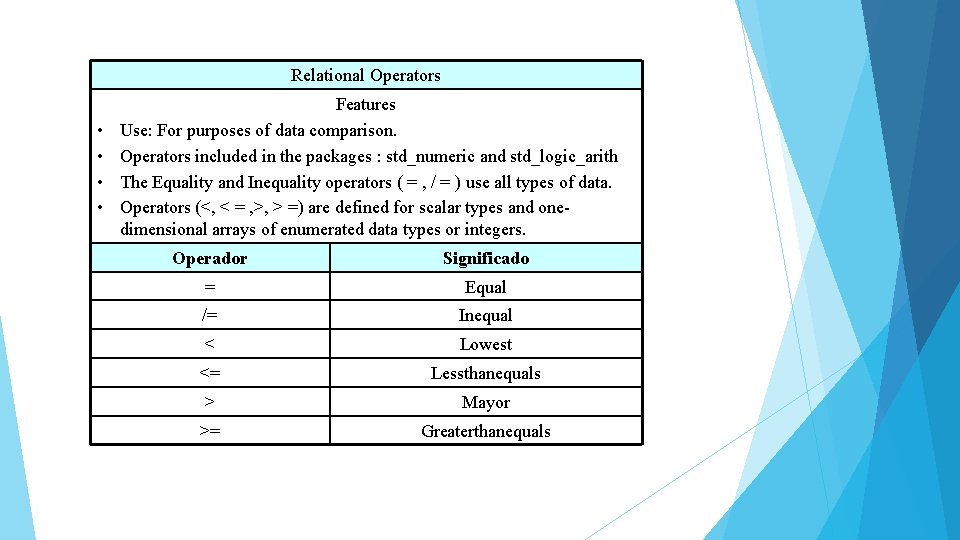

Relational Operators • • Features Use: For purposes of data comparison. Operators included in the packages : std_numeric and std_logic_arith The Equality and Inequality operators ( = , / = ) use all types of data. Operators (<, < = , >, > =) are defined for scalar types and onedimensional arrays of enumerated data types or integers. Operador Significado = Equal /= Inequal < Lowest <= Lessthanequals > Mayor >= Greaterthanequals

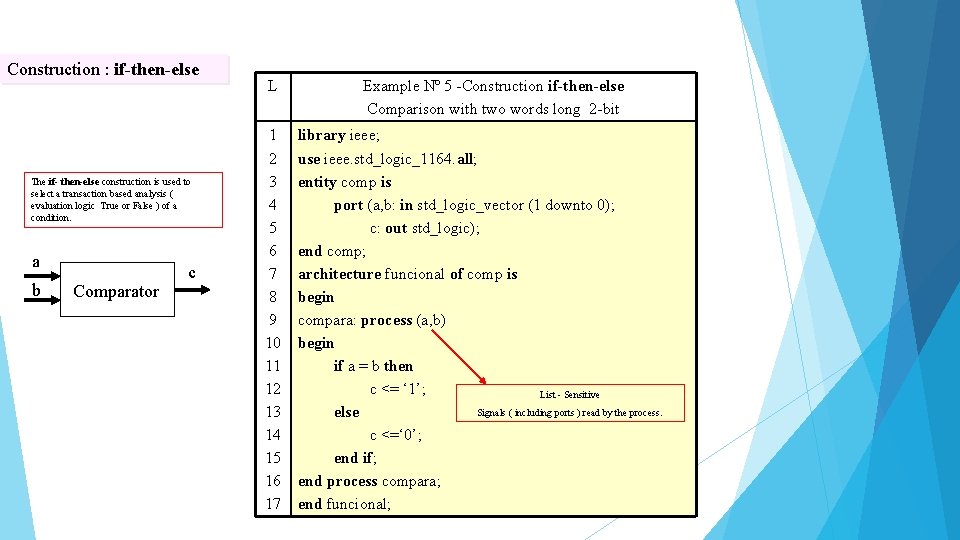

Construction : if-then-else The if- then-else construction is used to select a transaction based analysis ( evaluation logic True or False ) of a condition. a b Comparator c L 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 Example Nº 5 -Construction if-then-else Comparison with two words long 2 -bit library ieee; use ieee. std_logic_1164. all; entity comp is port (a, b: in std_logic_vector (1 downto 0); c: out std_logic); end comp; architecture funcional of comp is begin compara: process (a, b) begin if a = b then c <= ‘ 1’; List - Sensitive Signals ( including ports ) read by the process. else c <=‘ 0’; end if; end process compara; end funcional;

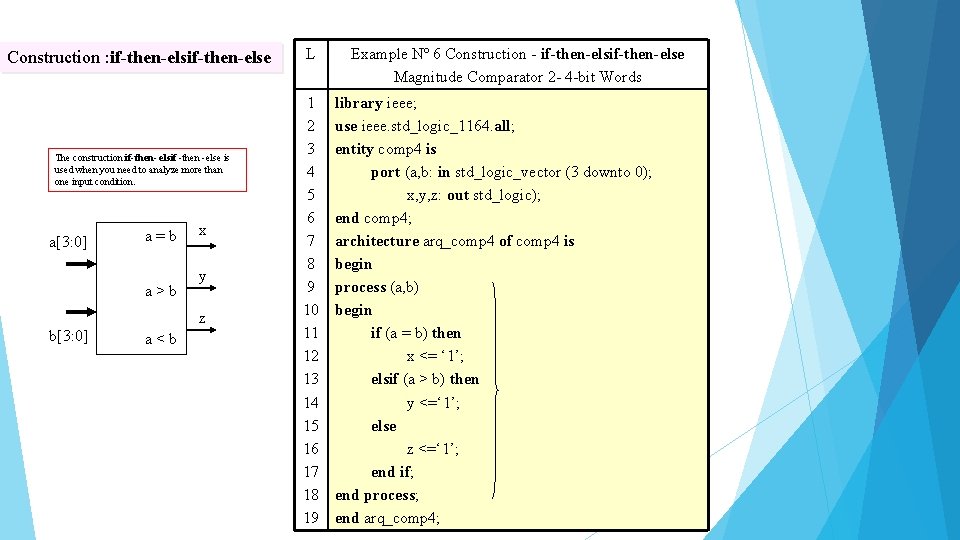

Construction : if-then-else The construction if-then- elsif -then -else is used when you need to analyze more than one input condition. a[3: 0] a=b a>b x y z b[3: 0] a<b L 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 Example Nº 6 Construction - if-then-else Magnitude Comparator 2 - 4 -bit Words library ieee; use ieee. std_logic_1164. all; entity comp 4 is port (a, b: in std_logic_vector (3 downto 0); x, y, z: out std_logic); end comp 4; architecture arq_comp 4 of comp 4 is begin process (a, b) begin if (a = b) then x <= ‘ 1’; elsif (a > b) then y <=‘ 1’; else z <=‘ 1’; end if; end process; end arq_comp 4;

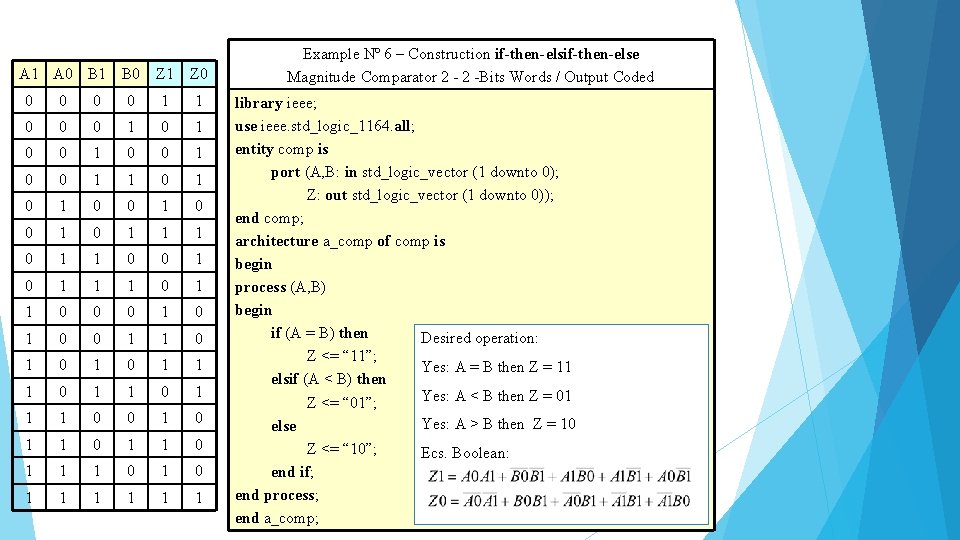

A 1 A 0 B 1 B 0 Z 1 Z 0 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 1 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 0 1 1 1 Example Nº 6 – Construction if-then-else Magnitude Comparator 2 -Bits Words / Output Coded library ieee; use ieee. std_logic_1164. all; entity comp is port (A, B: in std_logic_vector (1 downto 0); Z: out std_logic_vector (1 downto 0)); end comp; architecture a_comp of comp is begin process (A, B) begin if (A = B) then Desired operation: Z <= “ 11”; Yes: A = B then Z = 11 elsif (A < B) then Yes: A < B then Z = 01 Z <= “ 01”; Yes: A > B then Z = 10 else Z <= “ 10”; end if; end process; end a_comp; Ecs. Boolean:

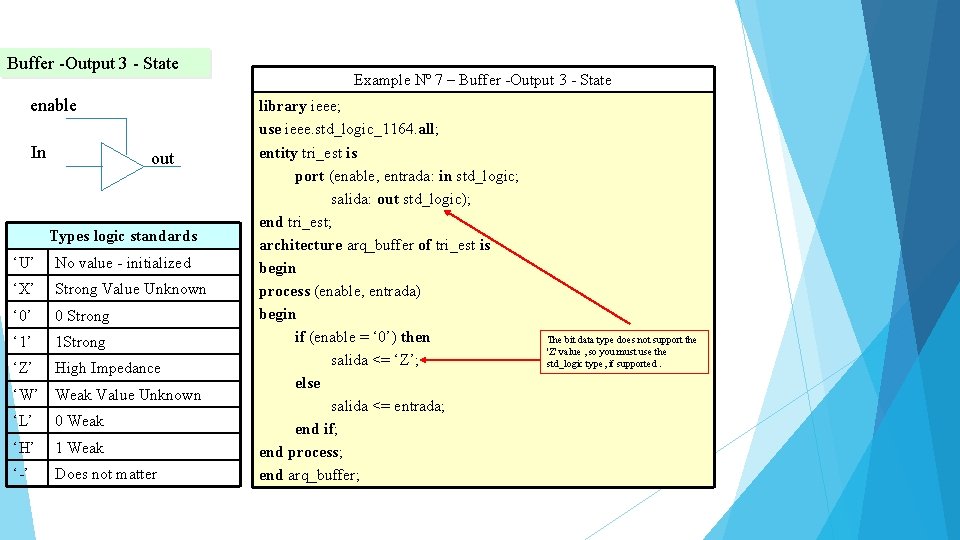

Buffer -Output 3 - State enable In out Types logic standards ‘U’ No value - initialized ‘X’ Strong Value Unknown ‘ 0’ 0 Strong ‘ 1’ 1 Strong ‘Z’ High Impedance ‘W’ Weak Value Unknown ‘L’ 0 Weak ‘H’ 1 Weak ‘-’ Does not matter Example Nº 7 – Buffer -Output 3 - State library ieee; use ieee. std_logic_1164. all; entity tri_est is port (enable, entrada: in std_logic; salida: out std_logic); end tri_est; architecture arq_buffer of tri_est is begin process (enable, entrada) begin if (enable = ‘ 0’) then salida <= ‘Z’; else salida <= entrada; end if; end process; end arq_buffer; The bit data type does not support the 'Z' value , so you must use the std_logic type, if supported.

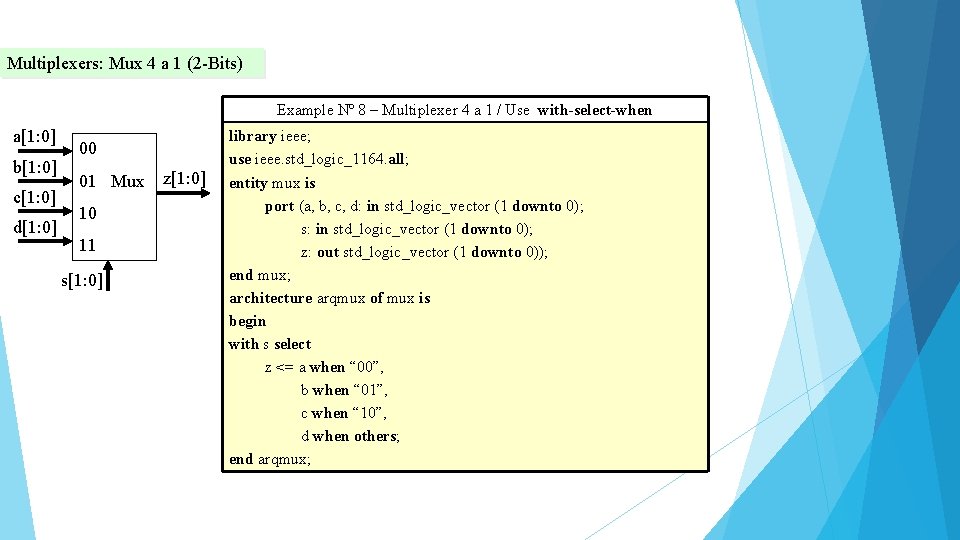

Multiplexers: Mux 4 a 1 (2 -Bits) Example Nº 8 – Multiplexer 4 a 1 / Use with-select-when a[1: 0] b[1: 0] c[1: 0] d[1: 0] 00 01 Mux 10 11 s[1: 0] z[1: 0] library ieee; use ieee. std_logic_1164. all; entity mux is port (a, b, c, d: in std_logic_vector (1 downto 0); s: in std_logic_vector (1 downto 0); z: out std_logic_vector (1 downto 0)); end mux; architecture arqmux of mux is begin with s select z <= a when “ 00”, b when “ 01”, c when “ 10”, d when others; end arqmux;

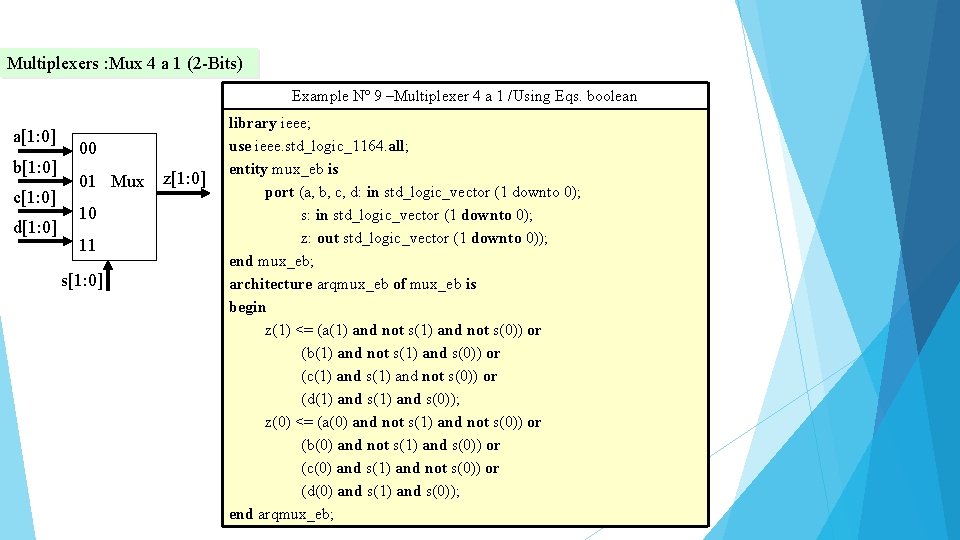

Multiplexers : Mux 4 a 1 (2 -Bits) Example Nº 9 –Multiplexer 4 a 1 /Using Eqs. boolean a[1: 0] b[1: 0] c[1: 0] d[1: 0] 00 01 Mux 10 11 s[1: 0] z[1: 0] library ieee; use ieee. std_logic_1164. all; entity mux_eb is port (a, b, c, d: in std_logic_vector (1 downto 0); s: in std_logic_vector (1 downto 0); z: out std_logic_vector (1 downto 0)); end mux_eb; architecture arqmux_eb of mux_eb is begin z(1) <= (a(1) and not s(0)) or (b(1) and not s(1) and s(0)) or (c(1) and s(1) and not s(0)) or (d(1) and s(0)); z(0) <= (a(0) and not s(1) and not s(0)) or (b(0) and not s(1) and s(0)) or (c(0) and s(1) and not s(0)) or (d(0) and s(1) and s(0)); end arqmux_eb;

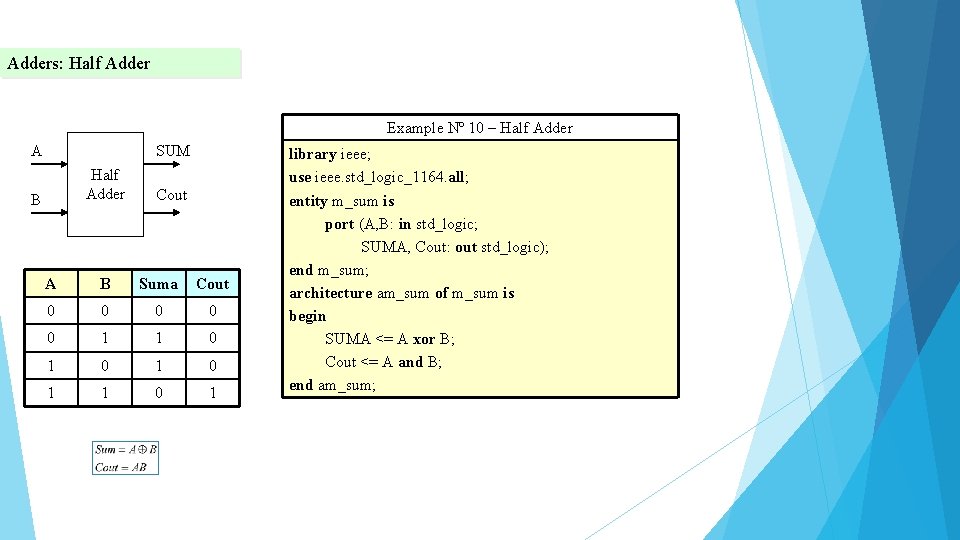

Adders: Half Adder Example Nº 10 – Half Adder A SUM Half Adder B Cout A B Suma Cout 0 0 0 1 1 0 1 0 1 library ieee; use ieee. std_logic_1164. all; entity m_sum is port (A, B: in std_logic; SUMA, Cout: out std_logic); end m_sum; architecture am_sum of m_sum is begin SUMA <= A xor B; Cout <= A and B; end am_sum;

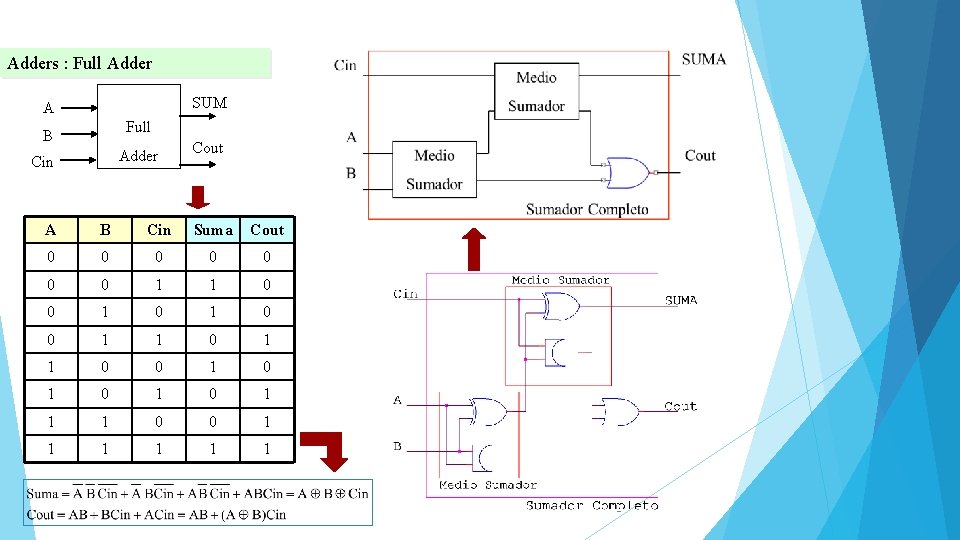

Adders : Full Adder SUM A Full B Adder Cin Cout A B Cin Suma Cout 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1

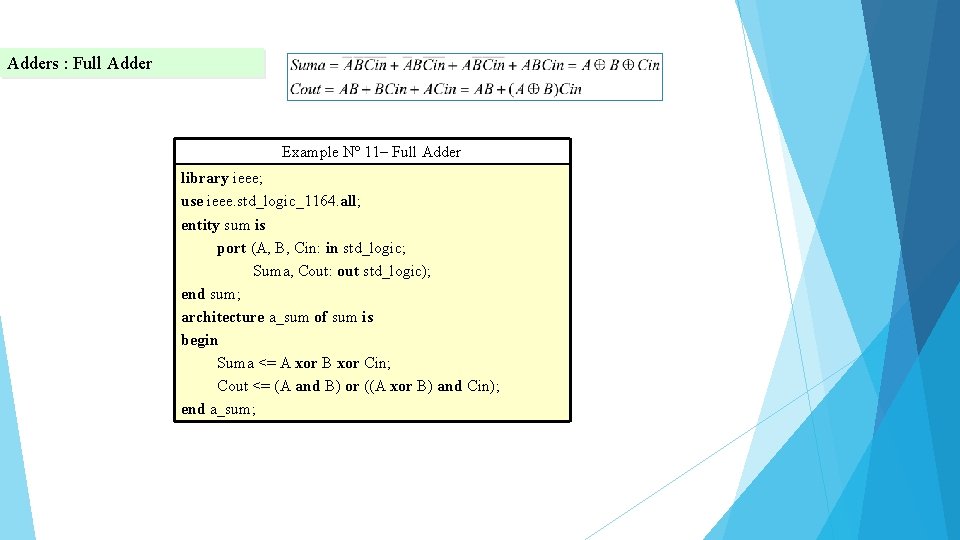

Adders : Full Adder Example Nº 11– Full Adder library ieee; use ieee. std_logic_1164. all; entity sum is port (A, B, Cin: in std_logic; Suma, Cout: out std_logic); end sum; architecture a_sum of sum is begin Suma <= A xor B xor Cin; Cout <= (A and B) or ((A xor B) and Cin); end a_sum;

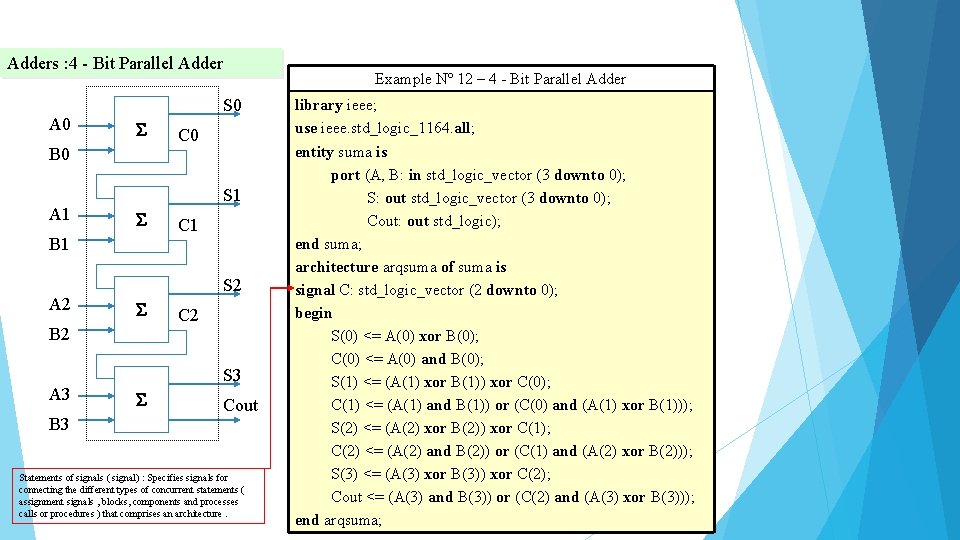

Adders : 4 - Bit Parallel Adder A 0 S 0 B 0 A 1 S 1 B 1 A 2 B 3 C 1 S 2 B 2 A 3 C 0 C 2 S 3 Cout Statements of signals ( signal) : Specifies signals for connecting the different types of concurrent statements ( assignment signals , blocks, components and processes calls or procedures ) that comprises an architecture. Example Nº 12 – 4 - Bit Parallel Adder library ieee; use ieee. std_logic_1164. all; entity suma is port (A, B: in std_logic_vector (3 downto 0); S: out std_logic_vector (3 downto 0); Cout: out std_logic); end suma; architecture arqsuma of suma is signal C: std_logic_vector (2 downto 0); begin S(0) <= A(0) xor B(0); C(0) <= A(0) and B(0); S(1) <= (A(1) xor B(1)) xor C(0); C(1) <= (A(1) and B(1)) or (C(0) and (A(1) xor B(1))); S(2) <= (A(2) xor B(2)) xor C(1); C(2) <= (A(2) and B(2)) or (C(1) and (A(2) xor B(2))); S(3) <= (A(3) xor B(3)) xor C(2); Cout <= (A(3) and B(3)) or (C(2) and (A(3) xor B(3))); end arqsuma;

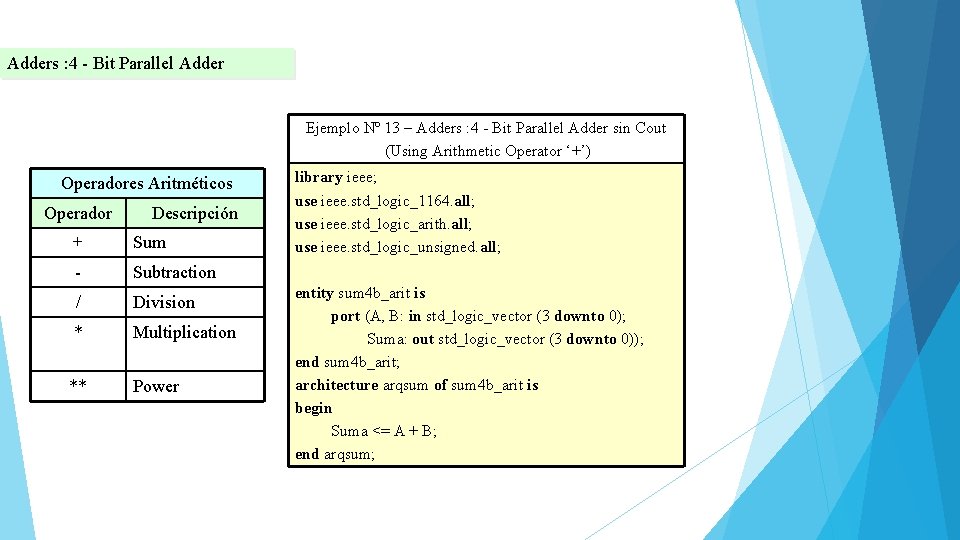

Adders : 4 - Bit Parallel Adder Ejemplo Nº 13 – Adders : 4 - Bit Parallel Adder sin Cout (Using Arithmetic Operator ‘+’) Operadores Aritméticos Operador Descripción + Sum - Subtraction / Division * Multiplication ** Power library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_arith. all; use ieee. std_logic_unsigned. all; entity sum 4 b_arit is port (A, B: in std_logic_vector (3 downto 0); Suma: out std_logic_vector (3 downto 0)); end sum 4 b_arit; architecture arqsum of sum 4 b_arit is begin Suma <= A + B; end arqsum;

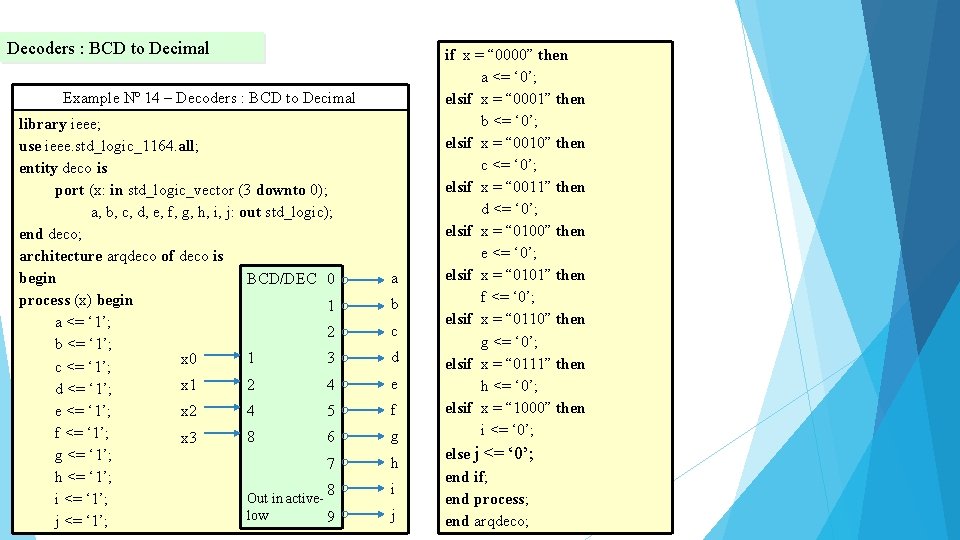

Decoders : BCD to Decimal Example Nº 14 – Decoders : BCD to Decimal library ieee; use ieee. std_logic_1164. all; entity deco is port (x: in std_logic_vector (3 downto 0); a, b, c, d, e, f, g, h, i, j: out std_logic); end deco; architecture arqdeco of deco is begin BCD/DEC 0 process (x) begin 1 a <= ‘ 1’; 2 b <= ‘ 1’; 1 3 x 0 c <= ‘ 1’; 2 4 x 1 d <= ‘ 1’; e <= ‘ 1’; 4 5 x 2 f <= ‘ 1’; 8 6 x 3 g <= ‘ 1’; 7 h <= ‘ 1’; 8 Out in activei <= ‘ 1’; low 9 j <= ‘ 1’; a b c d e f g h i j if x = “ 0000” then a <= ‘ 0’; elsif x = “ 0001” then b <= ‘ 0’; elsif x = “ 0010” then c <= ‘ 0’; elsif x = “ 0011” then d <= ‘ 0’; elsif x = “ 0100” then e <= ‘ 0’; elsif x = “ 0101” then f <= ‘ 0’; elsif x = “ 0110” then g <= ‘ 0’; elsif x = “ 0111” then h <= ‘ 0’; elsif x = “ 1000” then i <= ‘ 0’; else j <= ‘ 0’; end if; end process; end arqdeco;

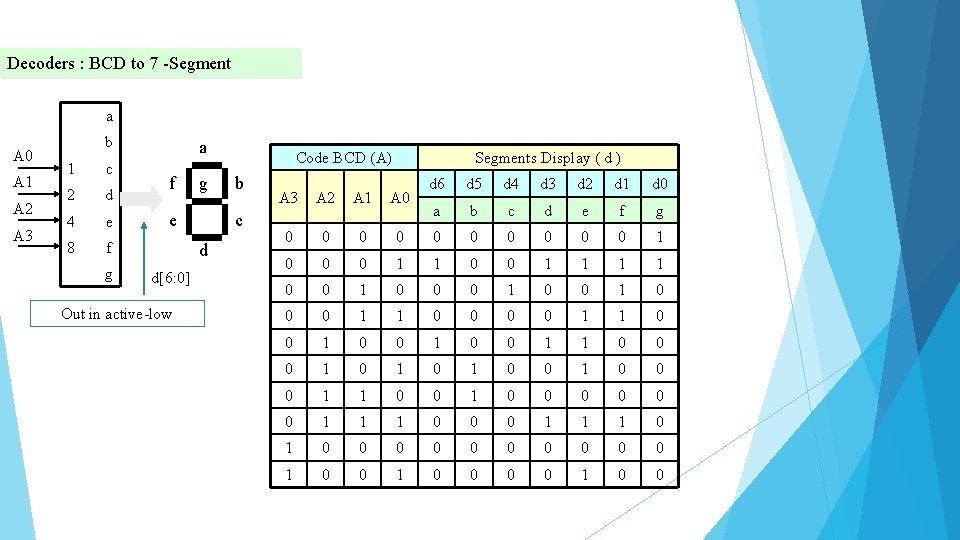

Decoders : BCD to 7 -Segment a A 0 A 1 A 2 A 3 b 1 c 2 d 4 e 8 f g a f g e Out in active-low b c d d[6: 0] Code BCD (A) Segments Display ( d ) d 6 d 5 d 4 d 3 d 2 d 1 d 0 a b c d e f g 0 0 0 0 1 1 0 1 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 1 0 0 0 0 1 0 0 A 3 A 2 A 1 A 0 0 0 0

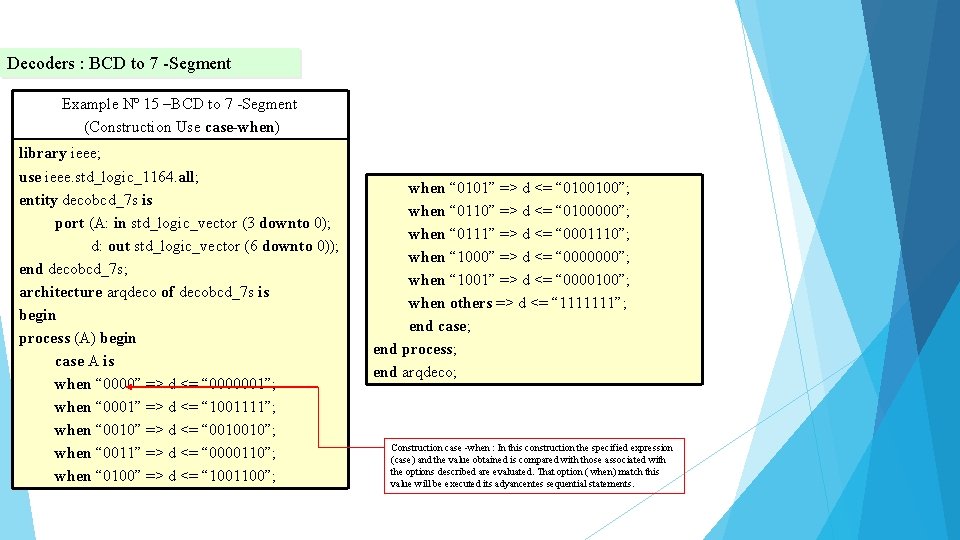

Decoders : BCD to 7 -Segment Example Nº 15 –BCD to 7 -Segment (Construction Use case-when) library ieee; use ieee. std_logic_1164. all; entity decobcd_7 s is port (A: in std_logic_vector (3 downto 0); d: out std_logic_vector (6 downto 0)); end decobcd_7 s; architecture arqdeco of decobcd_7 s is begin process (A) begin case A is when “ 0000” => d <= “ 0000001”; when “ 0001” => d <= “ 1001111”; when “ 0010” => d <= “ 0010010”; when “ 0011” => d <= “ 0000110”; when “ 0100” => d <= “ 1001100”; when “ 0101” => d <= “ 0100100”; when “ 0110” => d <= “ 0100000”; when “ 0111” => d <= “ 0001110”; when “ 1000” => d <= “ 0000000”; when “ 1001” => d <= “ 0000100”; when others => d <= “ 1111111”; end case; end process; end arqdeco; Construction case -when : In this construction the specified expression (case) and the value obtained is compared with those associated with the options described are evaluated. That option ( when) match this value will be executed its adyancentes sequential statements.

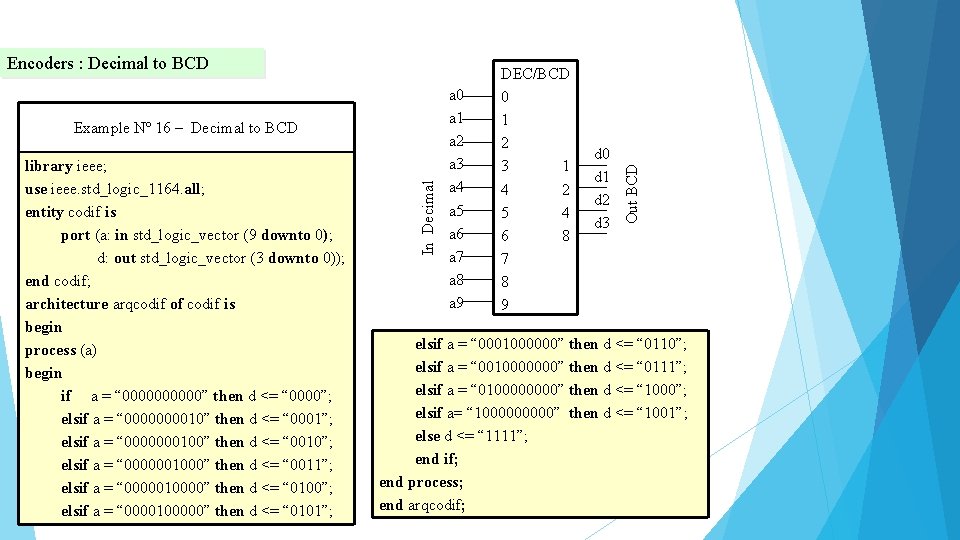

library ieee; use ieee. std_logic_1164. all; entity codif is port (a: in std_logic_vector (9 downto 0); d: out std_logic_vector (3 downto 0)); end codif; architecture arqcodif of codif is begin process (a) begin if a = “ 00000” then d <= “ 0000”; elsif a = “ 000010” then d <= “ 0001”; elsif a = “ 0000000100” then d <= “ 0010”; elsif a = “ 0000001000” then d <= “ 0011”; elsif a = “ 0000010000” then d <= “ 0100”; elsif a = “ 0000100000” then d <= “ 0101”; In Decimal Example Nº 16 – Decimal to BCD a 0 a 1 a 2 a 3 a 4 a 5 a 6 a 7 a 8 a 9 DEC/BCD 0 1 2 3 1 4 2 5 4 6 8 7 8 9 d 0 d 1 d 2 d 3 Out BCD Encoders : Decimal to BCD elsif a = “ 0001000000” then d <= “ 0110”; elsif a = “ 0010000000” then d <= “ 0111”; elsif a = “ 010000” then d <= “ 1000”; elsif a= “ 100000” then d <= “ 1001”; else d <= “ 1111”; end if; end process; end arqcodif;

- Slides: 30