Combinational Logic Design Parity Generator Checker q Parity

Combinational Logic Design Parity Generator & Checker

q Parity Generator/Checkers - XOR &XNOR Revision - Application of XOR&XNOR gates - Parity System - Parity Generator Design - Parity Checker Design - Parity Generator/Checker Chip

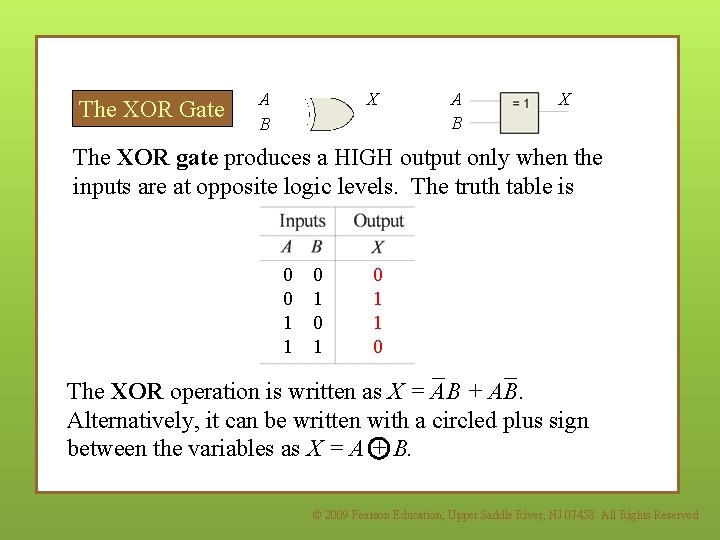

The XOR Gate A B X The XOR gate produces a HIGH output only when the inputs are at opposite logic levels. The truth table is 0 0 1 1 0 1 0 1 1 0 The XOR operation is written as X = AB + AB. Alternatively, it can be written with a circled plus sign between the variables as X = A + B. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

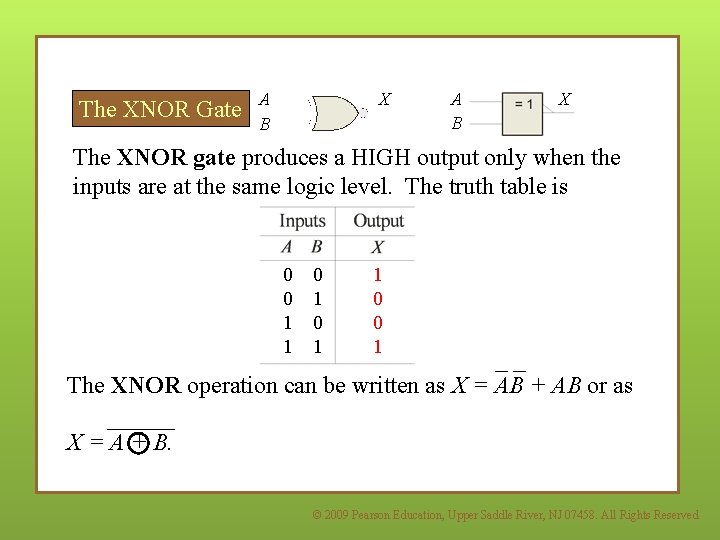

The XNOR Gate A B X The XNOR gate produces a HIGH output only when the inputs are at the same logic level. The truth table is 0 0 1 1 0 0 1 The XNOR operation can be written as X = AB + AB or as X = A + B. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Applications of XOR and XNOR Gates Three 1. 2. 3. common applications: Comparators Controlled inverters Parity generation and checking

Application #3: Parity Checking Parity checking is a method of error detection for simple transmission errors involving one bit. A parity bit is an “extra” bit attached to a group of bits to force the total number of 1’s to be either even (even parity) or odd (odd parity). The ASCII character for “a” is 1100001 and for “A” is 1000001. What is the correct bit to append to make both of these have odd parity? The ASCII “a” has an odd number of bits that are equal to 1; therefore the parity bit is 0. The ASCII “A” has an even number of bits that are equal to 1; therefore the parity bit is 1. © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

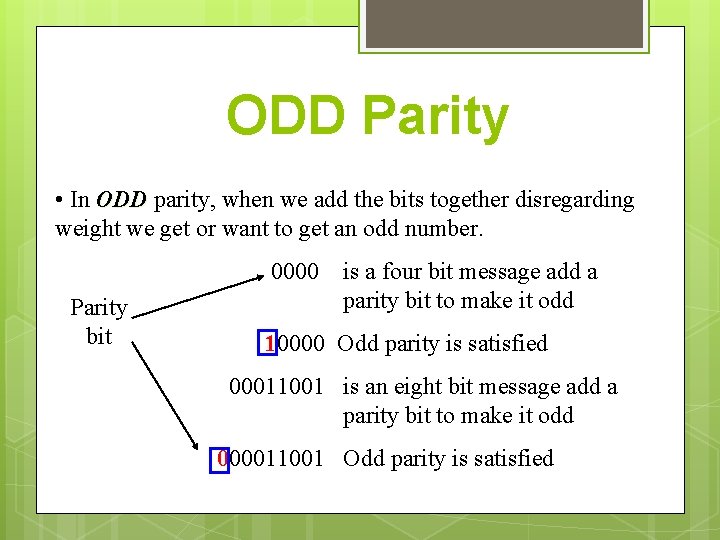

ODD Parity • In ODD parity, when we add the bits together disregarding weight we get or want to get an odd number. 0000 Parity bit is a four bit message add a parity bit to make it odd 10000 Odd parity is satisfied 00011001 is an eight bit message add a parity bit to make it odd 000011001 Odd parity is satisfied

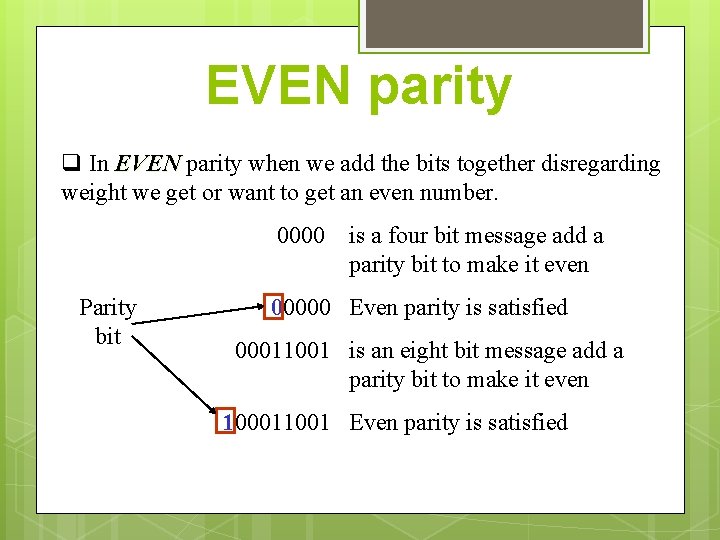

EVEN parity q In EVEN parity when we add the bits together disregarding weight we get or want to get an even number. 0000 Parity bit is a four bit message add a parity bit to make it even 00000 Even parity is satisfied 00011001 is an eight bit message add a parity bit to make it even 100011001 Even parity is satisfied

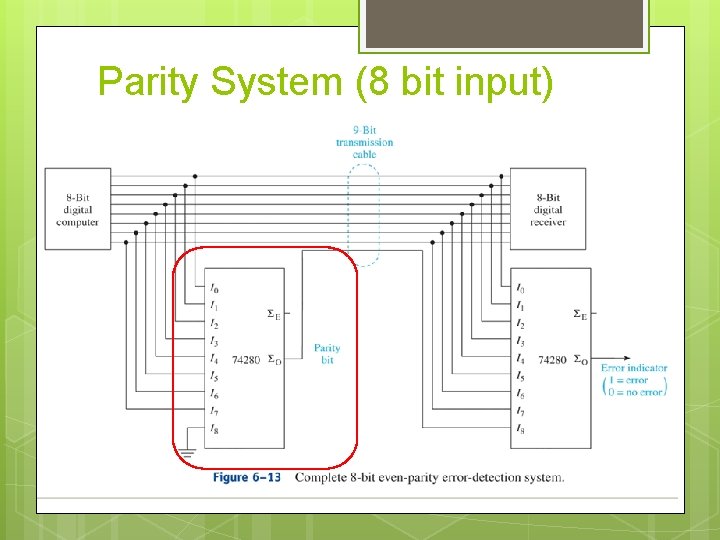

Parity System (8 bit input)

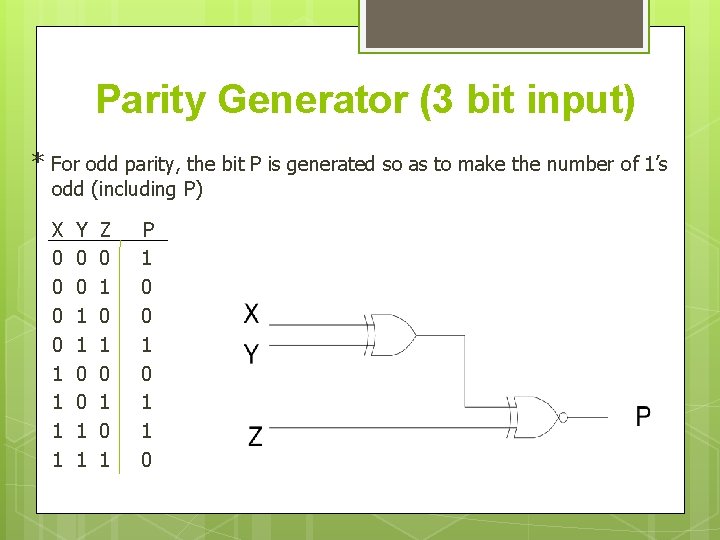

Parity Generator (3 bit input) * For odd parity, the bit P is generated so as to make the number of 1’s odd (including P) X 0 0 1 1 Y 0 0 1 1 Z 0 1 0 1 P 1 0 0 1 1 0

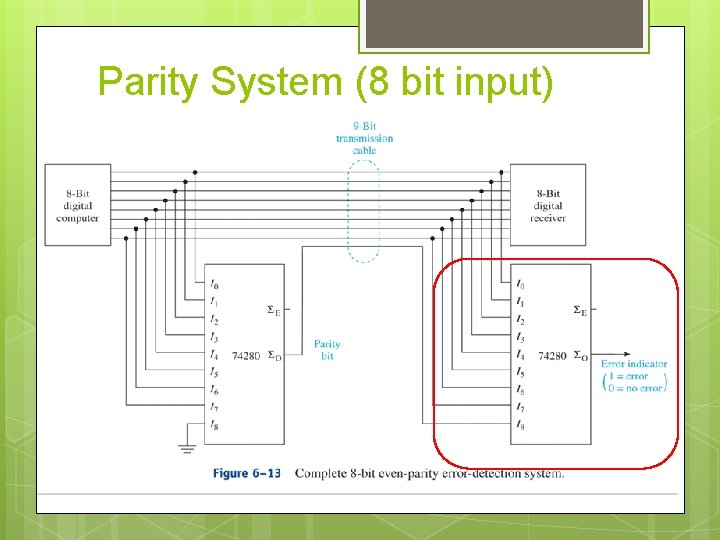

Parity System (8 bit input)

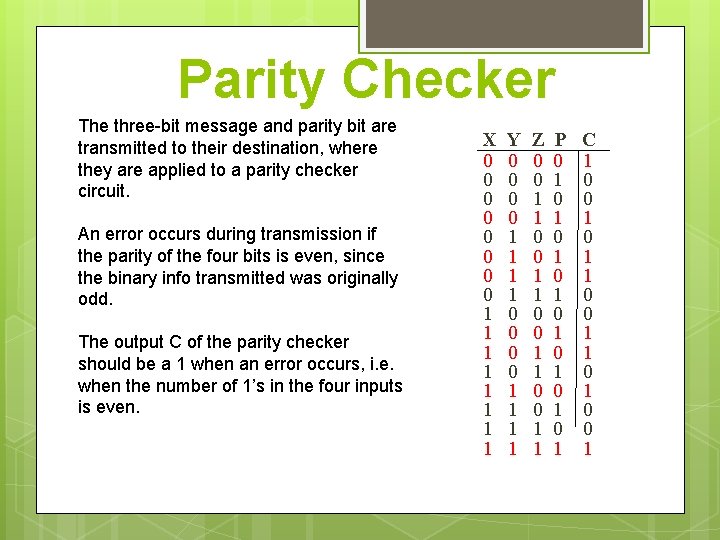

Parity Checker The three-bit message and parity bit are transmitted to their destination, where they are applied to a parity checker circuit. An error occurs during transmission if the parity of the four bits is even, since the binary info transmitted was originally odd. The output C of the parity checker should be a 1 when an error occurs, i. e. when the number of 1’s in the four inputs is even. X 0 0 0 0 1 1 1 1 Y 0 0 0 0 1 1 1 1 Z 0 0 1 1 P 0 1 0 1 C 1 0 0 1 1 0 0 1

Error-Detection q Parity is used in digital circuits to check for errors in transmission. q In Four bit transmission a parity bit is added to make the fifth bit. q In a eight bit transmission a parity bit is added to made a ninth bit. …. . and so on.

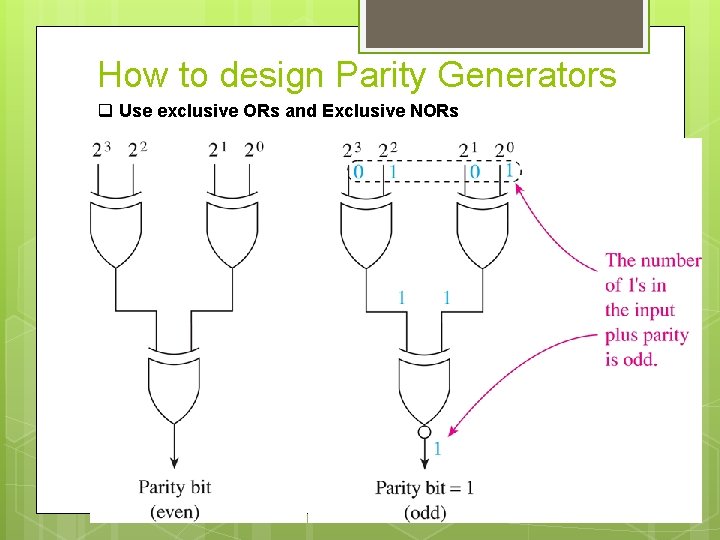

Parity Generators To implement parity checking, we need circuitry on the transmitter that generates the parity bit for each group of bits being sent. This circuitry is called a parity generator. Next slide shows how to build 4 -bit even or odd parity generators.

How to design Parity Generators q Use exclusive ORs and Exclusive NORs

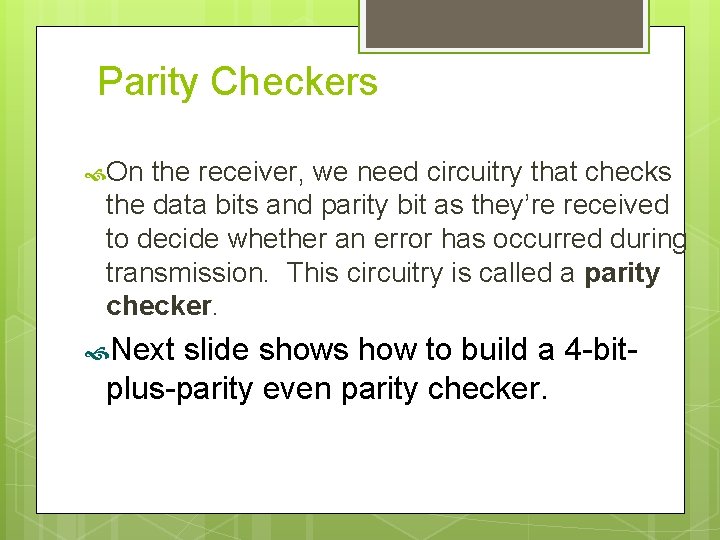

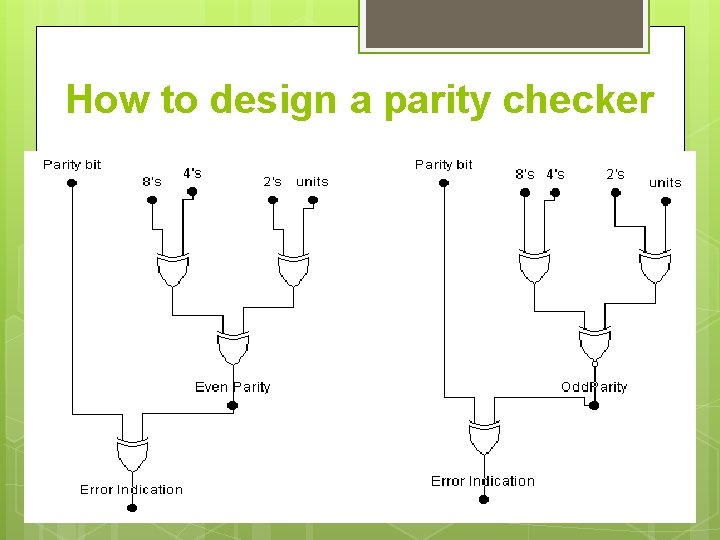

Parity Checkers On the receiver, we need circuitry that checks the data bits and parity bit as they’re received to decide whether an error has occurred during transmission. This circuitry is called a parity checker. Next slide shows how to build a 4 -bitplus-parity even parity checker.

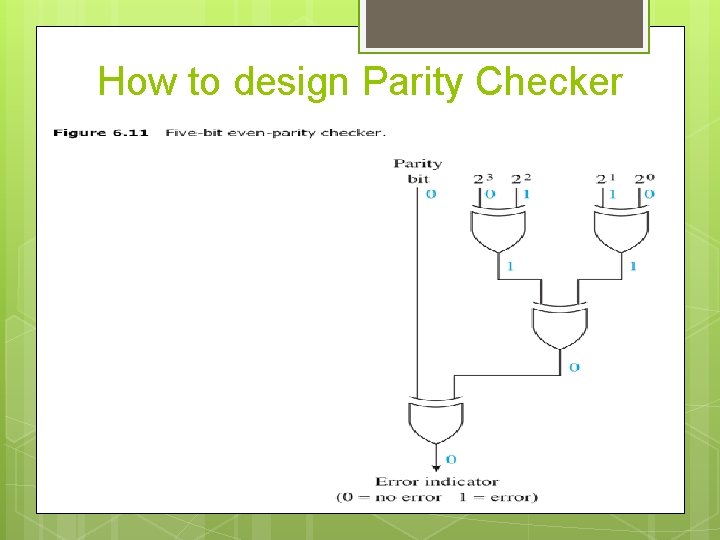

How to design Parity Checker

How to design a parity checker

Odd or even parity - 0 out of a parity checker means the parity checks and all is ok -1 out of a parity checker means there is an error

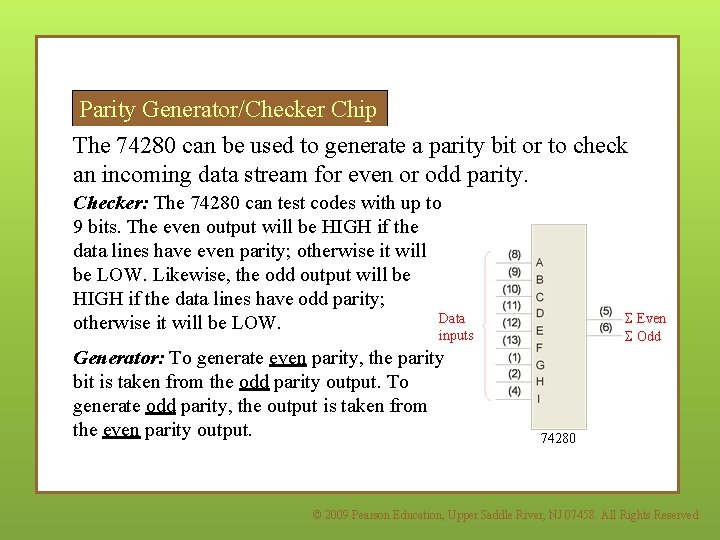

Parity Generator/Checker Chip The 74280 can be used to generate a parity bit or to check an incoming data stream for even or odd parity. Checker: The 74280 can test codes with up to 9 bits. The even output will be HIGH if the data lines have even parity; otherwise it will be LOW. Likewise, the odd output will be HIGH if the data lines have odd parity; Data otherwise it will be LOW. S Even S Odd inputs Generator: To generate even parity, the parity bit is taken from the odd parity output. To generate odd parity, the output is taken from the even parity output. 74280 © 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The End

- Slides: 21