COLDATAP 3 Testing Scott Holm David Christian February

COLDATA_P 3 Testing Scott Holm & David Christian February 22, 2021

Review of what’s new in this version • PLL • Now locks to 62. 5 MHz system clock instead of dedicated 40 MHz clock • Previous version failed to lock at room temp with 1. 1 V bias (required 1. 17 V at RT; locked at 1. 1 V when cold). • I 2 C relay fix • First command to a new I 2 C address failed if it was a read. • Other small bug fixes • Timestamp now counts 62. 5 MHz clock ticks • Timestamp has been extended to 15 bits (16 th bit used to indicate test pulse issued to LAr. ASIC) • Registers used to control time between LAr. ASIC pulse edges extended to 16 bits • Additional functionality • Added a means to determine cable delay from WIB • Added 3 more general purpose I/O pads & made these bits tri-stateable • Procedure to read e. Fuse registers made more user friendly • Modified data frame structure to make WIB microcoding easier and eliminated Frame-15

Testing Delay • COLDATA_P 3 chips arrived at FNAL on 1/21, but… • The test board didn’t arrive until a couple of days later and… • The wrong board was made (there was a mixup and the wrong design file was sent for fabrication). • We were finally able to start testing last Thursday (2/18). • First tests were done with two COLDATA_P 3 chips mounted on the test board, but no COLDADCs.

I 2 C is functional • Scott verified that I 2 C registers in both COLDATA chips can be read and written. • LVDS I 2 C interface works • CMOS relay and CMOS I 2 C interface works

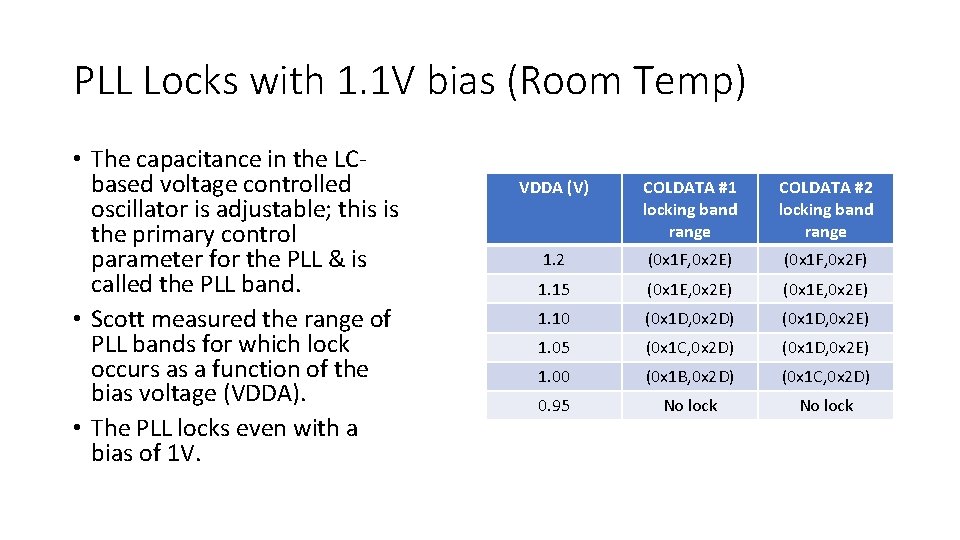

PLL Locks with 1. 1 V bias (Room Temp) • The capacitance in the LCbased voltage controlled oscillator is adjustable; this is the primary control parameter for the PLL & is called the PLL band. • Scott measured the range of PLL bands for which lock occurs as a function of the bias voltage (VDDA). • The PLL locks even with a bias of 1 V. VDDA (V) COLDATA #1 locking band range COLDATA #2 locking band range 1. 2 (0 x 1 F, 0 x 2 E) (0 x 1 F, 0 x 2 F) 1. 15 (0 x 1 E, 0 x 2 E) 1. 10 (0 x 1 D, 0 x 2 D) (0 x 1 D, 0 x 2 E) 1. 05 (0 x 1 C, 0 x 2 D) (0 x 1 D, 0 x 2 E) 1. 00 (0 x 1 B, 0 x 2 D) (0 x 1 C, 0 x 2 D) 0. 95 No lock

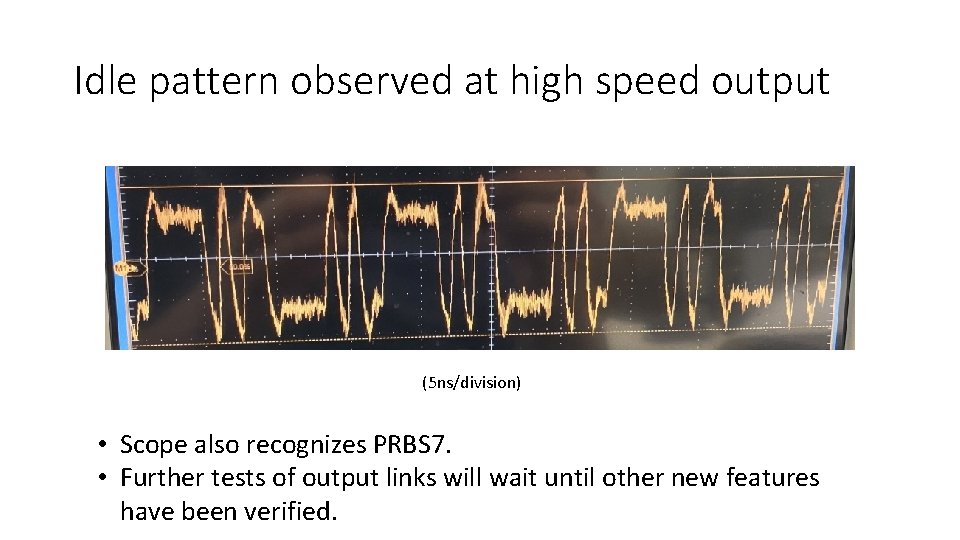

Idle pattern observed at high speed output (5 ns/division) • Scope also recognizes PRBS 7. • Further tests of output links will wait until other new features have been verified.

- Slides: 6