COE 1502 Memory Model Introduction l Our current

- Slides: 13

COE 1502 Memory Model

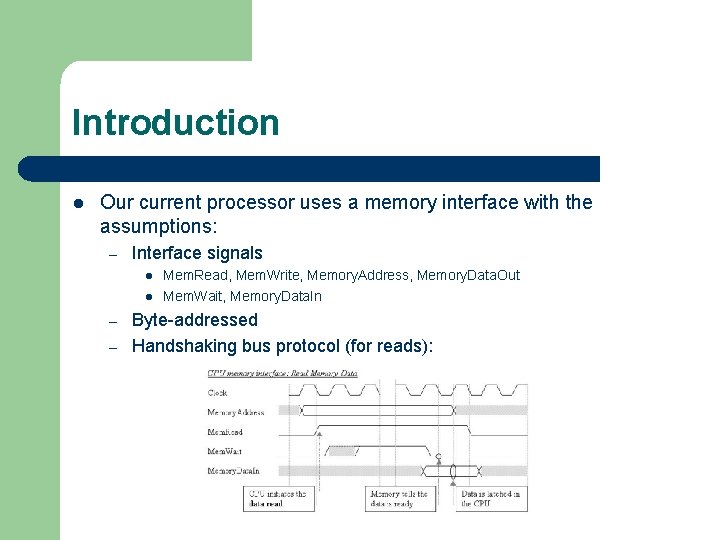

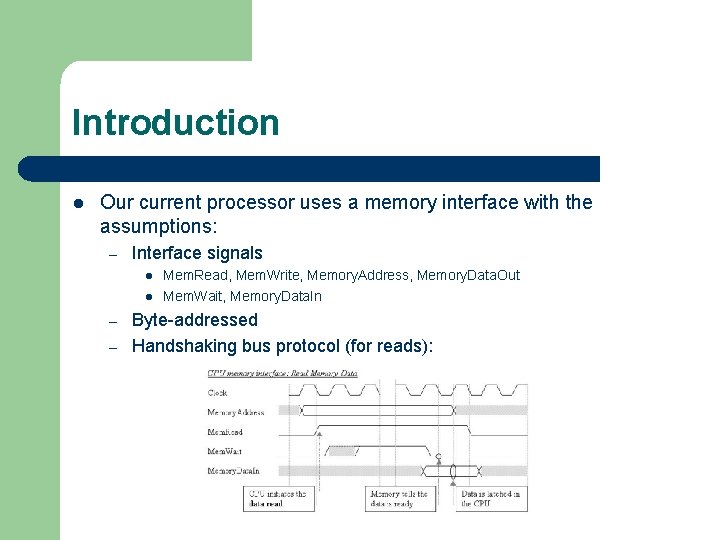

Introduction l Our current processor uses a memory interface with the assumptions: – Interface signals l l – – Mem. Read, Mem. Write, Memory. Address, Memory. Data. Out Mem. Wait, Memory. Data. In Byte-addressed Handshaking bus protocol (for reads):

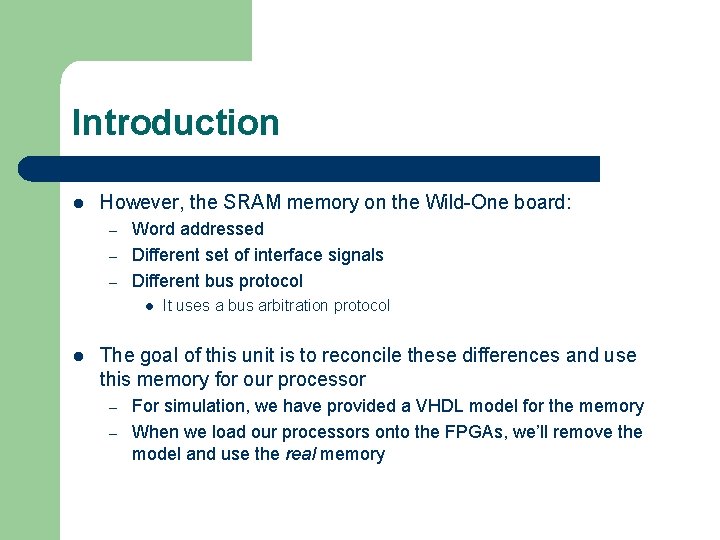

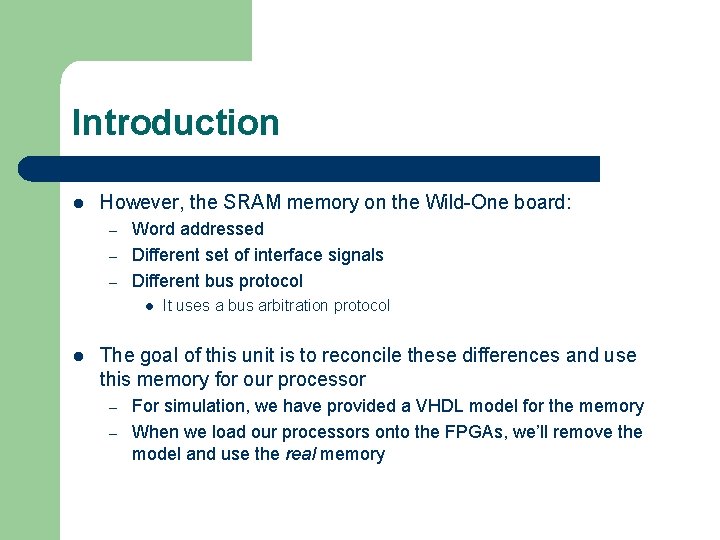

Introduction l However, the SRAM memory on the Wild-One board: – – – Word addressed Different set of interface signals Different bus protocol l l It uses a bus arbitration protocol The goal of this unit is to reconcile these differences and use this memory for our processor – – For simulation, we have provided a VHDL model for the memory When we load our processors onto the FPGAs, we’ll remove the model and use the real memory

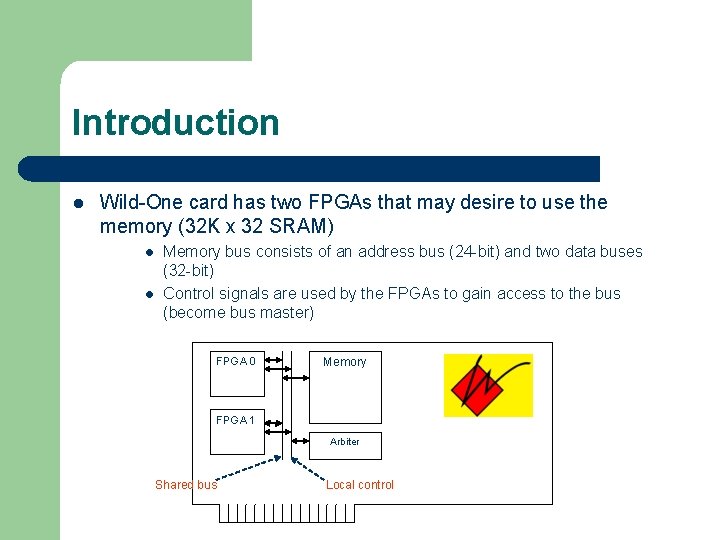

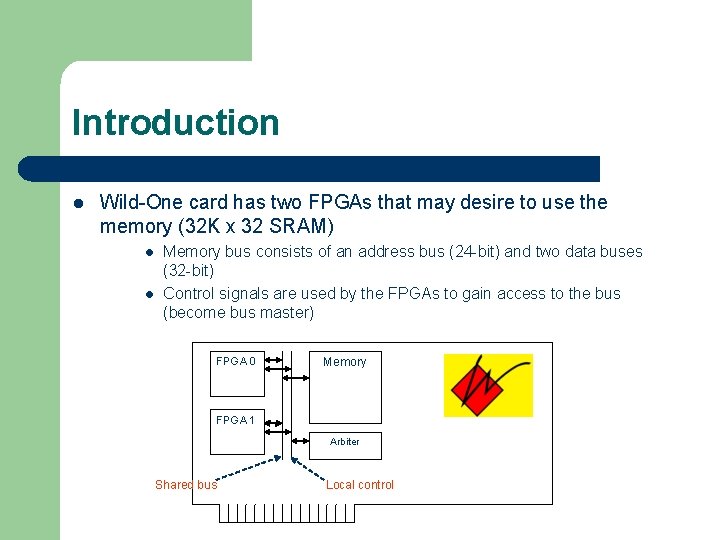

Introduction l Wild-One card has two FPGAs that may desire to use the memory (32 K x 32 SRAM) l l Memory bus consists of an address bus (24 -bit) and two data buses (32 -bit) Control signals are used by the FPGAs to gain access to the bus (become bus master) FPGA 0 Memory FPGA 1 Arbiter Shared bus Local control

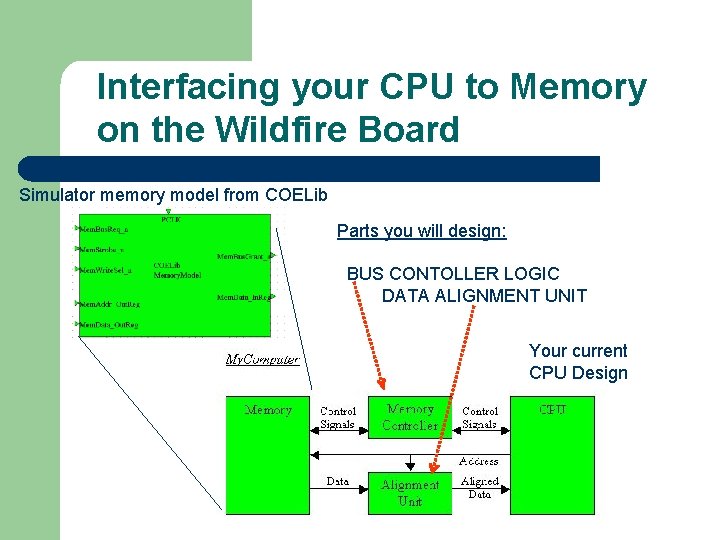

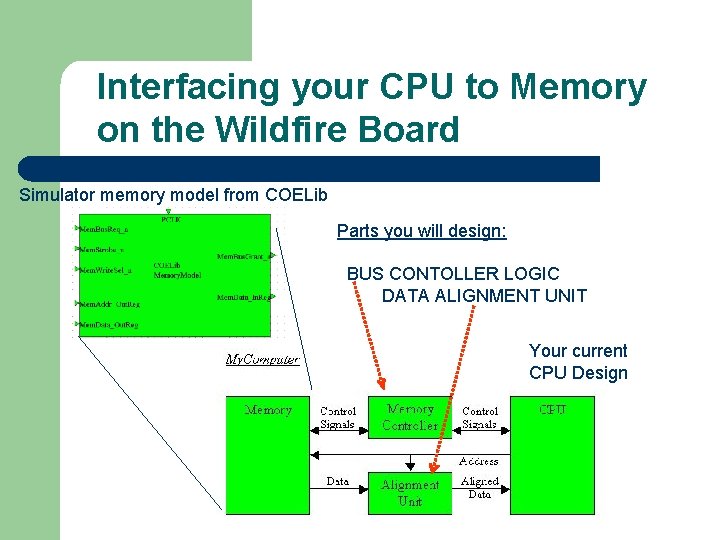

Interfacing your CPU to Memory on the Wildfire Board Simulator memory model from COELib Parts you will design: BUS CONTOLLER LOGIC DATA ALIGNMENT UNIT Your current CPU Design

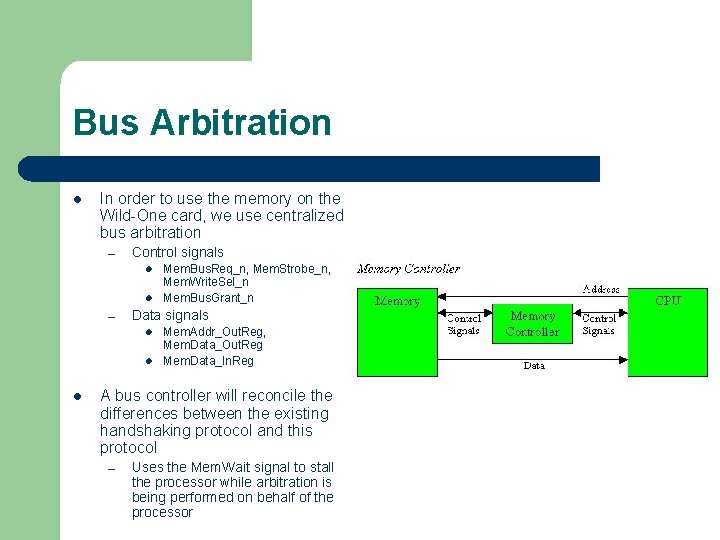

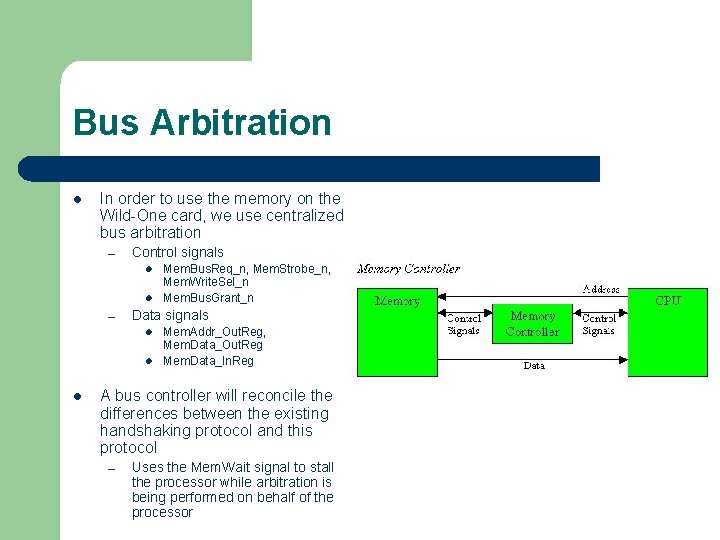

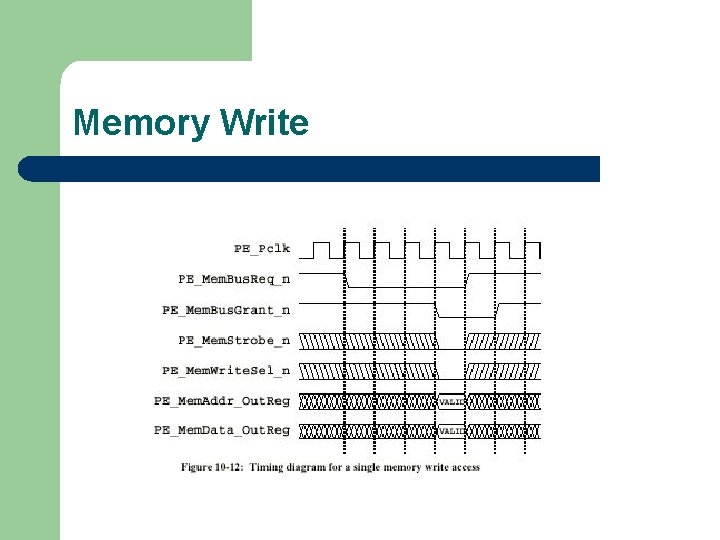

Bus Arbitration l In order to use the memory on the Wild-One card, we use centralized bus arbitration – Control signals l l – Data signals l l l Mem. Bus. Req_n, Mem. Strobe_n, Mem. Write. Sel_n Mem. Bus. Grant_n Mem. Addr_Out. Reg, Mem. Data_Out. Reg Mem. Data_In. Reg A bus controller will reconcile the differences between the existing handshaking protocol and this protocol – Uses the Mem. Wait signal to stall the processor while arbitration is being performed on behalf of the processor

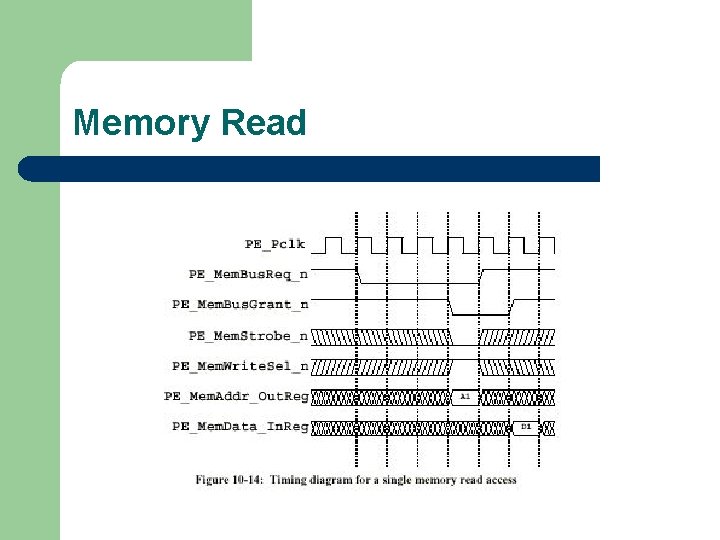

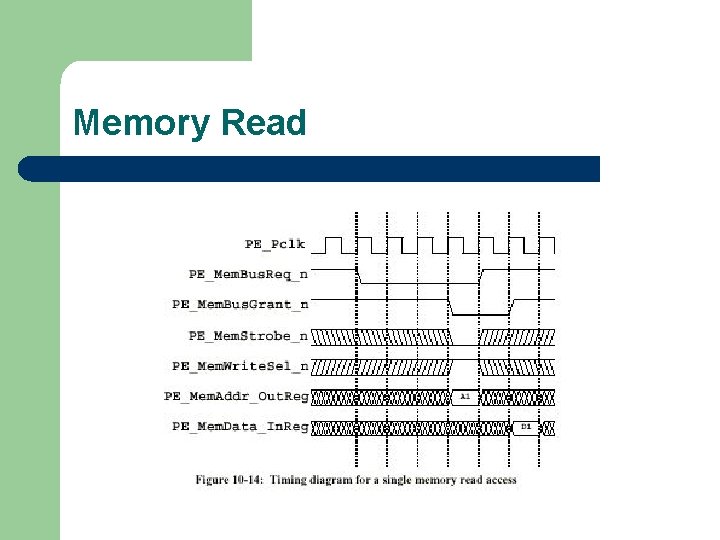

Memory Read

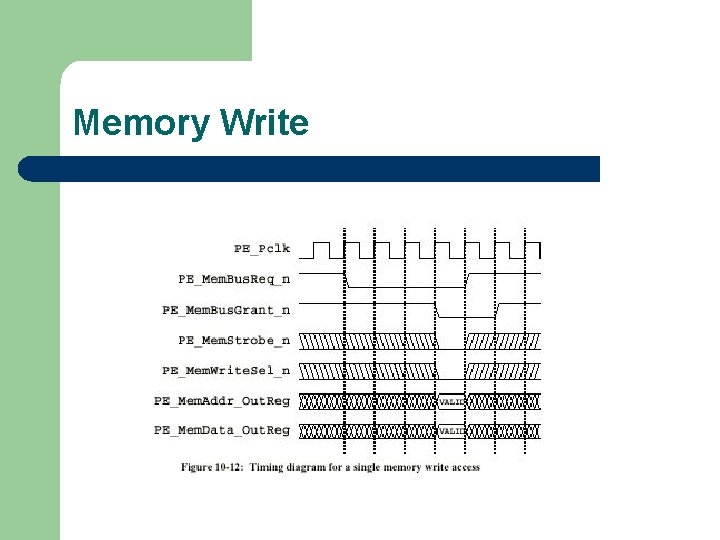

Memory Write

Bus Arbitration l We use a bus for the processor to access the memory – – A bus is a shared communication link How is the bus reserved by a device that wishes it to communicate? l Single Master – l CPU is master, memory/(all others) is slave (we assumed this before) Arbitration schemes Multiple bus master system – Arbiter decides who is the bus master – Arbiter may employ priority –

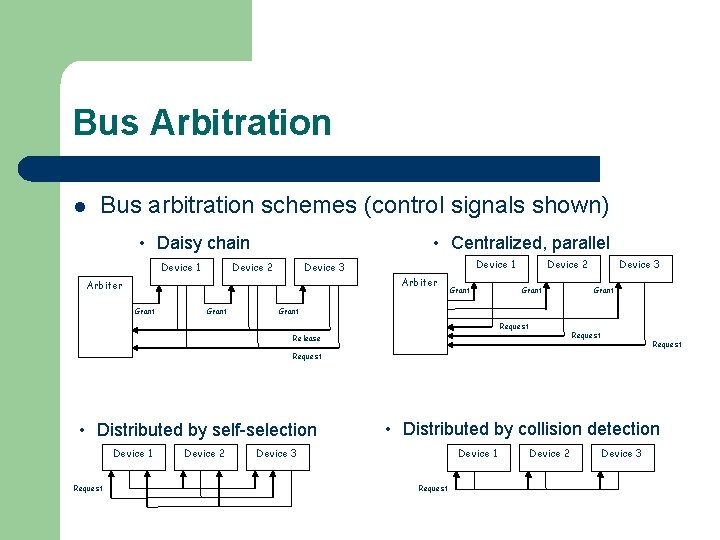

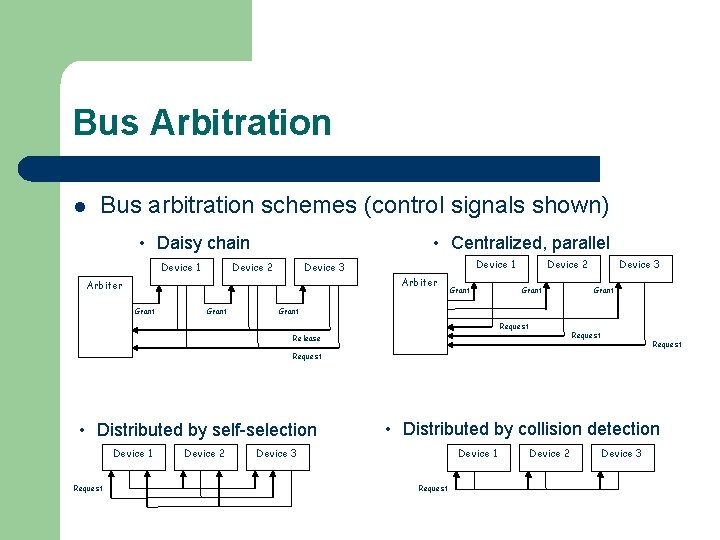

Bus Arbitration l Bus arbitration schemes (control signals shown) • Daisy chain Device 1 • Centralized, parallel Device 2 Device 1 Device 3 Arbiter Grant Device 2 Grant Device 3 Grant Request Release Request • Distributed by self-selection Device 1 Request Device 2 • Distributed by collision detection Device 3 Device 1 Request Device 2 Device 3

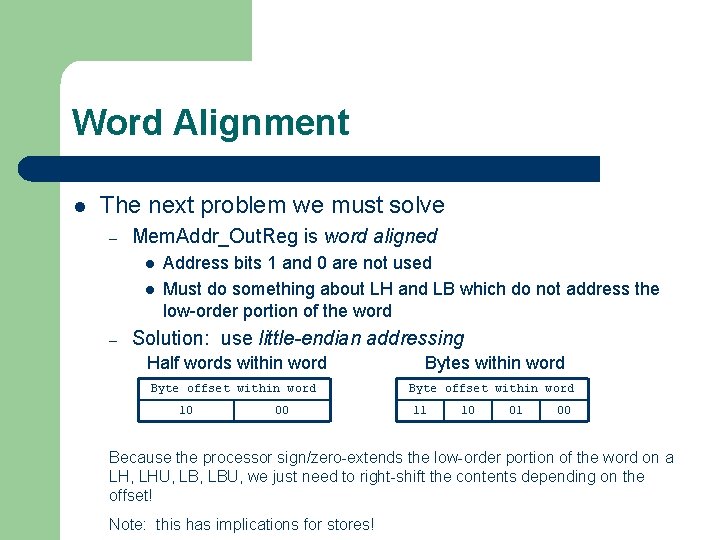

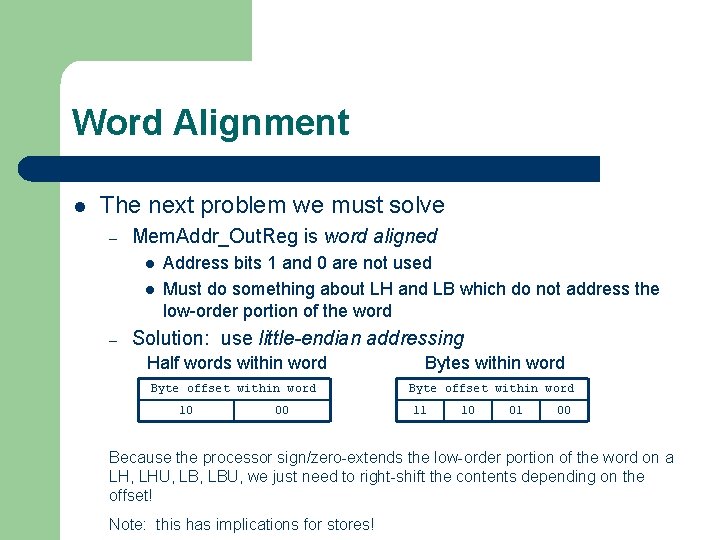

Word Alignment l The next problem we must solve – Mem. Addr_Out. Reg is word aligned l l – Address bits 1 and 0 are not used Must do something about LH and LB which do not address the low-order portion of the word Solution: use little-endian addressing Half words within word Byte offset within word 10 00 11 10 01 00 Because the processor sign/zero-extends the low-order portion of the word on a LH, LHU, LBU, we just need to right-shift the contents depending on the offset! Note: this has implications for stores!

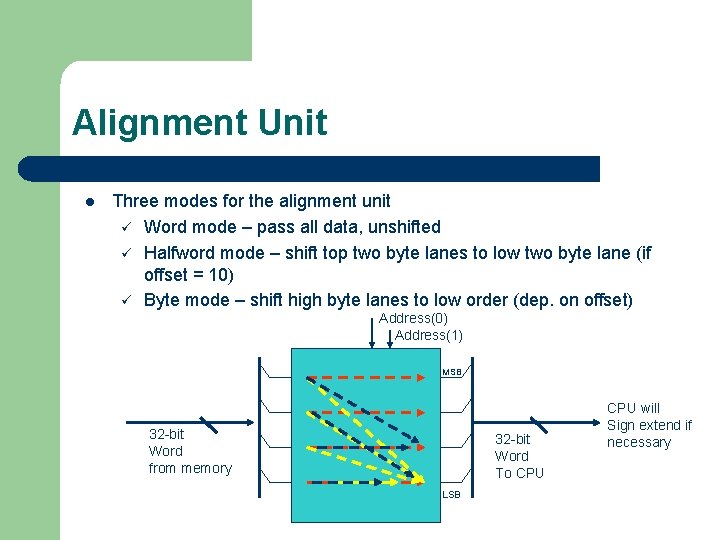

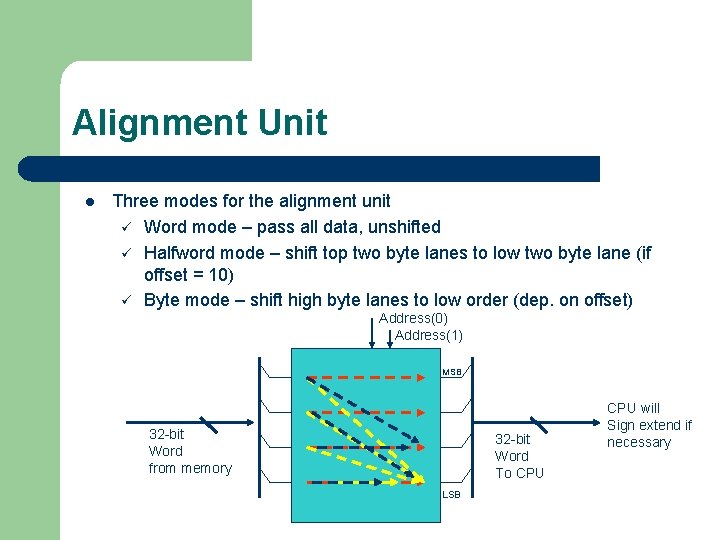

Alignment Unit l Three modes for the alignment unit ü Word mode – pass all data, unshifted ü Halfword mode – shift top two byte lanes to low two byte lane (if offset = 10) ü Byte mode – shift high byte lanes to low order (dep. on offset) Address(0) Address(1) MSB 32 -bit Word from memory 32 -bit Word To CPU LSB CPU will Sign extend if necessary

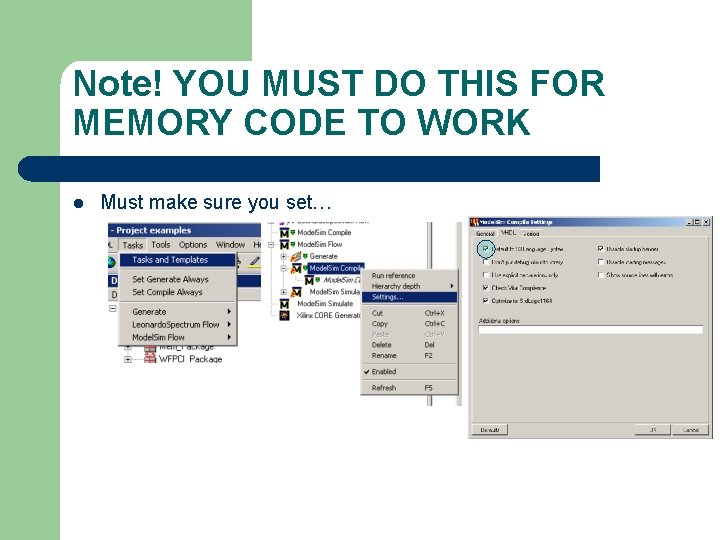

Note! YOU MUST DO THIS FOR MEMORY CODE TO WORK l Must make sure you set…