CNET 315 Microprocessor Assembly Language Phiros Mansur Nalakath

CNET 315 Microprocessor & Assembly Language Phiros Mansur Nalakath Course Coordinator College of Computer Science & Information Systems, Jazan University, KSA 1

Chapter - 5 Interrupts in 8086 Microprocessor

Interrupt �Interrupt is the method of creating a temporary halt during program execution and allows peripheral devices to access the microprocessor. �The microprocessor responds to the interrupt with an ISR (Interrupt Service Routine). � ISR is a short program to instruct the microprocessor on how to handle the interrupt.

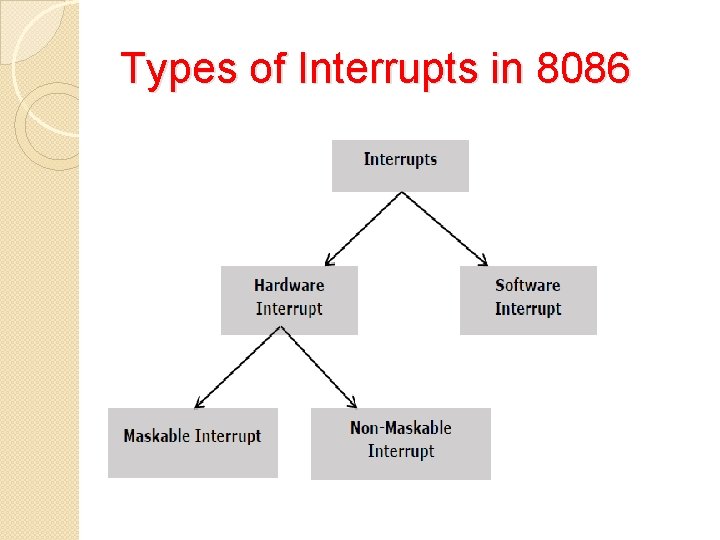

Types of Interrupts in 8086

Hardware Interrupts �Hardware interrupt is caused by any peripheral device by sending a signal through the specified pins NMI or INTR to the microprocessor. �NMI is a Non-Maskable Interrupt and INTR is a maskable interrupt having lower priority. �INTA called Interrupt Acknowledge.

Hardware Interrupts. . . NMI �Single non-maskable interrupt pin (NMI) �Higher priority than INTR interrupt �Type 2 interrupt INTR �INTR is a maskable interrupt �INTR interrupt is activated by an I/O port.

Software Interrupts �Some instructions in the program can create interrupts like, INT instruction with type number �There are 256 interrupt types under this group.

Interrupt Execution steps �Flag register value is pushed to the stack. �CS value and IP value of the return address are pushed on to the stack. �IP is loaded from the contents of the word location ‘Type number’ × 4 �CS is loaded from the contents of the next word location. �Interrupt Flag and Trap Flag are reset to 0

INTERRUPT VECTOR TABLE (IVT)

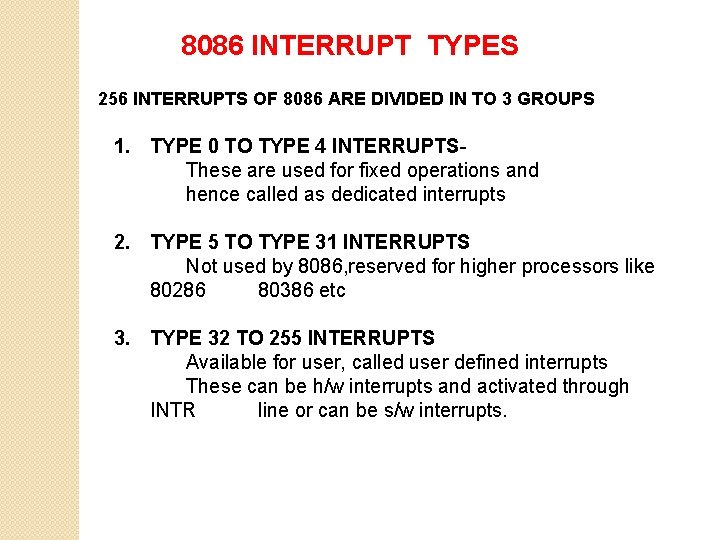

8086 INTERRUPT TYPES 256 INTERRUPTS OF 8086 ARE DIVIDED IN TO 3 GROUPS 1. TYPE 0 TO TYPE 4 INTERRUPTSThese are used for fixed operations and hence called as dedicated interrupts 2. TYPE 5 TO TYPE 31 INTERRUPTS Not used by 8086, reserved for higher processors like 80286 80386 etc 3. TYPE 32 TO 255 INTERRUPTS Available for user, called user defined interrupts These can be h/w interrupts and activated through INTR line or can be s/w interrupts.

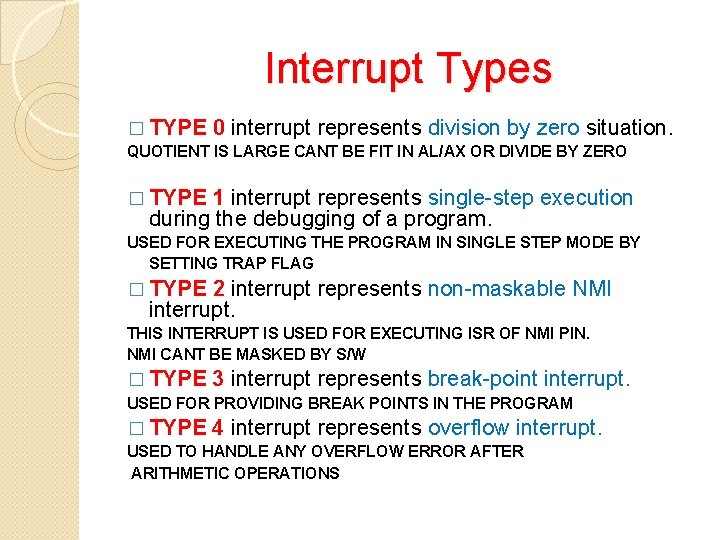

Interrupt Types � TYPE 0 interrupt represents division by zero situation. QUOTIENT IS LARGE CANT BE FIT IN AL/AX OR DIVIDE BY ZERO � TYPE 1 interrupt represents single-step execution during the debugging of a program. USED FOR EXECUTING THE PROGRAM IN SINGLE STEP MODE BY SETTING TRAP FLAG � TYPE 2 interrupt represents non-maskable NMI interrupt. THIS INTERRUPT IS USED FOR EXECUTING ISR OF NMI PIN. NMI CANT BE MASKED BY S/W � TYPE 3 interrupt represents break-point interrupt. USED FOR PROVIDING BREAK POINTS IN THE PROGRAM � TYPE 4 interrupt represents overflow interrupt. USED TO HANDLE ANY OVERFLOW ERROR AFTER ARITHMETIC OPERATIONS

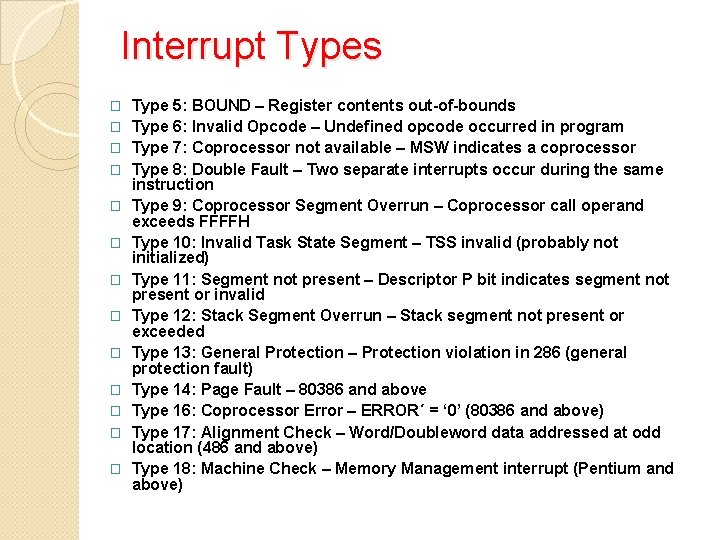

Interrupt Types � � � � Type 5: BOUND – Register contents out-of-bounds Type 6: Invalid Opcode – Undefined opcode occurred in program Type 7: Coprocessor not available – MSW indicates a coprocessor Type 8: Double Fault – Two separate interrupts occur during the same instruction Type 9: Coprocessor Segment Overrun – Coprocessor call operand exceeds FFFFH Type 10: Invalid Task State Segment – TSS invalid (probably not initialized) Type 11: Segment not present – Descriptor P bit indicates segment not present or invalid Type 12: Stack Segment Overrun – Stack segment not present or exceeded Type 13: General Protection – Protection violation in 286 (general protection fault) Type 14: Page Fault – 80386 and above Type 16: Coprocessor Error – ERROR΄ = ‘ 0’ (80386 and above) Type 17: Alignment Check – Word/Doubleword data addressed at odd location (486 and above) Type 18: Machine Check – Memory Management interrupt (Pentium and above)

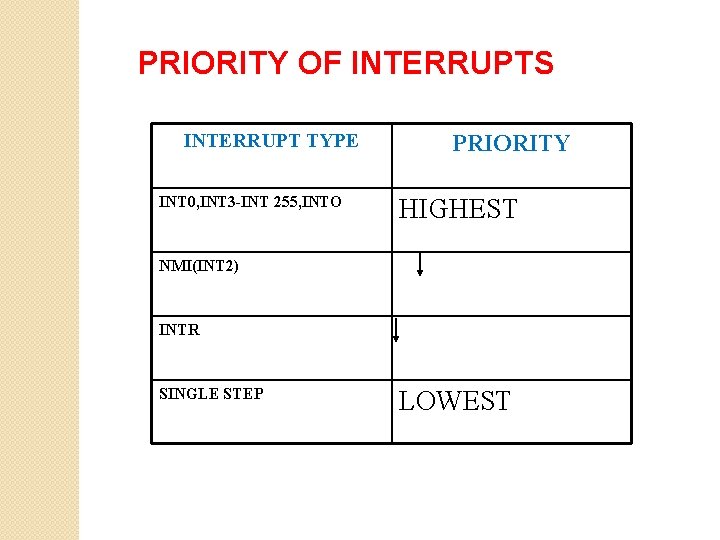

PRIORITY OF INTERRUPTS INTERRUPT TYPE INT 0, INT 3 -INT 255, INTO PRIORITY HIGHEST NMI(INT 2) INTR SINGLE STEP LOWEST

Programmable Interrupt Controller 8259

8259 �The Programmable Interrupt Controller (PIC) functions as an overall manager in an Interrupt-Driven system. �It accepts requests from the peripheral equipments. �Determines which of the incoming requests is of the highest priority. �Issues an interrupt to the CPU based on this determination

Cont’d �The PIC manages eight levels of requests and has built-in features for expandability to other PIC (up to 64 levels). �The priority modes can be changed or reconfigured dynamically at any time during main program operation

Block diagram of the 8259 A Programmable Interrupt Controller

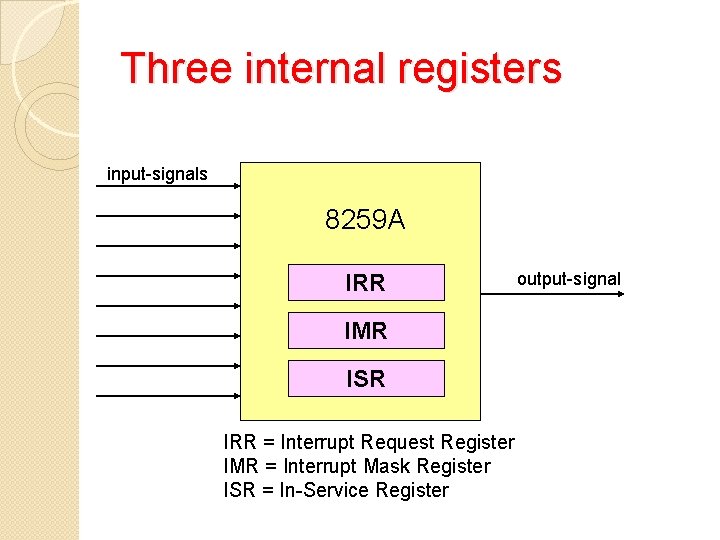

Three internal registers input-signals 8259 A IRR IMR ISR IRR = Interrupt Request Register IMR = Interrupt Mask Register ISR = In-Service Register output-signal

Interrupt Request Register (IRR) �The interrupts at the IR input lines are handled by two registers in cascade, the Interrupt Request Register (l. RR) and the In- Service Register (l. SR). �The IRR is used to indicate all the interrupt levels which are requesting service.

In-Service Register (ISR) �ISR is used to store all the interrupt levels which are currently being serviced

Priority Resolver �PR determines the priorities of the bits set in the l. RR. �The highest priority is selected and strobed into the corresponding bit of the l. SR during the INTA sequence.

Interrupt Mask Register (IMR) �The l. MR stores the bits which disable the interrupt lines to be masked. �The IMR operates on the output of the IRR. �Masking of a higher priority input will not affect the interrupt request lines of lower priority.

Data Bus Buffer �This 3 -state, bidirectional 8 -bit buffer is used to interface the PIC to the System Data Bus. �Control words and status information are transferred through the Data Bus Buffer. �D[7. . 0] are connected to the system bus and are used by the microprocessor to write or read the internal registers of the 8259.

Important Signals �D 0 -D 7 : Bidirectional data connections �IR 0 -IR 7 : Interrupt request inputs �WR΄ : Write input strobe �RD΄ : Read input connects to the IORC΄signal �INT : Output, connects to μP INTR pin �INTA΄ : Input, connects to μP INTA΄ pin �A 0 : Command word select �CS΄ : Chip select input �SP/EN΄ : Slave program/enable buffer pin �CAS 0 -CAS 2 : Outputs from master to slave for cascading multiple 8259 A chips

Questions… ? Thank you…!

- Slides: 25