CNED LINEL CNED ELECTRONIQUE NUMERIQUE anne 2010 11

- Slides: 10

CNED LINEL CNED ELECTRONIQUE NUMERIQUE année 2010 -11 Travaux pratiques Électronique numérique VHDL Intervenants : Boitier V. / Perisse T. 1

LINEL CNED 2007 -08 LINEL CNED ELECTRONIQUENUMERIQUE Électronique Numérique VHDL Travaux pratiques Outils mis à la disposition des étudiants : Le logiciel MAXPLUS 2 de la société ALTERA (version étudiante téléchargeable et gratuite sur le net) Une maquette permettant la programmation de 2 composants au choix (EPM 7128 S ou EPF 10 K 20). Un guide d’utilisation de la maquette récupérer sur le site d’ALTERA. Dans un premier temps nous allons travailler sur un composant appartenant à la famille MAX 7000 S qui est de type EEPROM le EPM 7128 SLC 84 – 15. La configuration matérielle pourra être modifiée à volonté par l’utilisateur directement sur le circuit (I. S. P. : In Situ Programmable) sans avoir à utiliser de programmateur. Intervenants : Boitier V. / Perisse T. 2

LINEL CNED 2007 -08 LINEL CNED ELECTRONIQUENUMERIQUE Travaux pratiques VHDL TP 1 – Initiation au logiciel Maxplus 2 : Réaliser une porte ET au format. gdf (entrée graphique) et effectuer l’ensemble des opérations de programmation (en incluant l a simulation de la porte afin de valider le bon fonctionnement). Réaliser une porte OU au format. vhd (entrée en texte vhdl)… Réaliser une porte inverseuse au format. wdf (entrée en chronogramme). . . Proposer un projet graphique de OU exclusif (2 entrées) utilisant le. sym des trois portes déjà réalisées (ET. sym OU. sym et INV. sym). Intervenants : Boitier V. / Perisse T. 3

LINEL CNED 2007 -08 LINEL CNED ELECTRONIQUENUMERIQUE Travaux pratiques VHDL TP 2 - Additionneurs : Préparation (position du problème, table de vérité, tableau de karnaugh, écriture des équations, écriture du code VHDL…) Réaliser un additionneur de deux mots de 1 bit A 1 et B 1 avec retenue d’entrée Cin, et retenue de sortie Cout. Table de vérité; Tableau de Karnaugh; Equations de S 1 et de Cout; Schéma structurel à l’aide de portes. Compilation et simulation fonctionnelle. Intégration et validation sur le composant. Associer la structure précédente pour réaliser un additionneur 3 bits avec retenue. A 3, A 2, A 1 et B 3, B 2, B 1 Cout, S 3, S 2, S 1 Ecrire une description VHDL réalisant un additionneur (8 bits) (On privilégiera l’utilisation de vecteurs). Intervenants : Boitier V. / Perisse T. 4

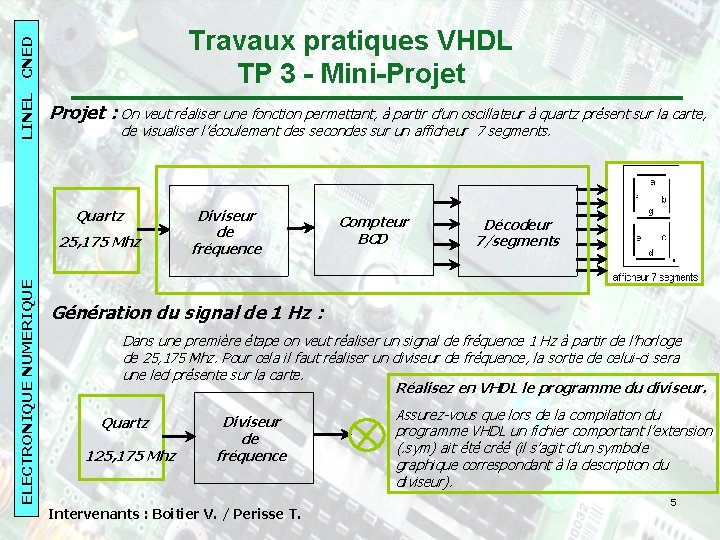

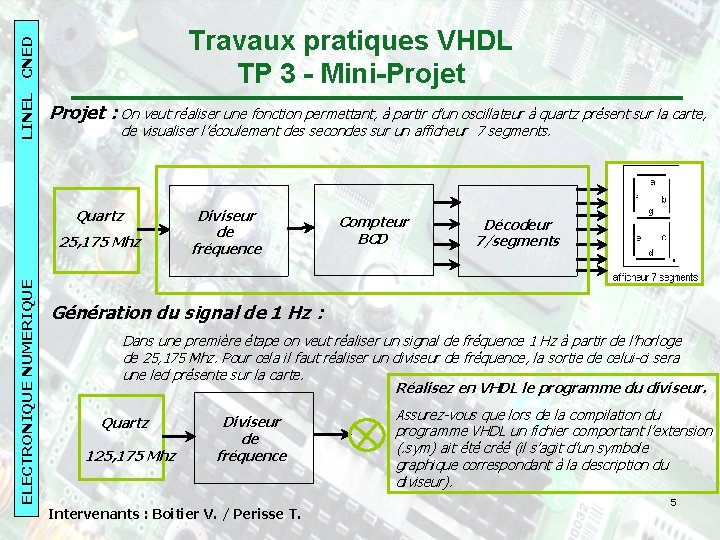

LINEL CNED 2007 -08 LINEL CNED Travaux pratiques VHDL TP 3 - Mini-Projet : On veut réaliser une fonction permettant, à partir d’un oscillateur à quartz présent sur la carte, de visualiser l’écoulement des secondes sur un afficheur 7 segments. Quartz ELECTRONIQUENUMERIQUE 25, 175 Mhz Diviseur de fréquence Compteur BCD Décodeur 7/segments Génération du signal de 1 Hz : Dans une première étape on veut réaliser un signal de fréquence 1 Hz à partir de l’horloge de 25, 175 Mhz. Pour cela il faut réaliser un diviseur de fréquence, la sortie de celui-ci sera une led présente sur la carte. Réalisez en VHDL le programme du diviseur. Quartz 125, 175 Mhz Diviseur de fréquence Intervenants : Boitier V. / Perisse T. Assurez-vous que lors de la compilation du programme VHDL un fichier comportant l’extension (. sym) ait été créé (il s’agit d’un symbole graphique correspondant à la description du diviseur). 5

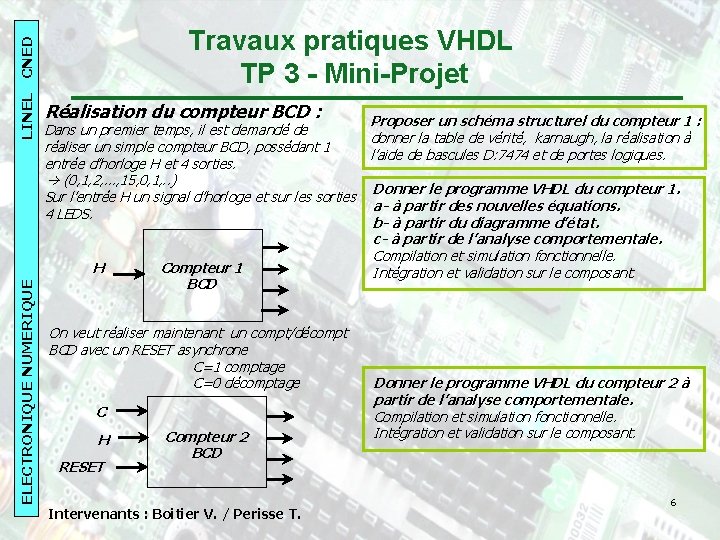

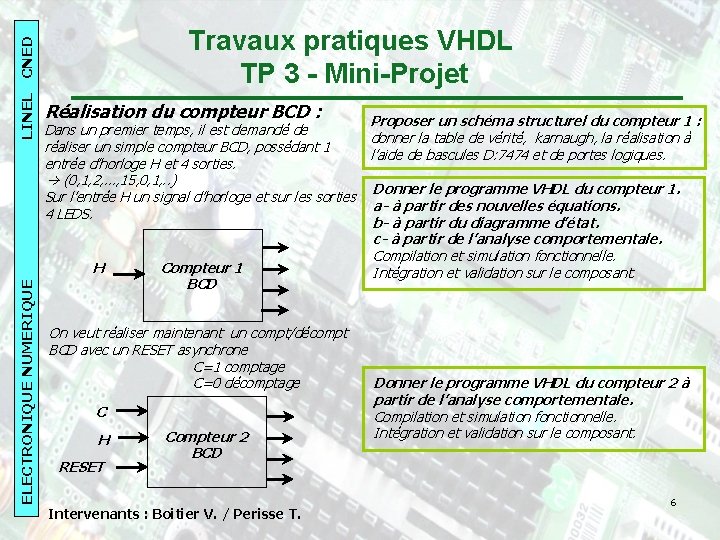

LINEL CNED 2007 -08 LINEL CNED ELECTRONIQUENUMERIQUE Travaux pratiques VHDL TP 3 - Mini-Projet Réalisation du compteur BCD : Proposer un schéma structurel du compteur 1 : Dans un premier temps, il est demandé de donner la table de vérité, karnaugh, la réalisation à réaliser un simple compteur BCD, possédant 1 l’aide de bascules D: 7474 et de portes logiques. entrée d’horloge H et 4 sorties. (0, 1, 2, …, 15, 0, 1, . . ) Donner le programme VHDL du compteur 1. Sur l’entrée H un signal d’horloge et sur les sorties a- à partir des nouvelles équations. 4 LEDS. b- à partir du diagramme d’état. c- à partir de l’analyse comportementale. Compilation et simulation fonctionnelle. Compteur 1 H Intégration et validation sur le composant. BCD On veut réaliser maintenant un compt/décompt BCD avec un RESET asynchrone C=1 comptage C=0 décomptage C H RESET Compteur 2 BCD Intervenants : Boitier V. / Perisse T. Donner le programme VHDL du compteur 2 à partir de l’analyse comportementale. Compilation et simulation fonctionnelle. Intégration et validation sur le composant. 6

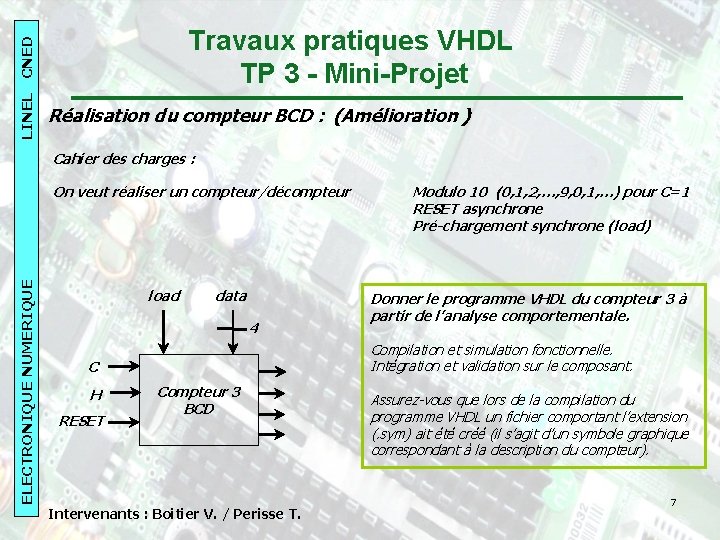

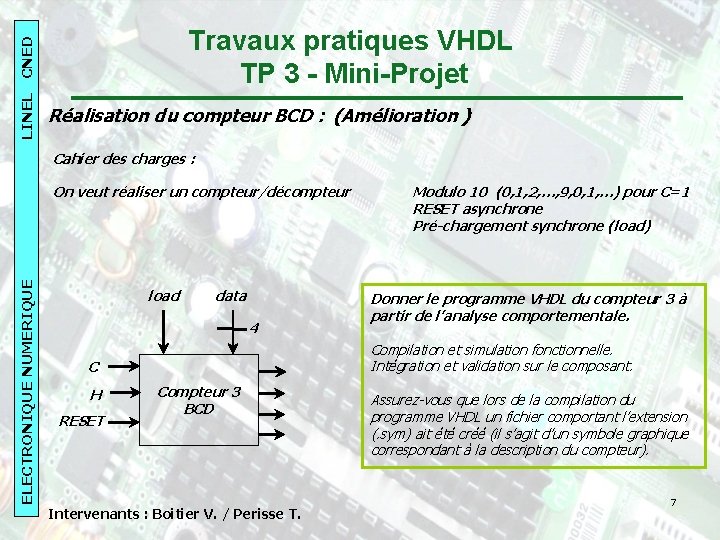

LINEL CNED 2007 -08 LINEL CNED ELECTRONIQUENUMERIQUE Travaux pratiques VHDL TP 3 - Mini-Projet Réalisation du compteur BCD : (Amélioration ) Cahier des charges : On veut réaliser un compteur/décompteur load data 4 RESET Donner le programme VHDL du compteur 3 à partir de l’analyse comportementale. Compilation et simulation fonctionnelle. Intégration et validation sur le composant. C H Modulo 10 (0, 1, 2, …, 9, 0, 1, …) pour C=1 RESET asynchrone Pré-chargement synchrone (load) Compteur 3 BCD Intervenants : Boitier V. / Perisse T. Assurez-vous que lors de la compilation du programme VHDL un fichier comportant l’extension (. sym) ait été créé (il s’agit d’un symbole graphique correspondant à la description du compteur). 7

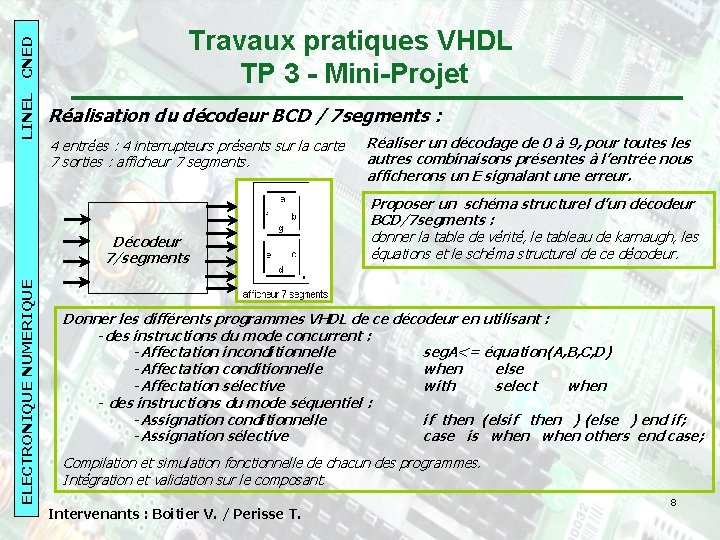

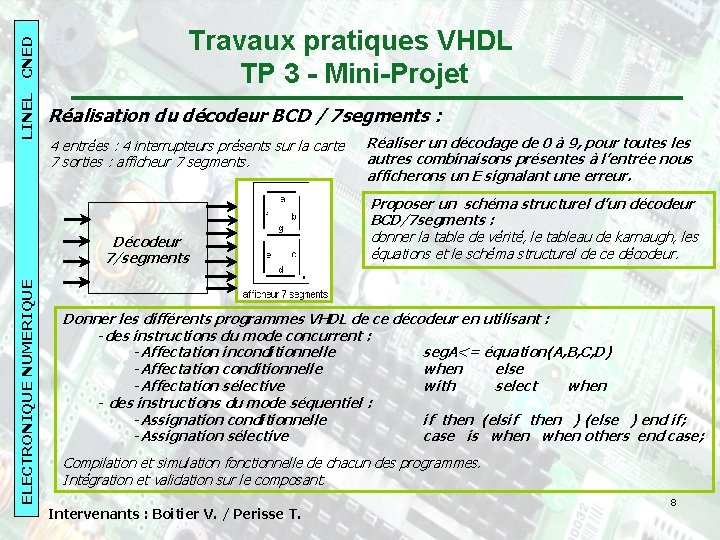

LINEL CNED 2007 -08 LINEL CNED Travaux pratiques VHDL TP 3 - Mini-Projet Réalisation du décodeur BCD / 7 segments : 4 entrées : 4 interrupteurs présents sur la carte 7 sorties : afficheur 7 segments. ELECTRONIQUENUMERIQUE Décodeur 7/segments Réaliser un décodage de 0 à 9, pour toutes les autres combinaisons présentes à l’entrée nous afficherons un E signalant une erreur. Proposer un schéma structurel d’un décodeur BCD/7 segments : donner la table de vérité, le tableau de karnaugh, les équations et le schéma structurel de ce décodeur. Donner les différents programmes VHDL de ce décodeur en utilisant : -des instructions du mode concurrent : -Affectation inconditionnelle seg. A<= équation(A, B, C, D) -Affectation conditionnelle when else -Affectation sélective with select when - des instructions du mode séquentiel : -Assignation conditionnelle if then (elsif then ) (else ) end if; -Assignation sélective case is when others end case; Compilation et simulation fonctionnelle de chacun des programmes. Intégration et validation sur le composant. Intervenants : Boitier V. / Perisse T. 8

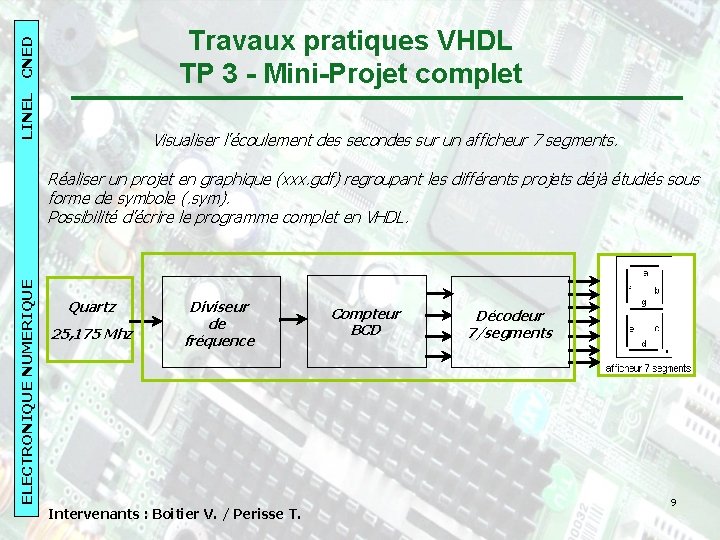

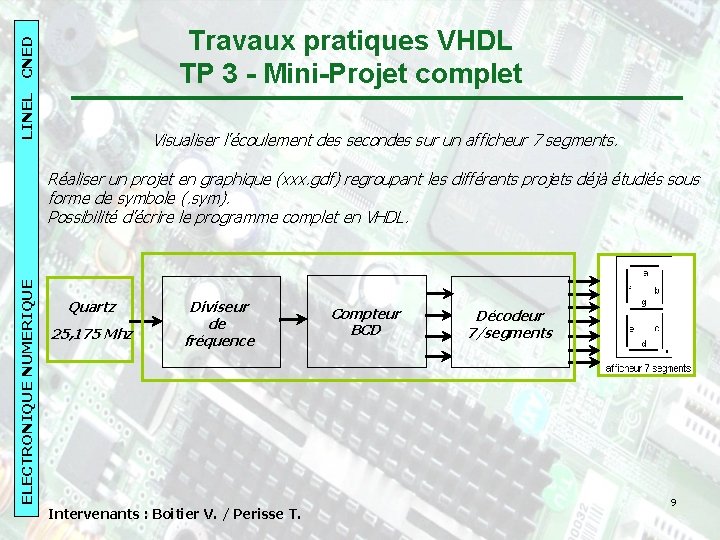

LINEL CNED 2007 -08 LINEL CNED ELECTRONIQUENUMERIQUE Travaux pratiques VHDL TP 3 - Mini-Projet complet Visualiser l’écoulement des secondes sur un afficheur 7 segments. Réaliser un projet en graphique (xxx. gdf) regroupant les différents projets déjà étudiés sous forme de symbole (. sym). Possibilité d’écrire le programme complet en VHDL. Quartz 25, 175 Mhz Diviseur de fréquence Intervenants : Boitier V. / Perisse T. Compteur BCD Décodeur 7/segments 9

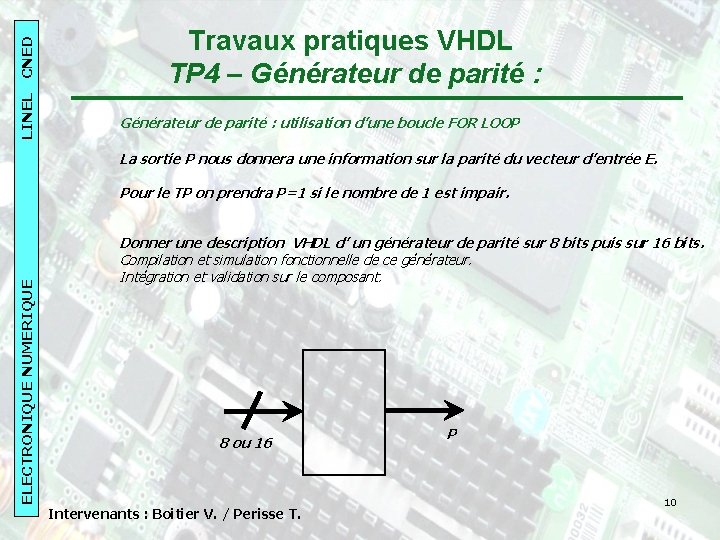

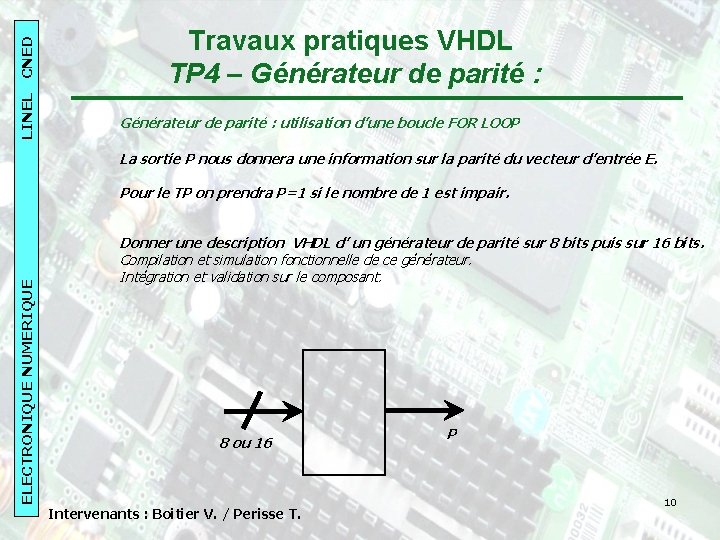

LINEL CNED 2007 -08 LINEL CNED ELECTRONIQUENUMERIQUE Travaux pratiques VHDL TP 4 – Générateur de parité : utilisation d’une boucle FOR LOOP La sortie P nous donnera une information sur la parité du vecteur d’entrée E. Pour le TP on prendra P=1 si le nombre de 1 est impair. Donner une description VHDL d’ un générateur de parité sur 8 bits puis sur 16 bits. Compilation et simulation fonctionnelle de ce générateur. Intégration et validation sur le composant. 8 ou 16 Intervenants : Boitier V. / Perisse T. P 10