CMS Week Sept 2002 HCAL Data Concentrator Status

- Slides: 14

CMS Week Sept 2002 HCAL Data Concentrator Status Report for RUWG and Calibration WG Eric Hazen, Jim Rohlf, Shouxiang Wu Boston University 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen

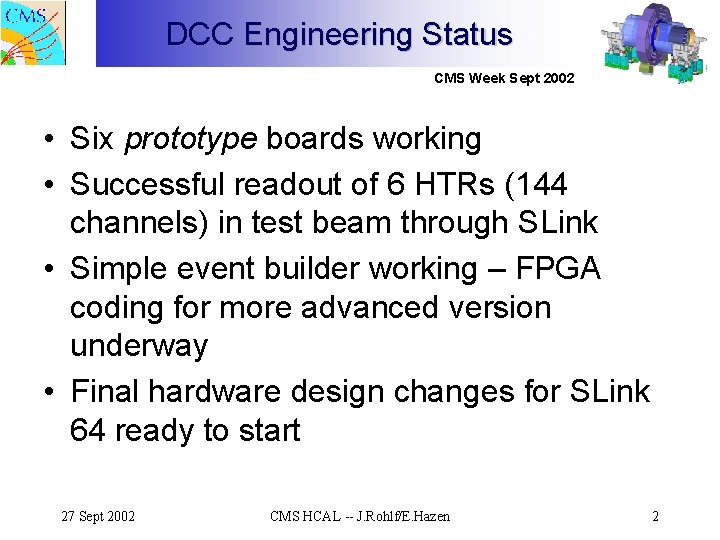

DCC Engineering Status CMS Week Sept 2002 • Six prototype boards working • Successful readout of 6 HTRs (144 channels) in test beam through SLink • Simple event builder working – FPGA coding for more advanced version underway • Final hardware design changes for SLink 64 ready to start 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 2

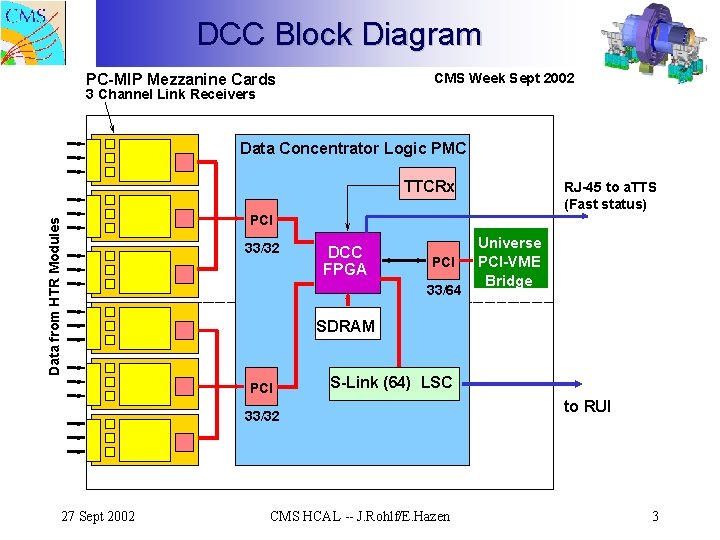

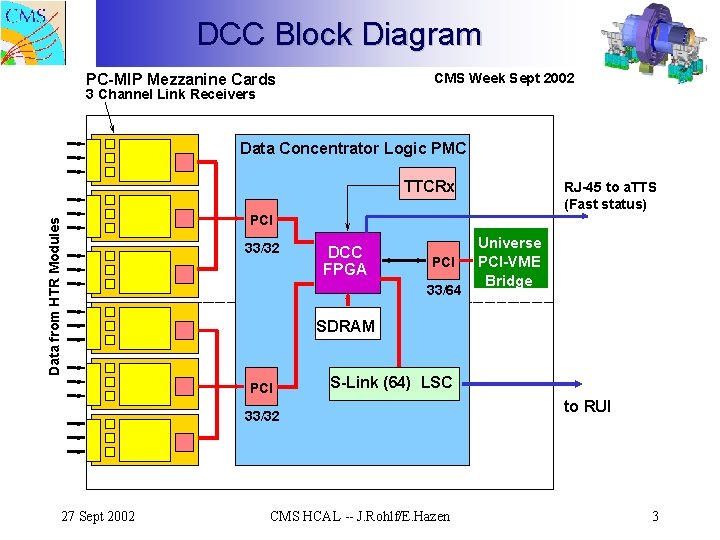

DCC Block Diagram CMS Week Sept 2002 PC-MIP Mezzanine Cards 3 Channel Link Receivers Data Concentrator Logic PMC Data from HTR Modules TTCRx PCI 33/32 DCC FPGA PCI 33/64 Universe PCI-VME Bridge SDRAM PCI S-Link (64) LSC 33/32 27 Sept 2002 RJ-45 to a. TTS (Fast status) CMS HCAL -- J. Rohlf/E. Hazen to RUI 3

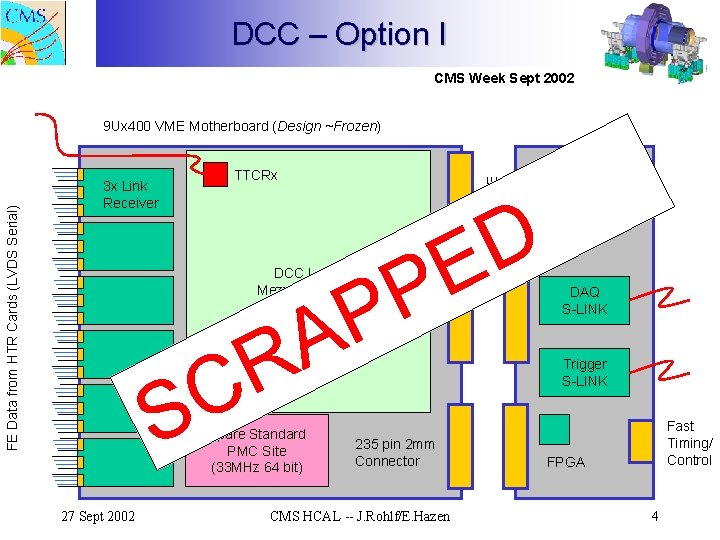

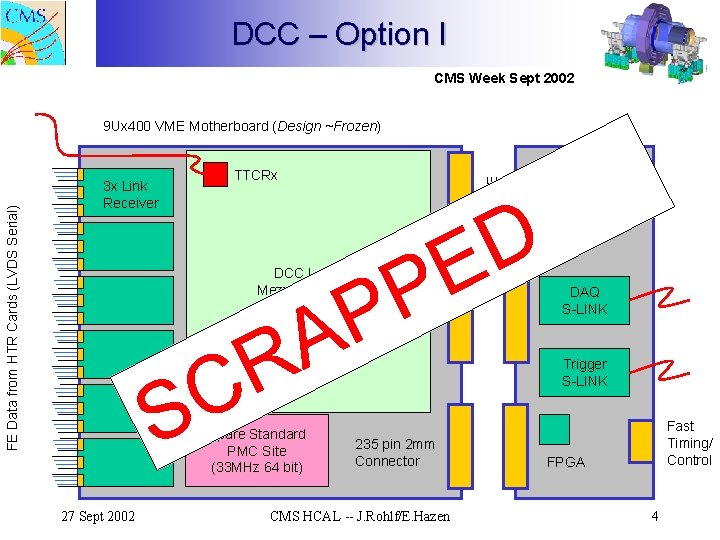

DCC – Option I CMS Week Sept 2002 3 x Link Receiver TTCRx VME FE Data from HTR Cards (LVDS Serial) 9 Ux 400 VME Motherboard (Design ~Frozen) D E P P DCC Logic Mezzanine Card A R C S Spare Standard PMC Site (33 MHz 64 bit) 27 Sept 2002 Proposed Transition Module 235 pin 2 mm Connector CMS HCAL -- J. Rohlf/E. Hazen DAQ S-LINK Trigger S-LINK Fast Timing/ Control FPGA 4

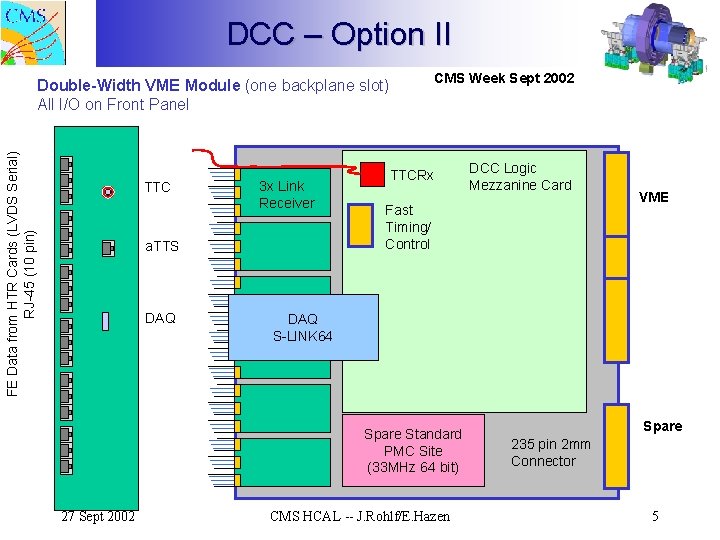

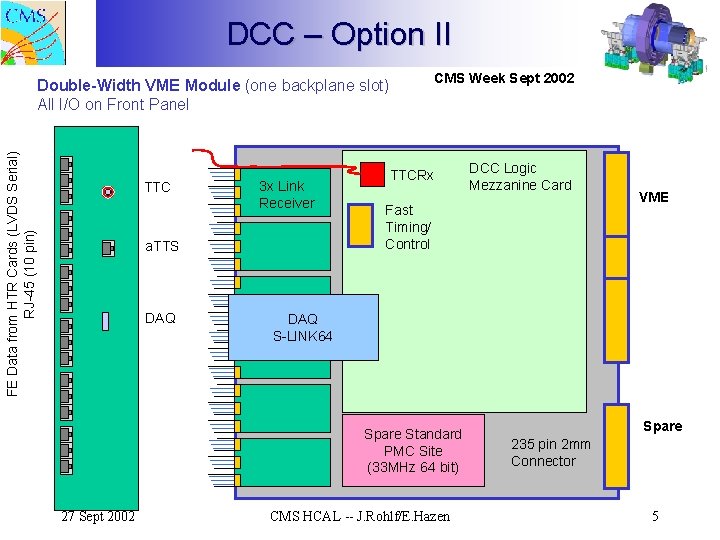

DCC – Option II CMS Week Sept 2002 FE Data from HTR Cards (LVDS Serial) RJ-45 (10 pin) Double-Width VME Module (one backplane slot) All I/O on Front Panel TTC 3 x Link Receiver a. TTS DAQ TTCRx Fast Timing/ Control VME DAQ S-LINK 64 Spare Standard PMC Site (33 MHz 64 bit) 27 Sept 2002 DCC Logic Mezzanine Card CMS HCAL -- J. Rohlf/E. Hazen Spare 235 pin 2 mm Connector 5

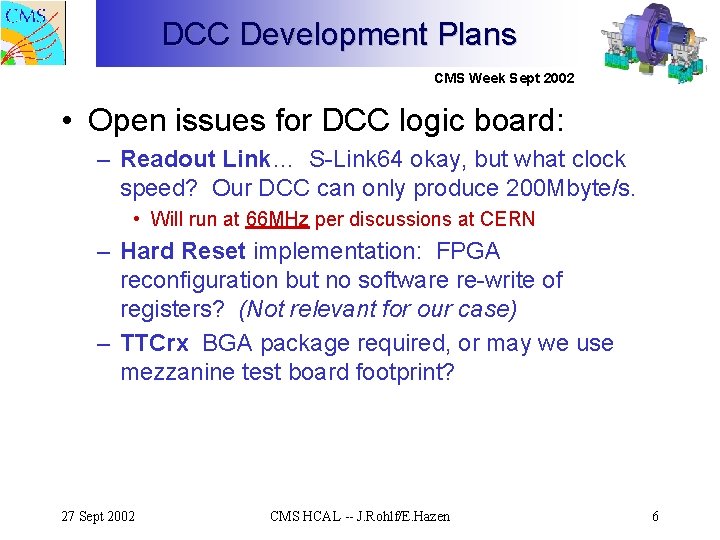

DCC Development Plans CMS Week Sept 2002 • Open issues for DCC logic board: – Readout Link… S-Link 64 okay, but what clock speed? Our DCC can only produce 200 Mbyte/s. • Will run at 66 MHz per discussions at CERN – Hard Reset implementation: FPGA reconfiguration but no software re-write of registers? (Not relevant for our case) – TTCrx BGA package required, or may we use mezzanine test board footprint? 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 6

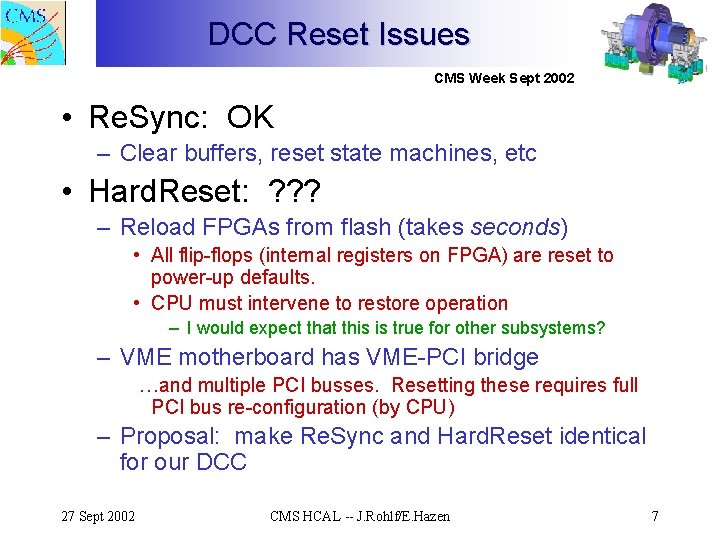

DCC Reset Issues CMS Week Sept 2002 • Re. Sync: OK – Clear buffers, reset state machines, etc • Hard. Reset: ? ? ? – Reload FPGAs from flash (takes seconds) • All flip-flops (internal registers on FPGA) are reset to power-up defaults. • CPU must intervene to restore operation – I would expect that this is true for other subsystems? – VME motherboard has VME-PCI bridge …and multiple PCI busses. Resetting these requires full PCI bus re-configuration (by CPU) – Proposal: make Re. Sync and Hard. Reset identical for our DCC 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 7

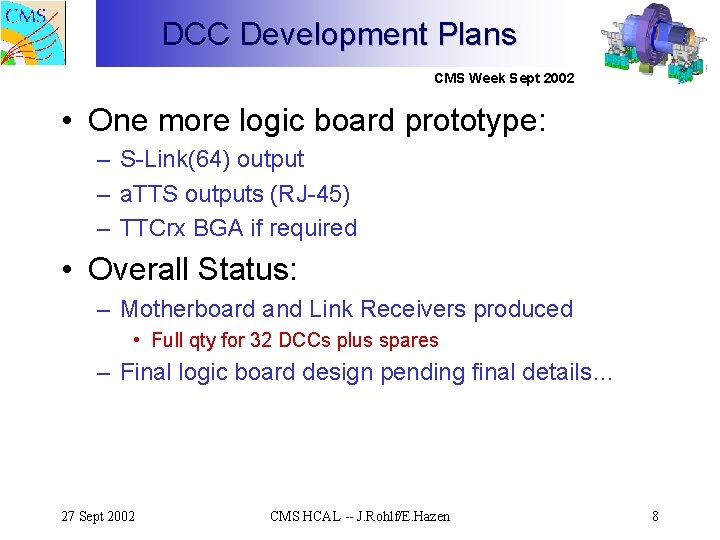

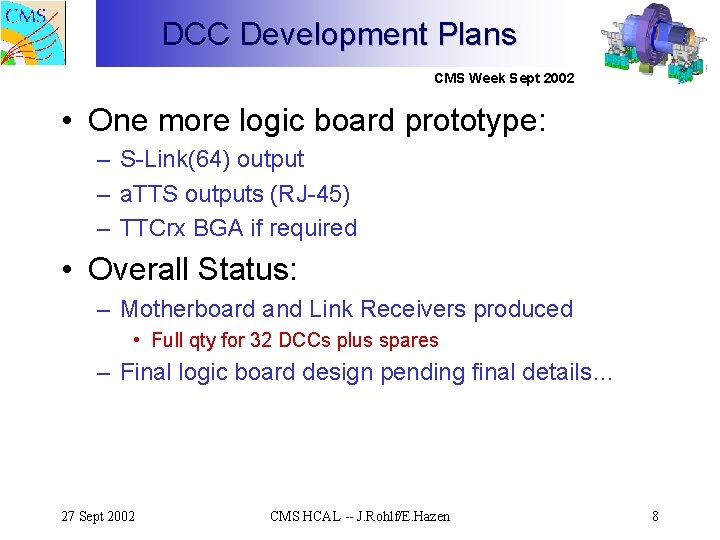

DCC Development Plans CMS Week Sept 2002 • One more logic board prototype: – S-Link(64) output – a. TTS outputs (RJ-45) – TTCrx BGA if required • Overall Status: – Motherboard and Link Receivers produced • Full qty for 32 DCCs plus spares – Final logic board design pending final details… 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 8

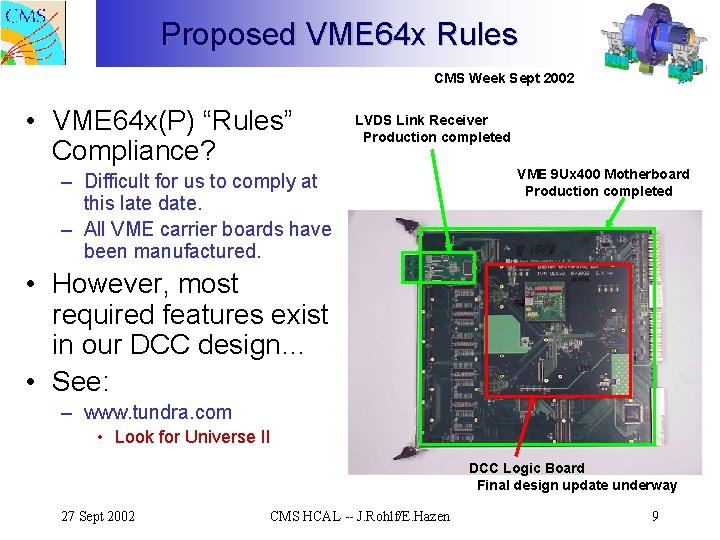

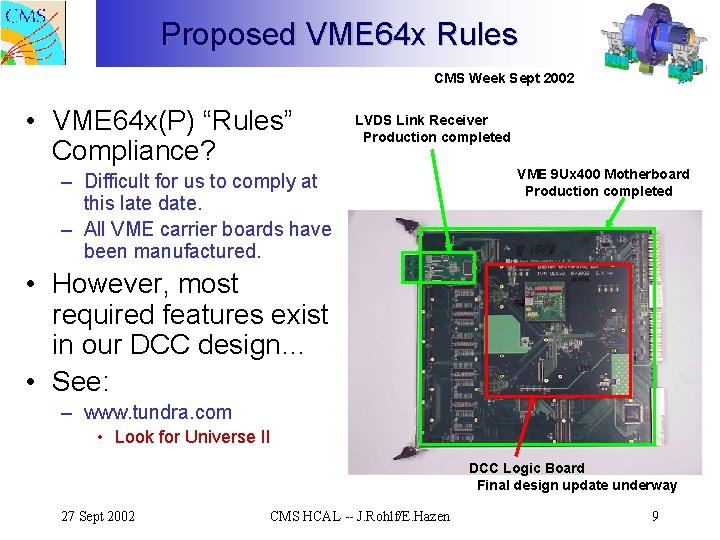

Proposed VME 64 x Rules CMS Week Sept 2002 • VME 64 x(P) “Rules” Compliance? LVDS Link Receiver Production completed – Difficult for us to comply at this late date. – All VME carrier boards have been manufactured. VME 9 Ux 400 Motherboard Production completed • However, most required features exist in our DCC design… • See: – www. tundra. com • Look for Universe II DCC Logic Board Final design update underway 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 9

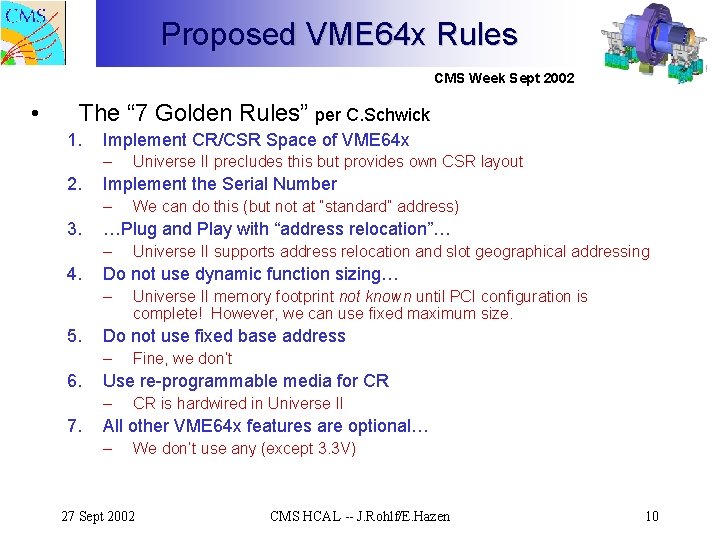

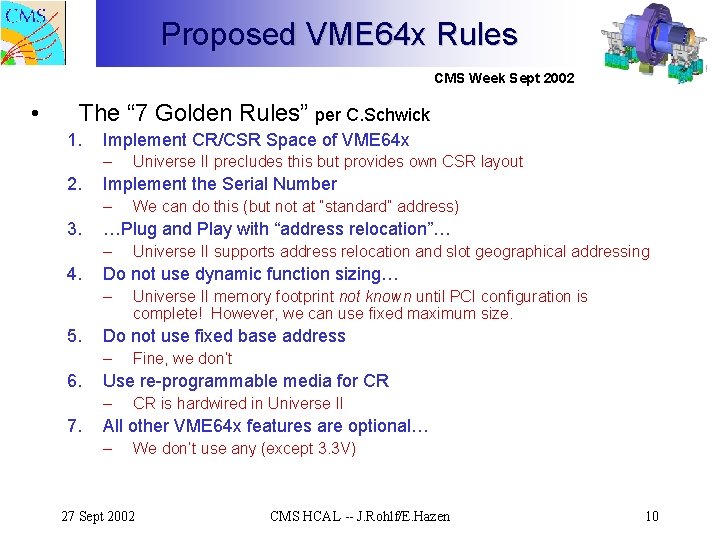

Proposed VME 64 x Rules CMS Week Sept 2002 • The “ 7 Golden Rules” per C. Schwick 1. Implement CR/CSR Space of VME 64 x – 2. Implement the Serial Number – 3. Fine, we don’t Use re-programmable media for CR – 7. Universe II memory footprint not known until PCI configuration is complete! However, we can use fixed maximum size. Do not use fixed base address – 6. Universe II supports address relocation and slot geographical addressing Do not use dynamic function sizing… – 5. We can do this (but not at “standard” address) …Plug and Play with “address relocation”… – 4. Universe II precludes this but provides own CSR layout CR is hardwired in Universe II All other VME 64 x features are optional… – We don’t use any (except 3. 3 V) 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 10

Proposed VME 64 x Rules CMS Week Sept 2002 • HCAL DCC Implementation provides functionality similar to VME 64 x. • Plug-and-play is supported, but requires specific software • It is unfortunate that we cannot comply exactly with the “rules”, but our hardware is already built! 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 11

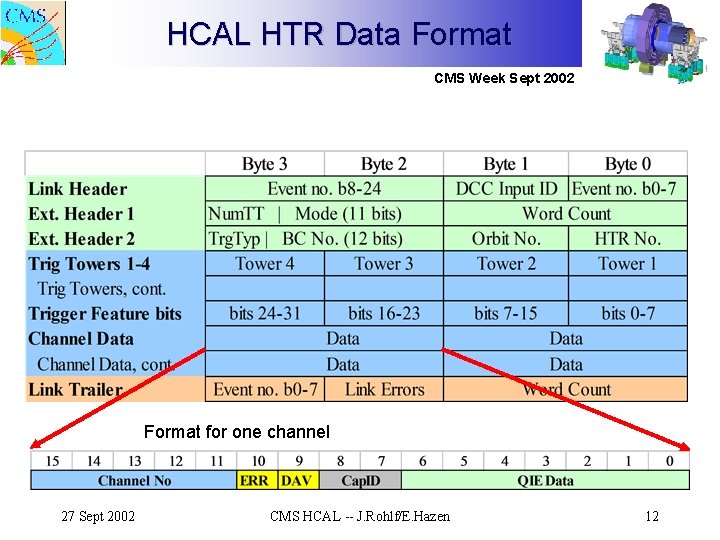

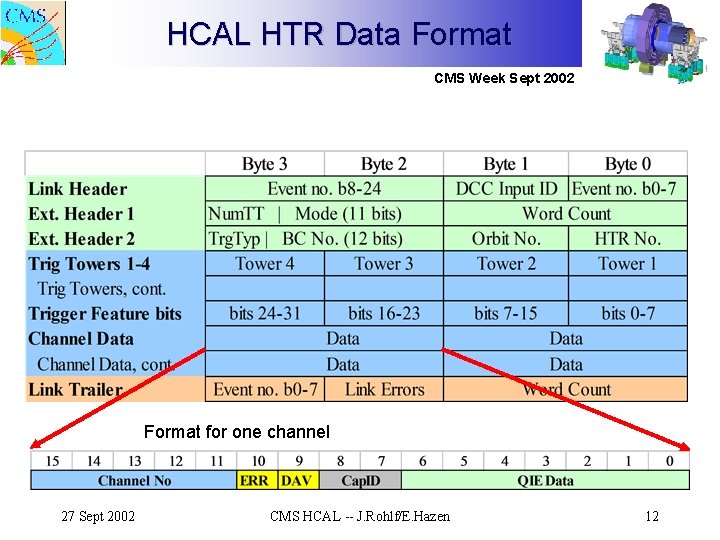

HCAL HTR Data Format CMS Week Sept 2002 Format for one channel 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 12

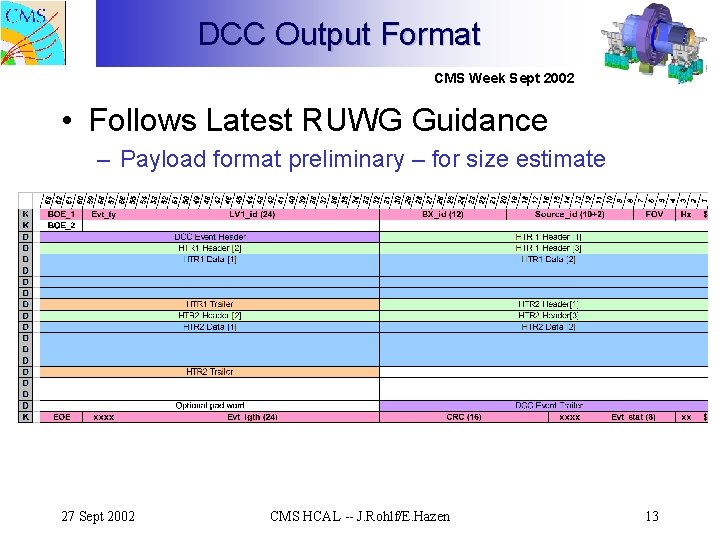

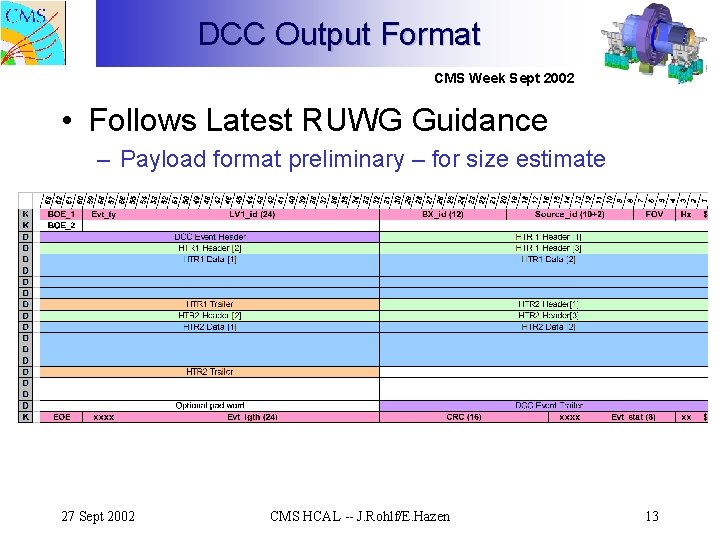

DCC Output Format CMS Week Sept 2002 • Follows Latest RUWG Guidance – Payload format preliminary – for size estimate 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen 13

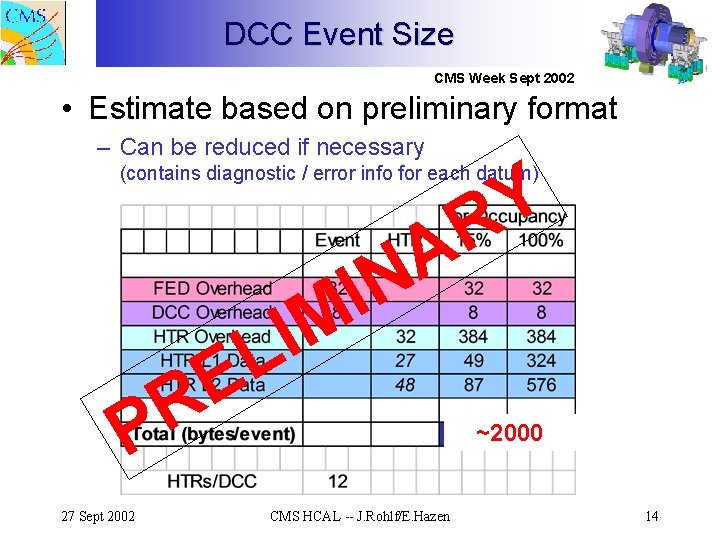

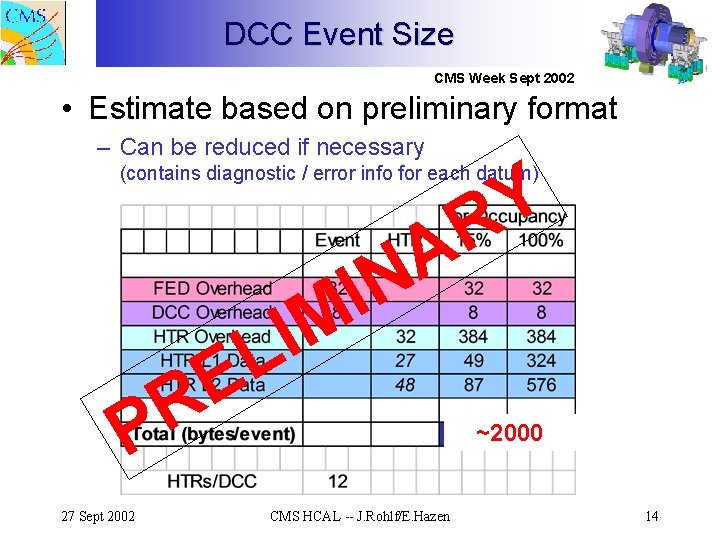

DCC Event Size CMS Week Sept 2002 • Estimate based on preliminary format – Can be reduced if necessary (contains diagnostic / error info for each datum) Y R A N I M I L E R P 27 Sept 2002 CMS HCAL -- J. Rohlf/E. Hazen ~2000 14