CMS Tracker FED CMS Tracker System Meeting Test

- Slides: 12

CMS Tracker FED CMS Tracker System Meeting Test Rob Halsall et al 30 July 2001 CERN Rutherford Appleton Laboratory Instrumentation Department Electronic System Design Group Rob Halsall et al. 30 July 2001

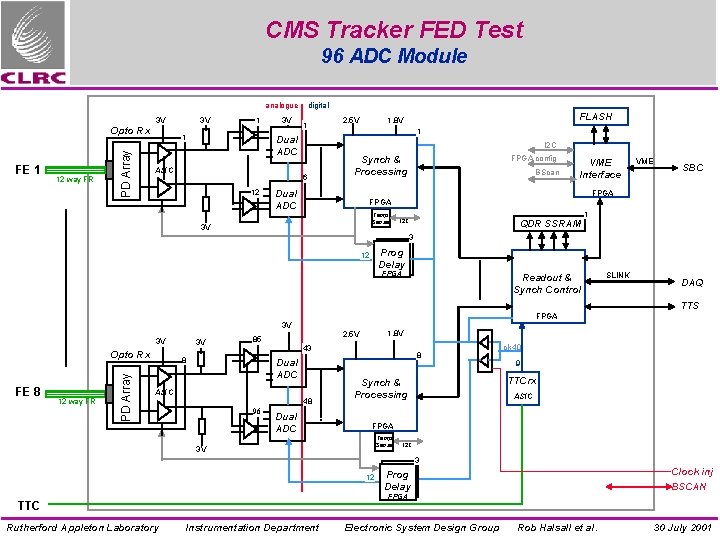

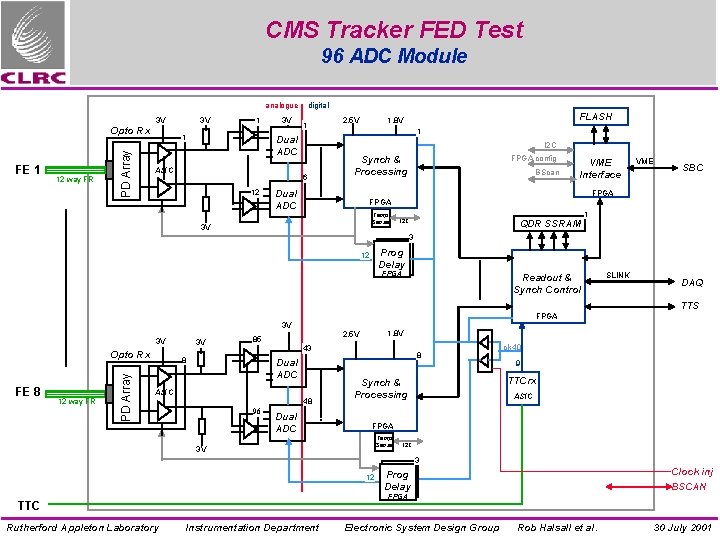

CMS Tracker FED Test 96 ADC Module analogue 3 V FE 1 12 way FR PD Array Opto Rx 3 V 1 1 3 V digital 1 Dual ADC ASIC FLASH 1. 8 V 1 I 2 C 6 12 2. 5 V Synch & Processing Dual ADC FPGA config BScan VME Interface Temp Sense SBC FPGA 3 V VME QDR SSRAM I 2 C 1 3 Prog Delay 12 FPGA Readout & Synch Control SLINK DAQ TTS FPGA 3 V 3 V FE 8 12 way FR PD Array Opto Rx 3 V 1. 8 V 2. 5 V 85 43 8 Dual ADC ASIC 48 96 Dual ADC 8 clk 40 9 TTCrx Synch & Processing ASIC FPGA Temp Sense 3 V I 2 C 3 12 BSCAN FPGA TTC Rutherford Appleton Laboratory Clock inj Prog Delay Instrumentation Department Electronic System Design Group Rob Halsall et al. 30 July 2001

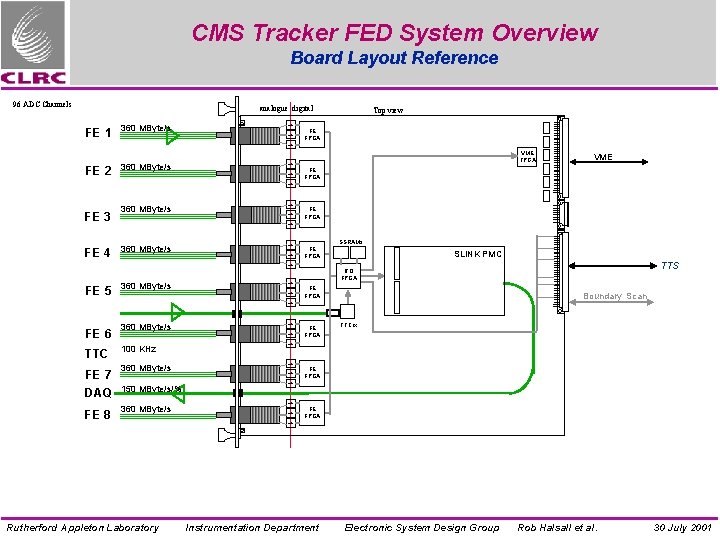

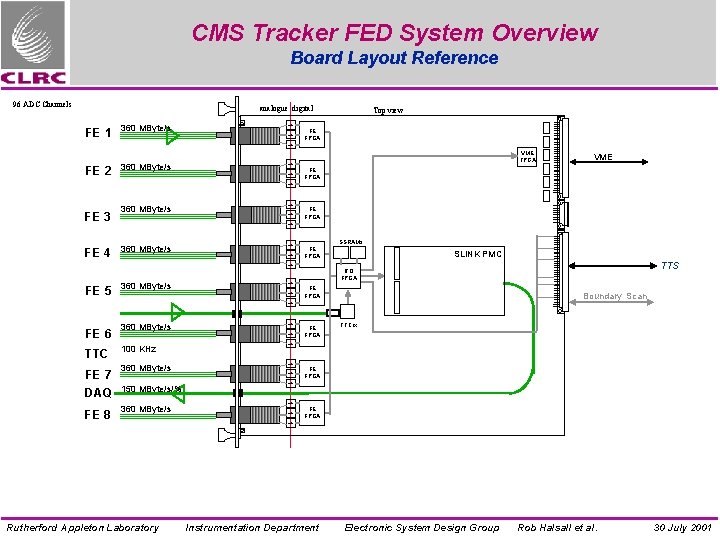

CMS Tracker FED System Overview Board Layout Reference 96 ADC Channels analogue digital FE 1 360 MByte/s Top view adc FE FPGA adc FE 2 360 MByte/s VME FPGA adc VME FE FPGA adc FE 3 FE 4 360 MByte/s adc FE FPGA adc 360 MByte/s adc SSRAMs FE FPGA SLINK PMC TTS adc FE 5 360 MByte/s RO FPGA adc FE FPGA Boundary Scan adc FE 6 TTC FE 7 DAQ FE 8 360 MByte/s adc 100 KHz 360 MByte/s 150 MByte/s/% 360 MByte/s FE FPGA TTCrx adc adc adc FE FPGA adc Rutherford Appleton Laboratory Instrumentation Department Electronic System Design Group Rob Halsall et al. 30 July 2001

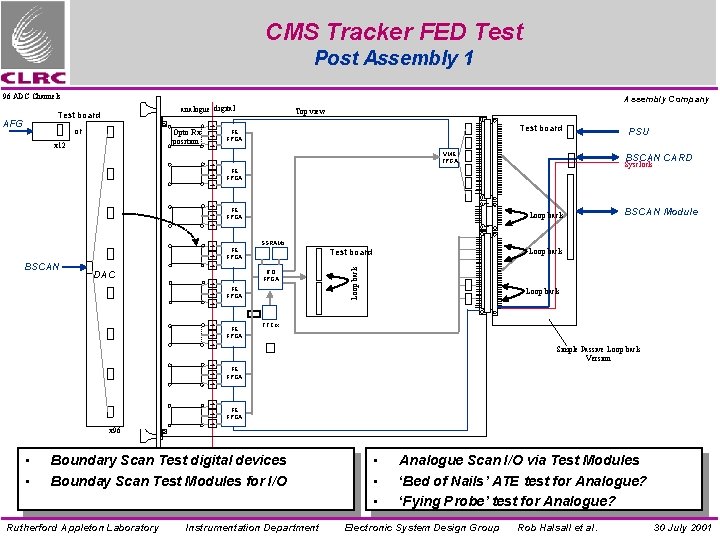

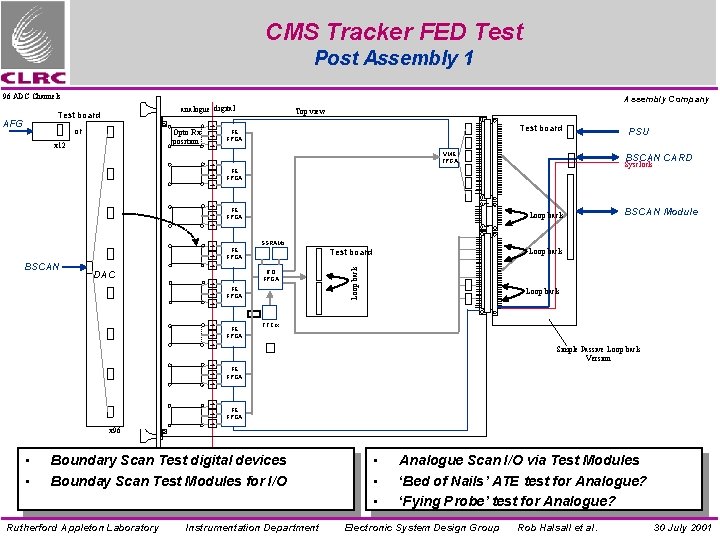

CMS Tracker FED Test Post Assembly 1 96 ADC Channels Test board AFG Assembly Company analogue digital Top view Test board adc or Opto Rx position x 12 adc FE FPGA PSU adc VME FPGA adc BSCAN CARD Sysclock FE FPGA adc adc FE FPGA Loop back BSCAN Module adc BSCAN SSRAMs FE FPGA Test board adc RO FPGA DAC adc FE FPGA Loop back adc adc FE FPGA TTCrx adc adc Simple Passive Loop back Version FE FPGA adc adc FE FPGA adc x 96 • • Boundary Scan Test digital devices Bounday Scan Test Modules for I/O Rutherford Appleton Laboratory Instrumentation Department • • • Analogue Scan I/O via Test Modules ‘Bed of Nails’ ATE test for Analogue? ‘Fying Probe’ test for Analogue? Electronic System Design Group Rob Halsall et al. 30 July 2001

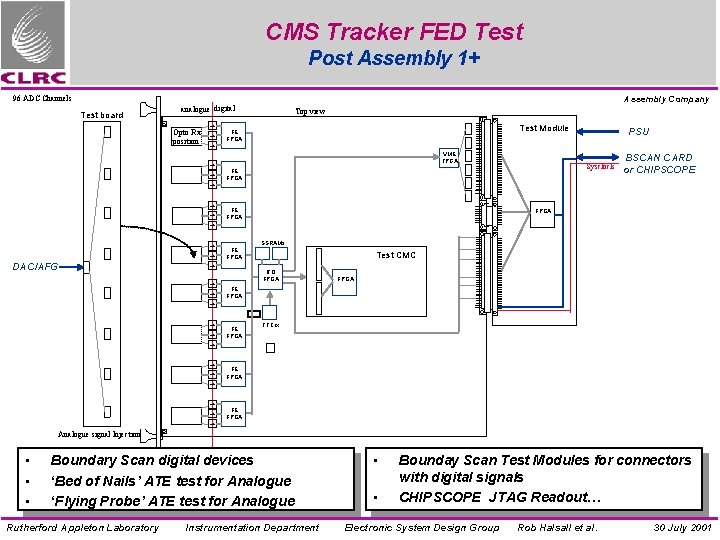

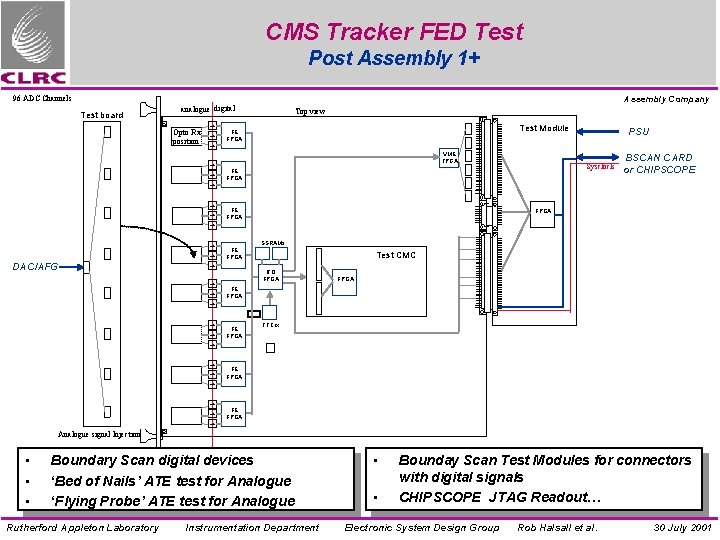

CMS Tracker FED Test Post Assembly 1+ 96 ADC Channels Test board Assembly Company analogue digital Top view Test Module adc Opto Rx position adc FE FPGA PSU adc VME FPGA adc Sysclock FE FPGA BSCAN CARD or CHIPSCOPE adc adc FE FPGA adc adc DAC/AFG SSRAMs FE FPGA Test CMC adc RO FPGA adc FPGA FE FPGA adc adc FE FPGA TTCrx adc adc adc FE FPGA adc Analogue signal Injection • • • Boundary Scan digital devices ‘Bed of Nails’ ATE test for Analogue ‘Flying Probe’ ATE test for Analogue Rutherford Appleton Laboratory Instrumentation Department • • Bounday Scan Test Modules for connectors with digital signals CHIPSCOPE JTAG Readout… Electronic System Design Group Rob Halsall et al. 30 July 2001

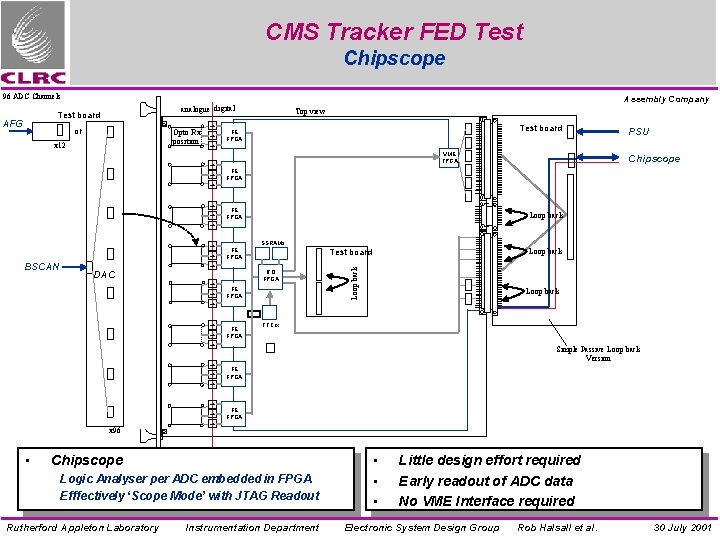

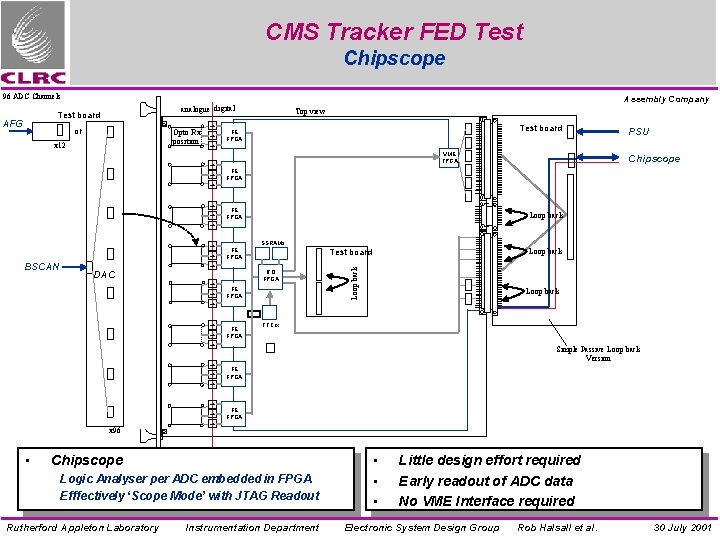

CMS Tracker FED Test Chipscope 96 ADC Channels Test board AFG Assembly Company analogue digital Top view Test board adc or Opto Rx position x 12 adc FE FPGA PSU adc VME FPGA adc Chipscope FE FPGA adc adc FE FPGA Loop back adc BSCAN SSRAMs FE FPGA Test board adc RO FPGA DAC adc FE FPGA Loop back adc adc FE FPGA TTCrx adc adc Simple Passive Loop back Version FE FPGA adc adc FE FPGA adc x 96 • Chipscope Logic Analyser per ADC embedded in FPGA Efffectively ‘Scope Mode’ with JTAG Readout Rutherford Appleton Laboratory Instrumentation Department • • • Little design effort required Early readout of ADC data No VME Interface required Electronic System Design Group Rob Halsall et al. 30 July 2001

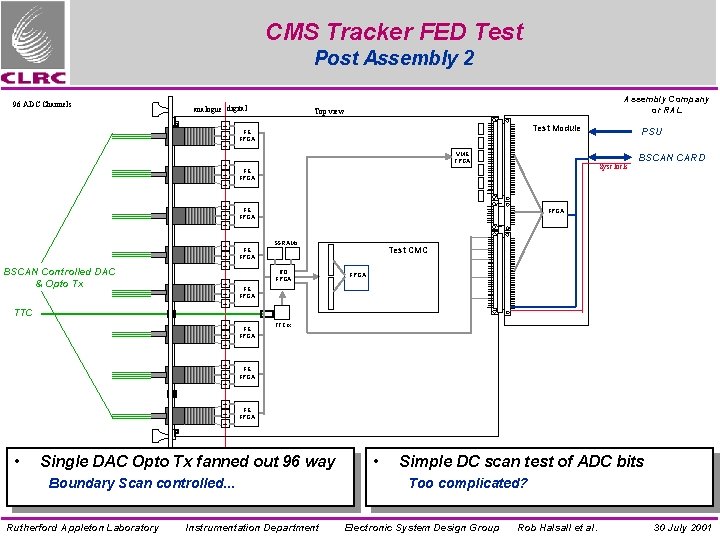

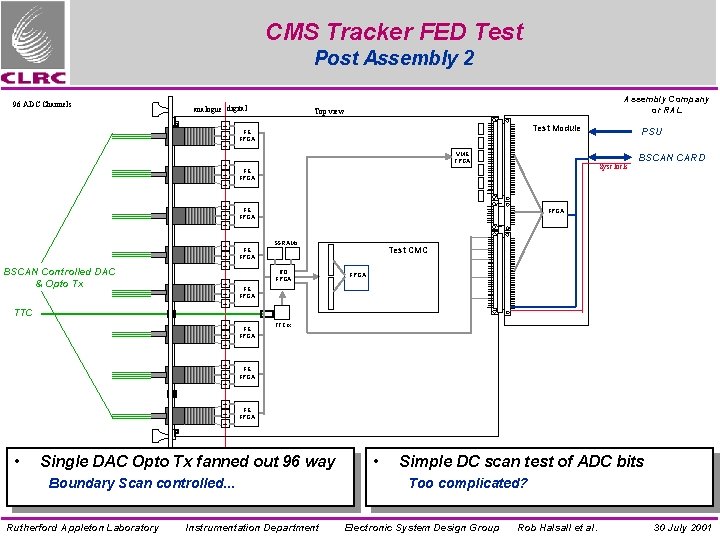

CMS Tracker FED Test Post Assembly 2 96 ADC Channels analogue digital Assembly Company or RAL Top view Test Module adc FE FPGA PSU adc VME FPGA adc Sysclock FE FPGA BSCAN CARD adc adc FE FPGA adc adc BSCAN Controlled DAC & Opto Tx SSRAMs Test CMC FE FPGA adc RO FPGA adc FPGA FE FPGA adc TTC adc FE FPGA TTCrx adc adc adc FE FPGA adc • Single DAC Opto Tx fanned out 96 way Boundary Scan controlled. . . Rutherford Appleton Laboratory Instrumentation Department • Simple DC scan test of ADC bits Too complicated? Electronic System Design Group Rob Halsall et al. 30 July 2001

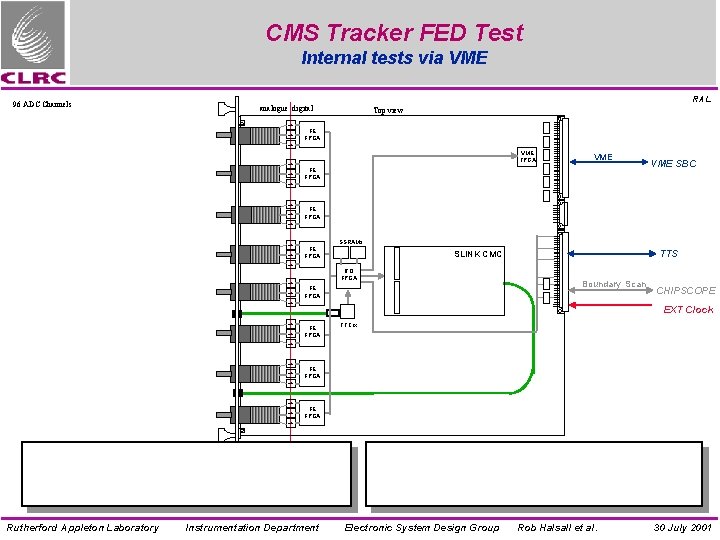

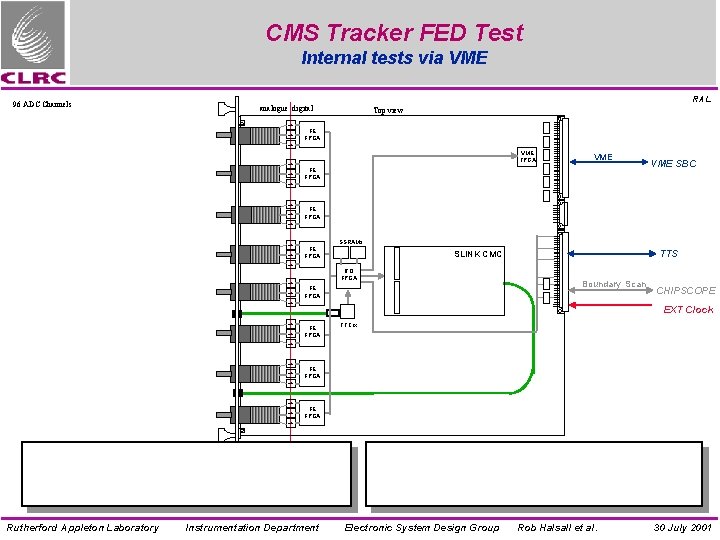

CMS Tracker FED Test Internal tests via VME 96 ADC Channels RAL analogue digital Top view adc FE FPGA adc VME FE FPGA VME SBC adc adc FE FPGA adc adc SSRAMs FE FPGA TTS SLINK CMC adc RO FPGA adc FE FPGA Boundary Scan adc adc CHIPSCOPE EXT Clock FE FPGA TTCrx adc adc adc FE FPGA adc Rutherford Appleton Laboratory Instrumentation Department Electronic System Design Group Rob Halsall et al. 30 July 2001

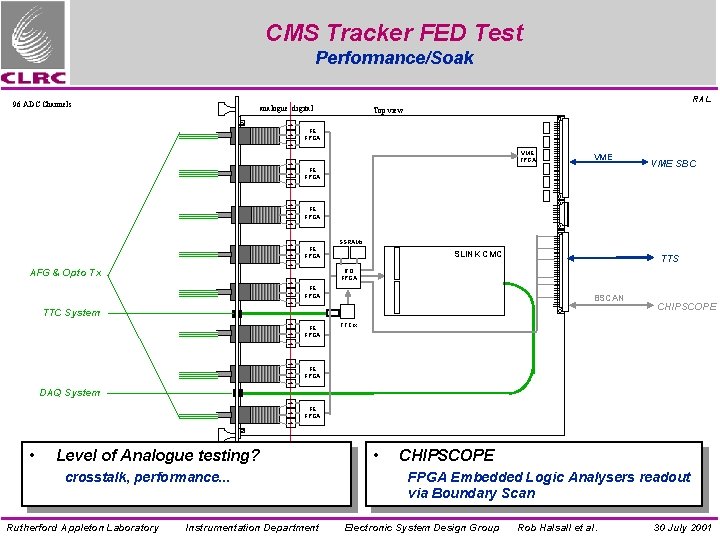

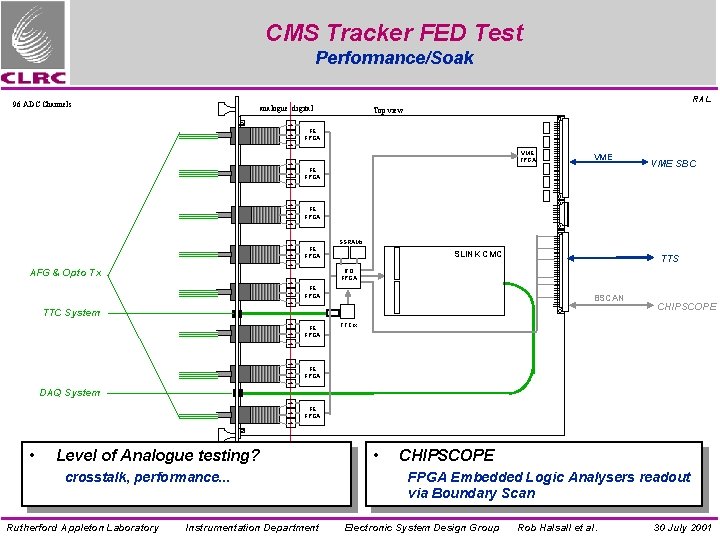

CMS Tracker FED Test Performance/Soak 96 ADC Channels RAL analogue digital Top view adc FE FPGA adc VME FE FPGA VME SBC adc adc FE FPGA adc adc SSRAMs FE FPGA SLINK CMC TTS adc AFG & Opto Tx RO FPGA adc FE FPGA BSCAN adc TTC System adc FE FPGA CHIPSCOPE TTCrx adc adc FE FPGA adc DAQ System adc FE FPGA adc • Level of Analogue testing? crosstalk, performance. . . Rutherford Appleton Laboratory Instrumentation Department • CHIPSCOPE FPGA Embedded Logic Analysers readout via Boundary Scan Electronic System Design Group Rob Halsall et al. 30 July 2001

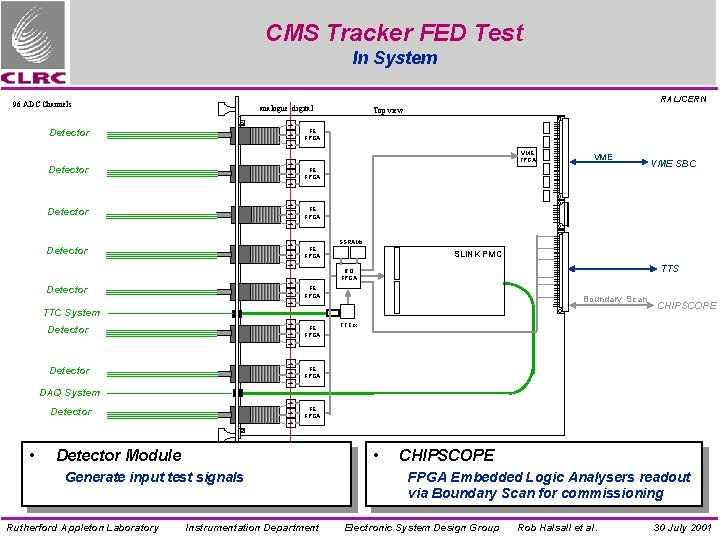

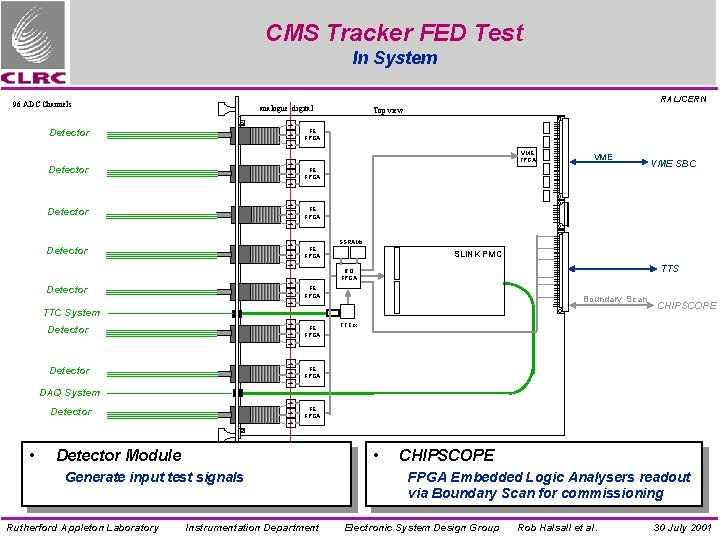

CMS Tracker FED Test In System 96 ADC Channels RAL/CERN analogue digital Top view adc Detector adc FE FPGA adc VME FPGA adc Detector adc VME FE FPGA VME SBC adc Detector adc FE FPGA adc Detector adc SSRAMs FE FPGA SLINK PMC adc Detector adc TTS RO FPGA adc FE FPGA Boundary Scan adc TTC System adc Detector adc FE FPGA CHIPSCOPE TTCrx adc Detector adc FE FPGA adc DAQ System adc Detector adc FE FPGA adc • • Detector Module Generate input test signals Rutherford Appleton Laboratory Instrumentation Department CHIPSCOPE FPGA Embedded Logic Analysers readout via Boundary Scan for commissioning Electronic System Design Group Rob Halsall et al. 30 July 2001

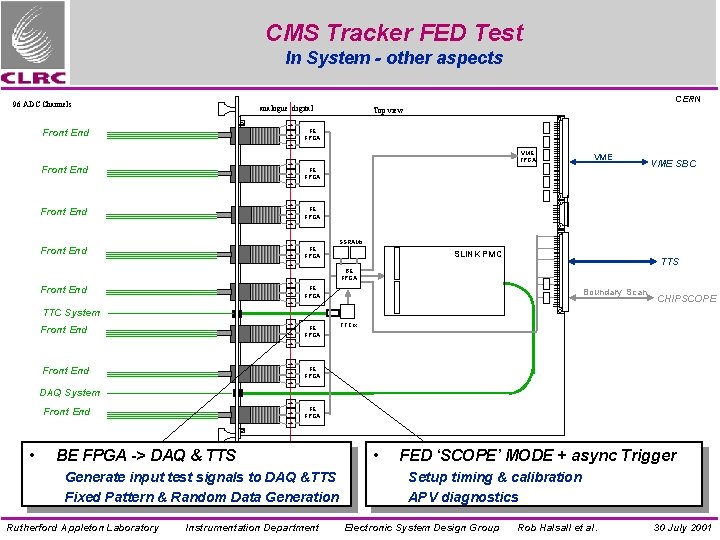

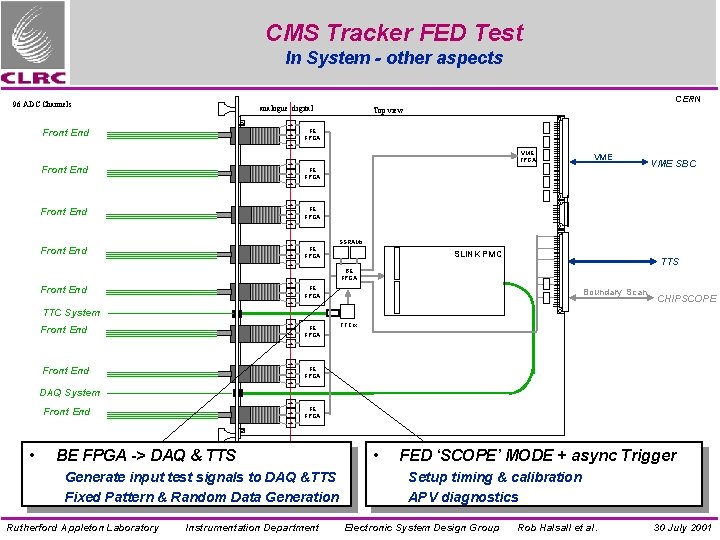

CMS Tracker FED Test In System - other aspects 96 ADC Channels CERN analogue digital Top view adc Front End adc FE FPGA adc VME FPGA adc Front End adc VME FE FPGA VME SBC adc Front End adc FE FPGA adc Front End adc SSRAMs FE FPGA SLINK PMC TTS adc BE FPGA adc Front End adc FE FPGA Boundary Scan adc CHIPSCOPE TTC System adc Front End adc FE FPGA TTCrx adc Front End adc FE FPGA adc DAQ System adc Front End adc FE FPGA adc • BE FPGA -> DAQ & TTS Generate input test signals to DAQ &TTS Fixed Pattern & Random Data Generation Rutherford Appleton Laboratory Instrumentation Department • FED ‘SCOPE’ MODE + async Trigger Setup timing & calibration APV diagnostics Electronic System Design Group Rob Halsall et al. 30 July 2001

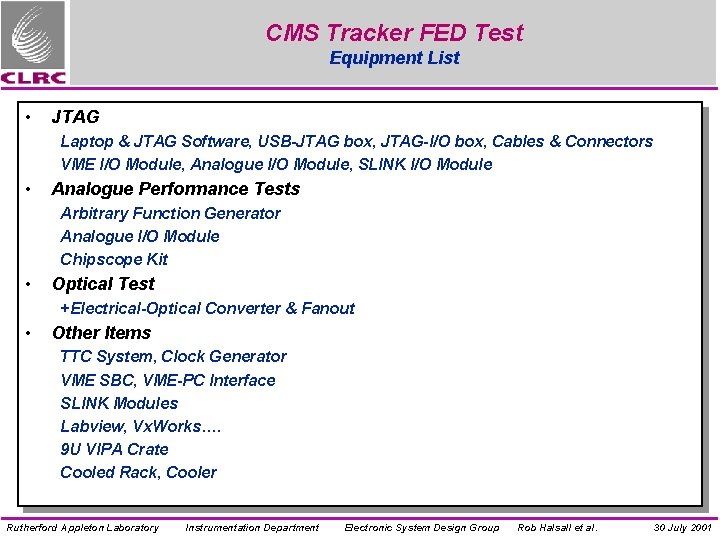

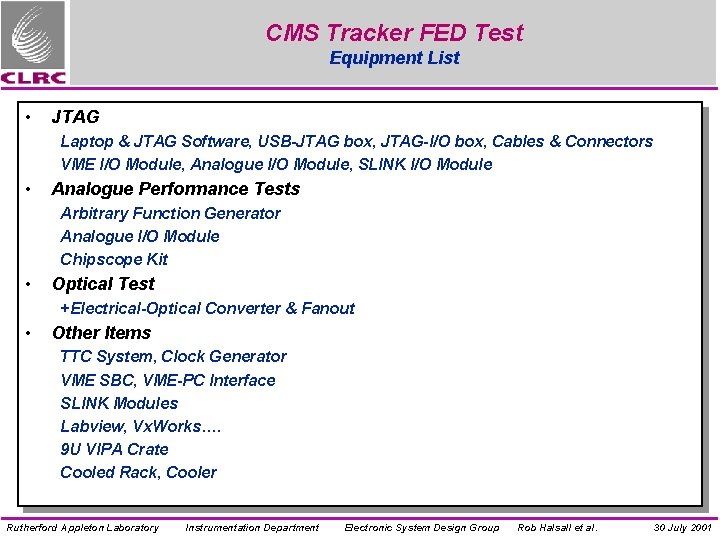

CMS Tracker FED Test Equipment List • JTAG Laptop & JTAG Software, USB-JTAG box, JTAG-I/O box, Cables & Connectors VME I/O Module, Analogue I/O Module, SLINK I/O Module • Analogue Performance Tests Arbitrary Function Generator Analogue I/O Module Chipscope Kit • Optical Test +Electrical-Optical Converter & Fanout • Other Items TTC System, Clock Generator VME SBC, VME-PC Interface SLINK Modules Labview, Vx. Works…. 9 U VIPA Crate Cooled Rack, Cooler Rutherford Appleton Laboratory Instrumentation Department Electronic System Design Group Rob Halsall et al. 30 July 2001