CMOS A Low Voltage Low Noise CMOS Active

![與現有技術比較 parameter This work [A] [B] Darabi, H X. Wang Frequency(GHz) 2. 01 2 與現有技術比較 parameter This work [A] [B] Darabi, H X. Wang Frequency(GHz) 2. 01 2](https://slidetodoc.com/presentation_image_h2/ac8d790e691e7d56a1f040a87a3721be/image-17.jpg)

- Slides: 24

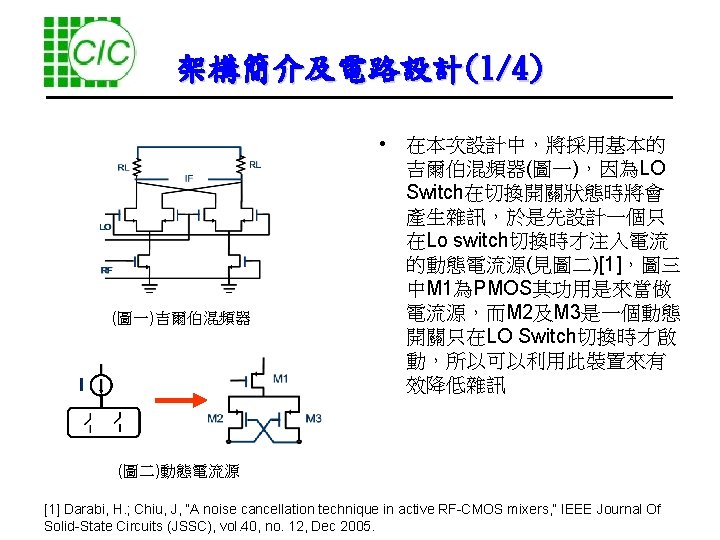

應用於低中頻系統的低電壓、低雜訊、CMOS主動混頻器 A Low Voltage Low Noise CMOS Active Mixer for Low IF System Process: U 18 -95 A FTP No. : 23 Date: 2006/02/18

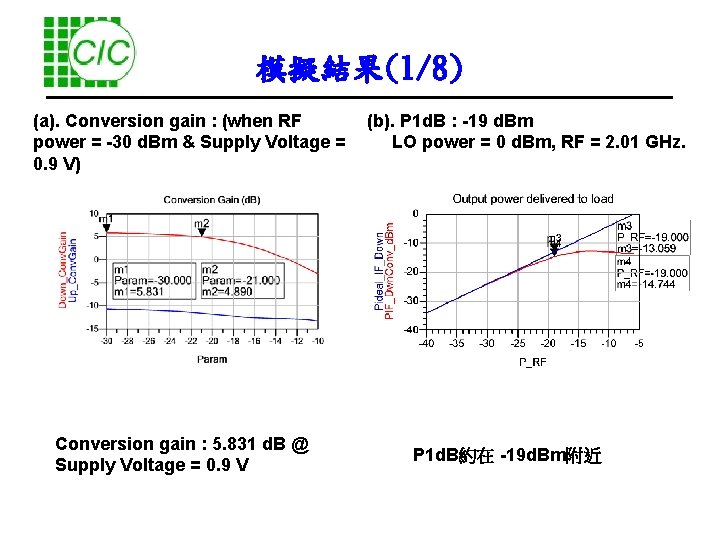

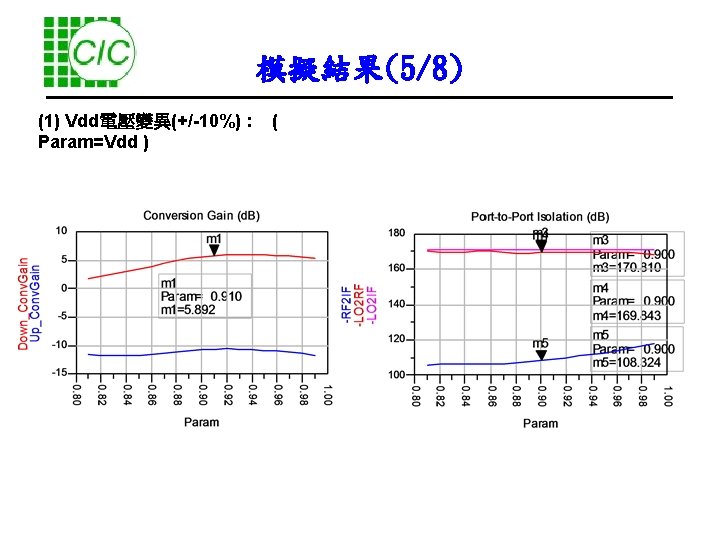

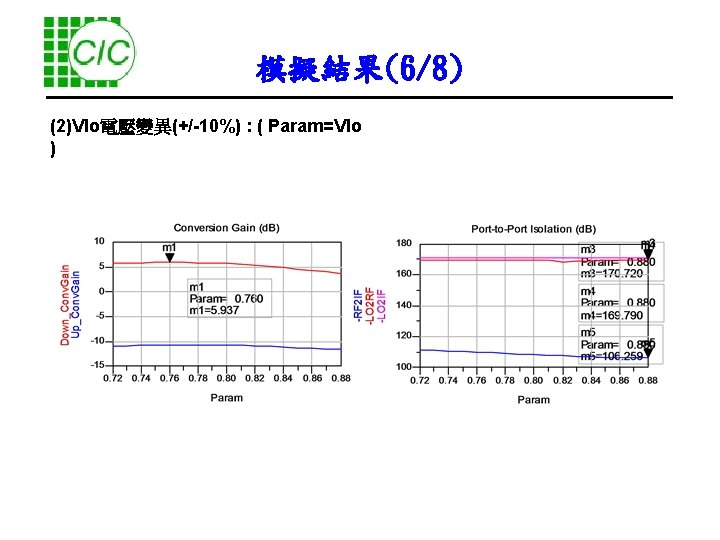

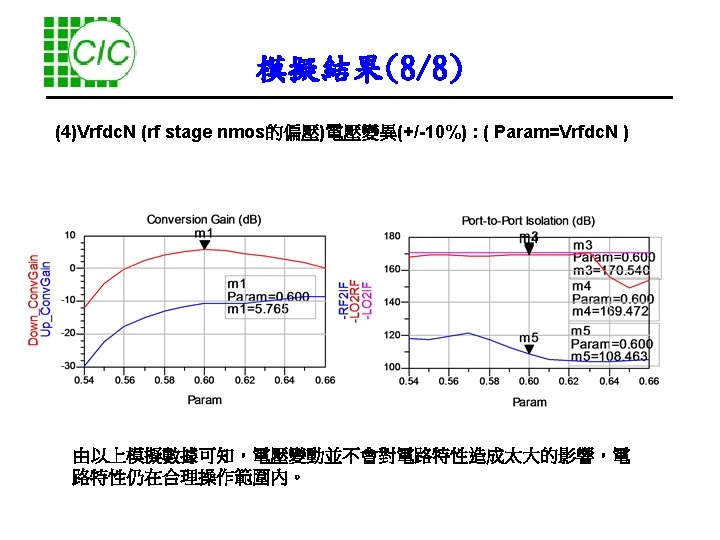

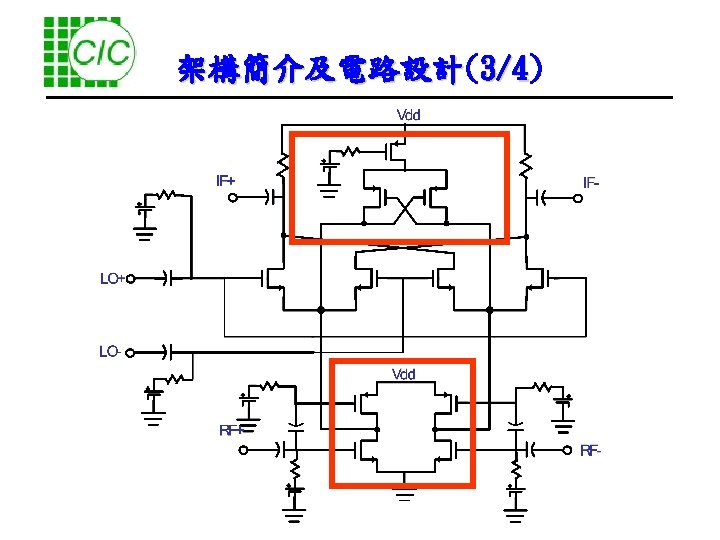

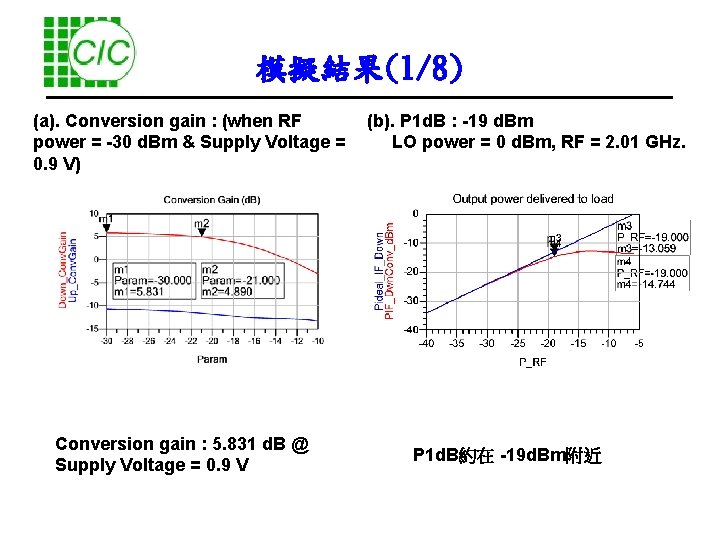

模擬結果(1/8) (a). Conversion gain : (when RF power = -30 d. Bm & Supply Voltage = 0. 9 V) Conversion gain : 5. 831 d. B @ Supply Voltage = 0. 9 V (b). P 1 d. B : -19 d. Bm LO power = 0 d. Bm, RF = 2. 01 GHz. P 1 d. B約在 -19 d. Bm附近

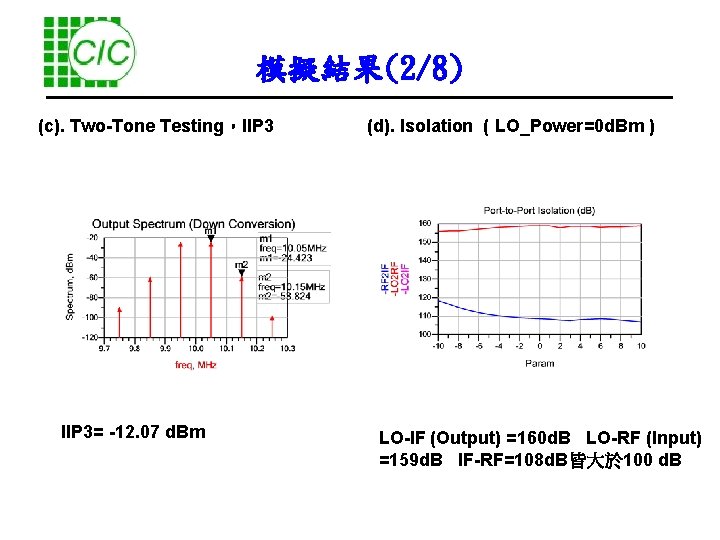

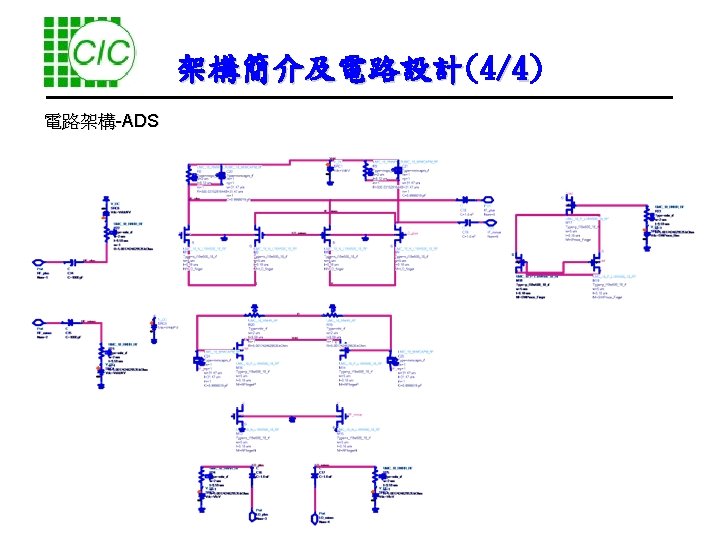

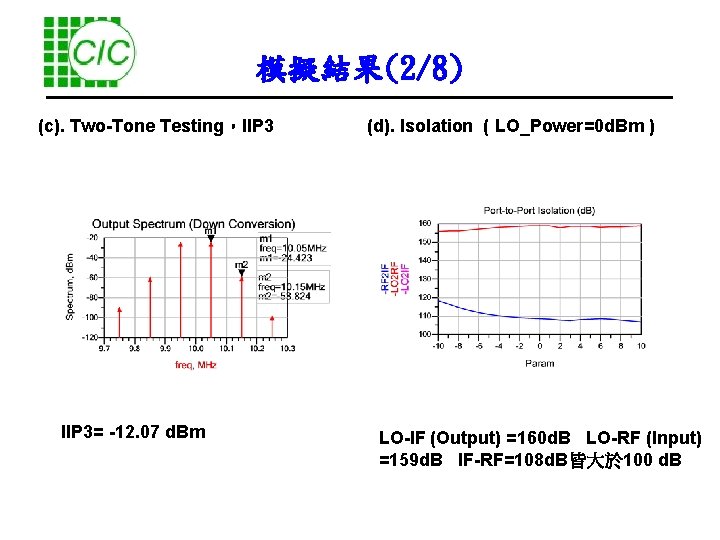

模擬結果(2/8) (c). Two-Tone Testing,IIP 3= -12. 07 d. Bm (d). Isolation ( LO_Power=0 d. Bm ) LO-IF (Output) =160 d. B LO-RF (Input) =159 d. B IF-RF=108 d. B皆大於 100 d. B

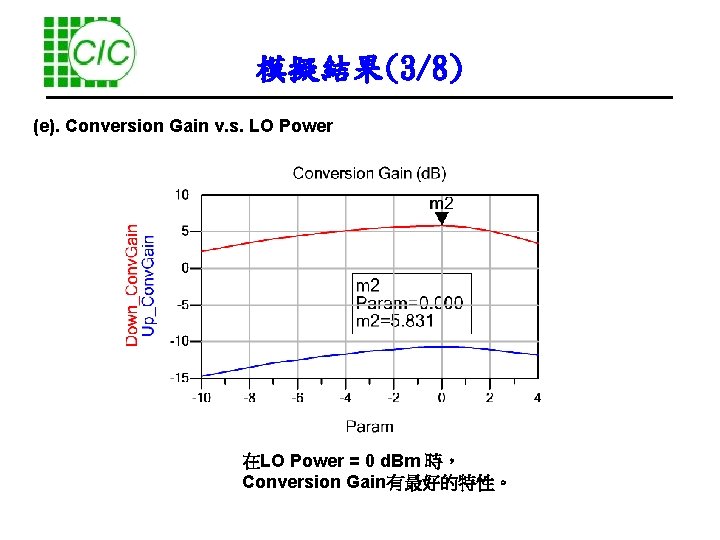

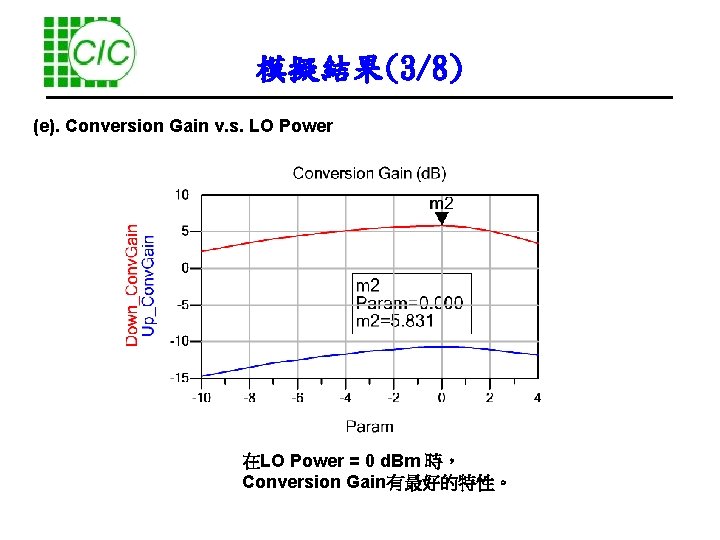

模擬結果(3/8) (e). Conversion Gain v. s. LO Power 在LO Power = 0 d. Bm 時, Conversion Gain有最好的特性。

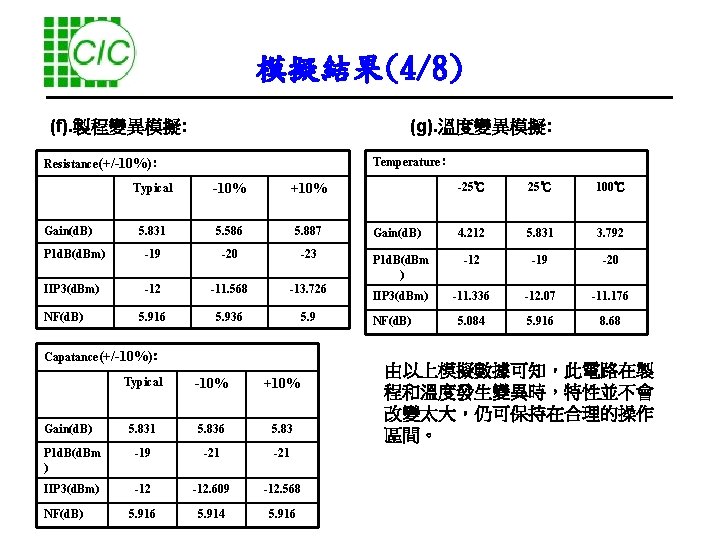

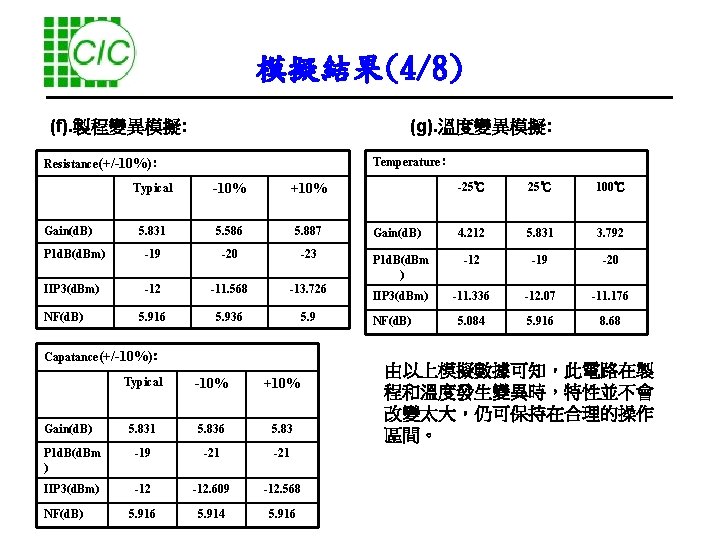

模擬結果(4/8) (f). 製程變異模擬: (g). 溫度變異模擬: Temperature﹕ Resistance(+/-10%)﹕ Typical -10% +10% 5. 831 5. 586 5. 887 P 1 d. B(d. Bm) -19 -20 -23 IIP 3(d. Bm) -12 -11. 568 -13. 726 5. 916 5. 936 5. 9 Gain(d. B) NF(d. B) Capatance(+/-10%)﹕ Typical -10% +10% 5. 831 5. 836 5. 83 P 1 d. B(d. Bm ) -19 -21 IIP 3(d. Bm) -12. 609 -12. 568 5. 916 5. 914 5. 916 Gain(d. B) NF(d. B) -25℃ 100℃ 4. 212 5. 831 3. 792 P 1 d. B(d. Bm ) -12 -19 -20 IIP 3(d. Bm) -11. 336 -12. 07 -11. 176 5. 084 5. 916 8. 68 Gain(d. B) NF(d. B) 由以上模擬數據可知,此電路在製 程和溫度發生變異時,特性並不會 改變太大,仍可保持在合理的操作 區間。

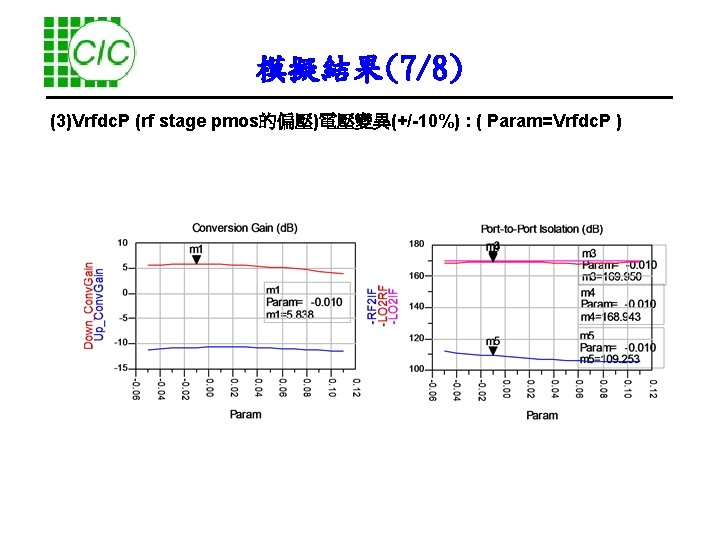

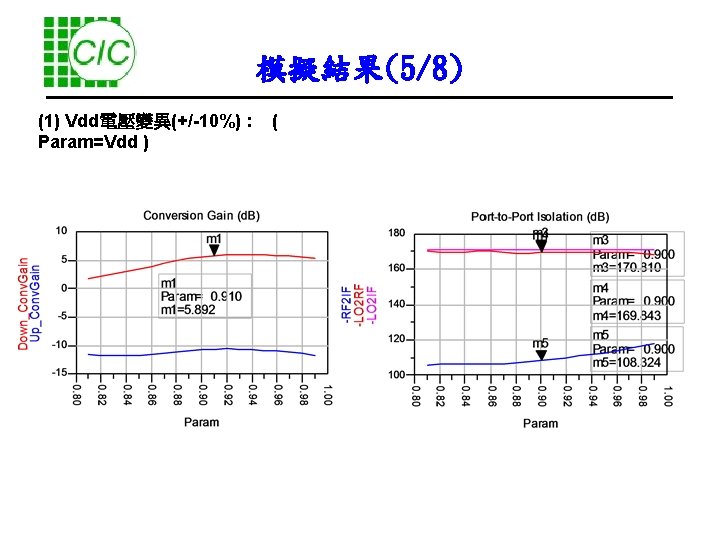

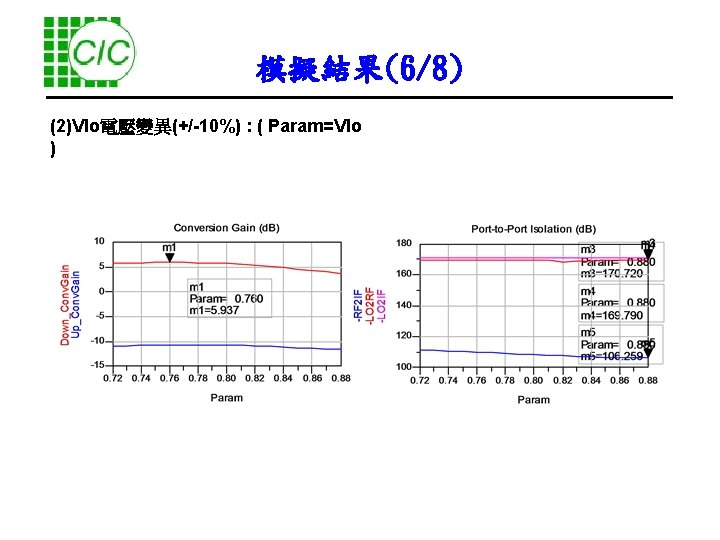

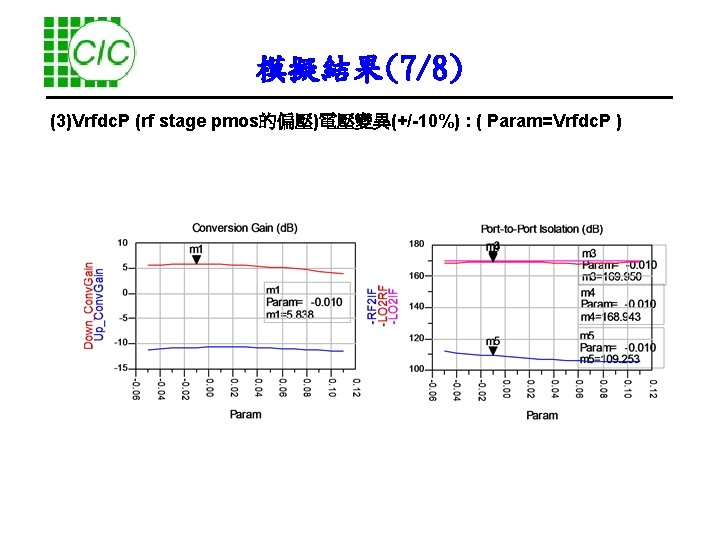

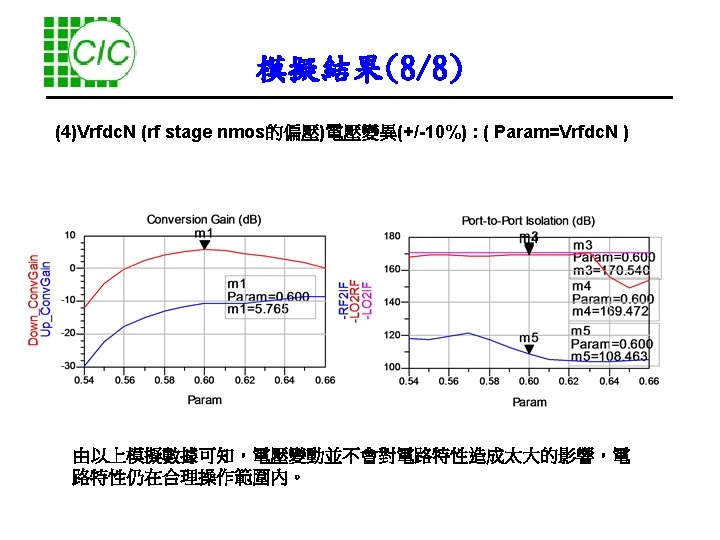

模擬結果(7/8) (3)Vrfdc. P (rf stage pmos的偏壓)電壓變異(+/-10%) : ( Param=Vrfdc. P )

![與現有技術比較 parameter This work A B Darabi H X Wang FrequencyGHz 2 01 2 與現有技術比較 parameter This work [A] [B] Darabi, H X. Wang Frequency(GHz) 2. 01 2](https://slidetodoc.com/presentation_image_h2/ac8d790e691e7d56a1f040a87a3721be/image-17.jpg)

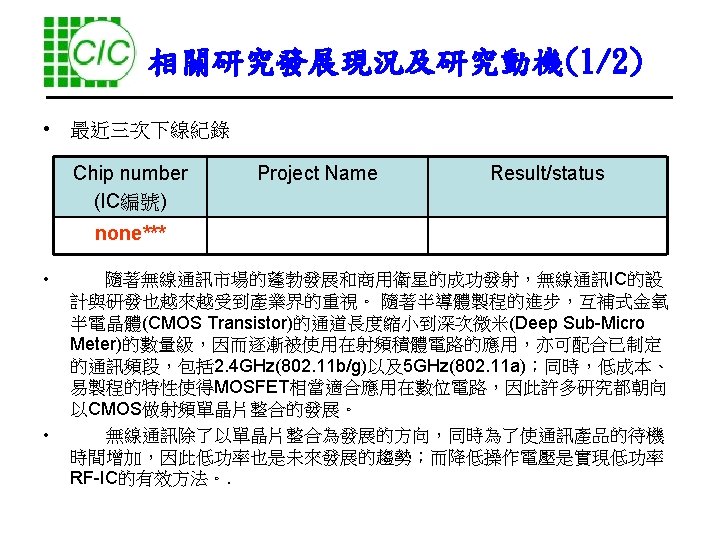

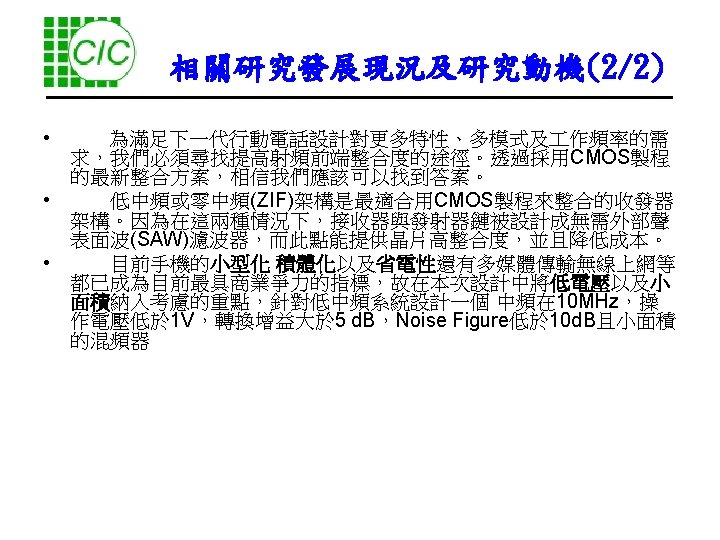

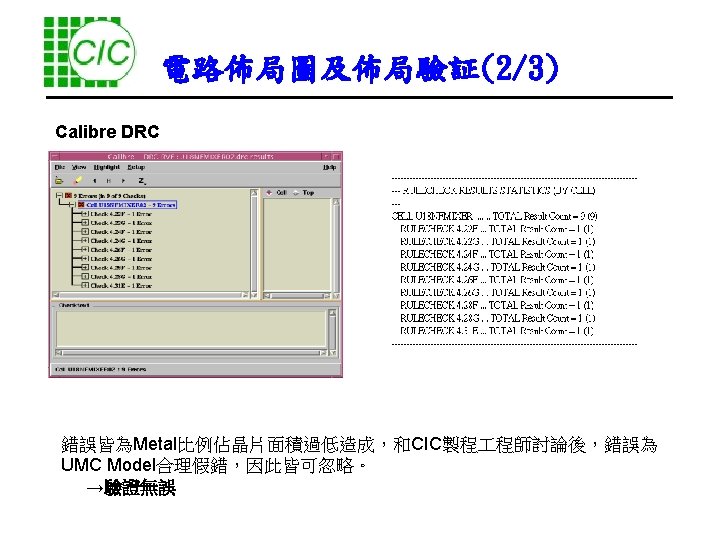

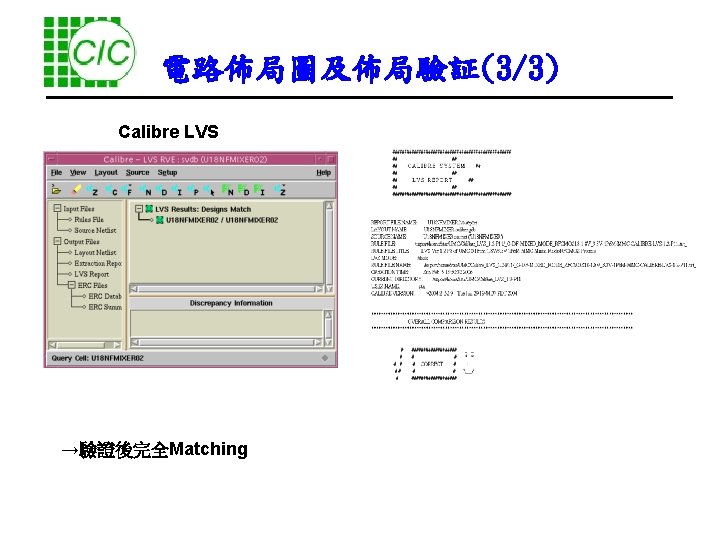

與現有技術比較 parameter This work [A] [B] Darabi, H X. Wang Frequency(GHz) 2. 01 2 5. 8 Voltage(V) 0. 9 1. 2 1. 5 Power consumption (mw) 2. 385 2. 4 6. 89 P 1 d. B(d. Bm) -19 -0. 8 N/A IIP 3(d. Bm) -12. 07 11 -2. 94 Conversion Gain (d. B) 5. 831 1. 26 7 SSB NF(d. B) 5. 916 11. 8 14. 3 Technology Area(mm 2) UMC 0. 18µm CMOS 0. 555× 0. 475 TSMC 0. 13µm CMOS 0. 08× 0. 15 (active area) TSMC 0. 18µm CMOS N/A 本次電路設計重點在於低電壓操作時,電路可以提供增益,並且在不使用電 感的情況下,Noise Figure 仍可有相當好的表現,另外由於沒有使用電感, 整體電路面積大幅降低,面積只有0. 555× 0. 475 (mm 2)

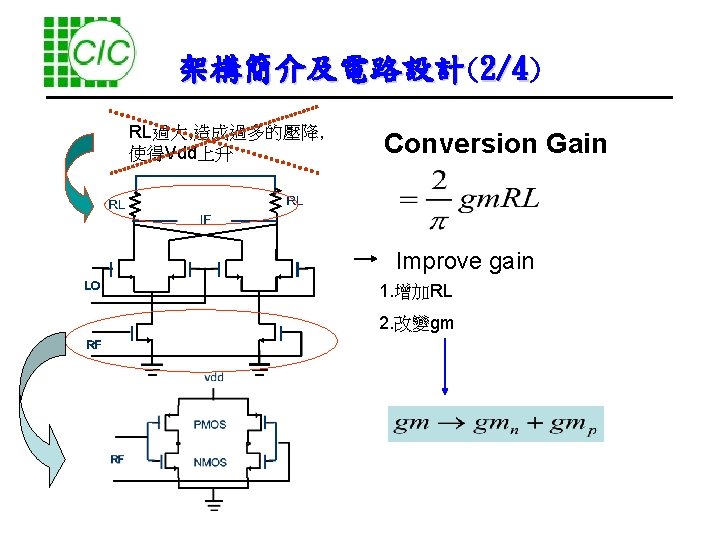

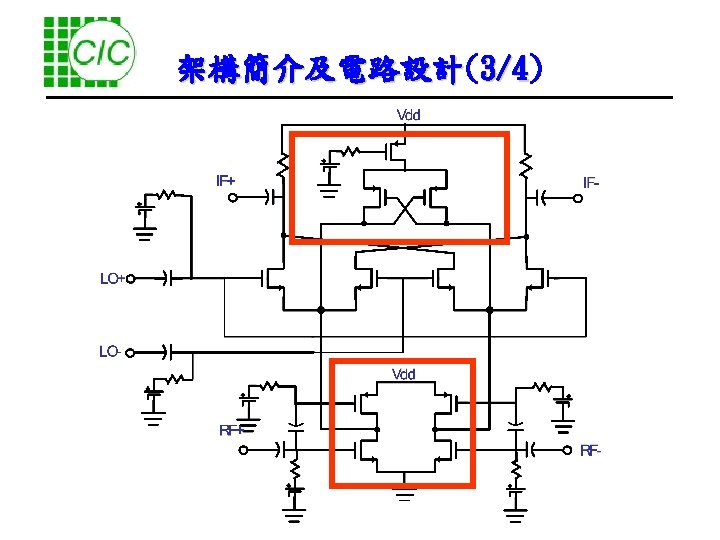

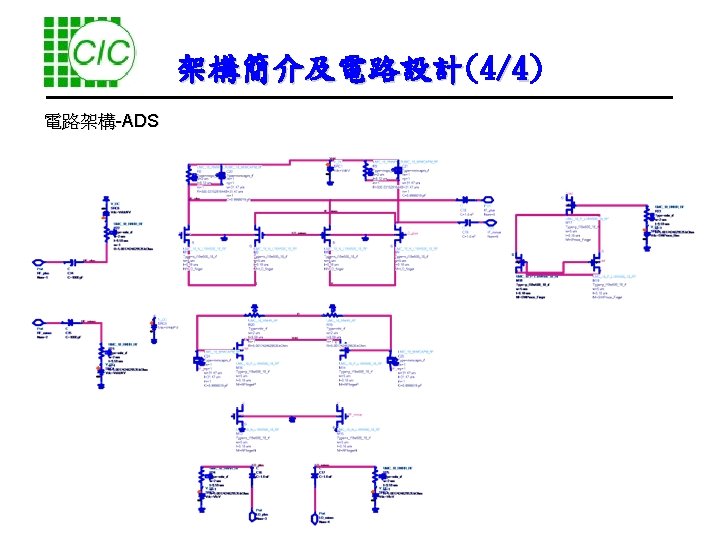

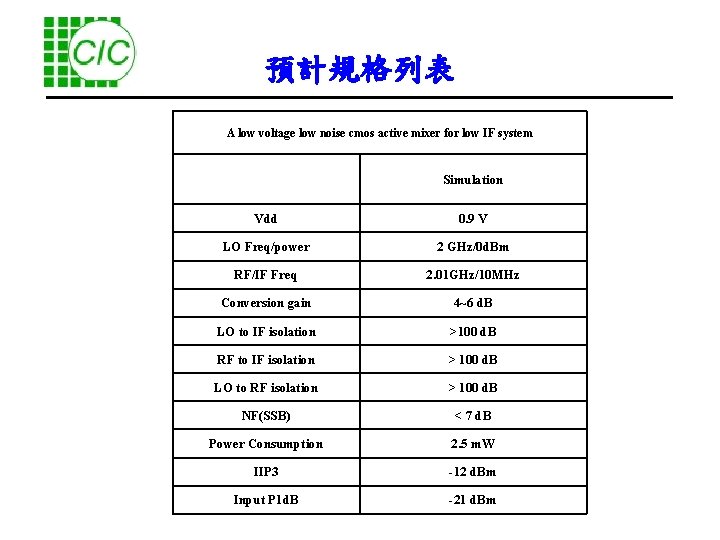

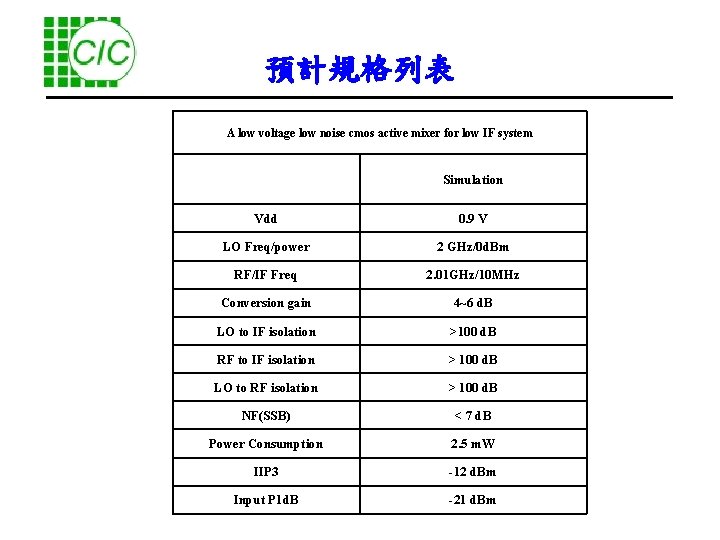

預計規格列表 A low voltage low noise cmos active mixer for low IF system Simulation Vdd 0. 9 V LO Freq/power 2 GHz/0 d. Bm RF/IF Freq 2. 01 GHz/10 MHz Conversion gain 4~6 d. B LO to IF isolation >100 d. B RF to IF isolation > 100 d. B LO to RF isolation > 100 d. B NF(SSB) < 7 d. B Power Consumption 2. 5 m. W IIP 3 -12 d. Bm Input P 1 d. B -21 d. Bm

參考文獻 1. 4. 5. Darabi, H. ; Chiu, J, “A noise cancellation technique in active RFCMOS mixers, ” IEEE Journal Of Solid-State Circuits (JSSC), vol. 40, no. 12, Dec 2005. X. Wang and R. Weber, "A novel low voltage low power 5. 8 GHz CMOS down-conversion mixer design, " IEEE Radio And Wireless Conference (RAWCON), pp. 301– 304, Aug. 2003. P. J. Sullivan, B. A. Xavier, and W. H. Ku, “Low voltage performance of a microwave CMOS Gilbert cell mixer, ” IEEE J. Solid-State Circuits, vol. 32, pp. 1151– 1155, July 1997. Stephen A. Maas, “Microwave Mixer” Stephen A. Maas, “Nonlinear Microwave Circuits” 6. Behzad Razavi, “RF Microelectronics, ” Prentice Hall PTR , 1998 2. 3.