Clockless Logic Review Logic Implementation Styles Static CMOS

- Slides: 5

Clockless Logic Review Logic Implementation Styles: ã Static CMOS logic ã Dynamic logic, or “domino” logic ã Transmission gates, or “pass-transistor” logic 1

Static CMOS logic Advantages: l output always strongly driven Ø pull-up and pull-down networks are fully-complementary; exactly one of them is “on” always Ø good immunity from noise and leakage l both inverting and non-inverting functions implementable Ø each gate is inverting Ø cascade two gates together to get non-inverting logic Disadvantages: l slow/big PMOS devices needed (in addition to NMOS) Ø greater chip area Ø higher power consumption Ø slower switching speed 2

Dynamic Logic, or “domino” Key idea: l only use NMOS’s to compute function l use a single PMOS to reset Advantages: l significantly fewer transistors smaller chip area l higher speed, lower power Ø less “loading” on wires (drive fewer transistors) l for async: no storage elements needed Disadvantages: l need extra control input to precharge l logic is typically non-inverting only l more vulnerable to noise and leakage effects 3

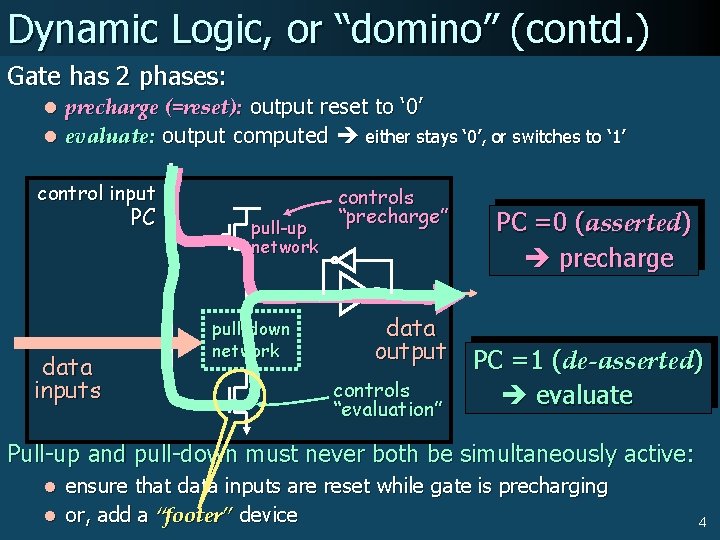

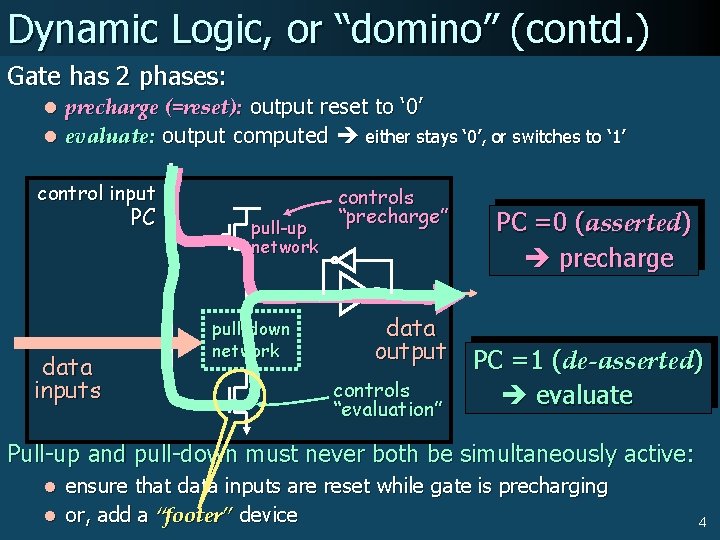

Dynamic Logic, or “domino” (contd. ) Gate has 2 phases: l precharge (=reset): output reset to ‘ 0’ l evaluate: output computed either stays ‘ 0’, or switches to ‘ 1’ control input PC data inputs pull-up network pull-down network controls “precharge” data output controls “evaluation” PC =0 (asserted) precharge PC =1 (de-asserted) evaluate Pull-up and pull-down must never both be simultaneously active: l ensure that data inputs are reset while gate is precharging l or, add a “footer” device 4

Transmission Gates Key Idea: l transistors used in a different configuration l when switched on: instead of connecting output to Vdd or Gnd, they connect output to the input Advantage: l very efficient for implementing switches and multiplexors Disadvantage: l not very useful for logic functions 5