Clock distribution and absolute time calibration in NEMO

Clock distribution and absolute time calibration in NEMO phase 1 Martino Ruppi INFN di Bari Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

Outlook • • • NEMO phase 1 mini-tower Clock Requirements Clock Shore Station implementation Time data flow The console Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

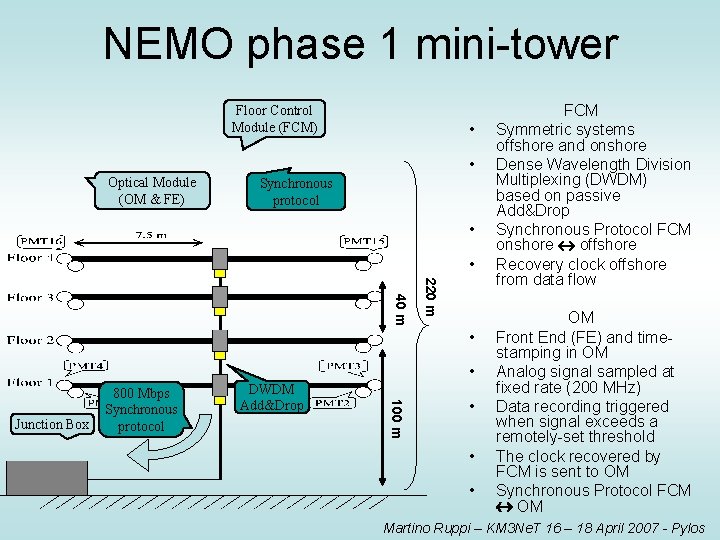

NEMO phase 1 mini-tower Floor Control Module (FCM) • • Optical Module (OM & FE) Synchronous protocol • • 220 m 40 m • • DWDM Add&Drop 100 m Junction Box 800 Mbps Synchronous protocol • • • FCM Symmetric systems offshore and onshore Dense Wavelength Division Multiplexing (DWDM) based on passive Add&Drop Synchronous Protocol FCM onshore offshore Recovery clock offshore from data flow OM Front End (FE) and timestamping in OM Analog signal sampled at fixed rate (200 MHz) Data recording triggered when signal exceeds a remotely-set threshold The clock recovered by FCM is sent to OM Synchronous Protocol FCM OM Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

Clock Requirements Time counting in OMs is based on clock recovered in FCM Each onshore FCM has to be synchronized by a low-jitter common clock We need to compare the OM time flow with UTC Onshore clock has to be extracted from GPS clock and time information has to be sent to the apparatus System scaling to KM 3 size The clock produced has to guarantee a very high fan-out Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

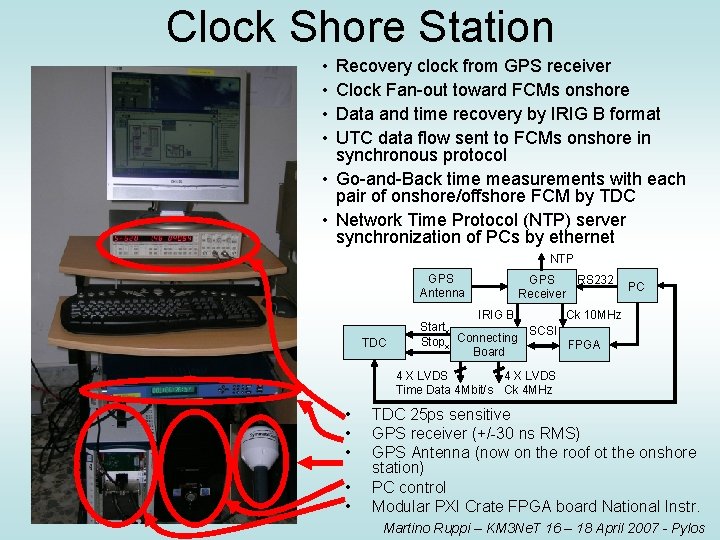

Clock Shore Station • • Recovery clock from GPS receiver Clock Fan-out toward FCMs onshore Data and time recovery by IRIG B format UTC data flow sent to FCMs onshore in synchronous protocol • Go-and-Back time measurements with each pair of onshore/offshore FCM by TDC • Network Time Protocol (NTP) server synchronization of PCs by ethernet NTP GPS Antenna TDC GPS RS 232 Receiver PC IRIG B Ck 10 MHz Startx SCSI Stopx Connecting FPGA Board 4 X LVDS Time Data 4 Mbit/s Ck 4 MHz • • • TDC 25 ps sensitive GPS receiver (+/-30 ns RMS) GPS Antenna (now on the roof ot the onshore station) PC control Modular PXI Crate FPGA board National Instr. Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

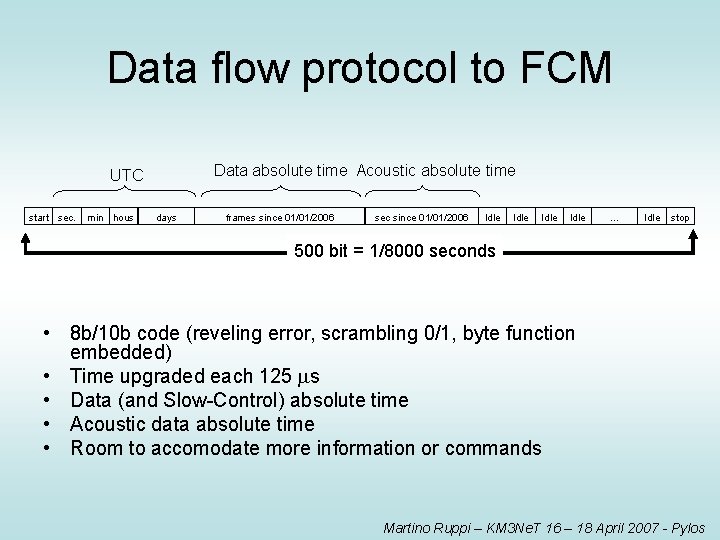

Data flow protocol to FCM Data absolute time Acoustic absolute time UTC start sec. min hous days frames since 01/01/2006 sec since 01/01/2006 Idle … Idle stop 500 bit = 1/8000 seconds • 8 b/10 b code (reveling error, scrambling 0/1, byte function embedded) • Time upgraded each 125 s • Data (and Slow-Control) absolute time • Acoustic data absolute time • Room to accomodate more information or commands Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

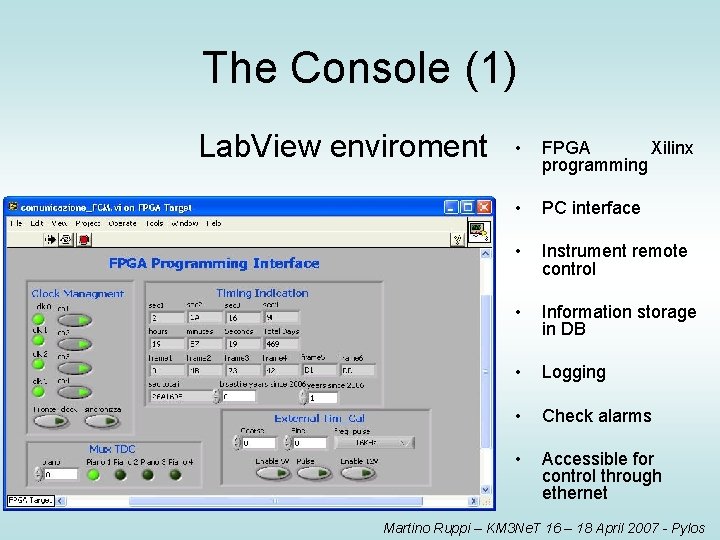

The Console (1) Lab. View enviroment • FPGA Xilinx programming • PC interface • Instrument remote control • Information storage in DB • Logging • Check alarms • Accessible for control through ethernet Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

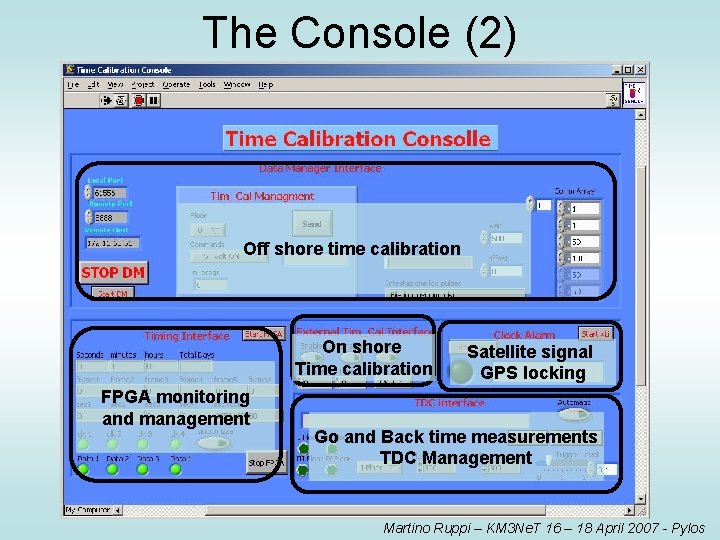

The Console (2) Off shore time calibration On shore Time calibration FPGA monitoring and management Satellite signal GPS locking Go and Back time measurements TDC Management Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

Conclusions • The system is currently working in the NEMO Phase 1 control station • Extension for a full-size 16 -floor tower is undergoing (NEMO Phase 2) • The setup can be easily adapted to serve even a KM 3 -size apparatus (it only needs more modules for the PXI crate) Martino Ruppi – KM 3 Ne. T 16 – 18 April 2007 - Pylos

- Slides: 9