Clock Configuration for GBT Application GBT application requires

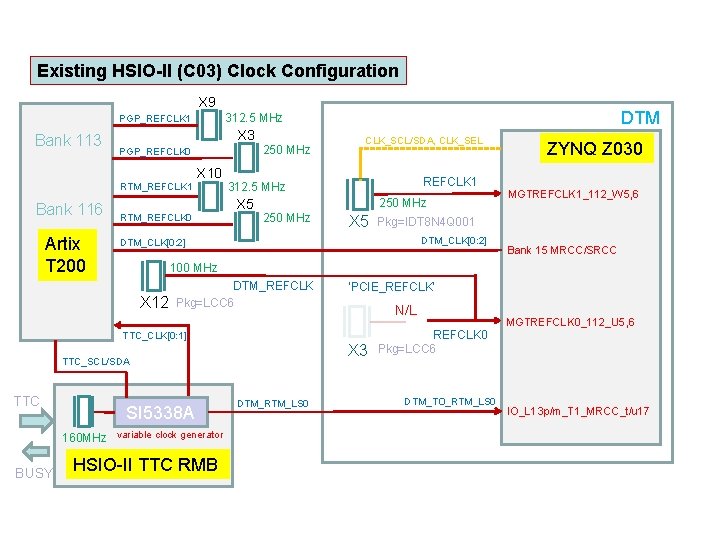

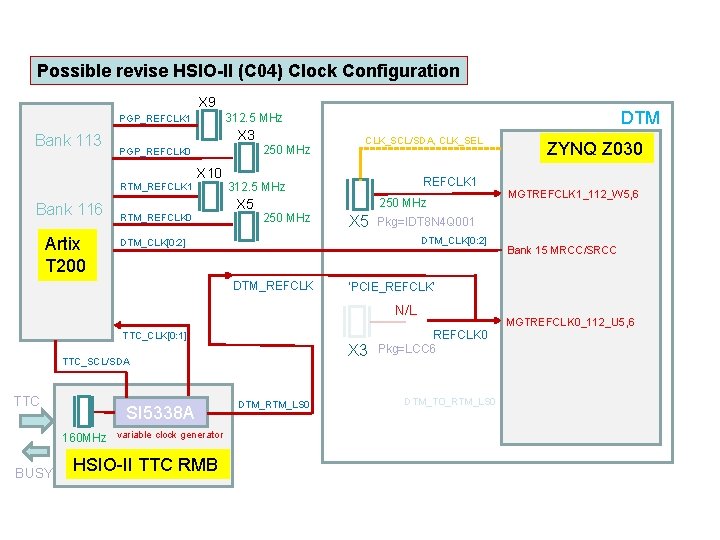

Clock Configuration for GBT Application GBT application requires 120 MHz clock for MGT HSIO-II: * TTC RMB variable clock generator has 120 MHz TTC clock for Artix, but clock to DTM is delivered to a regular fabric clock pin. * Simplest to to replace HSIO-II X 12 100 MHz Oscillator with 120 MHz part, but only on-shelf part has a central ground pad that can short out HSIO-II board pads. Tried one replacement with central pad taped over. * Possible revision for HSIO-II to redirect TTC RMB clock to DTM REFclock path to replace the X 12 oscillator.

Existing HSIO-II (C 03) Clock Configuration X 9 Bank 113 X 3 250 MHz PGP_REFCLK 0 X 10 RTM_REFCLK 1 Bank 116 Artix T 200 DTM 312. 5 MHz PGP_REFCLK 1 312. 5 MHz X 5 RTM_REFCLK 0 CLK_SCL/SDA, CLK_SEL 250 MHz X 5 DTM_CLK[0: 2] Bank 15 MRCC/SRCC 100 MHz DTM_REFCLK Pkg=LCC 6 ‘PCIE_REFCLK’ N/L TTC_CLK[0: 1] X 3 TTC_SCL/SDA SI 5338 A 160 MHz variable clock generator BUSY MGTREFCLK 1_112_W 5, 6 Pkg=IDT 8 N 4 Q 001 DTM_CLK[0: 2] X 12 TTC ZYNQ Z 030 HSIO-II TTC RMB DTM_RTM_LS 0 MGTREFCLK 0_112_U 5, 6 REFCLK 0 Pkg=LCC 6 DTM_TO_RTM_LS 0 IO_L 13 p/m_T 1_MRCC_t/u 17

Possible revise HSIO-II (C 04) Clock Configuration X 9 Bank 113 X 3 250 MHz PGP_REFCLK 0 X 10 RTM_REFCLK 1 Bank 116 Artix T 200 DTM 312. 5 MHz PGP_REFCLK 1 312. 5 MHz X 5 RTM_REFCLK 0 CLK_SCL/SDA, CLK_SEL 250 MHz X 5 DTM_CLK[0: 2] TTC_CLK[0: 1] TTC SI 5338 A X 3 160 MHz variable clock generator BUSY HSIO-II TTC RMB DTM_RTM_LS 0 Bank 15 MRCC/SRCC ‘PCIE_REFCLK’ N/L TTC_SCL/SDA MGTREFCLK 1_112_W 5, 6 Pkg=IDT 8 N 4 Q 001 DTM_CLK[0: 2] DTM_REFCLK ZYNQ Z 030 REFCLK 0 Pkg=LCC 6 DTM_TO_RTM_LS 0 MGTREFCLK 0_112_U 5, 6

120 MHz Source for COB * Current COB+RTM rely on external TTC source to generate 120 MHz * Cannot touch the 100 MHz oscillator on the COB – needed for PCIe control * Only need 120 MHz MGTrefclk for DPM which can only come from the TTC distribution path from DTM, while DTM itself don’t need to run GBT on the COB * Can do a simple revision of the TTC RTM with a clock generator to output 120 MHz, but how does this co-exists with TTC if that needs to be run at the same time ?

- Slides: 4