CLEOIII Trigger DAQ Status Trigger Illinois Cornell DAQ

- Slides: 18

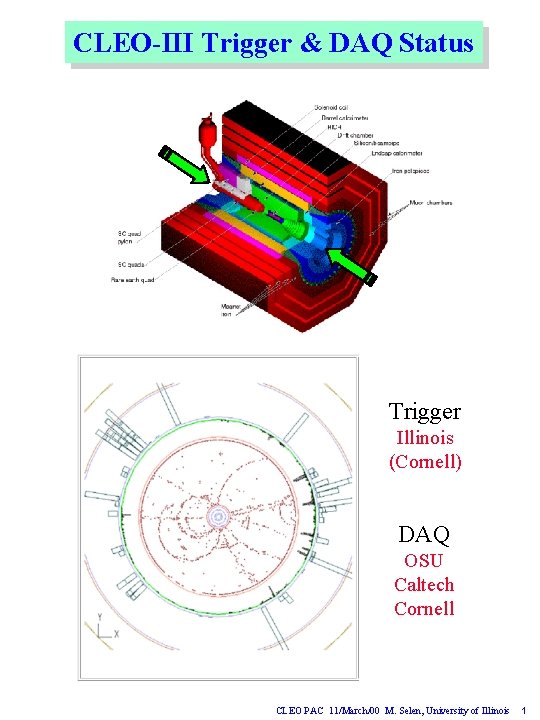

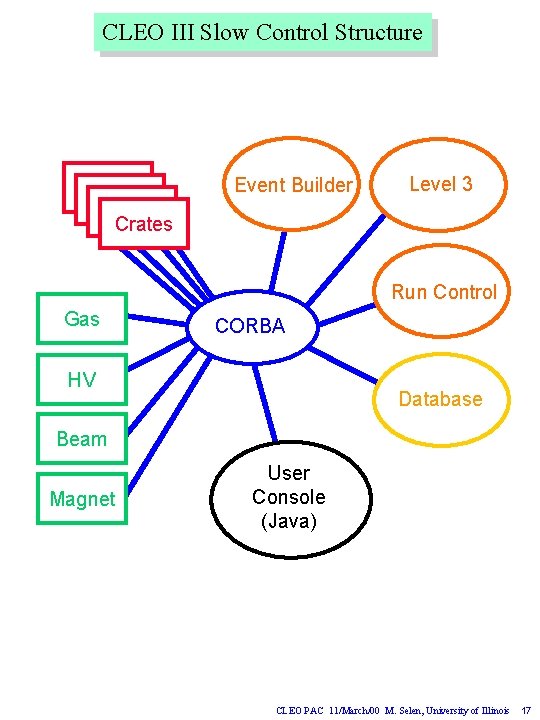

CLEO-III Trigger & DAQ Status Trigger Illinois (Cornell) DAQ OSU Caltech Cornell CLEO PAC 11/March/00 M. Selen, University of Illinois 1

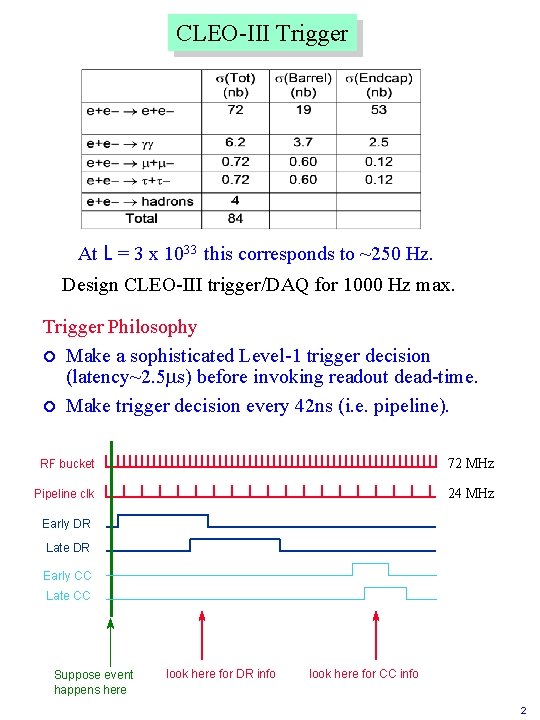

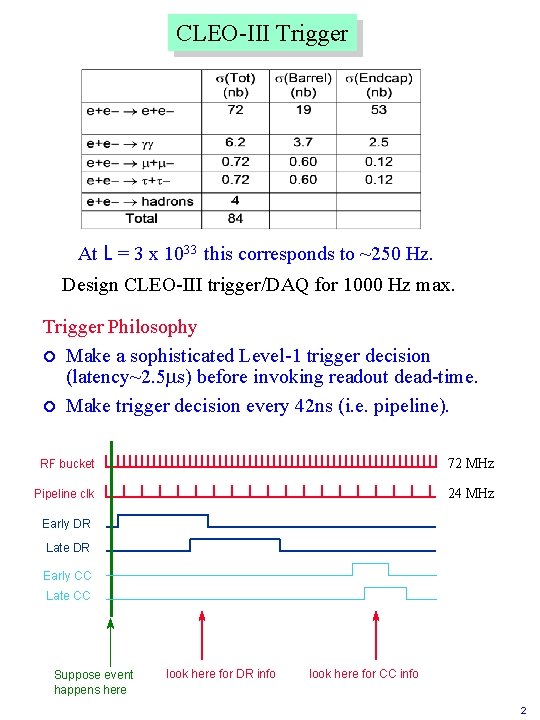

CLEO-III Trigger At L = 3 x 1033 this corresponds to ~250 Hz. Design CLEO-III trigger/DAQ for 1000 Hz max. Trigger Philosophy ¡ Make a sophisticated Level-1 trigger decision (latency~2. 5 ms) before invoking readout dead-time. ¡ Make trigger decision every 42 ns (i. e. pipeline). RF bucket 72 MHz Pipeline clk 24 MHz Early DR Late DR Early CC Late CC Suppose event happens here look here for DR info look here for CC info 2

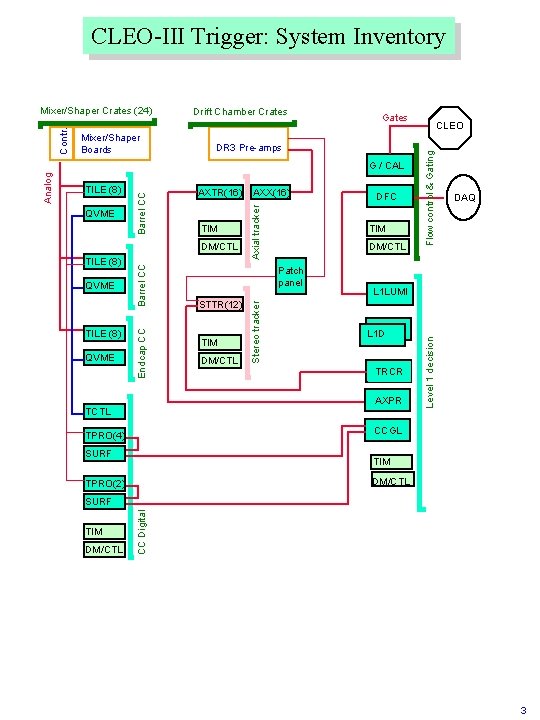

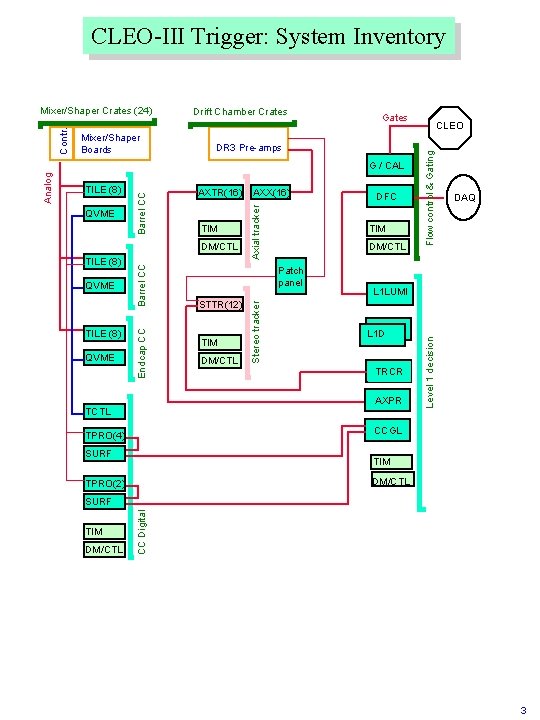

CLEO-III Trigger: System Inventory Gates DR 3 Pre-amps AXTR(16) AXX(16) TIM QVME TILE (8) QVME Endcap CC Axial tracker TILE (8) Barrel CC DM/CTL STTR(12) TIM DM/CTL DFC TIM DM/CTL Patch panel Stereo tracker QVME Barrel CC TILE (8) DAQ L 1 LUMI L 1 D TRCR AXPR TCTL CCGL TPRO(4) SURF TIM DM/CTL TPRO(2) SURF TIM DM/CTL CC Digital Analog G / CAL CLEO Flow control & Gating Mixer/Shaper Boards Drift Chamber Crates Level 1 decision Contr. Mixer/Shaper Crates (24) 3

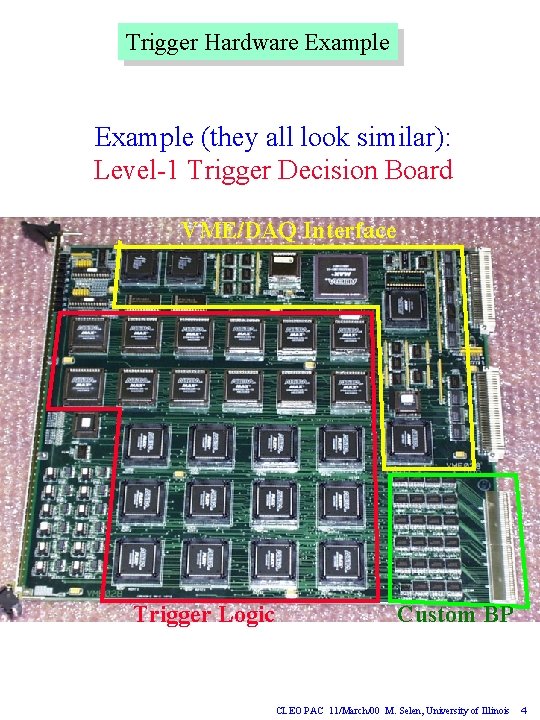

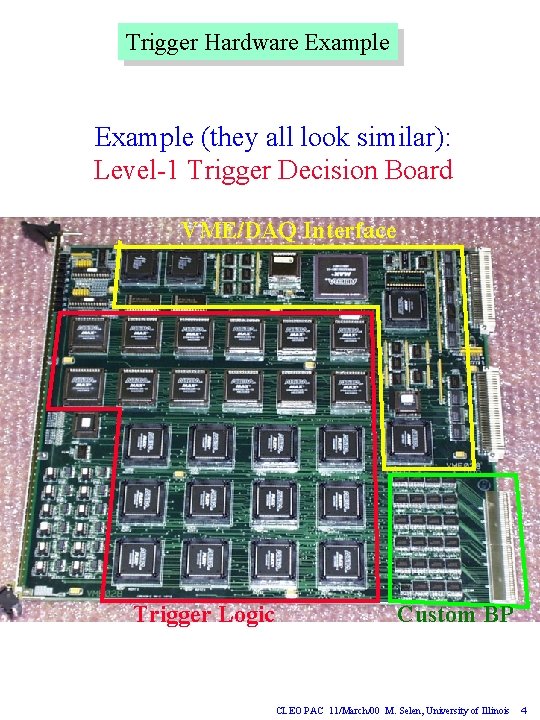

Trigger Hardware Example (they all look similar): Level-1 Trigger Decision Board VME/DAQ Interface Trigger Logic Custom BP CLEO PAC 11/March/00 M. Selen, University of Illinois 4

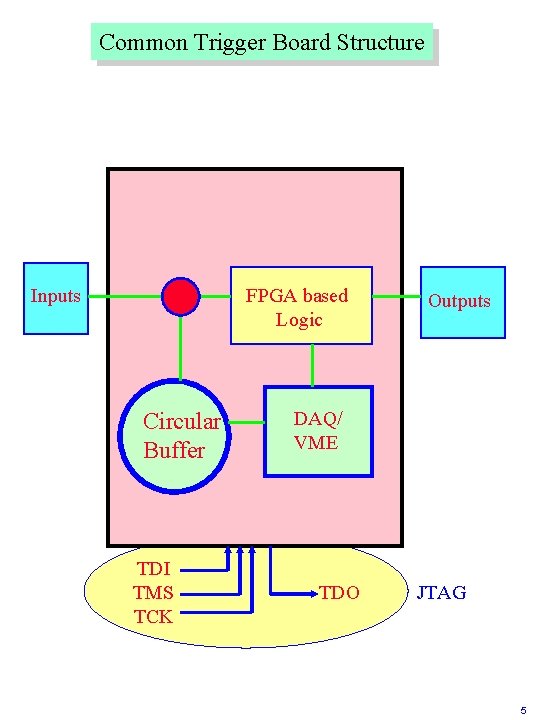

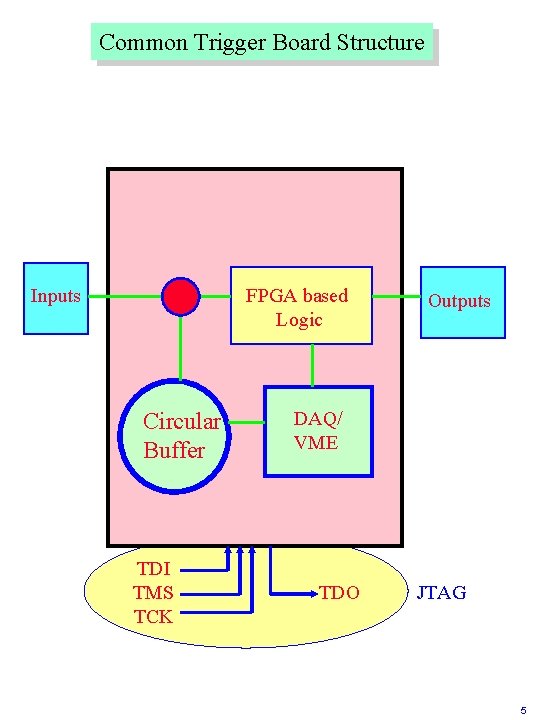

Common Trigger Board Structure Inputs FPGA based Logic Circular Buffer TDI TMS TCK Outputs DAQ/ VME TDO JTAG 5

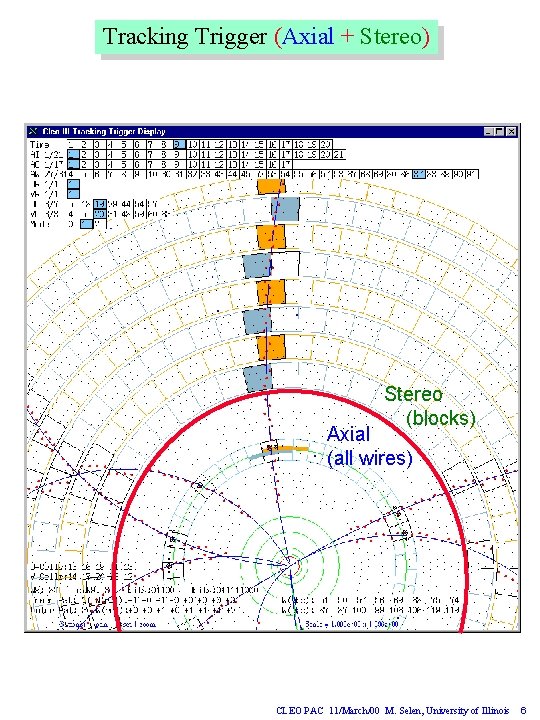

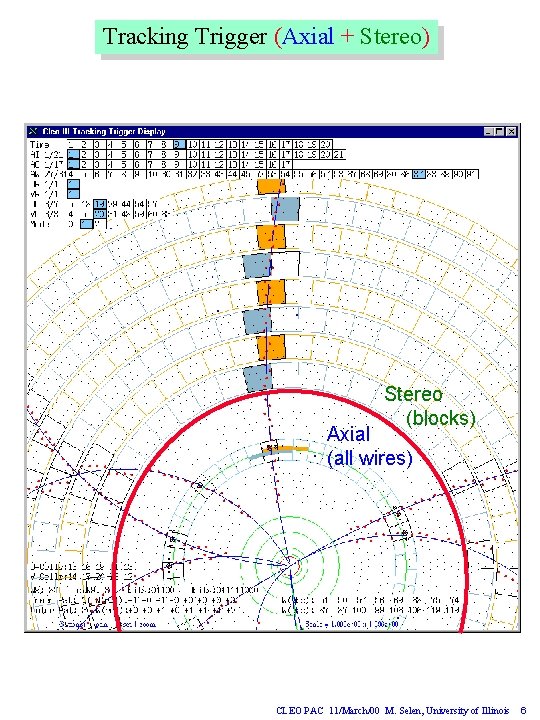

Tracking Trigger (Axial + Stereo) Stereo (blocks) Axial (all wires) CLEO PAC 11/March/00 M. Selen, University of Illinois 6

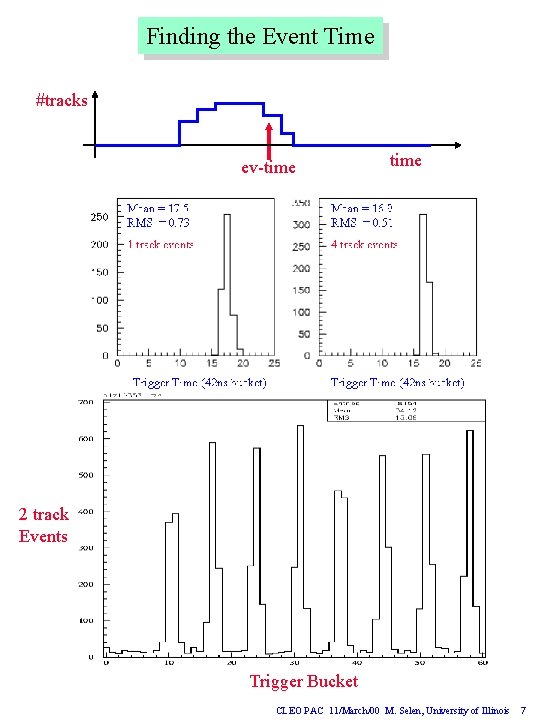

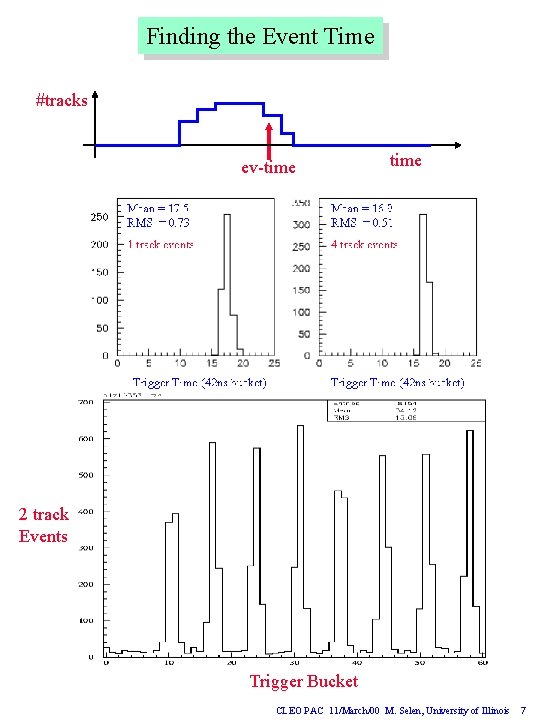

Finding the Event Time #tracks ev-time 2 track Events Trigger Bucket CLEO PAC 11/March/00 M. Selen, University of Illinois 7

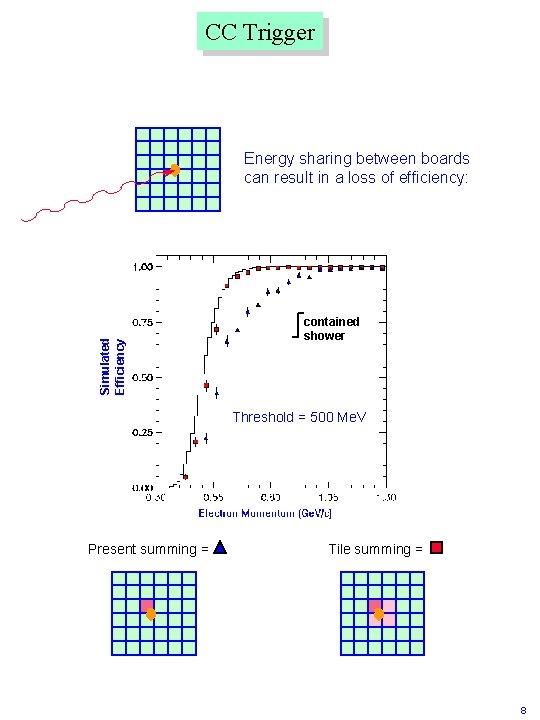

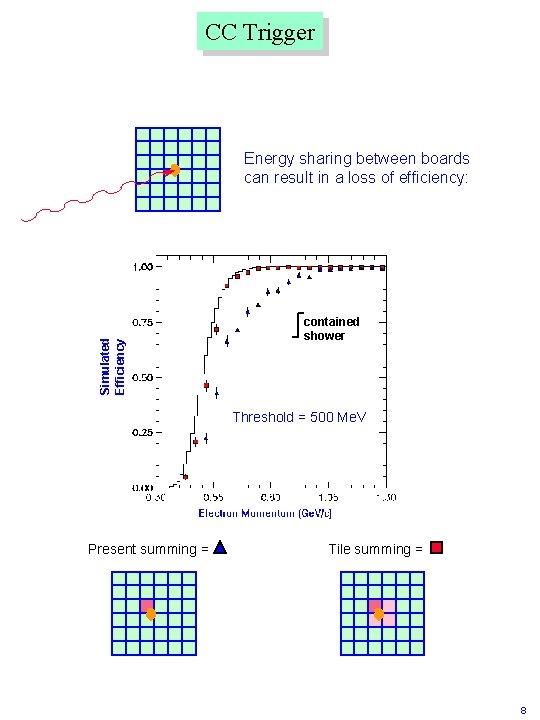

CC Trigger Simulated Efficiency Energy sharing between boards can result in a loss of efficiency: contained shower Threshold = 500 Me. V Present summing = Tile summing = 8

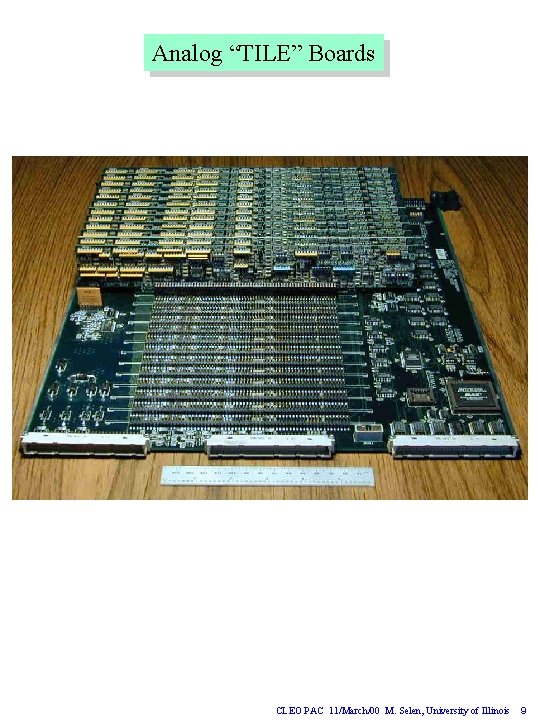

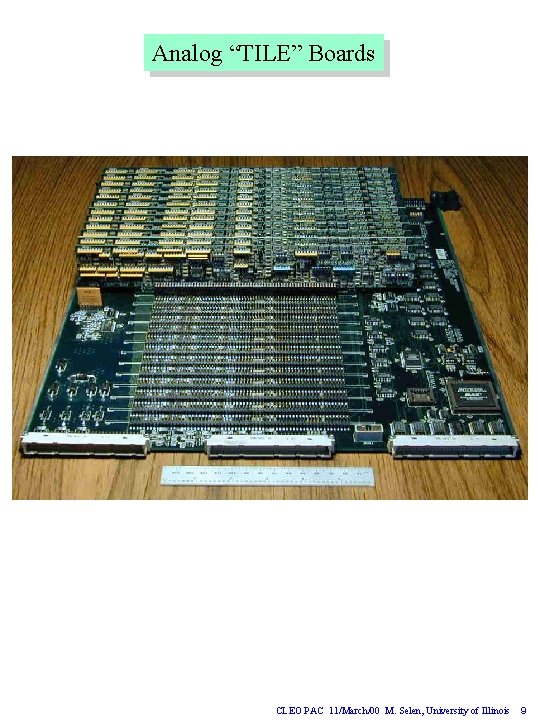

Analog “TILE” Boards CLEO PAC 11/March/00 M. Selen, University of Illinois 9

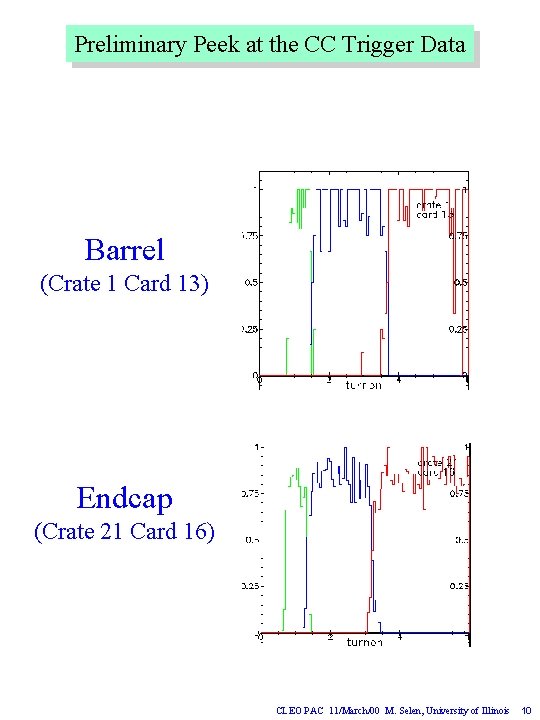

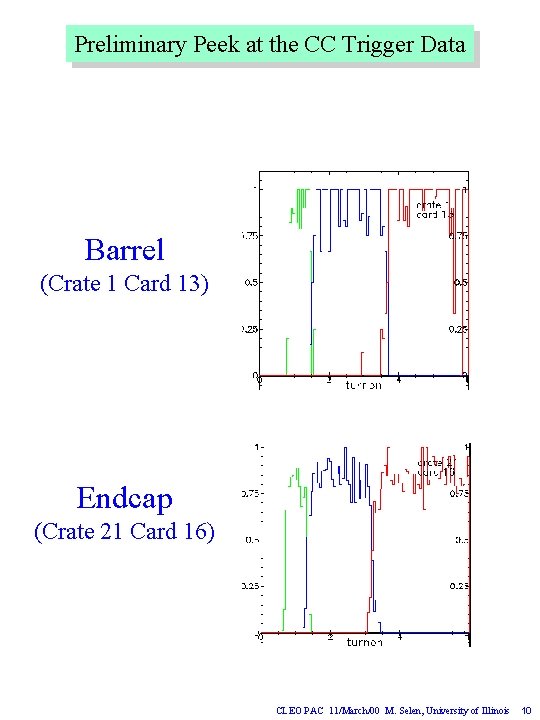

Preliminary Peek at the CC Trigger Data Barrel (Crate 1 Card 13) Endcap (Crate 21 Card 16) CLEO PAC 11/March/00 M. Selen, University of Illinois 10

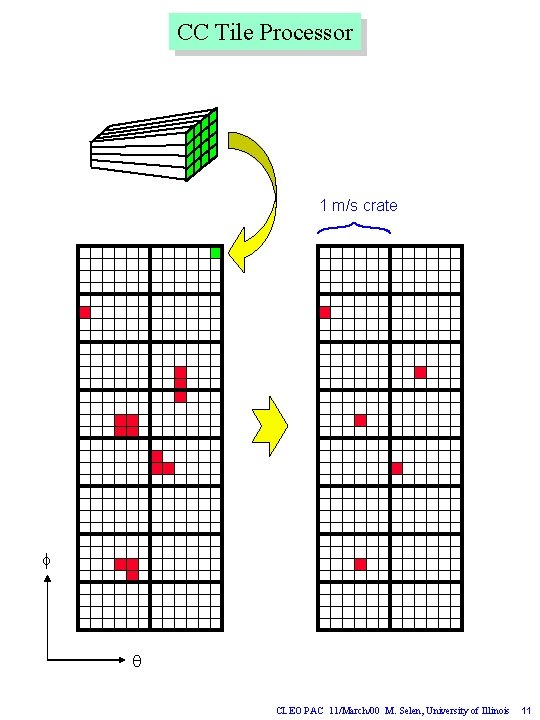

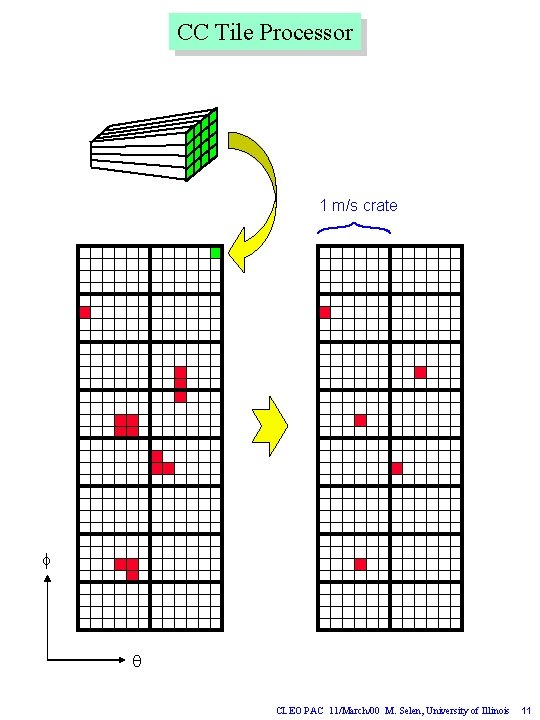

CC Tile Processor 1 m/s crate CLEO PAC 11/March/00 M. Selen, University of Illinois 11

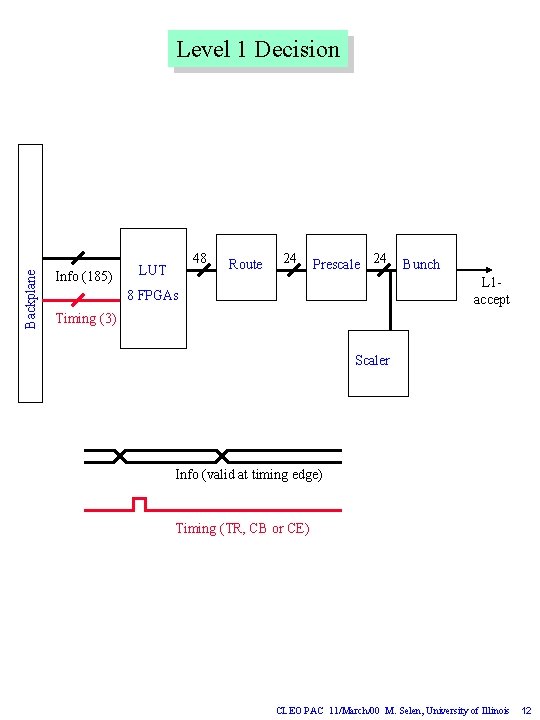

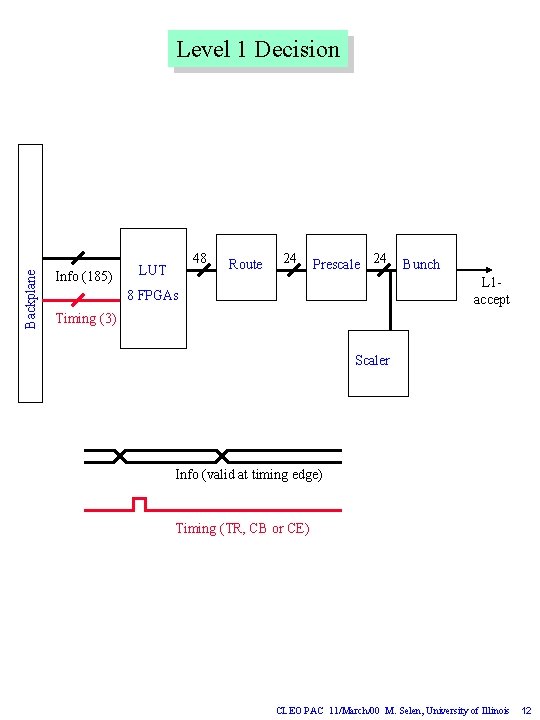

Backplane Level 1 Decision Info (185) 48 LUT Route 24 Prescale 24 Bunch L 1 accept 8 FPGAs Timing (3) Scaler Info (valid at timing edge) Timing (TR, CB or CE) CLEO PAC 11/March/00 M. Selen, University of Illinois 12

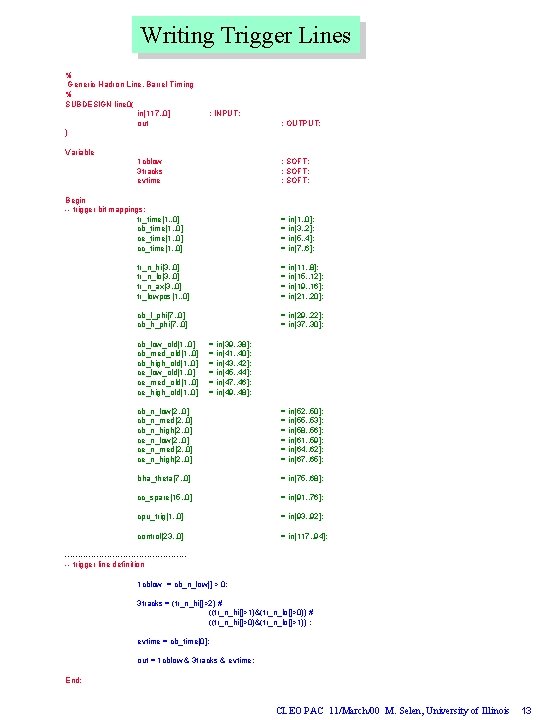

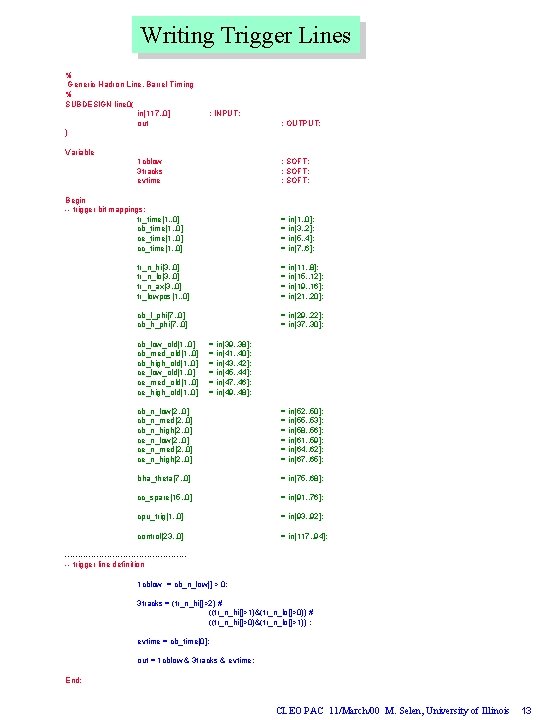

Writing Trigger Lines % Generic Hadron Line, Barrel Timing % SUBDESIGN line 0( in[117. . 0] out ) : INPUT; : OUTPUT; Variable 1 cblow 3 tracks evtime : SOFT; Begin -- trigger bit mappings: tr_time[1. . 0] cb_time[1. . 0] ce_time[1. . 0] cc_time[1. . 0] = in[1. . 0]; = in[3. . 2]; = in[5. . 4]; = in[7. . 6]; tr_n_hi[3. . 0] tr_n_lo[3. . 0] tr_n_ax[3. . 0] tr_lowpos[1. . 0] = in[11. . 8]; = in[15. . 12]; = in[19. . 16]; = in[21. . 20]; cb_l_phi[7. . 0] cb_h_phi[7. . 0] = in[29. . 22]; = in[37. . 30]; cb_low_old[1. . 0] cb_med_old[1. . 0] cb_high_old[1. . 0] ce_low_old[1. . 0] ce_med_old[1. . 0] ce_high_old[1. . 0] = in[39. . 38]; = in[41. . 40]; = in[43. . 42]; = in[45. . 44]; = in[47. . 46]; = in[49. . 48]; cb_n_low[2. . 0] cb_n_med[2. . 0] cb_n_high[2. . 0] ce_n_low[2. . 0] ce_n_med[2. . 0] ce_n_high[2. . 0] = in[52. . 50]; = in[55. . 53]; = in[58. . 56]; = in[61. . 59]; = in[64. . 62]; = in[67. . 65]; bha_theta[7. . 0] = in[75. . 68]; cc_spare[15. . 0] = in[91. . 76]; cpu_trig[1. . 0] = in[93. . 92]; control[23. . 0] = in[117. . 94]; ------------------------ trigger line definition 1 cblow = cb_n_low[] > 0; 3 tracks = (tr_n_hi[]>2) # ((tr_n_hi[]>1)&(tr_n_lo[]>0)) # ((tr_n_hi[]>0)&(tr_n_lo[]>1)) ; evtime = cb_time[0]; out = 1 cblow & 3 tracks & evtime; End; CLEO PAC 11/March/00 M. Selen, University of Illinois 13

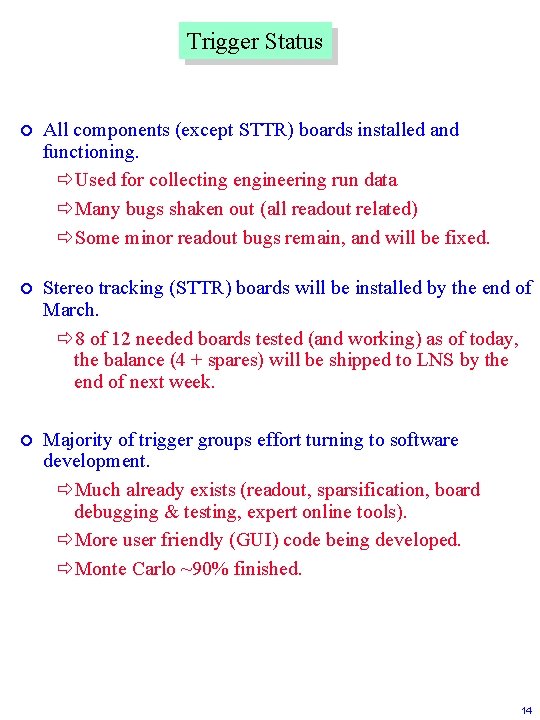

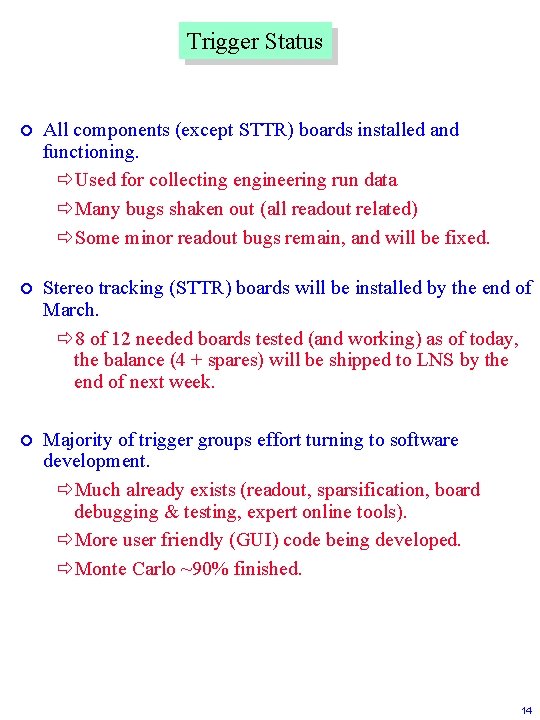

Trigger Status ¡ All components (except STTR) boards installed and functioning. ðUsed for collecting engineering run data ðMany bugs shaken out (all readout related) ðSome minor readout bugs remain, and will be fixed. ¡ Stereo tracking (STTR) boards will be installed by the end of March. ð 8 of 12 needed boards tested (and working) as of today, the balance (4 + spares) will be shipped to LNS by the end of next week. ¡ Majority of trigger groups effort turning to software development. ðMuch already exists (readout, sparsification, board debugging & testing, expert online tools). ðMore user friendly (GUI) code being developed. ðMonte Carlo ~90% finished. 14

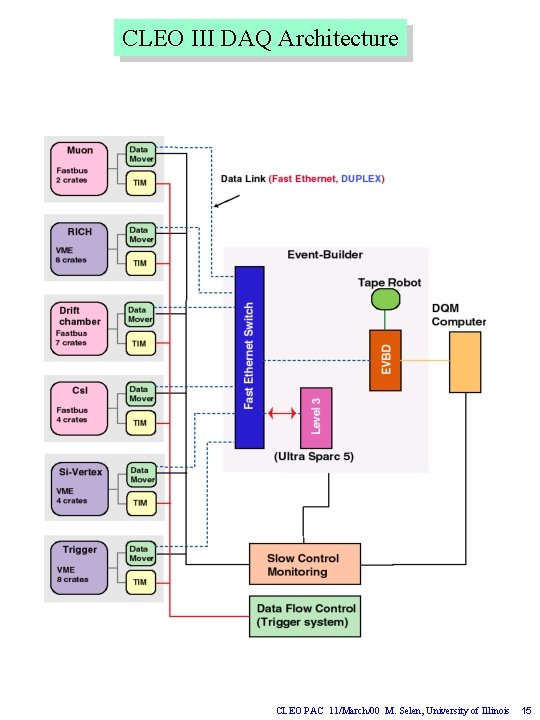

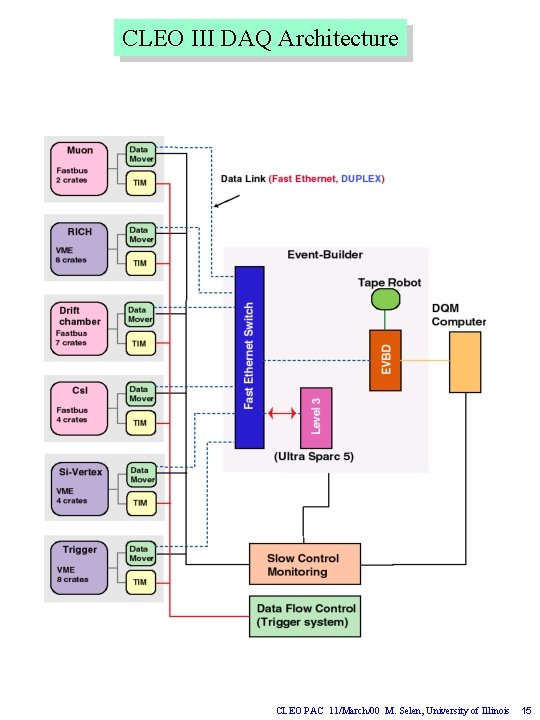

CLEO III DAQ Architecture CLEO PAC 11/March/00 M. Selen, University of Illinois 15

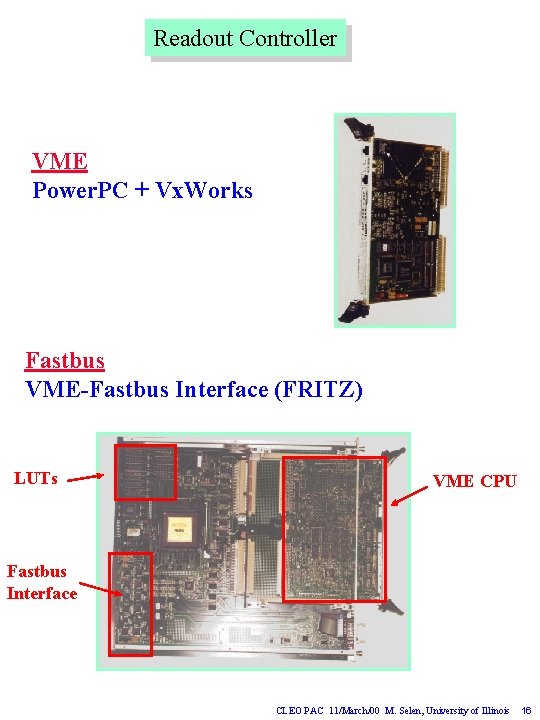

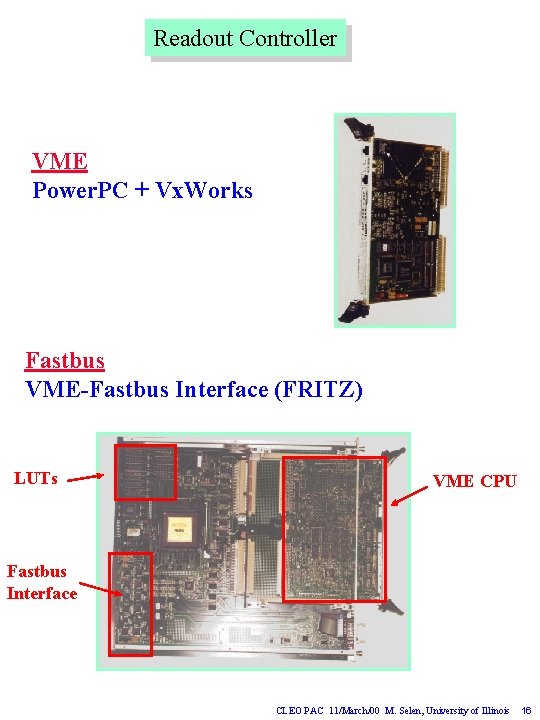

Readout Controller VME Power. PC + Vx. Works Fastbus VME-Fastbus Interface (FRITZ) LUTs VME CPU Fastbus Interface CLEO PAC 11/March/00 M. Selen, University of Illinois 16

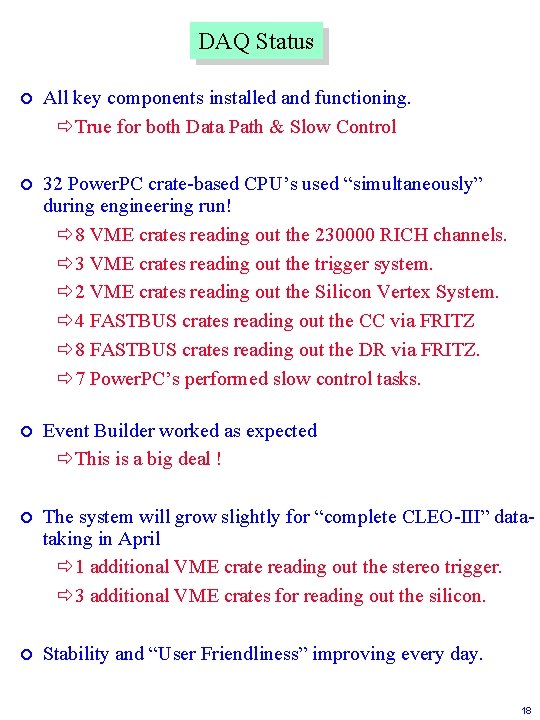

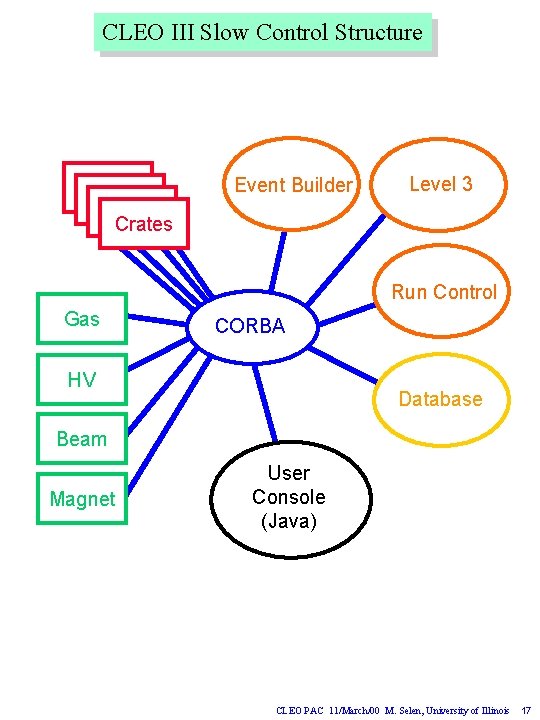

CLEO III Slow Control Structure Event Builder Level 3 Crates Run Control Gas CORBA HV Database Beam Magnet User Console (Java) CLEO PAC 11/March/00 M. Selen, University of Illinois 17

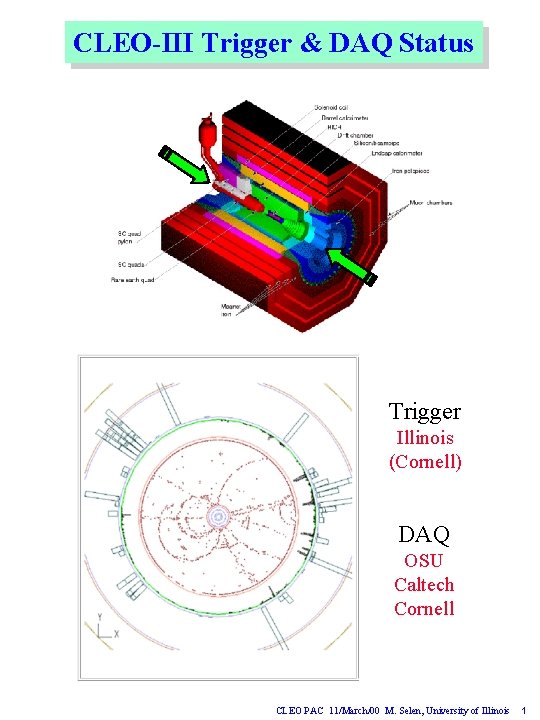

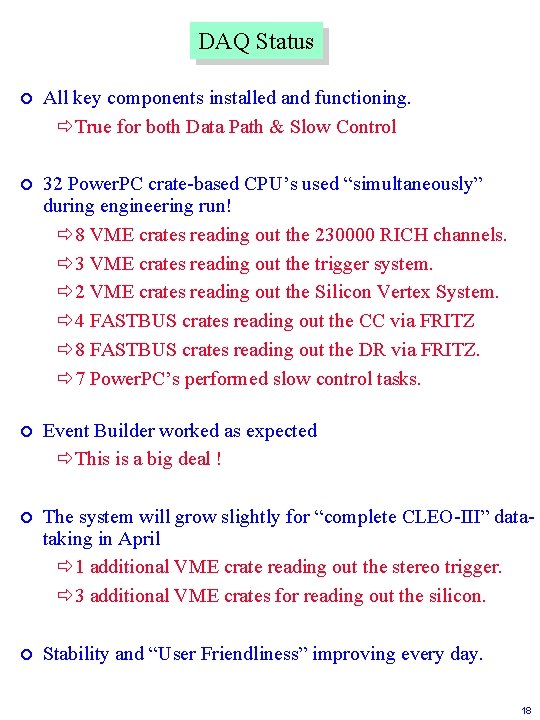

DAQ Status ¡ All key components installed and functioning. ðTrue for both Data Path & Slow Control ¡ 32 Power. PC crate-based CPU’s used “simultaneously” during engineering run! ð 8 VME crates reading out the 230000 RICH channels. ð 3 VME crates reading out the trigger system. ð 2 VME crates reading out the Silicon Vertex System. ð 4 FASTBUS crates reading out the CC via FRITZ ð 8 FASTBUS crates reading out the DR via FRITZ. ð 7 Power. PC’s performed slow control tasks. ¡ Event Builder worked as expected ðThis is a big deal ! ¡ The system will grow slightly for “complete CLEO-III” datataking in April ð 1 additional VME crate reading out the stereo trigger. ð 3 additional VME crates for reading out the silicon. ¡ Stability and “User Friendliness” improving every day. 18