Classification of Simulators Logic Simulators HDLbased Eventdriven Cyclebased

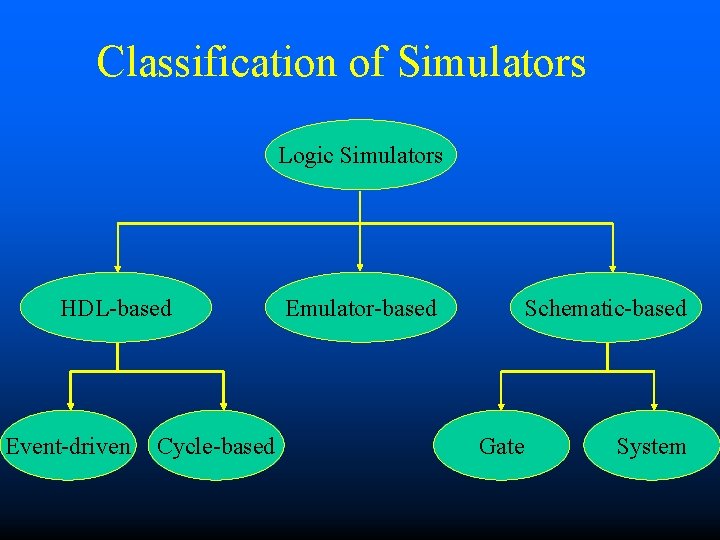

Classification of Simulators Logic Simulators HDL-based Event-driven Cycle-based Emulator-based Schematic-based Gate System

Classification of Simulators • HDL-based: Design and testbench described using HDL-based HDL – Event-driven – Cycle-based • Schematic-based: Design is entered graphically using Schematic-based a schematic editor • Emulators: Design is mapped into FPGA hardware for Emulators prototype simulation. Used to perform hardware/software co-simulation.

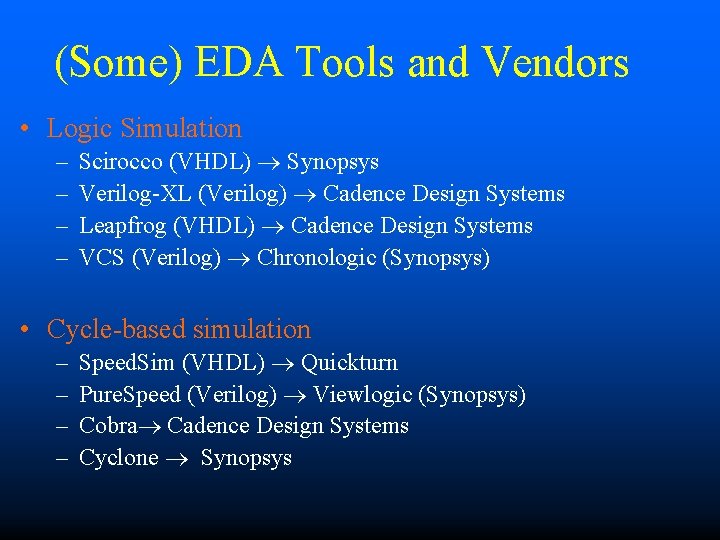

(Some) EDA Tools and Vendors • Logic Simulation – – Scirocco (VHDL) Synopsys Verilog-XL (Verilog) Cadence Design Systems Leapfrog (VHDL) Cadence Design Systems VCS (Verilog) Chronologic (Synopsys) • Cycle-based simulation – – Speed. Sim (VHDL) Quickturn Pure. Speed (Verilog) Viewlogic (Synopsys) Cobra Cadence Design Systems Cyclone Synopsys

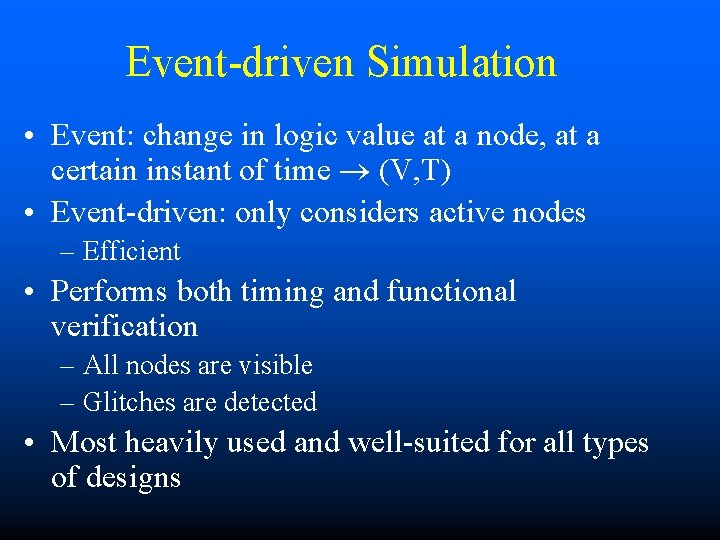

Event-driven Simulation • Event: change in logic value at a node, at a certain instant of time (V, T) • Event-driven: only considers active nodes – Efficient • Performs both timing and functional verification – All nodes are visible – Glitches are detected • Most heavily used and well-suited for all types of designs

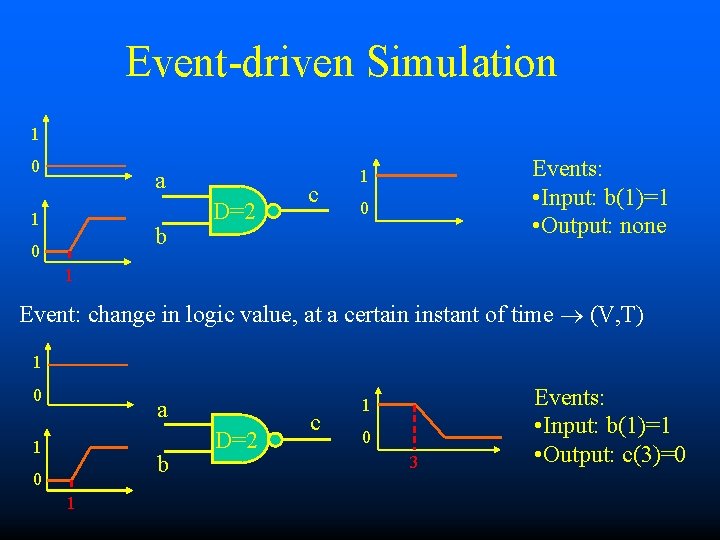

Event-driven Simulation 1 0 a 1 b 0 D=2 c Events: • Input: b(1)=1 • Output: none 1 0 1 Event: change in logic value, at a certain instant of time (V, T) 1 0 a 1 b 0 1 D=2 c 1 0 3 Events: • Input: b(1)=1 • Output: c(3)=0

Event-driven Simulation • Uses a timewheel to manage the relationship between components • Timewheel = list of all events not processed Timewheel yet, sorted in time (complete ordering) • When event is generated, it is put in the appropriate point in the timewheel to ensure causality

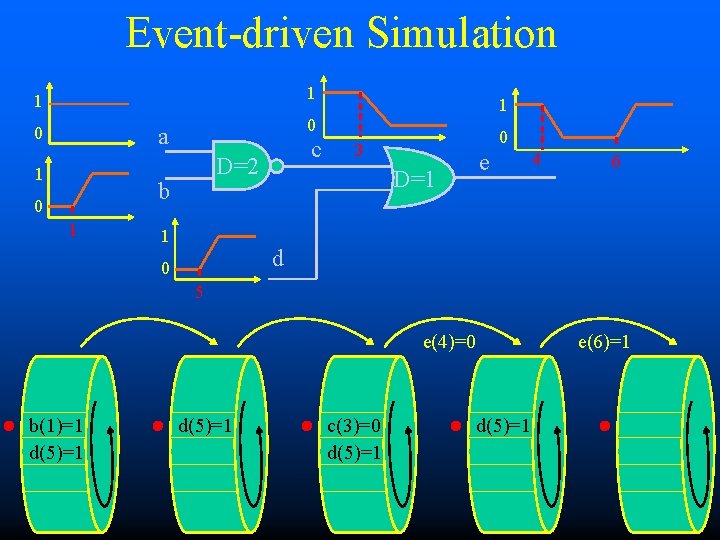

Event-driven Simulation 1 1 0 a 0 1 1 c D=2 b 0 1 1 0 3 D=1 e 4 6 d 0 5 e(6)=1 e(4)=0 b(1)=1 d(5)=1 c(3)=0 d(5)=1

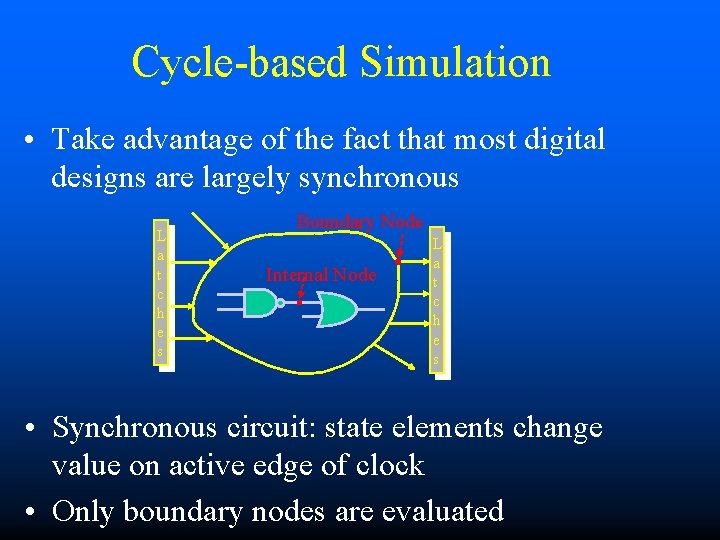

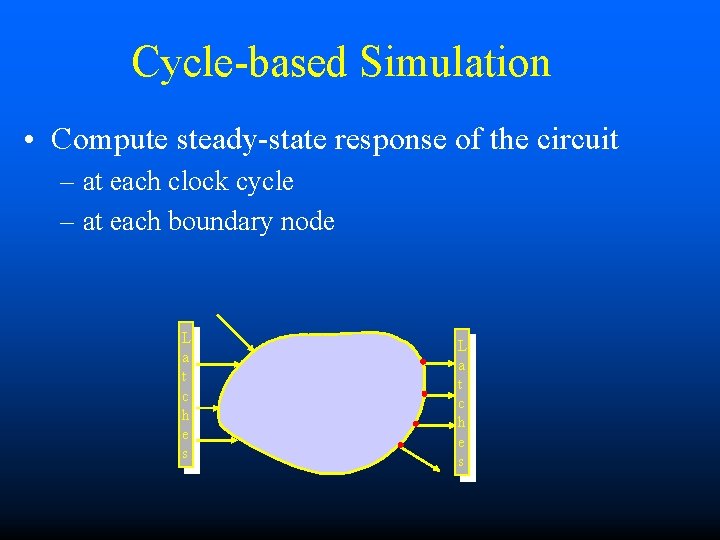

Cycle-based Simulation • Take advantage of the fact that most digital designs are largely synchronous L a t c h e s Boundary Node Internal Node L a t c h e s • Synchronous circuit: state elements change value on active edge of clock • Only boundary nodes are evaluated

Cycle-based Simulation • Compute steady-state response of the circuit – at each clock cycle – at each boundary node L a t c h e s Internal Node L a t c h e s

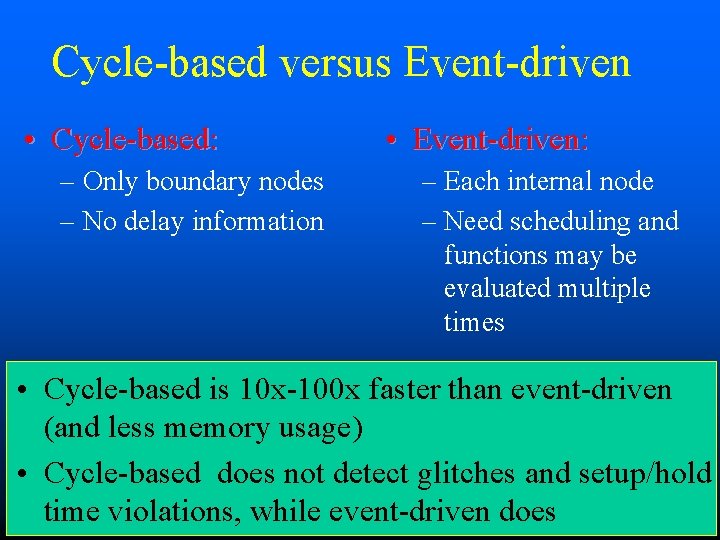

Cycle-based versus Event-driven • Cycle-based: – Only boundary nodes – No delay information • Event-driven: – Each internal node – Need scheduling and functions may be evaluated multiple times • Cycle-based is 10 x-100 x faster than event-driven (and less memory usage) • Cycle-based does not detect glitches and setup/hold time violations, while event-driven does

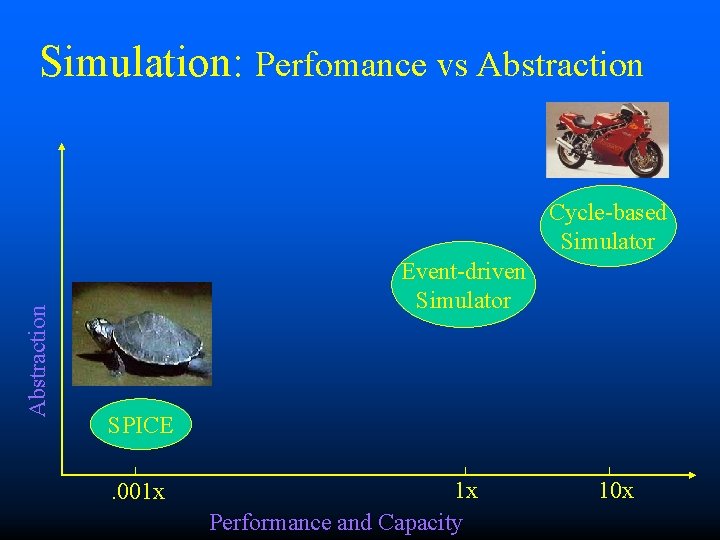

Simulation: Perfomance vs Abstraction Cycle-based Simulator Event-driven Simulator SPICE. 001 x 1 x Performance and Capacity 10 x

Simulation Testplan • Simulation – Write test vectors – Run simulation – Inspect results • About test vectors – HDL code coverage

Formal verification Symbolic simulation Can be applied in property checking. . . Or in input space constraining Digitaalsüsteemide verifitseerimise kursus 13

Symbolic simulation • Free variables (primary inputs, flip-flops) and internal variables. • Considers relations between free variables, not the stimuli values. Good for verifying properties. • Circuit unrolling for sequential circuits. Expressions will become complex! • BDDS used in representing the expressions. Digitaalsüsteemide verifitseerimise kursus 14

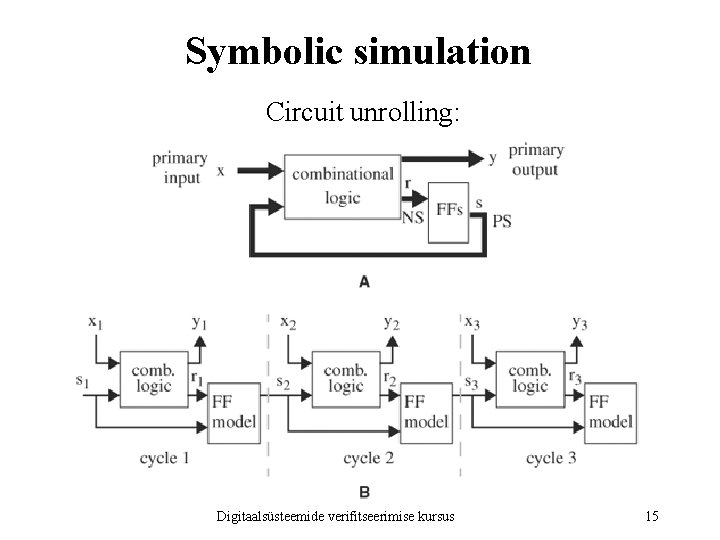

Symbolic simulation Circuit unrolling: Digitaalsüsteemide verifitseerimise kursus 15

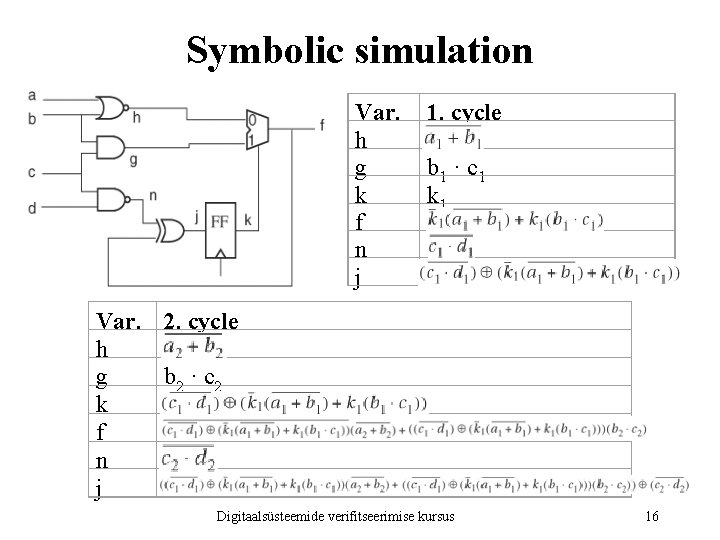

Symbolic simulation Var. h g k f n j 1. cycle b 1 · c 1 k 1 2. cycle b 2 · c 2 Digitaalsüsteemide verifitseerimise kursus 16

Symbolic verification • Symbolic simulation allows considering several stimuli simultaneously. • Thus suitable for verifying properties (assertions) • Properties may be time-limited (bound) or time-unlimited (unbound) • Symbolic verification can be applied to the former Digitaalsüsteemide verifitseerimise kursus 17

Input Space Constraining • Assign concrete values to some inputs and simulate • Simplifies the expressions considerably • A goal to verify partial functionality (functional partitioning) or to represent the environment • In the extreme case, where all the variables have values, it will be equivalent to normal simulation Digitaalsüsteemide verifitseerimise kursus 18

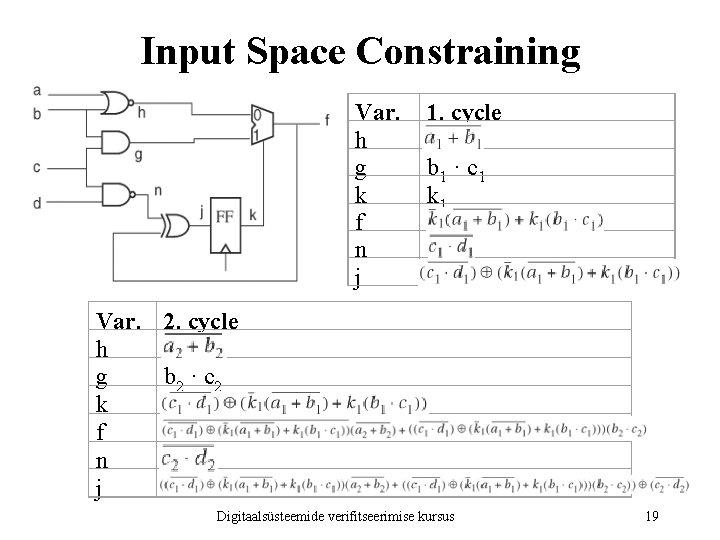

Input Space Constraining Var. h g k f n j 1. cycle b 1 · c 1 k 1 2. cycle b 2 · c 2 Digitaalsüsteemide verifitseerimise kursus 19

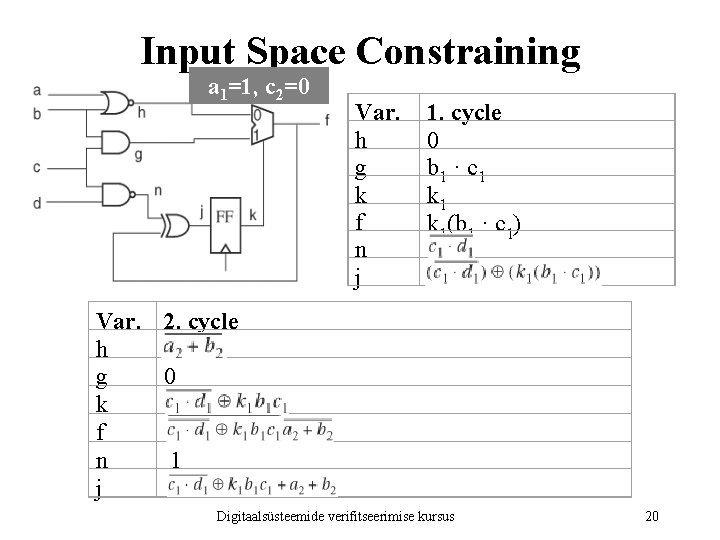

Input Space Constraining a 1=1, c 2=0 Var. h g k f n j 1. cycle 0 b 1 · c 1 k 1 (b 1 · c 1) 2. cycle 0 1 Digitaalsüsteemide verifitseerimise kursus 20

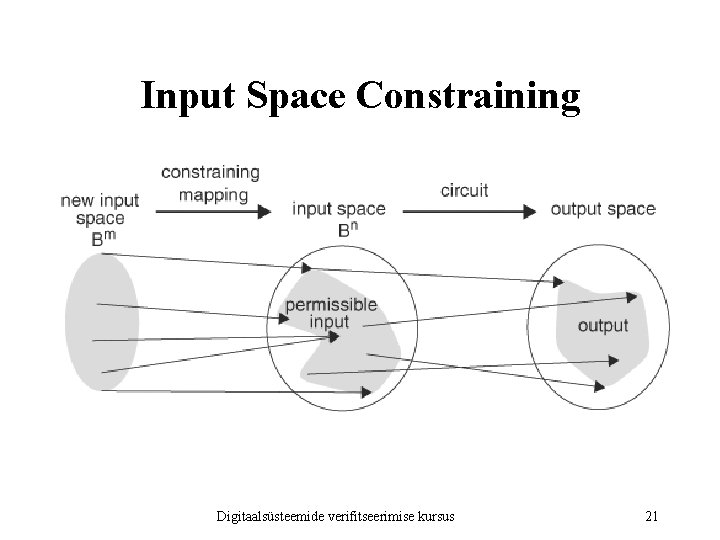

Input Space Constraining Digitaalsüsteemide verifitseerimise kursus 21

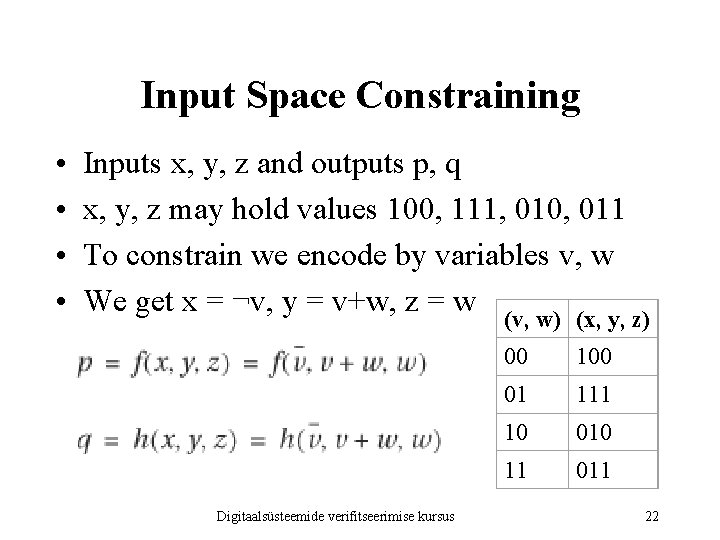

Input Space Constraining • • Inputs x, y, z and outputs p, q x, y, z may hold values 100, 111, 010, 011 To constrain we encode by variables v, w We get x = ¬v, y = v+w, z = w (v, w) (x, y, z) Digitaalsüsteemide verifitseerimise kursus 00 100 01 111 10 010 11 011 22

- Slides: 22